# Optimization of the New Vertex Detector for (Super) Belle

T.Hara (Osaka U) for Belle SVD group

#### - Contents -

- . Status of the current Silicon Vertex Detector

- . Super KEKB/Belle

- . Optimization of the Baseline design

- . Optimization of the Final (Lol) design

- . Summary

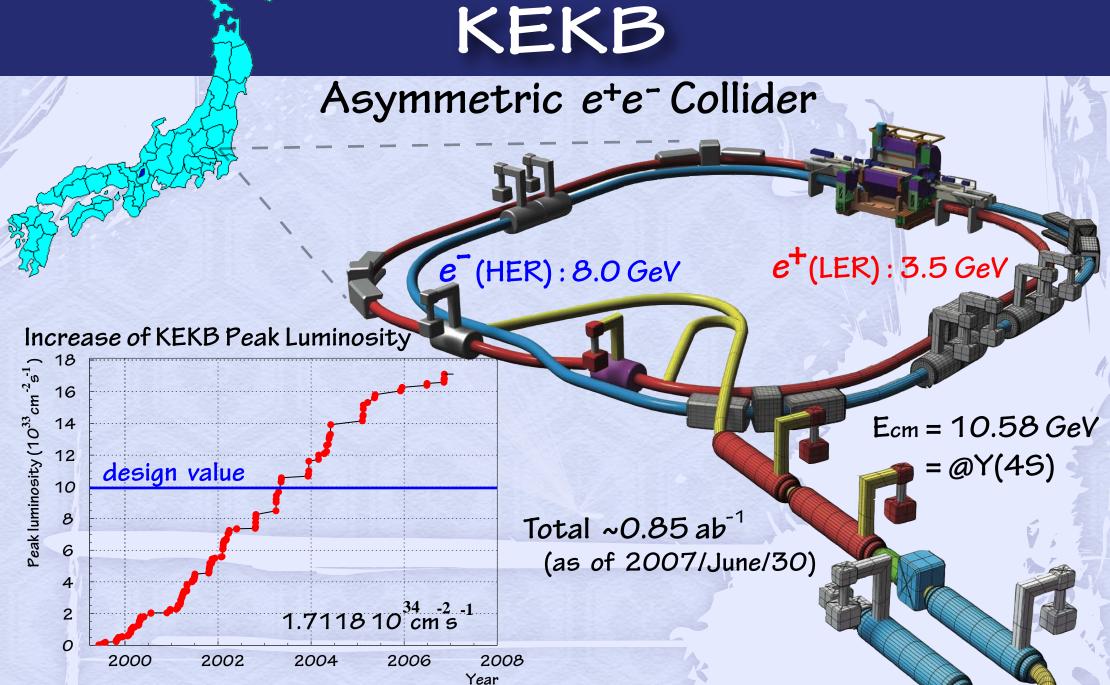

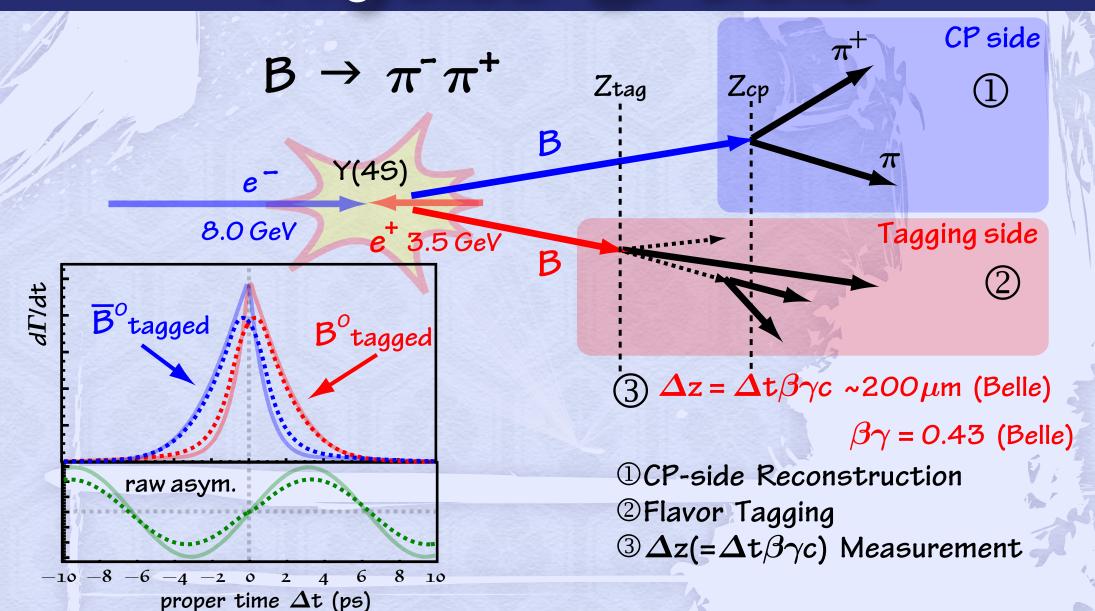

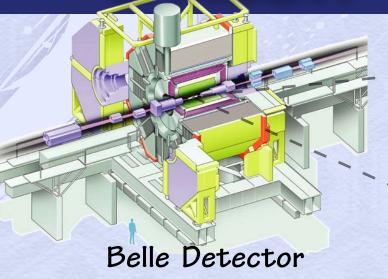

#### Physics @ Belle

#### Silicon Vertex Detector

over 20 institutes

~ 100 members

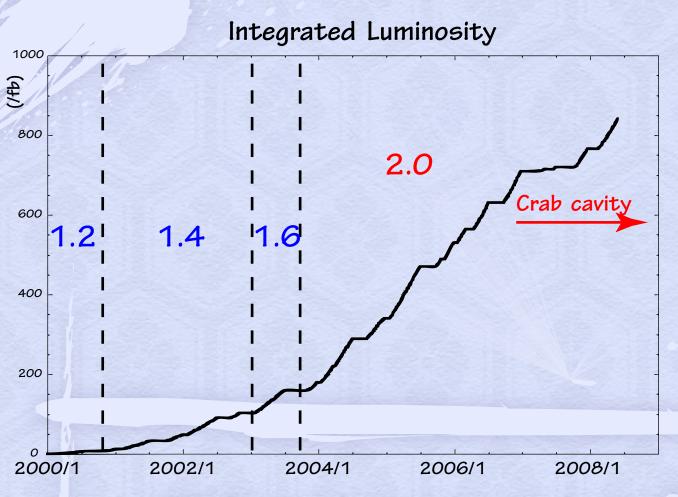

### SVD History

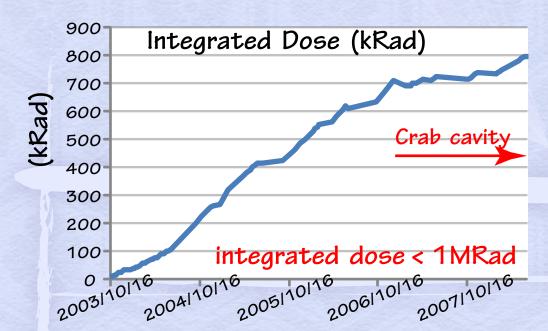

SVD1.0: VA w/  $1.2\mu m$  process (up to  $200 \, kRad$ ) demaged by soft X-rays

SVD1.2: a gold foil was wrapped on the beam pipe to stop X-rays

SVD1.4: VA w/  $0.8\mu m$  process (up to 1MRad)

SVD1.6: degraded ladders were replaced

SVD2.0: VA w/ 0.35 $\mu$ m process (up to 20MRad)

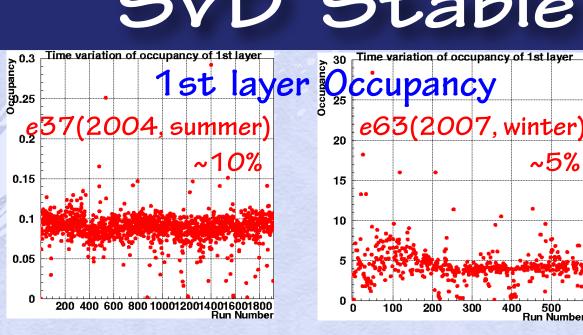

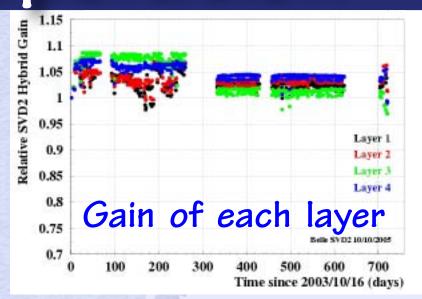

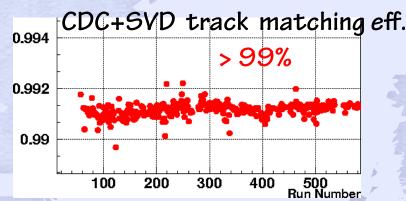

#### SVD Stable Operation

Belle operation will continue! 2009 fiscal year: ~5 months

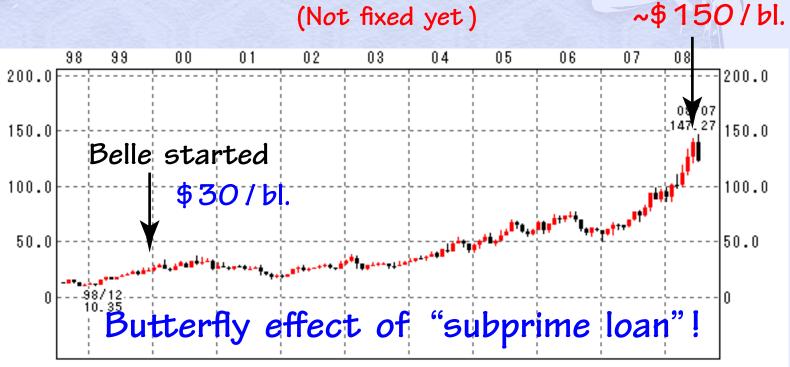

(Not fixed yet)

#### Price of crude oil

Belle operation will continue!

2009 fiscal year: ~5 months

(Not fixed yet)

Running cost is getting higher and higher these days!!

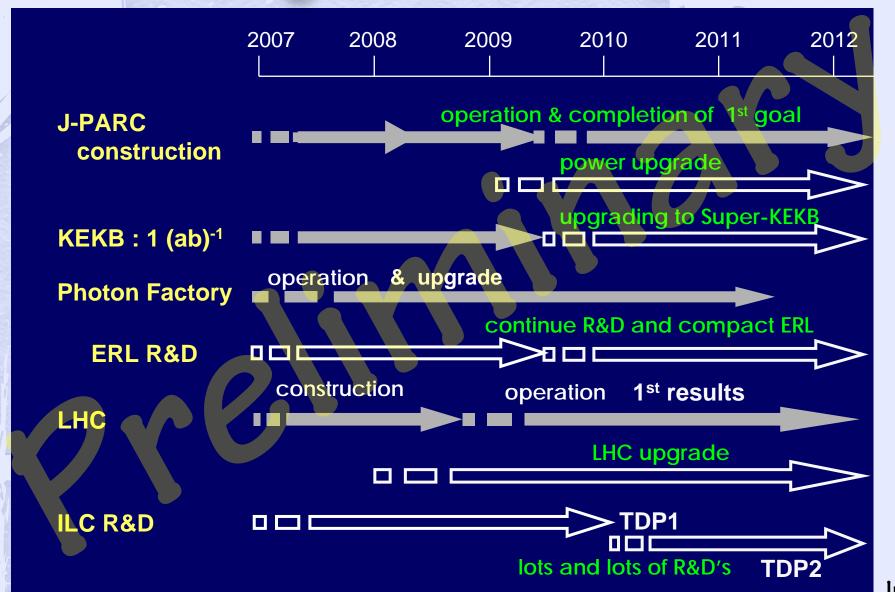

## Summary of KEK Roadmap

A.Suzuki July,4,2008

## Upgrade Strategy

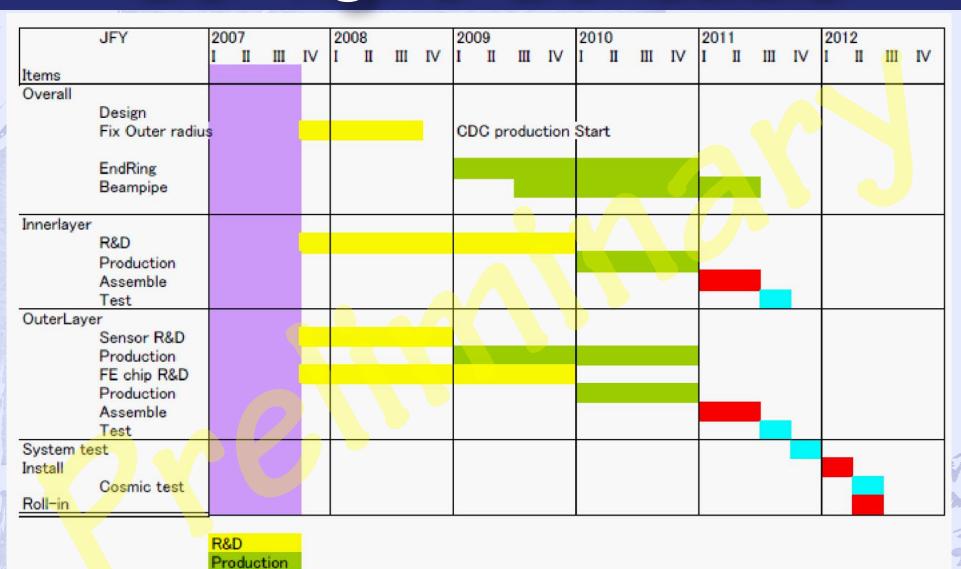

For commencement of operation on 2012, schedule is so tight!

We decided to upgrade the detector in two steps

| Baseline design                                                                                        | Lol design                                                                                                        |  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| From the beginning up to $2 \times 10^{35} \text{ cm}^2 \text{ s}^{-1}$ (~2014?)  (For Initial target) | after a few years operation $\sim 8 \times 10^{35} \text{ cm}^{-2} \text{ s}^{-1}$ (to the end?) (For Final goal) |  |

| 6-layer strip-type                                                                                     | 2-layer pixel-type<br>+ 4-layer strip-type                                                                        |  |

| 1.5 cm radius beam pipe                                                                                | 1.0 cm radius beam pipe                                                                                           |  |

## Requirement for "Baseline"

(1.5cm radius beam pipe + 6-layer SVD)

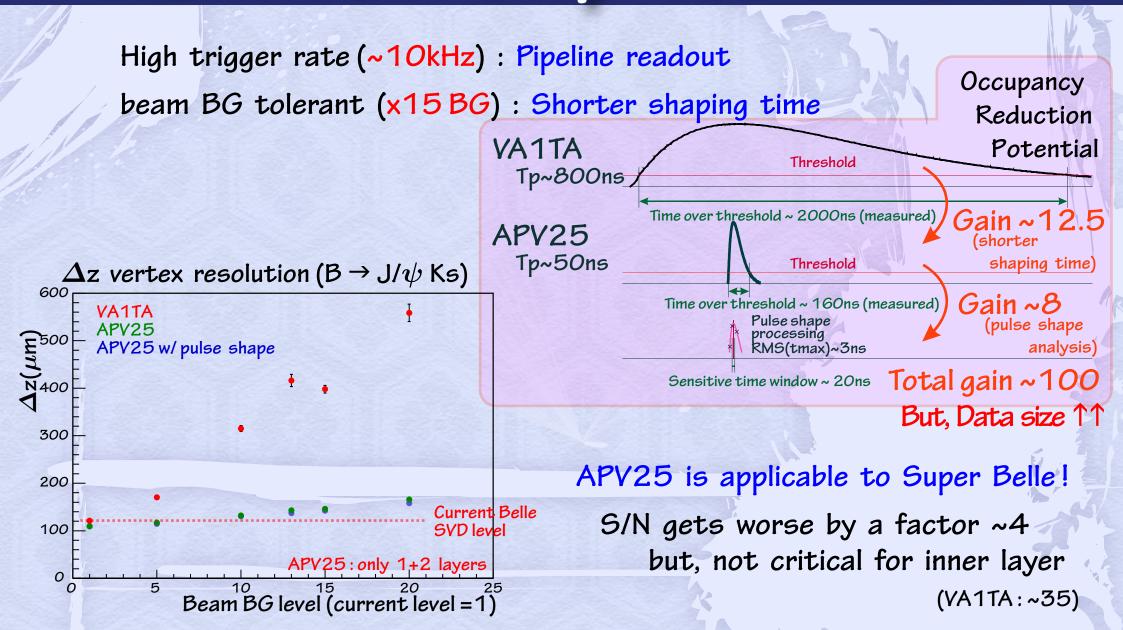

#### For trigger rate

.~10kHz (c.f. ~400Hz @ Belle)

#### For inner layers

. better vertex resolution (at least, SVD2 performance should be kept) SVD2 Occupancy(%)

$\sigma \Delta z < 100 \, \mu m$

. beam BG tolerant

x 15 BG is expected

$@2 \times 10^{35} \text{ cm}^{-2} \text{ s}^{-1}$

|      | L1 | L2 | L3 | L4 |

|------|----|----|----|----|

| SVD2 | 10 | 3  | 1  | 1  |

VA1TA(Tp=800nsec)

#### For outer layers

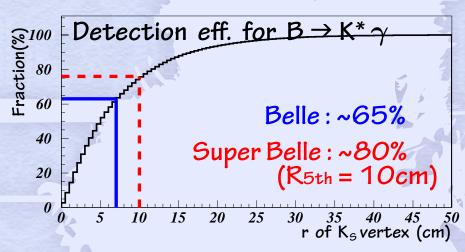

- . better detection eff. for B  $\rightarrow$  K\*  $\gamma$

- .S/N ratio

- . Readout pitch

- . Material thickness

- . Slanted sensors

## Readout Chip for inners

#### Inner Layers

```

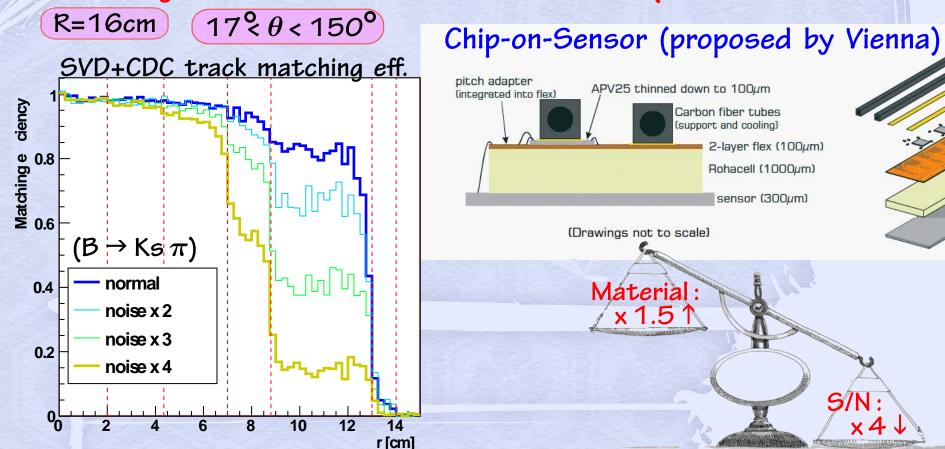

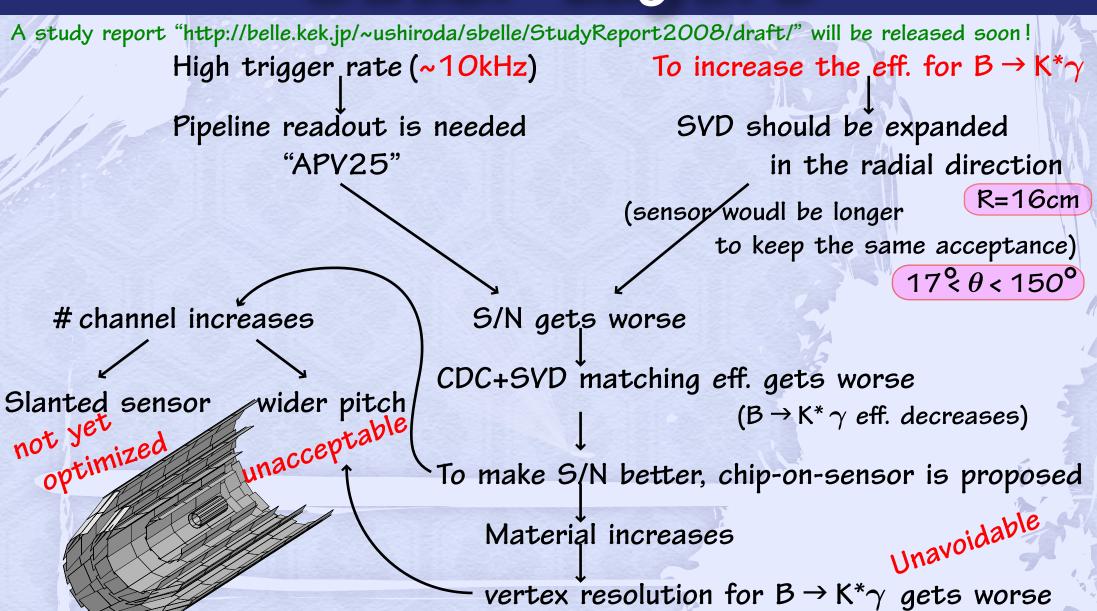

A study report "http://belle.kek.jp/~ushiroda/sbelle/StudyReport2008/draft/" will be released soon!

High trigger rate (~10kHz)

To achieve better vertex resolution

\sigma \Delta z < \sim 100 \, \mu m

Innermost layer should be located

as close to the beam pipe as possible

Innermost layer should be operable

under harsh beam background

(x15 higher BG than Belle)

Shorter shaping time

Pipeline readout

VA1 → APV25 equivalent chip, S/N gets worse

~10% Occ. (inner)

~35 (inner), ~16 (outer)

for Belle VA1

for Belle VA1

APV25 : ~4times worse

```

but DSSD + APV25 can be used

$VA1 \rightarrow APV25$  is the key

## Readout Chip for outers

High trigger rate (~10kHz): Pipeline readout → APV25

beam BG tolerant: Shorter shaping time is preferred, but not critical

longer sensor + APV25 → worse S/N (VA1TA ~16 for outer layer)

#### Outer Layers

#### Hurdles we face

. DSSD sensors from HPK (Hamamatsu)

HPK stopped the DSSD production!

- . Micron  $\rightarrow$  Several samples in hands.

- . Kyungpook  $\rightarrow$  DC coupled DSSD was produced.

Test in progress.

. Tata  $\rightarrow$  Waiting for the first test production.

Double-sided, double-metal and AC-coupled sensor

- . Other vendors... Canberra, SINTEF?

- .# of readout chips will be >10 times larger than SVD2

Space for cables, repeaters and backend electronics. Larger power supply, cooling system.

. Chip-on-sensor

leakage of coolant, system test, ...

#### Milestones

#### 2008

#### Demonstrate APV25 readout chain

- . Design optimization (Osaka, Niigata)

- . APV25 front-end, repeater and FADC (Vienna)

- . Data acquisition board: COPPER/FINNESE (Cracow)

DSSD test production

2009

Fix the design of Silicon Vertex Detector

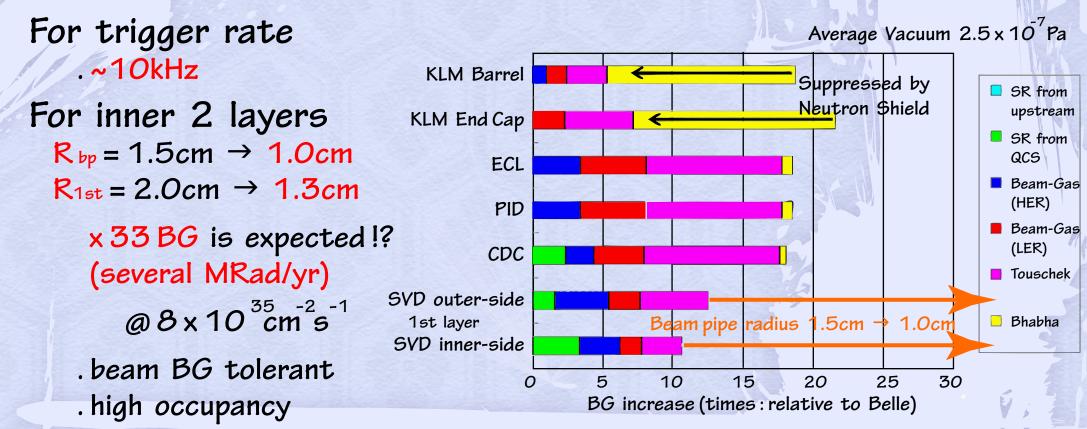

## Requirement for "Lol" design

(1.0cm radius beam pipe + 2-layer PXD + 4-layer SVD)

DSSD can not survive anymore! → pixel-type

For outer 4 layers

DSSD w/ APV25 can still survive.

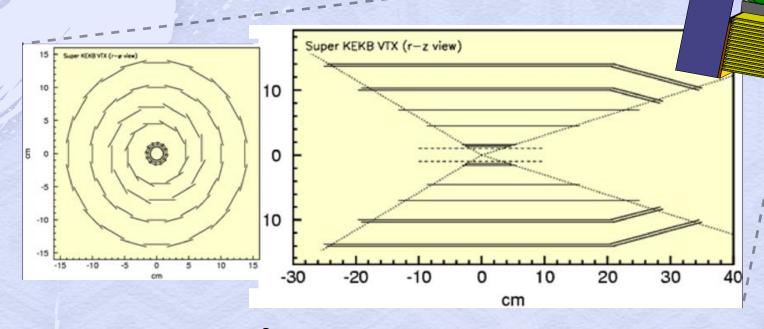

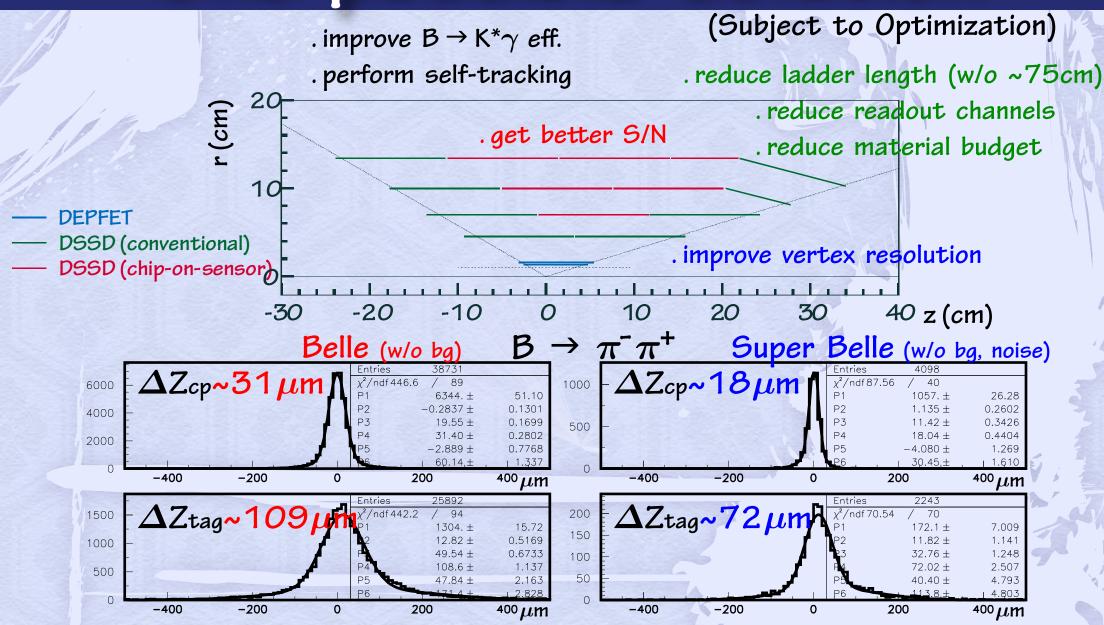

#### Tentative "Lol"

Super Belle detector

likewise as Baseline

- . Acceptance:  $17^{\circ} < \theta < 150^{\circ}$

- . Radius (for better vertex resolution)

- . Beam pipe = 10 mm

- . Innermost = 13 mm

- .Outermost = 150 mm

- . 6-layer (2-lyr pixel + 4-lyr DSSD)

- . Inclined sensors in Layer5 and 6

- . reduce readout channels

- . reduce material budget

- . reduce ladder length (w/o ~75cm)

- . Technology options

DEPFET / CMOS / SOI

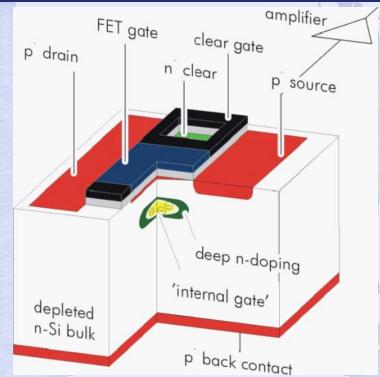

#### DEPFET

- Intense R&D has been done for ILC pixel sensors has been used in several experiments already!

- . Technology is available in MPI only

- . Sensor size is limited by wafer size  $50~\mu\text{m} \times 75~\mu\text{m}: 215 \times 512~\text{pixel (adjustable)}$  almost no gap in the acceptance

- . Not very rad-hard (tested up to 1Mrad)

OK up to 8Mrad??

- . Small power consumption

- . Reset switcher chip: Voltage swing > 8V

- . Thickness  $20\mu \text{m} \sim 100\mu \text{m}$  (adjustable for experiments)

- . Doubly-correlated sampling can be done → low noise

- . 10kHz trigger rate, O-suppression, ~4pixels/hit, 32 bits/pixel includiing address

Disadvantage: ~1% inefficiency

Data processing is done in subsequent chips on repeater system or in backend system

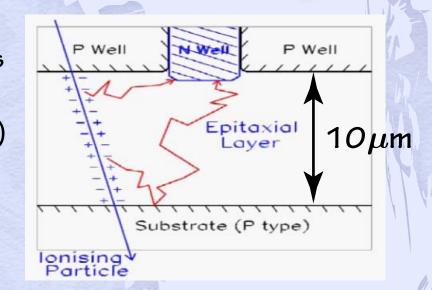

## CMOS pixel (CAPS/MAPS)

- The same technology as commercial CMOS cameras 5-10M -pixel chips are in production

- . Sensor size is limited by reticle size (21 x 21 mm²)

22.5  $\mu$ m x 22.5  $\mu$ m

gap in the acceptance

- . Intrinsic rad-hard (deep sub-micron technology) > 30 MRad

- . Sensor is a thin epitaxial layer (5~10  $\mu$ m thick) signal si small  $\rightarrow$  No problem as the detector capacitance is also small <code><=50  $\mu$ m</code>

- . N-well is used to collect charge from the epitaxial layer

- . 100kHz frame rate is achieved (132 x 48 pixel)

Full-size detector (928 x 128 pixel)

10kHz trigger rate ???

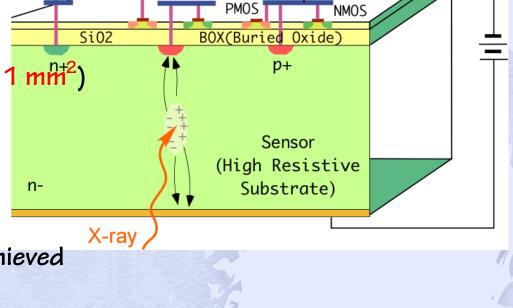

#### SOI

. Activity started as one of KEK detector R&D project in 2005

Sensor size is limited by reticle size  $(21 \times 21 \text{ mm}^2)$

$20\mu \text{m} \times 20\mu \text{m} : 128 \times 128$

gap in the acceptance

. rad-hard (deep 0.2  $\mu$ m technology)

tested > 30 MRad

. Depletion depth of 50-100  $\mu m$  has been achieved thinning after silicon process

$<=50\mu m$

. Signal induced in the sensor can be processed by the CMOS circuit Complex/rad-hard circuit can be made

DEPFET/CAP type readoout is also possible

10kHz trigger rate???

. R&D in progress

Evaluation of Belle PIXEL chip will start soon (pixel-shaper-discrimination-digital pipeline)

## Technology options

|                            | DEPFET                                                       | CMOS (CAPS/MAPS)                                              | 501                                                             |

|----------------------------|--------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------|

| Material budget            | 20 ~ 100μm<br>(adjustable)                                   | <- $50\mu \mathrm{m}$ (sensitive area 5~ $10\mu \mathrm{m}$ ) | $50 \sim 100 \mu \text{m}$ (could be $< \sim 50 \mu \text{m}$ ) |

| Size                       | limited by wafer<br>(50 x 75 mm²)                            | limited by reticle<br>(21 x 21 mm²)                           | limited by reticle<br>(21 x 21 mm <sup>2</sup> )                |

| Power consumption          | small (0.5w)<br>(reset switcher chip:<br>Voltage swing > 8V) | small                                                         | small                                                           |

| Radhardness<br>(3MRad/yr?) | tested < 1MRad<br>(up to 8MRad?:<br>irradiation test)        | intrinsic rad. hard<br>(must be > 30MRad)                     | tested > 30MRad                                                 |

| 10kHz<br>trig. rate        | estimated<br>~1% ineff.                                      | ?<br>(CAP3 too slow)                                          | not proved                                                      |

| Availability               | MPI only<br>(already used<br>in other exp.)                  | R&D in progress                                               | R&D in progress                                                 |

#### One possible solution

Assemble et

Test

#### So Tight Schedule

#### Summary

#### For current SVD in Belle

```

. operated stably and efficienctly for almost ~5 years

```

. will continue in the next fiscal year (2009: ~5 months: not fixed yet)

For "Baseline" design (for 2 x 10 5 cm 2 s peak lum.: 2012 ~)

- . optimization is still going on.

- . high trigger rate (~10kHz)

- beam BG tolerant (x 15 BG is expected)  $\rightarrow$  APV25 can keep a SVD2-equivalent vertex resolution ( $\sigma_{\Delta z}$  < 100  $\mu$ m)

- . better detection eff. for B  $\rightarrow$  K\*  $\gamma$   $\rightarrow$  realize a larger volume detector w/ chip-on-sensor for outer layers

- . many hurdles, e.x. DSSD production, system test, tight schedule...

#### For "Lol" design (for 8 x 10 55 cm 5 peak lum.: 2014 ~)

- . concrete optimization has just started. (esp., for two inner layers)

- . we have to determine which technology option we can use in real!

- . again many hurdles, e.x. system test, tight schedule ...

## T echnology and nstrumentation in

Particle

P hysics

The 1st International Conference on Technology and Instrumentation in Particle Physics

March 12-17, 2009 Tsukuba, Japan http://tipp09.kek.jp

- Topics -

Gaseous/liquid detectors

Semi-conductor detectors

Trigger &

data aquisition systems

Accelerator

and beam instrumentation

Experimental detector system

Calorimeters

Particle identification

and photon detectors

Instruments

for non-accelerator physics

Astrophysics

and space instrumentation Front-end electronics