# LAPP BPM Read-out electronics in CTF3

Jean Jacquemier, Yannis Karyotakis, Jean-Marc Nappa, Pierre Poulier, Jean Tassan, Sébastien Vilalte.

WS CLIC 14-17/10/2008

Conseil Généra

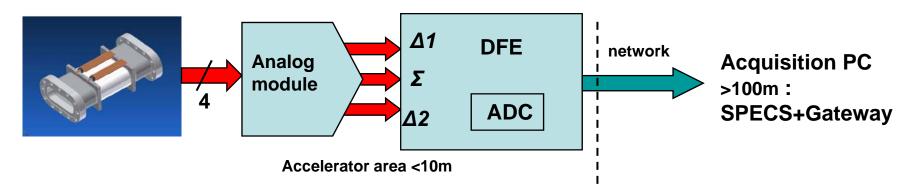

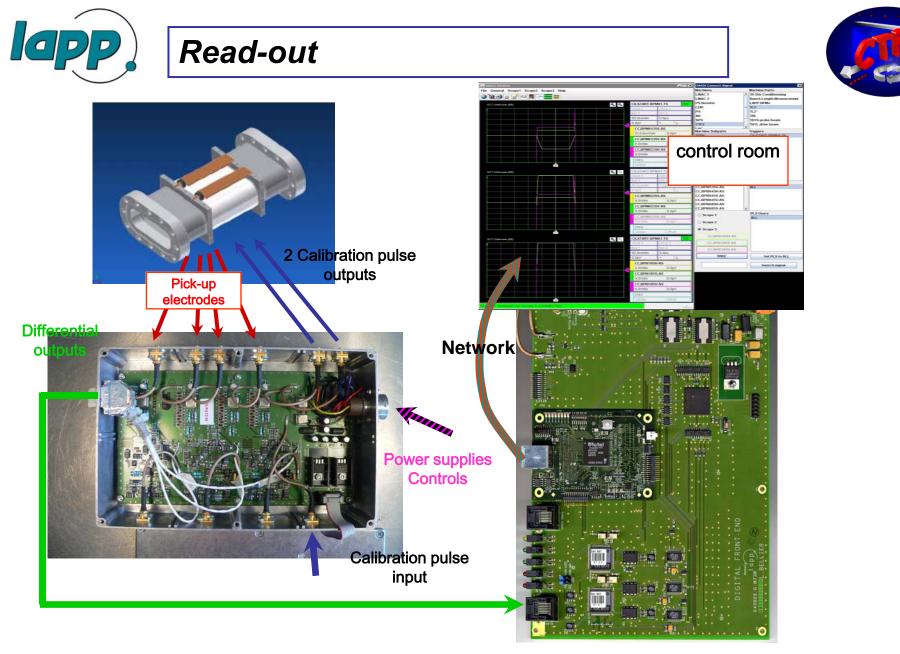

<u>Aim:</u> reduction of costs of long analog cables/ADC  $\rightarrow$  Rad-hard acquisition electronics close to beam.

Analog module: Intensity & deviations processing BPI or BPM.

**DFE board:** - digitalization **3channels**, **12 bits / 200MSps**.

- Feed-back for analog modules: gains, calibration and attenuations.

- Daisy chain acquisition: 1 network cable per crate.

**Acquisition PC :** FESA-OASIS soft and specialist requirements feed-back.

$\rightarrow$  Cost divided by a factor 3 comparing to a « far » acquisition.

Sébastien VILALTE

## LAPP in CTF3

<u>September 2005</u>: creation of the CTF3 group in LAPP  $\rightarrow$  R&D.

**February 2006**: analog + digital front-end solution proposed (Annecy bpm WS).

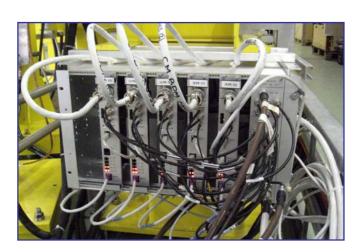

*From November 2006 to summer 2008*: production and installation of 47 analog modules and 31 DFE boards in 8 crates in TL2 and CLEX.

$\rightarrow$  All combination BPM&BPI pick-ups – Lapp&CERN analog modules for the local acquisition.

<u>Man power:</u> ~2,5men/year full time since september 2005  $\rightarrow$  analog, digital electronics and software, one of whom funded by « Conseil général Haute Savoie ».

<u>IN2P3 funding:</u> ~100k€ from Sept. 2005 to end 2007.

Still ~15 DFE to install for the BPS acquisition (2009): details to be discussed.

Uranus

16/10/2008

Sébastien VILALTE

#### File General Scope1 Scope2 Scope3 Help × 🅥 🔌 👩 💉 💉 pls 🎮 💳 🧱 $\boxtimes$ Scope1 CX.START-BPM01-TS SCT: (0) A C -200.000 mV -Trig level 50 0ns/div 0.0ps Machines Machine Parts CM.BPM0330S-AS 30 GHz Conditionning 300 0mA(div 0 OnA LINAC 3 Bunch Length Measuremen PS Booster TL2 LEIR TL2 PS TBL AD TBTS probe beam SPS TBTS drive beam LHC CALIFES CTF3 Machine Subparts Triggers CX.START-BPM01-TS e, SCT: (0) RDM CM.BPM0330H-AS Signals 300.0um/div 0.0pm CM.BPM0330H-AS CM.BPM0330S-AS CM.BPM0330V-AS CM.BPM0370H-AS CM.BPM0370S-AS PLS Machines CM.BPM0370V-AS ALL CM.BPM0510S-AS M.BPM0510H-AS CM.BPM0510V-AS SCT:(0) . CM.BPM0550S.AS CM.BPM0550H-AS PLS Users Scope ALL Scope 2 CM.BPM0330V-AS Scope 3 300.0um/div 0.0pr CM.BPM0330V-AS FREE FREE FREE FREE Set PLS to ALL Search signal 16:15:34 - Vchannel 1 in Vscope 3: CONNECTED

#### Debug during summer 2008:

Results

several problems on sampling electronics and transmissions currently solved by soft.

Jitter solved by a trigger, sampling memory still to be calibrated.

Thanks to operation team feedback and patience!

#### Sébastien VILALTE

The logical evolution of this system is to be dedicated to a larger accelerator as CLIC:

#### <u>Rare acces from surface, high number of channels, rad-hard,</u> <u>low-cost, low consumption</u>...

Most important points to develop: elimination of cables

- **<u>Power supplies:</u>** autonomous (220V sector, DC-DC converters...).

- <u>Local calibration</u>.

- <u>**Network :**</u> flexible data collection, repetition crates...

- <u>Acquisition architecture:</u> faster ADC, direct bpm read-out, continuous sampling...

- **<u>FPGA processing:</u>** raw data, processed data...

- <u>Radiations.</u>

$\rightarrow$  <u>All-around accelerator standard acquisition</u>.

A lot of specifications to be discussed with the collaboration:

- Input stages and input dynamic ranges.

Informations to collect: definition of transfer rates.

→ possible switching between FPGA local process of position/intensity and raw data for precision.

- Definition of a standard crate for a module (n channels)

- Infrastructure possibilities to study (see Lars concrete shielded crate...)

- ETC...

LAPP decided to get involved for a 2 years development: ~3 men/year and IN2P3 funding ~50k€/year.

### New acquisition board:

- 4 analog inputs with several input dynamic ranges, continuous 500Msps-12bits sampling.

- 6GHz optical link for data, timing: no more cables, no EMC problems...

- A Clock-management architecture to get free from timing problems.

## **Board for local power supplies/calibrations facility:**

study of a 220V sector power supplied crate & local calibration.

$\rightarrow$  Problem of radiations!

- Development about 1 year from September 2008: architecture and critical components chosen (ADC, timing, transmission).

- The two boards will be compatible with the existing crates to be tested and debugged in the CTF3 (6 months more) with no interference with the actual system.

- The optical reception board (PCI) already existing.

- Radiation tests foreseen.

- Remarks and ideas are welcome...

With the development of a multiplexer collection board, it could replace the current CTF3 acquisition ...