#### CERNopenlab

#### Research topics:

Silicon photonics systems

Next generation data

High speed configurable logic

Computing solutions for high performance data filtering

#### ICE-DIP 2013-2017: The Intel-CERN European Doctorate Industrial Program

A public-private partnership to research solutions for next generation data acquisition networks, offering research training to five Early Stage Researchers in ICT

13/04/2015 2 Background image: Shutterstock

# The Grand Challenge for proposed upgrade of LHCb experiment

- 500 Data sources each generating data at 100 Gbps

- > Requires FPGAs for

- **DAQ modules**

- Adaptive, high performance

- Low Level Trigger decisions

- Algorithm acceleration

- FPGAs are great

- High Performance

- Flexibility Build anything

- But...

# **FPGA** pains

#### **Programmability, Programmability, Programmability**

- Using Hardware Description Languages (HDLs)

- At Register transfer level (RTL) abstraction

- Create Custom Memory Hierarchies

- Manage Communication with PC

- Create PC side SW that plays nice with all this

**CERN** openlab

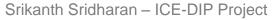

# **OpenCL for FPGA**

An unified programming model for accelerating algorithms on heterogeneous systems

- C based programming language

- System level design (Host CPU+FPGA)

- Memory Hierarchy auto generated

- Host CPU-FPGA communication abstracted away

- Potential to integrate existing VHDL/Verilog IP

**CERN** openlab

# **OpenCL for FPGA**

# read\_data\_from\_file( ... ); maninpulate\_data( ... );

clEnqueue WriteBuffer ( ... ); clEnqueue Task( ..., my\_kernel, ...); clEnqueueReadBuffer ( ... );

display\_result\_to\_user( ... );

## End to end DAQ + Acceleration system with 'OpenCL for FPGA' ?

#### **OpenCL spec targets**

- Algorithm Acceleration

- Not FPGA design

- But, How about 'OpenCL for FPGA'

- More than Acceleration?

- A DAQ system with OpenCL?

- Only one way to find out

- Go ahead and implement one

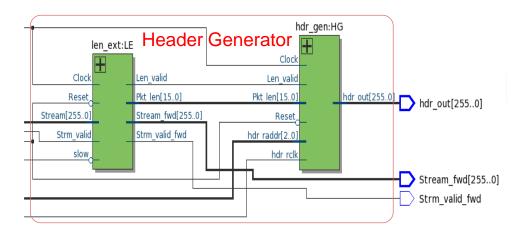

#### An existing FPGA DAQ system

|        | Requirement                                | OpenCL Std spec                | Altera OpenCL extension                                   |

|--------|--------------------------------------------|--------------------------------|-----------------------------------------------------------|

| < ø /  | IO, moving data between kernels            | X<br>Pipes in v2.0             | Channels (IO -> Kernel,<br>Kernel -> Kernel, Kernel ->IO) |

| -      | Bit level manipulation, non std data width | X                              | Bitfields &<br>Other mechanism                            |

|        | Control signals                            | Х                              | Х                                                         |

| $\geq$ | Maynooth                                   | Srikanth Sridharan – ICE-DIP F | Project 13/04/2015                                        |

**CERN** openlab

Srikanth Sridharan – ICE-DIP Project

13/04/2015 8 Background image: Shutterstock

# **OpenCL Algorithm Acceleration**

# > Hough Transform

- Used for particle track reconstruction in LHCb for the future VertexDetector

- Find tracks from the Hit data of the detector

- Exisiting OpenCL GPU code ported to FPGA

Erratum: on this slide a comparison measurement was shown which is erroneous and has been retracted. We will show a corrected measurement in the paper.

First Name and Family Name – ICE-DIP Project

# Conclusions

### **FPGAs** have always been capable devices

- Performance, Versatility, Flexibility

- But so have been limited by the usability

- Separate and HW oriented programming model

## **OpenCL is a game changer**

- Unlocking the potential of FPGAs much easier

- Sure, there are some road blocks

- But future of OpenCL for FPGA is definitely bright

**CERN** openlab

## **Thank You!**