# Introduction to analog integrated circuit design: from schematic to layout

Patrick Pittet, Francis Calmon, Laurent Quiquerez, Rémy Cellier

2nd International Summer School on INtelligent Signal Processing for FrontlEr Research and Industry

July 14th-25th, 2014, Paris Diderot University, Paris

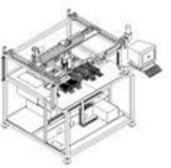

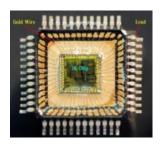

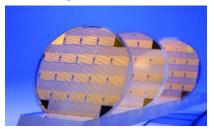

# Level 0: IC chip (die)

Level 1: Packaged chip

Level 2: Printed circuit board

Level 3: Card-on-board (backplane)

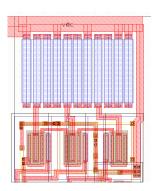

This lab is focused on the methodology and design flow for the design of CMOS analog integrated circuits (Full custom design).

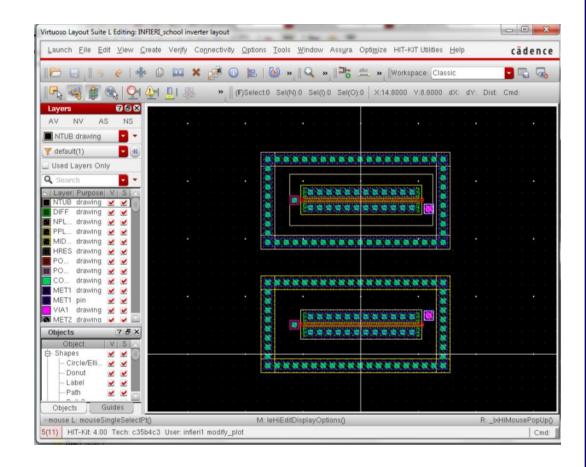

Layout

Packaged IC

This class implements Cadence CAD-Tools.

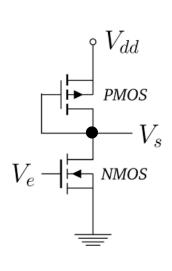

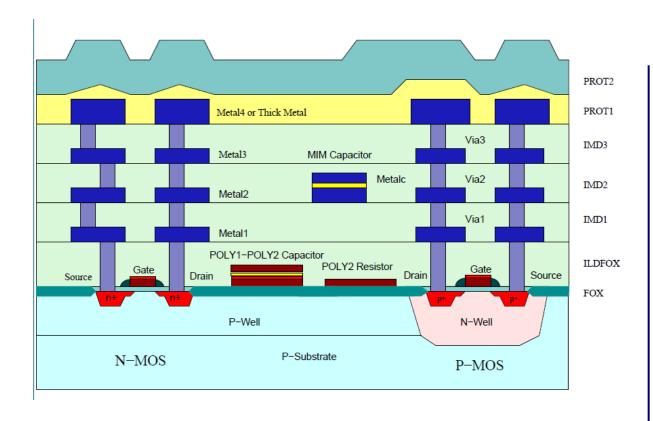

# Analog cell and CMOS technology

Analog cell (inverter)

Austriamicrosystems (AMS) 0.35 µm CMOS

(http://cmp.imag.fr/aboutus/slides/slides2007/03\_KT\_AMS.pdf)

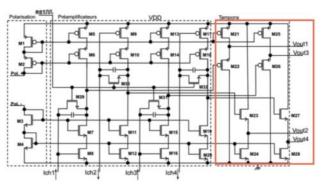

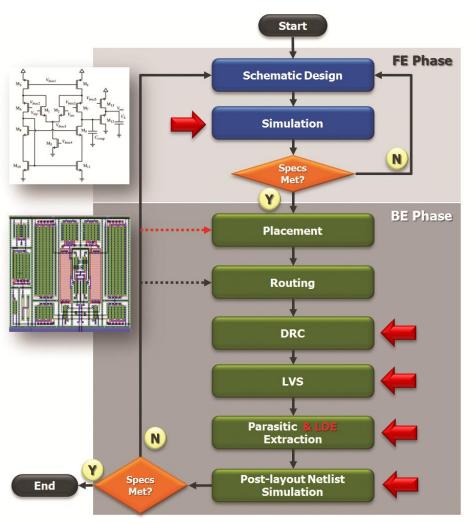

# IC design flows

### Schematic:

- Basics design computations

- Parametric study based on static, transient, small signal simulations and noise analysis

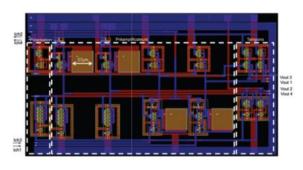

## Layout:

- Design Rule check

- Layout versus Schematic verification

- Parasitic components extraction

- Post-layout simulation

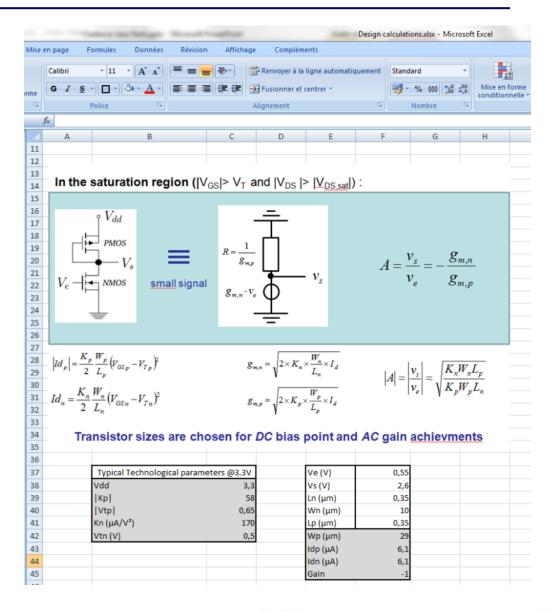

# Design calculations

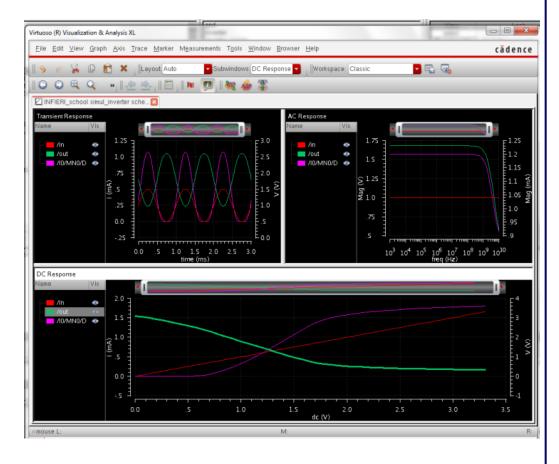

# **Simulations**

# Layout

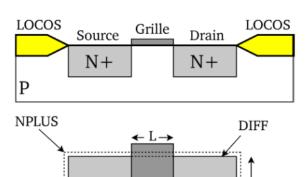

(a) Transistor NMOS

Grille

Source

W

Drain

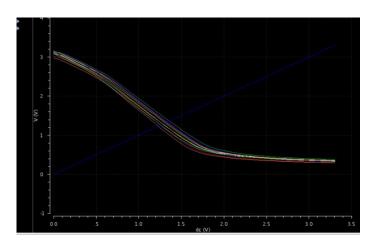

# **Process and Mismatch simulations**

Wafer production will always show some variation of technological parameter

Mismatch on design parameters components

=> Monte-Carlo Process and Mismatch simulations will be run