# Results of a prototype imaging system using the FGLD technology and self-triggering discharge-protected readout electronics

## Louis Dick,<sup>a</sup> Nail Malakhov,<sup>a</sup> Rui de Oliveira,<sup>a</sup> David Watts<sup>b</sup>

#### FGLD TECHNOLOGY

Produced using standard PCB maunfacturing techniques and patented by CERN, this detector combines a 3axis readout and gas amplification in a single flexible polyimide foil of only 100um thickness.

<sup>b</sup> <sup>a</sup> C.E.R.N., Geneva, Switzerland <sup>b</sup> Universitat Autónoma de Barcelona, Spain

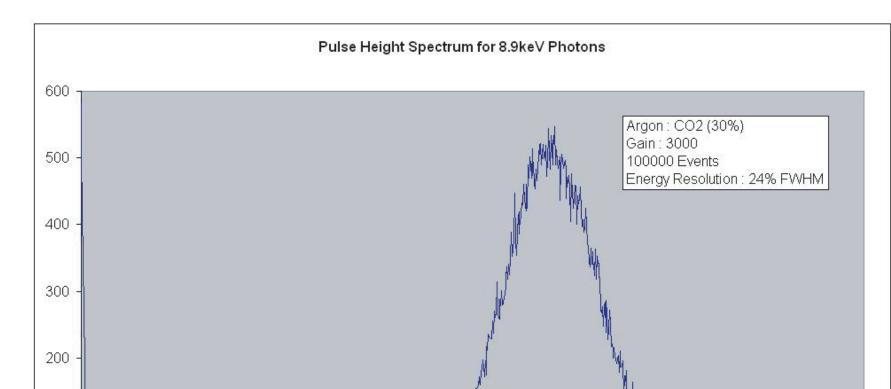

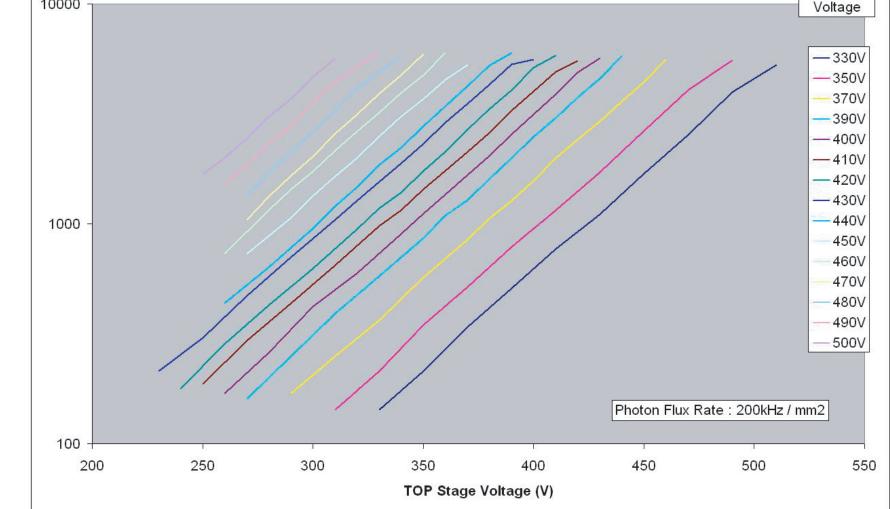

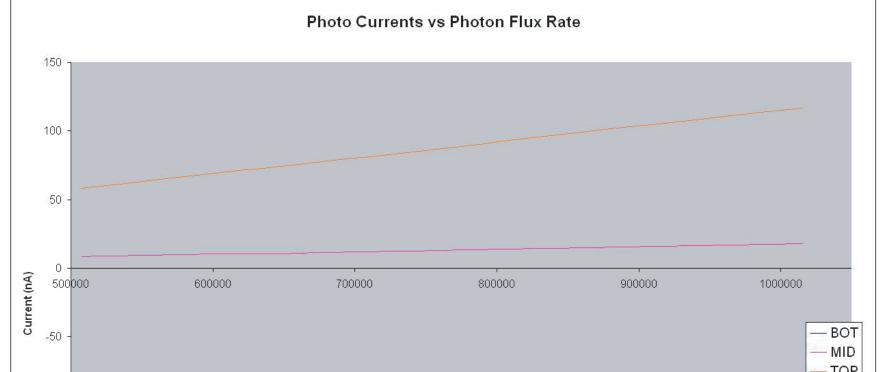

#### DETECTOR PERFORMANCE

BOT Stage

#### Features:

- very low capacitance due to the crossing configuration of strips

- 150um pitch strip-to-strip

- 100um single flexible polyimide foil

- 3-axis readout for reducing highrate ambiguities

- up to 6000 gas gain in Ar:CO2(15%)

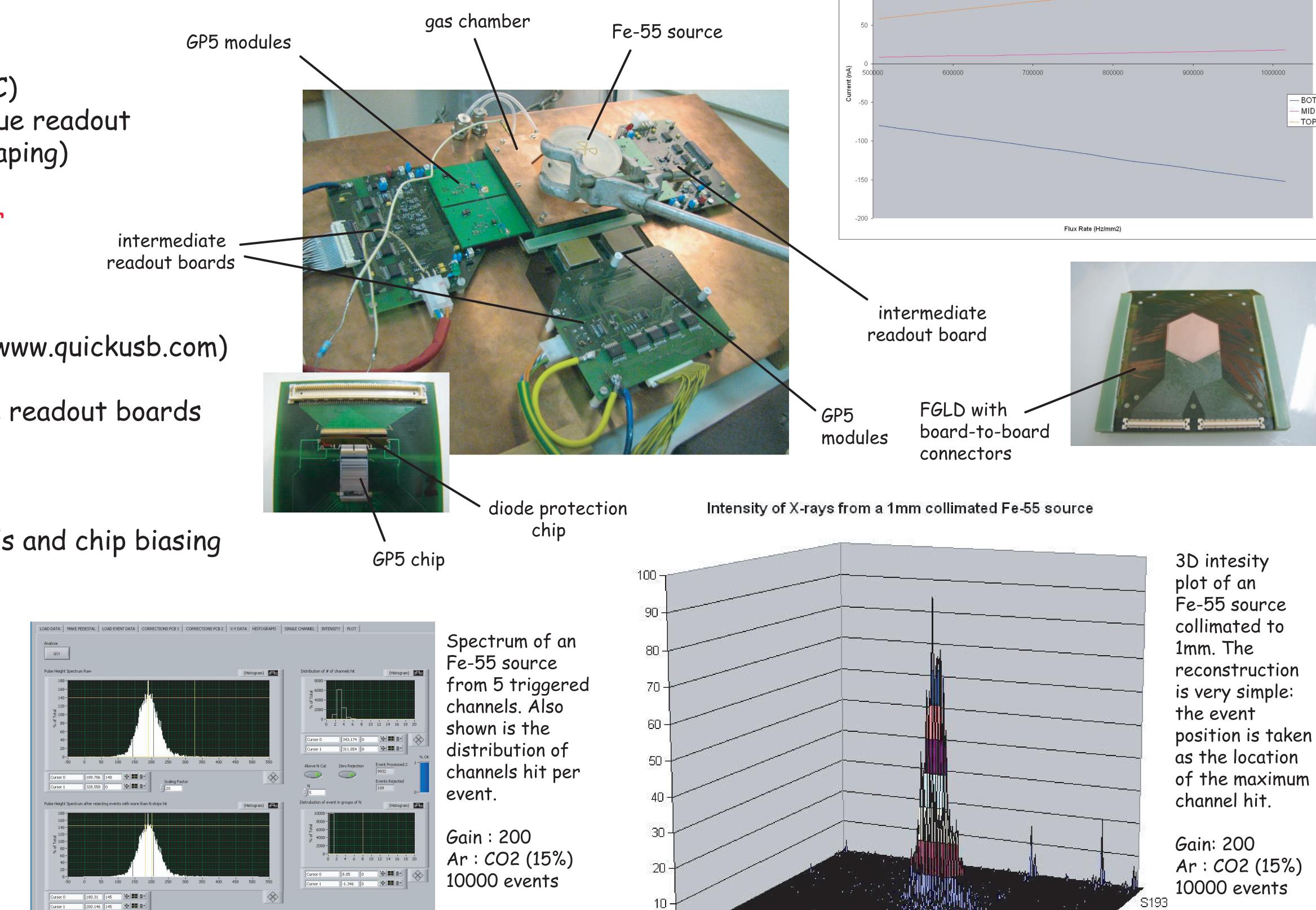

#### PROTOTYPE IMAGING SYSTEM

Comprises of 3 intermediate boards each with 2 GP5 chips, ADCs, and HV decoupling digital readout connected to a central DAQ for 3-axis coincidental data-taking and communication by USB 2.0 to a PC. Labview is presently used for the aquisition and analysis software.

attention of the stand and the stand of the stand of the

#### GP5

- 128-channel charge preamp

- high dynamic range (up to 3pC)

- 250ns shaping time on analogue readout - self-triggering (40ns fast shaping)

Diode Protection / Pitch Adaptor

- built for TOTEM-GEMs

#### Test-DAQ

- based on QuickUSB module (www.guickusb.com)

- Altera FPGA

- controls up to 3 intermediate readout boards

#### Intermediate Readout Board

- 2 channel 16-bit ADCs

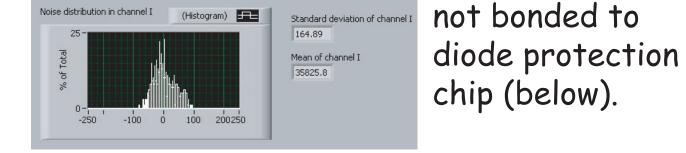

SYSTEM PERFORMANCE

Standard deviation of chan

273.746

Mean of channel 3

- 8 DACs for trigger thresholds and chip biasing

Noise spectrum

of 1000 events

detector (above)

on a channel

connected to

and a channel

### S145 S97 S49

#### SUMMARY

The following conclusions can be made regarding the prototype imaging system:

- 1. GP5 chips with diode protection is working well during discharge and no channels are destroyed.

- 2. GP5 threshold is working well for 6keV from Fe-55 with detector operating at low gain of 200 (trigger noise < 7fC). 3. With current board-to-board connection from electronics to detector, additional noise from detector is not significant. Majority of noise in system is coming from diode protection chip and fan-out to connector.

#### FUTURE DEVELOPMENTS

- 1. Build a 10x10cm FGLD detector in which all the electronic readout components are "hidden" behind the gas chamber.

- 2. Simplified software for high-rate data taking and fast position reconstruction algorhythm.

- UAB iversitat Autònom de Barcelona CERN

- 3. Peak recognition made directly "onboard" the intermediate board in a separate FPGA.