# An application of the DRS4 chip : the ASM Board

Fast Timing Workshop

Thursday, March 13th ELECTRONICS AND READOUT SESSION

<u>Magne Magali</u>

0

magne@clermont.in2p3.fr LPC Clermont-Ferrand

## Outlines

- Context

- ASM technical functionality

- Return of experiment

- Conclusion & Perspectives

Experiment system

Magne Magali LPC Clermont

## Context

- This board is a requirement of the team AVIRM of my Lab for the Project DPGA (Pixelized detector with a large acceptance)

- Have news sampling boards with higher performances than the ARS16 boards developed at the Laboratory and based on ARS0 chip.

- Electronic development begin in September 2011).

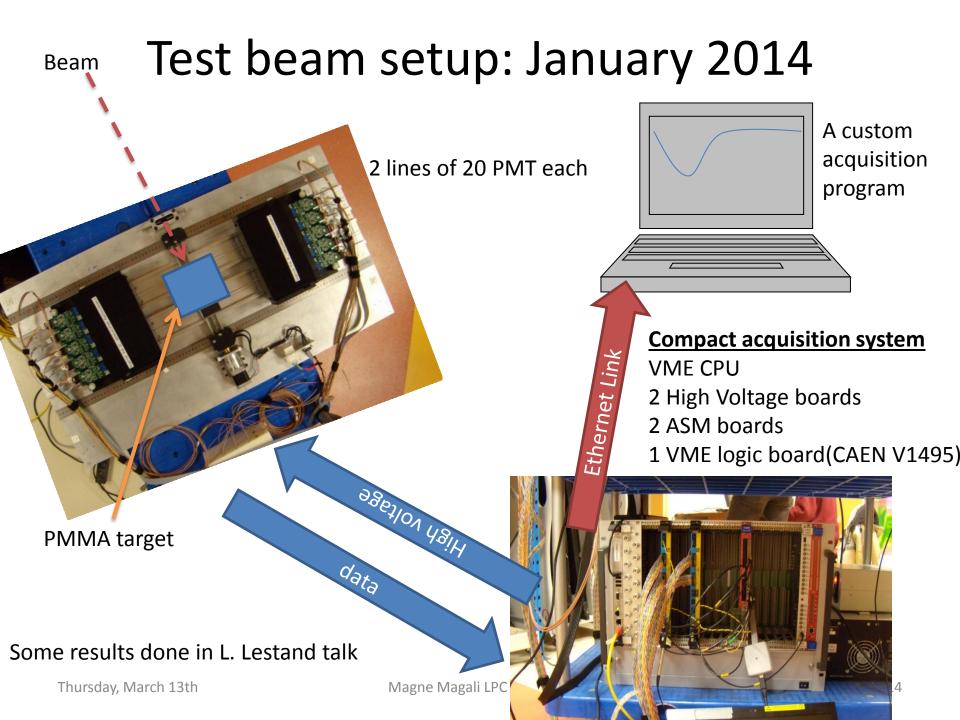

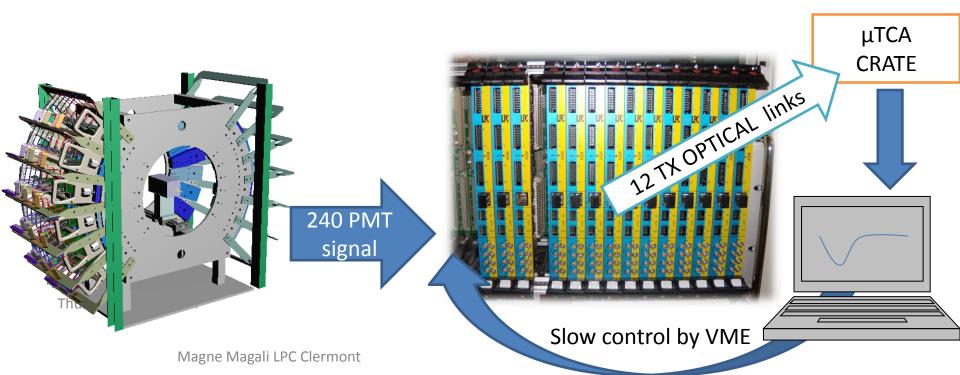

- Detector with 240 PMT sensors

- The goal is to have a good timing resolution with a fast sampling frequency.

- 11). DPGA O.33m 1m 1m

- The choice of the DRS4 is the good compromise between sampling frequency, acquisition windows and dead time.

## Requirements

#### Signal to be acquire by the board:

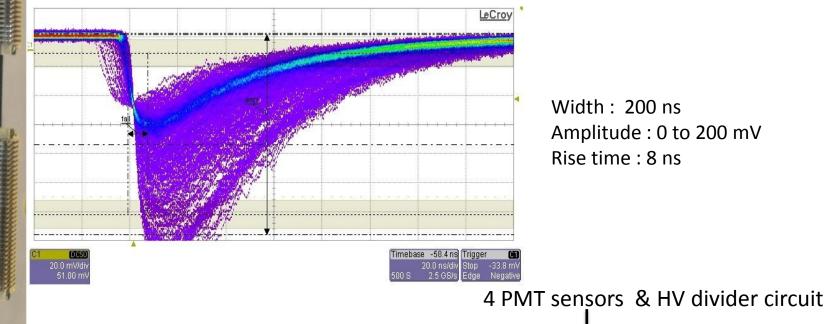

The picture below is a capture of the anode signal of the PMT (HR+ PET system). The HV divider circuit include a differential amplifier with a gain 2 to the board.

Scintillators crystals

Width: 200 ns Amplitude : 0 to 200 mV Rise time : 8 ns

ch 13th

00

Magne Magali LPC Cler

## ASM

- ASM for "Analog Sampling Module"

- **G**eneric electronic board

- 24 differentials analog inputs (600mV amplitude)

- VME 6U board format (compatible VME 64x)

- Scalable system

- Functions:

- sampling data at up to 6 GHz on a windows up to 1000 samples.

- Generate an own trigger detection by channel and by board.

- Data acquisition used VME BLT protocol

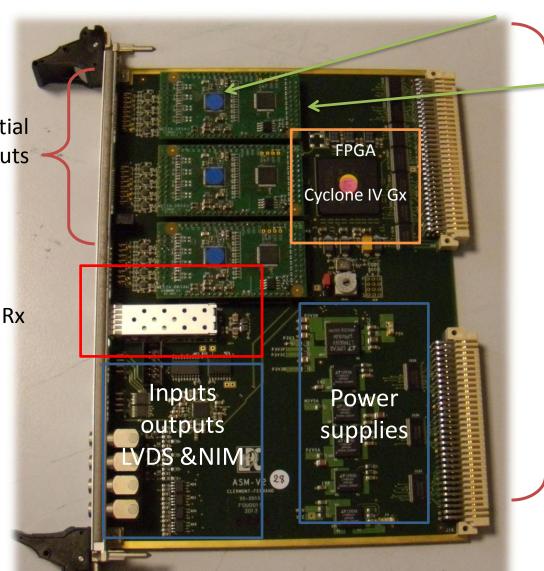

## **ASM** specifications

24 differential analog inputs

Optical Tx/ Rx 3.65 Gbs

3 Sampling & digitizing mezzanines

under mezzanines Analog trigger generation part

Connectors to VME Backplane

# **Board functional diagram**

rch 13th

00

00

00

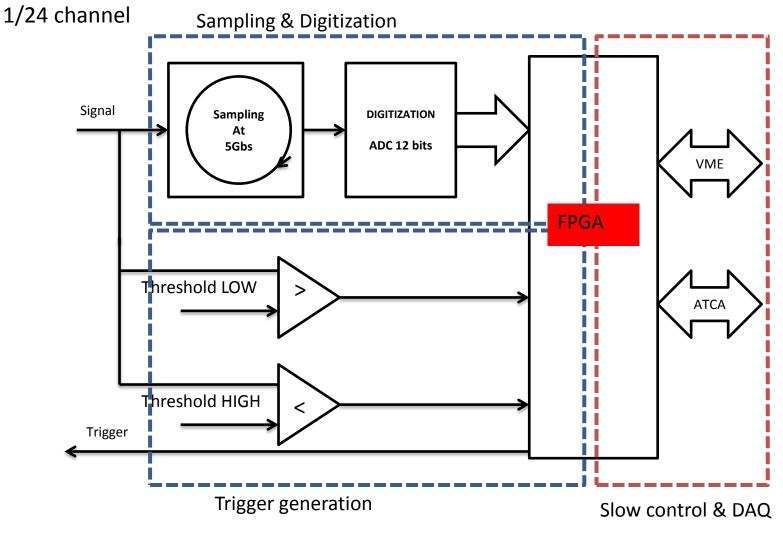

# Sampling & digitization

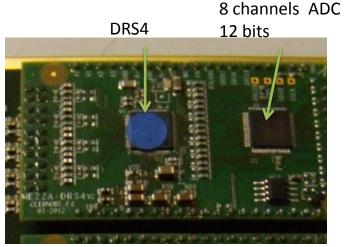

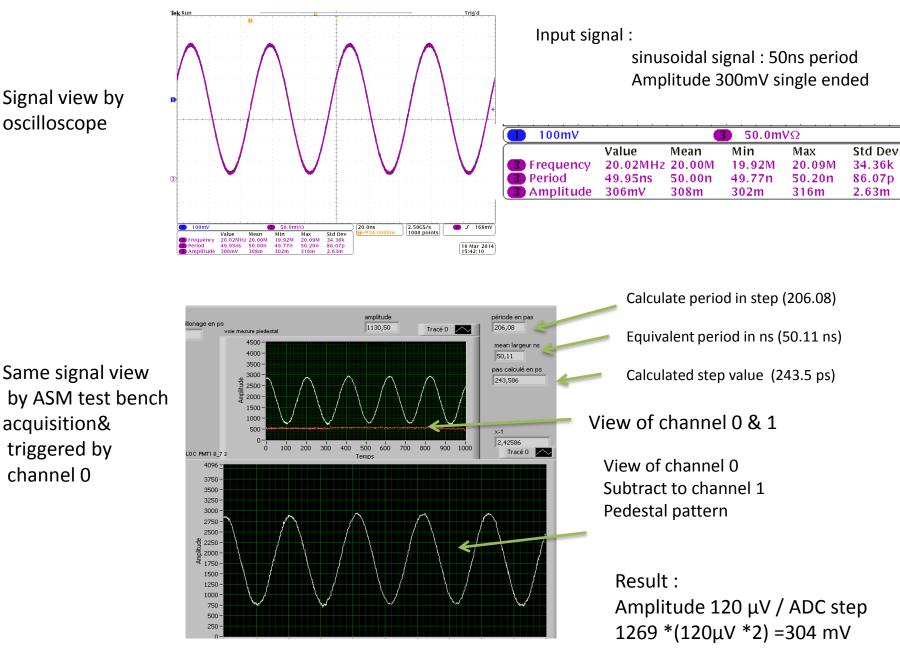

- Used DRS4 chips coupled with an ADC 12 bits

- By configuring VME register: one determines :

- Buffer size 10 to 1000 samples

- Sampling frequency ( for stand alone work)

- Select internal sampling frequency or external LVDS clock for multiple boards used

- Each mezzanine can be individually configured.

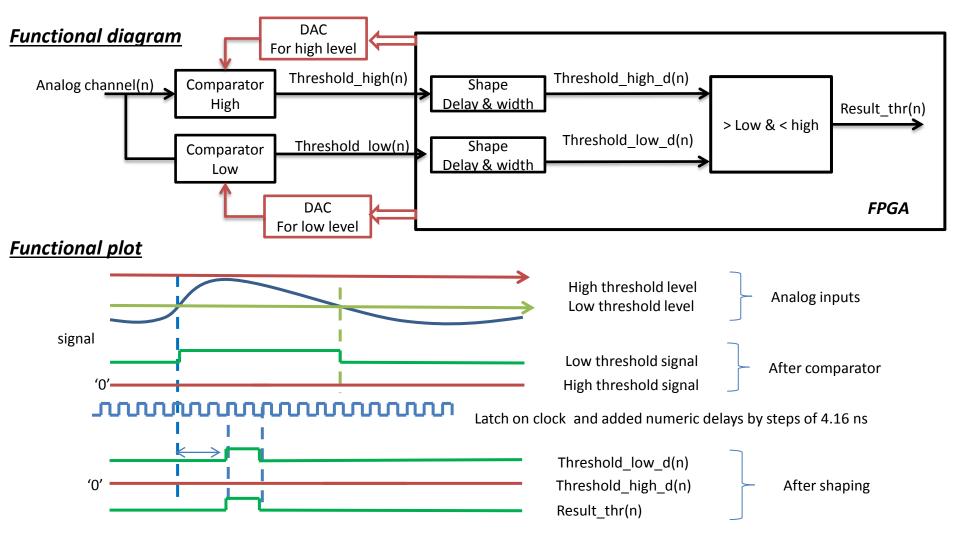

### Thresholds detection to trigger signal First step : individual trigger generation

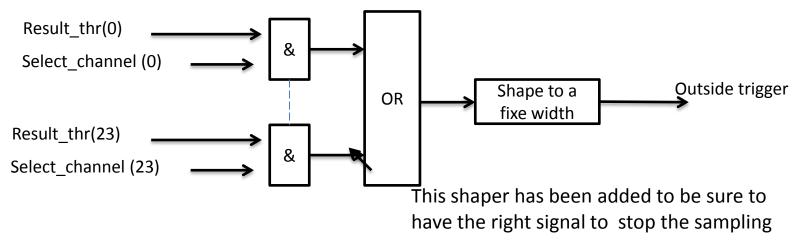

## Thresholds detection to trigger signal Second step: board trigger generation

• Each channel can be select to be in the board trigger

This signal go outside the board to permit make an external logic. Coincidences of others trigger boards

And permit to include BUSY of each board in equation to have less problem with the DAQ when we use more than one board.

ch 13th

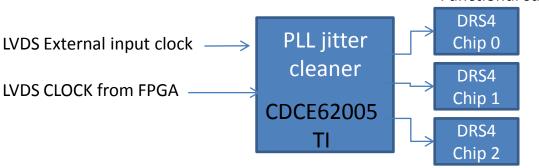

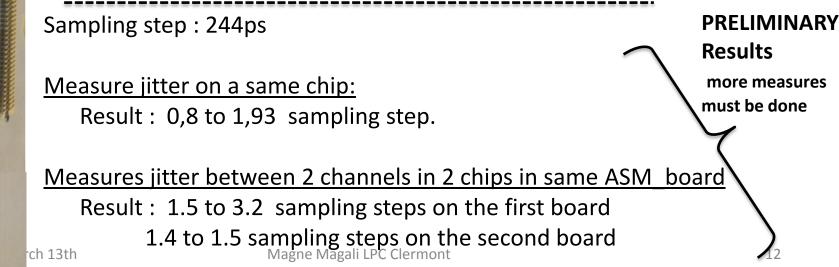

# Sampling Clock network

The PLL jitter cleaner permit to select on 2 inputs clock and generate 3 clocks for the 3 DRS4 chips.

*Functional sampling clock network*

- The PLL jitter cleaner ensure the low jitter between the 3 chips.

- The tracks on the PCB have been carefully studies .

## Data acquisition

At the output of the ADC the data are put 2 by 2 channels in a FIFO(24 bits width). (to be compatible with 32 bits VME bus).

For the first step of the acquisition data we used VME BLT protocol :

The acquisition time is function of numbers of channel read, numbers of samples by channel and digitization time .

- DATA VME OUTPUTS : ( available solution)

- Worst case : If you read 24 channels with 1000 samples each :

- 818 HZ Max readout frequency → Result in experiment 500 Hz by board ( to be divide if the number of board is increase)

#### • Next STEP : optical link

• The next step is to used the optical link : for the same example we hope a max readout of **6 KHz by board**

rch 13th

Magne Magali LPC Clermont

## **Conclusion & Perspectives**

- <u>Conclusion</u>

- This board has begin to give his performances

- The firmware are now stable and permit to make tests to well qualified it.

- Calibration must be add to current setup to hope to obtain low jitter permit by the DRS4 chip.

- More results in the next month

## **Conclusion & Perspectives**

#### Perspectives

- Increase the data rate acquisition by implementing optical link to ATCA.

- Achieve complete characterization of the boards.

- Scale the whole system to 12 ASM boards

## Questions ... Comments

00

0