AGH UNIVERSITY OF SCIENCE AND TECHNOLOGY

#### **Setup of multilayer detector modules for FCAL test-beams**

**Jakub Moroń** AGH-UST Przemyslaw Terlecki AGH-UST

Faculty of Physics and Applied Computer Science AGH University of Science and Technology

FCAL Workshop 2014 26 – 27 May 2014, Institute of Space Science, Bucharest-Măgurele, Romania

- Status found

- Present works

- HV filtering

- Voltage regulator

- Decoupling

- Multiboard integration

- Present status and plans

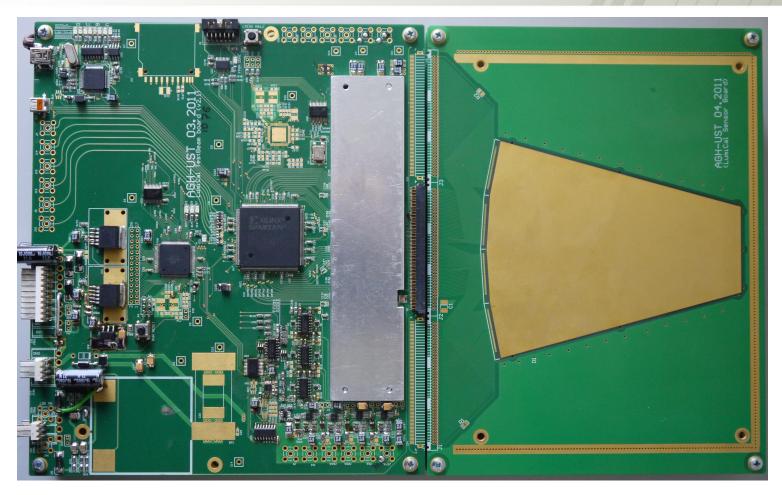

- LumiCal readout boards status Before my work...

- Currently we have four readout boards and three sensors (we are still missing one...)

- Status of the boards:

| Board<br>ID | Owner              | PCB<br>version | Assembly version | HV<br>filter | Noise<br>(active<br>feedback) | Noise<br>(resistive<br>feedback) | CERN<br>tests |

|-------------|--------------------|----------------|------------------|--------------|-------------------------------|----------------------------------|---------------|

| 63          | Krakow             | 2.0            | 1                | ОК           | 6                             | 3                                | *             |

| 67          | DESY               | 2.1            | 1                | OK           | 6                             | 3                                |               |

| 76          | Tel-Aviv           | 2.1            | 2                | NO           | 32                            | 16                               | *             |

| 64          | Krakow<br>(second) | 2.1            | 2                | Wrong        | 32                            | 16                               | *             |

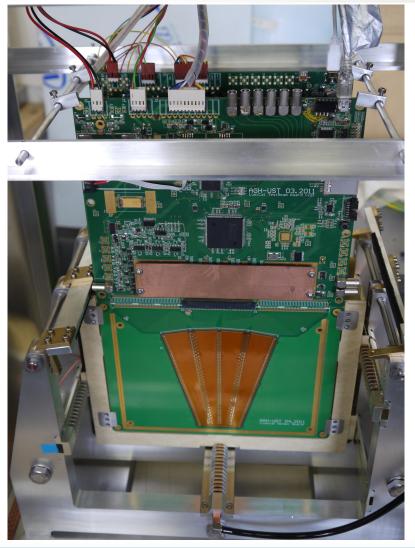

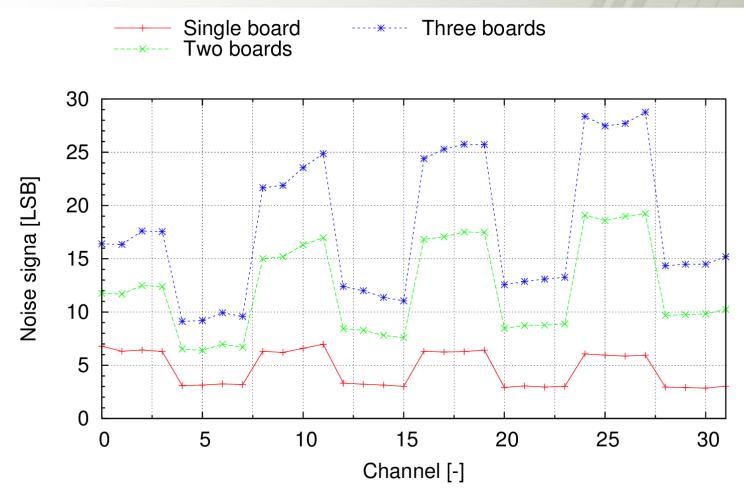

## Integration of multi-plane readout at CERN First try in November 2013...

- Tested configuration:

- Three readout boards with three sensors

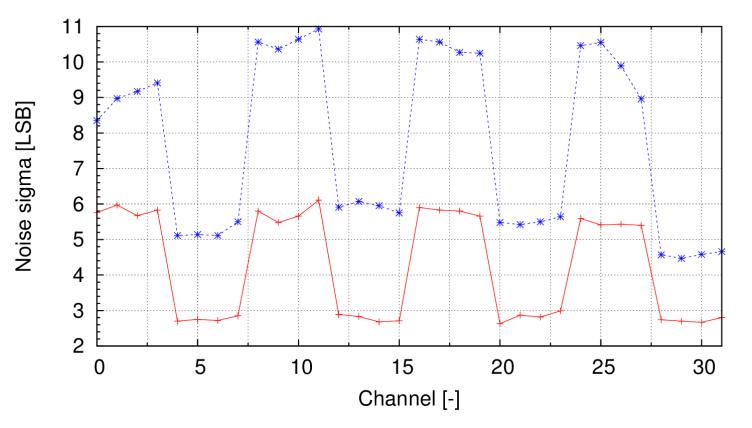

- Main problem: a large increase in noise with two or more boards connected togeather

#### Integration of multi-plane readout at CERN First try in November 2013...

Not acceptable increase of noise for more than one board !!!

27.05.2014

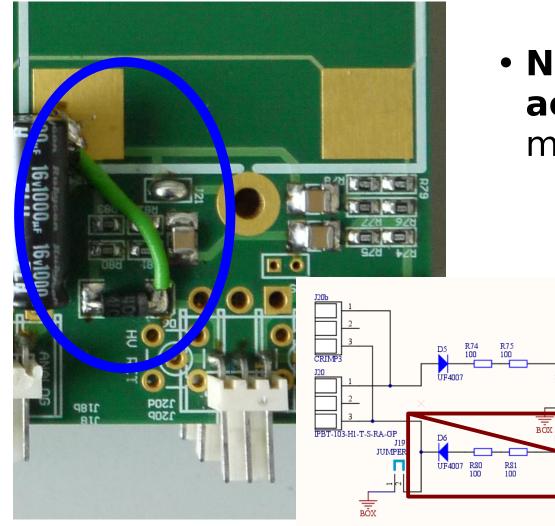

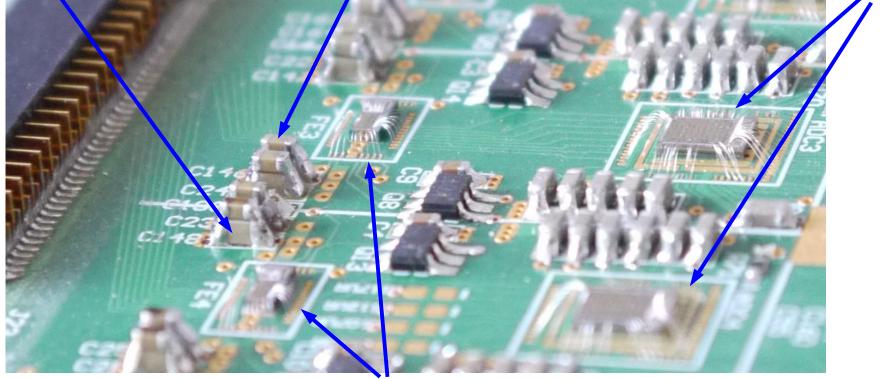

# Present works in Krakow HV filter modification on boards 64 and 76

• Noise reduction not achieved by HV filter modification...

C115 100nF/230V

C125

100nF/230V

R76

R77

101

R83

10k

R78 47k

C117

100nF/230V

R79 47k

C119

100nF/230V

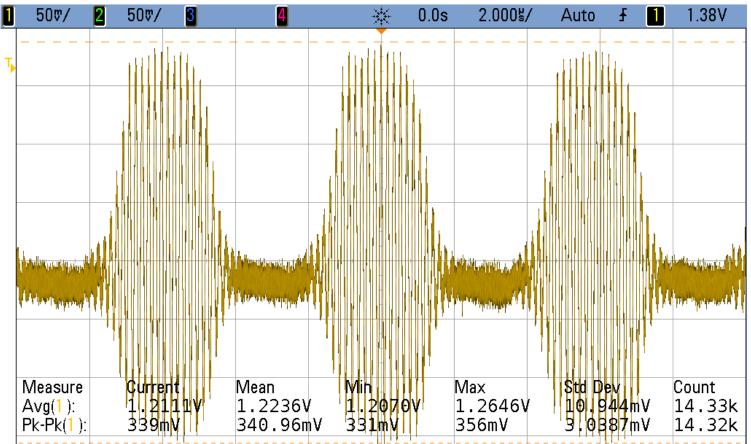

• FPGA core voltage regulator oscillations founded on boards 76 and 64 (second assembly version)

27.05.2014

Setup of multilayer detector modules for FCAL test-beams

# Present works in Krakow Wrong decoupling causes FPGA voltage regulator oscillations

27.05.2014

AGH

# Present works in Krakow FPGA core voltage regulator oscillations

- 100uF capacitance added to regulator output

- Noise reduced to 12/6 LSB to times higher than reference level

| Board ID | Owner              | PCB<br>version | Assembly version | Noise<br>(active<br>feedback) | Noise<br>(resistive<br>feedback) | Modifications                |

|----------|--------------------|----------------|------------------|-------------------------------|----------------------------------|------------------------------|

| 63       | Krakow             | 2.0            | 1                | 6                             | 3                                | -                            |

| 67       | DESY               | 2.1            | 1                | 6                             | 3                                | -                            |

| 76       | Tel-Aviv           | 2.1            | 2                | 12                            | 6                                | HV filter,<br>FPGA regulator |

| 64       | Krakow<br>(second) | 2.1            | 2                | 12                            | 6                                | HV filter,<br>FPGA regulator |

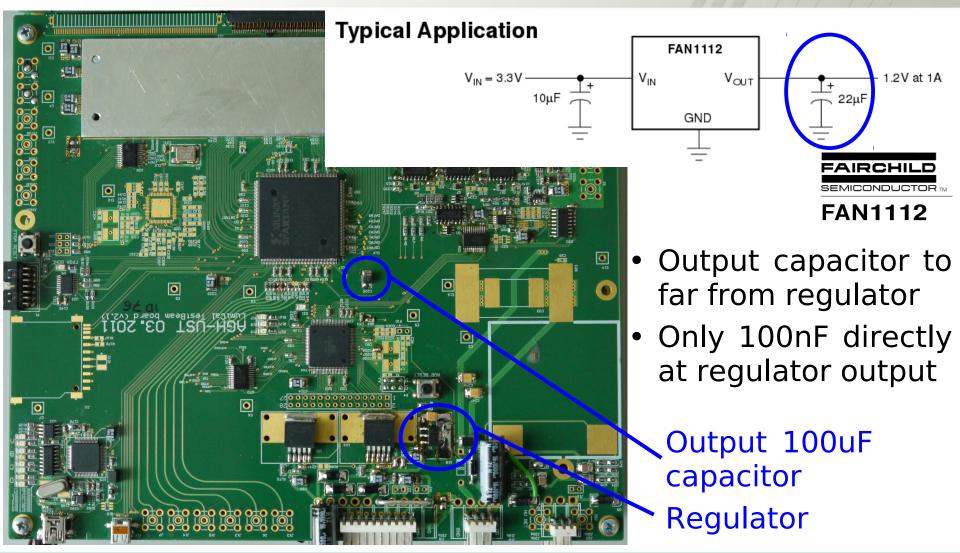

# Present works in Krakow FrondEnd decoupling capacitaces

- FrontEnd power supply 100nF decoupling capacitances used in two assembly runs differs – probably have different ESR (Equivalent Series Resistance)

- Capacitaces located very close to the wirebonds (around 1mm)

Setup of multilayer detector modules for FCAL test-beams

# Present works in Krakow FrondEnd decoupling capacitaces

Low ESR 1uF decoupling capacitors added paralelly to existing 100nF capacitances

Old 100nF New 1uF ADC ASICs

# Present works in Krakow FrondEnd decoupling capacitaces

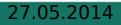

- Noise reduced to 5.5/2.5 LSB below reference level

- Decoupling capacitances added to all boards

| Board ID | Owner              | PCB<br>version | Assembly version | Noise<br>(active<br>feedback) | Noise<br>(resistive<br>feedback) | Modifications                                        |

|----------|--------------------|----------------|------------------|-------------------------------|----------------------------------|------------------------------------------------------|

| 63       | Krakow             | 2.0            | 1                | 6                             | 3                                | -                                                    |

| 67       | DESY               | 2.1            | 1                | 6                             | 3                                | -                                                    |

| 76       | Tel-Aviv           | 2.1            | 2                | 5.5                           | 2.5                              | HV filter,<br>FPGA regulator<br><b>FE decoupling</b> |

| 64       | Krakow<br>(second) | 2.1            | 2                | 5.5                           | 2.5                              | HV filter,<br>FPGA regulator<br><b>FE decoupling</b> |

#### **Present works in Krakow Single boards noise**

After all modifications four boards have the same noise

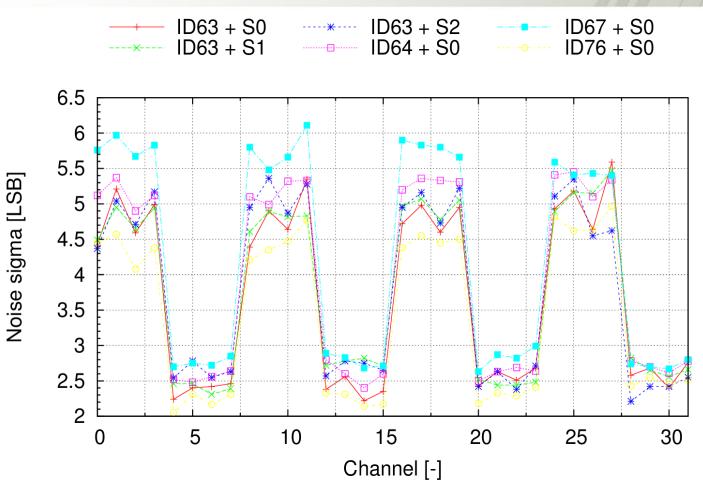

# Present works in Krakow Single board readout - USB ground loop problem

- Two separated power supply networks – one for equipment (ie. power supply) and second for computer

- Bad ground loop created by USB to PC connection

# Present works in Krakow Single board readout - USB ground loop problem

Disturbances caused by the connection of PC to separate power network

Setup of multilayer detector modules for FCAL test-beams

PC and power supplies connected to the same power

Setup of multilayer detector modules for FCAL test-beams

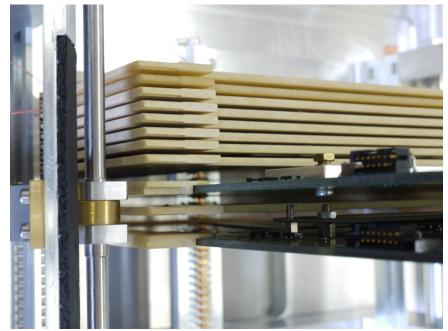

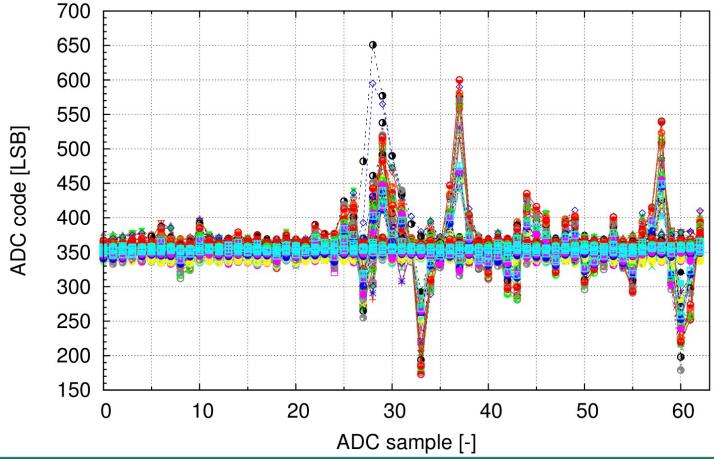

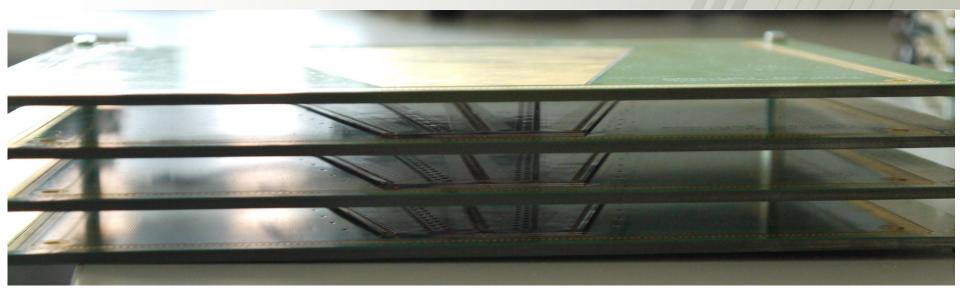

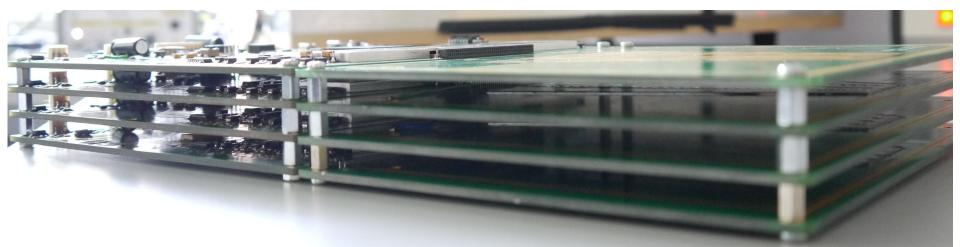

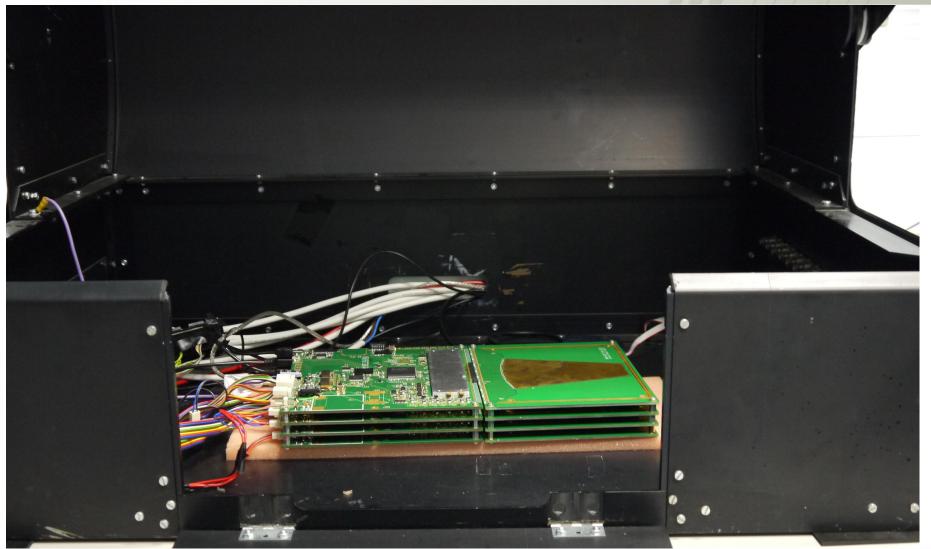

#### Present works in Krakow Multiboard readout integration

Setup of multilayer detector modules for FCAL test-beams

#### **Present works in Krakow Multiboard readout integration**

# The fourth sensor is still missing !!!

Setup of multilayer detector modules for FCAL test-beams 18

#### Present works in Krakow Multiboard readout integration

Setup of multilayer detector modules for FCAL test-beams

# **Present works in Krakow** Multiboard readout integration - power supply decoupling

Single ID67 + S0 All four boards connected, ID67 + S0

Again, the noise increases, but much less than at CERN

27.05.2014

AGH

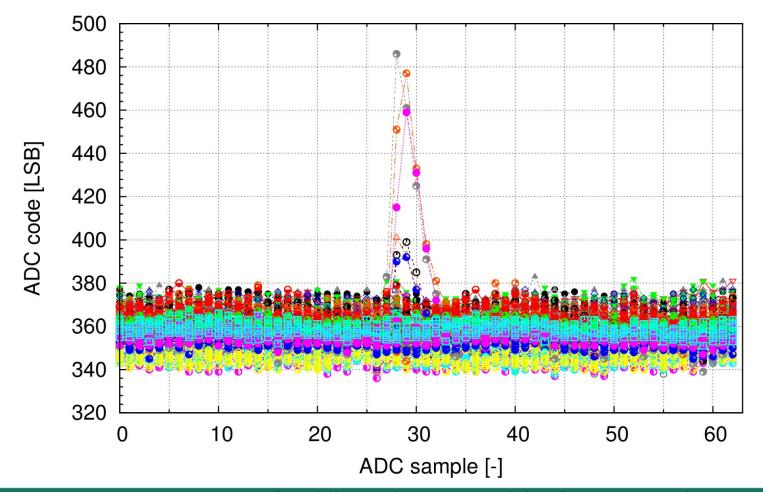

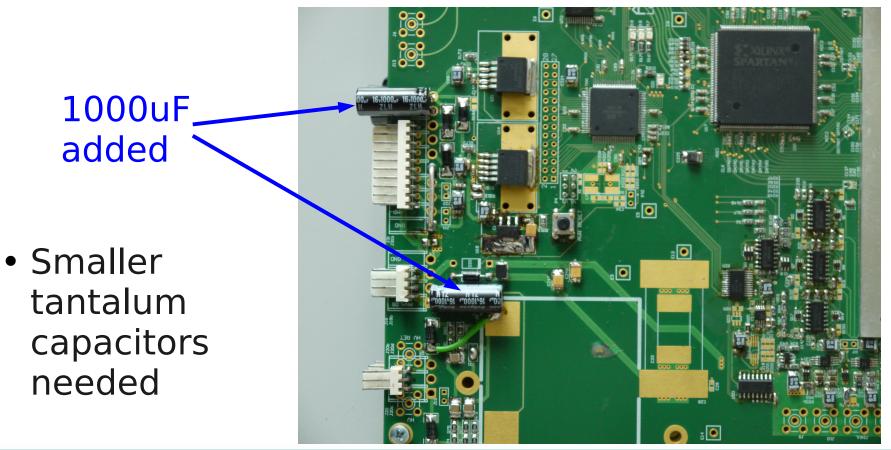

## Present works in Krakow Multiboard readout integration - power supply decoupling

Low ESR, 1000uF decouplig capacitors added on each board at power supply inputs

# Present works in Krakow Multiboard readout integration - power supply decoupling

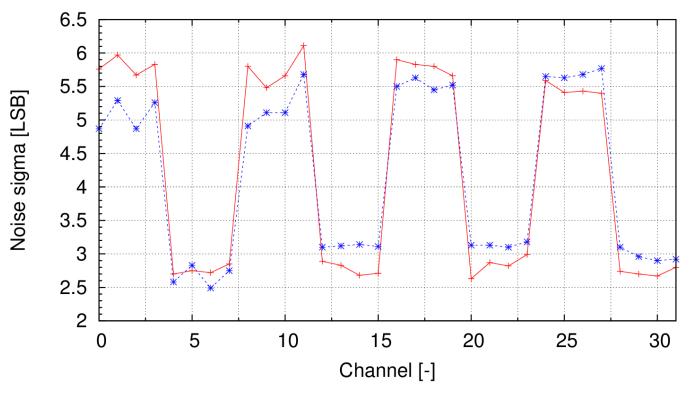

— Single ID67 + S0

All four boards connected, 1000uF decoupling, ID67 + S0

Four boards together have the same noise as the single board, but ... see next slide

27.05.2014

AGH

# AGH

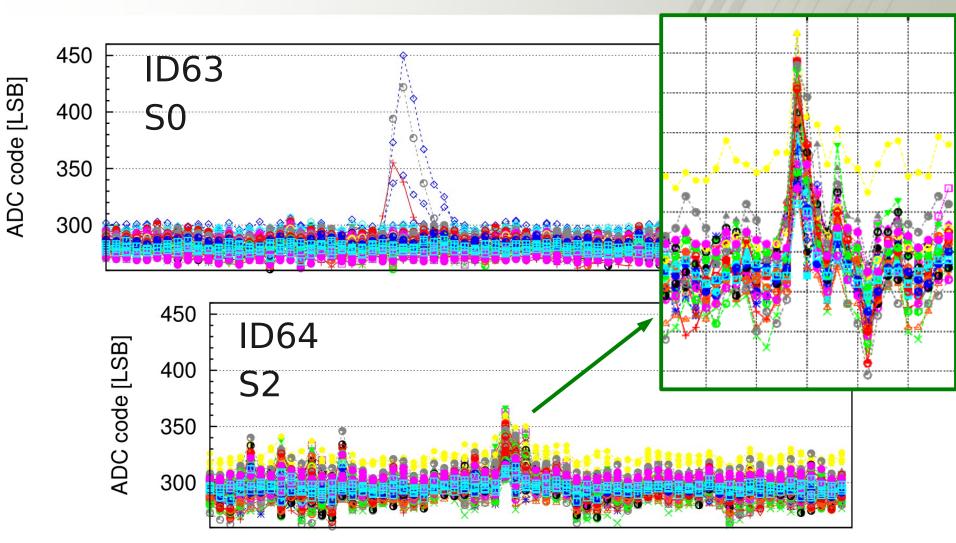

#### Present works in Krakow Multiboard readout - USB ground loop problem (?)

Present works in Krakow Multiboard readout - USB ground loop problem (?)

- Each board connected via USB cable to PC ground multiloop created

- USB ground shorted between boards – baseline variations reduced but not eliminated...

- FPGA core voltage unstability found on friday evening – probably better regulator needed...

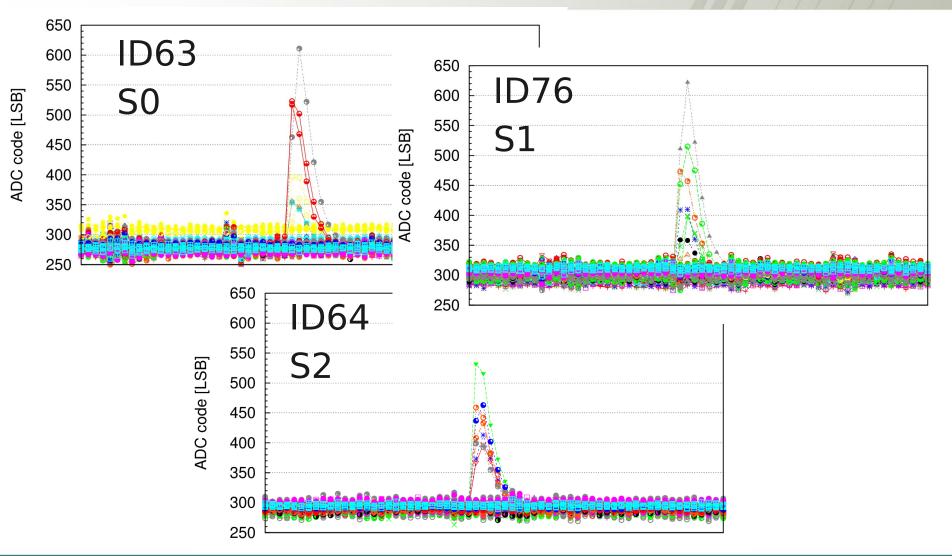

# Present works in Krakow Multiboard readout – USB ground loop problem – high trigger treshold

27.05.2014

AGH

Setup of multilayer detector modules for FCAL test-beams 25

# **Summary and Plans**

- All four boards uniformed and noise reduced

- HV filter modifications

- FPGA core voltage oscilation eliminated

- FrontEnd decoupling improved

- Ground loop through PC connnection reduced

- Multiboard integration still in progress...

- Noise reduced by power supply decoupling

- Baseline variations still require some work...

- TLU-like trigger system for cosmic measurements needs to be developed...