High precision design

AGH UNIVERSITY OF SCIENCE AND TECHNOLOGY

## Development of new front-end electronics in CMOS 130 nm

Marek Idzik AGH-UST

Faculty of Physics and Applied Computer Science AGH University of Science and Technology

24th FCAL Collaboration Workshop ISS Bucharest 26-27 May 2013

- Introduction and Where we are

- ASIC developments in CMOS 130 nm

- Preamp-Shaper, ADC, PLL, SLVS blocks

- IBM, TSMC technologies

- Summary and Plans

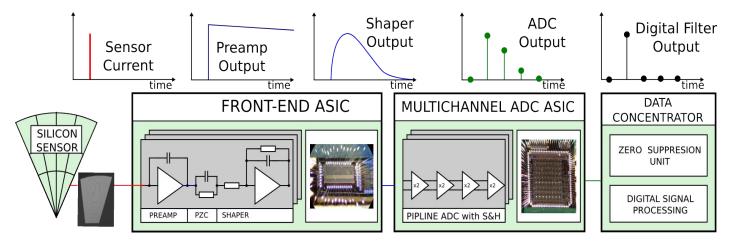

#### Existing readout developed in CMOS AMS 0.35 um comprises:

- 8 channel front-end ASIC (preamp, shaper Tpeak~60ns, ~9mW)

- 8 channel pipeline ADC ASIC, Tsmp<=25MS/s, ~1.2mW/MHz

- FPGA based data concentrator and further readout

### New developments in IBM CMOS 130 nm:

- First prototype of front-end ASIC developed and under tests

- First prototypes of SAR ADC ASIC developed and under tests

#### Even Newer developments in TSMC CMOS 130 nm just started...

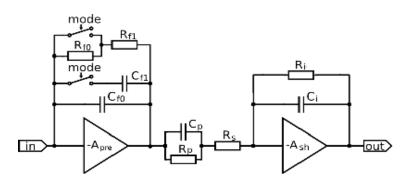

## New readout for LumiCal in IBM CMOS 130 nm Architecture and technology comparison

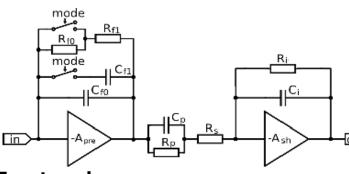

PZC

New readout in 130 nm has very similar architecture to existing one in 0.35um but should consume much less power and be radiation resistant

#### Front-end specs:

- Cdet  $\approx$  5 ÷ 50pF

- 1st order shaper (Tpeak  $\approx$  50 ns)

- Variable gain, two modes:

- calibration: MIP sensitivity

- physics:  $Q_{in}$  up to ~6 pC

- Power pulsing

- Peak power cons. ~1.5 mW/channel (in AMS 0.35um it was ~9mW)

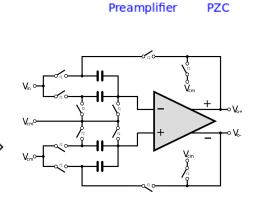

#### Single-to-Diff specs:

- Max freq. > 40MHz

- Power pulsing

- Peak power ~ 0.5mW

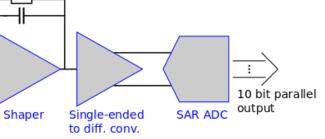

#### **ADC specs:**

- 10-bit resolution

- Architecture: SAR ADC

- Max frequency > 40 MHz

- Power pulsing

- Peak power ~ 1 mW @40MHz (in AMS 0.35u mit would be > 40mW)

Channel schematic diagram

#### **Design specs:**

- 8 channels

- Cdet ≈ 5 ÷ 50pF

- 1st order shaper (Tpeak ≈ 50 ns)

- Variable gain:

- calibration mode MIP sensitivity

- physics mode input charge up to ~5 pC

- Power pulsing implemented

- Power consumption ~1.5 mW/channel

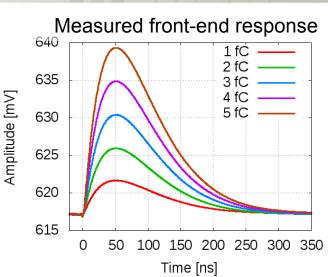

#### Very Preliminary Measurements:

- Fully functional

- Tpeak ≈ 51 ns

- Calibration mode @10pF:

- gain 4.1 mV/fC

- linear range ~60 fC

- ENC 930 e-

- Physics mode @10pF

- gain 105 mV/pC

- Linear range ~2.7 pC (saturates >5pC)

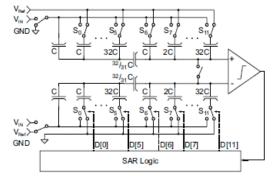

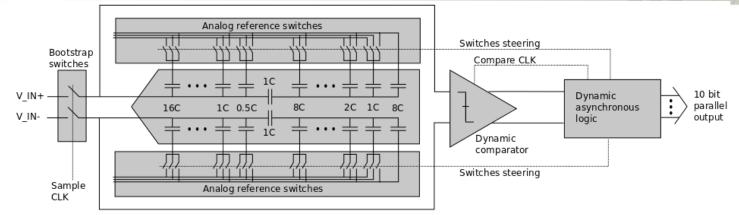

## **10-bit SAR ADC for LumiCal in IBM 130 nm AGH Architecture&Design considerations**

#### Architecture of ADC:

- Differential segmented/split DAC with MCS switching scheme ultra low power

- Dynamic comparator no static power consumption, power pulsing for free

- Asynchronous logic no clock tree power saving, allows asynchronous sampling

- Dynamic SAR logic *much faster than conventional static logic*

#### **Design considerations:**

| <ul> <li>Resolution</li> </ul>                                | 10 bits        |

|---------------------------------------------------------------|----------------|

| <ul> <li>Variable sampling frequency</li> </ul>               | up to ~50 MS/s |

| <ul> <li>Power consumption at 40 MS/s</li> </ul>              | ~1 mW          |

| <ul> <li>pitch, ready for multichannel integration</li> </ul> | 146 µm         |

J. Moron, M. Firlej, T. Fiutowski, M. Idzik, Sz. Kulis, K. Swientek. "Development of variable sampling rate low power 10-bit SAR ADC in IBM 130 nm technology", TWEPP2013 23-27 September 2013, Perugia Italy

ADC Out [LSB]

## **10-bit SAR ADC in IBM 130 nm Static measurement results**

#### Transfer function INL/DNL measurements 1024 1.5 1 INL [LSB] 896 0.5 0 768 -0.5 -1 640 -1.5 128 0 256 384 512 640 768 896 1024 512 Code [LSB] 1 384 0.5 DNL [LSB] 256 0 128 -0.5 0 -1 -0.8 -0.6 -0.4 -0.2 0 0.2 0.4 0.6 0.8 1 1.2 -1.2 -1 128 256 384 640 768 896 1024 0 512 Code [LSB] Vin [V]

- ADC works well in the whole input signal range

- Generally, good linearity is measured, although for a few codes improvement is still needed

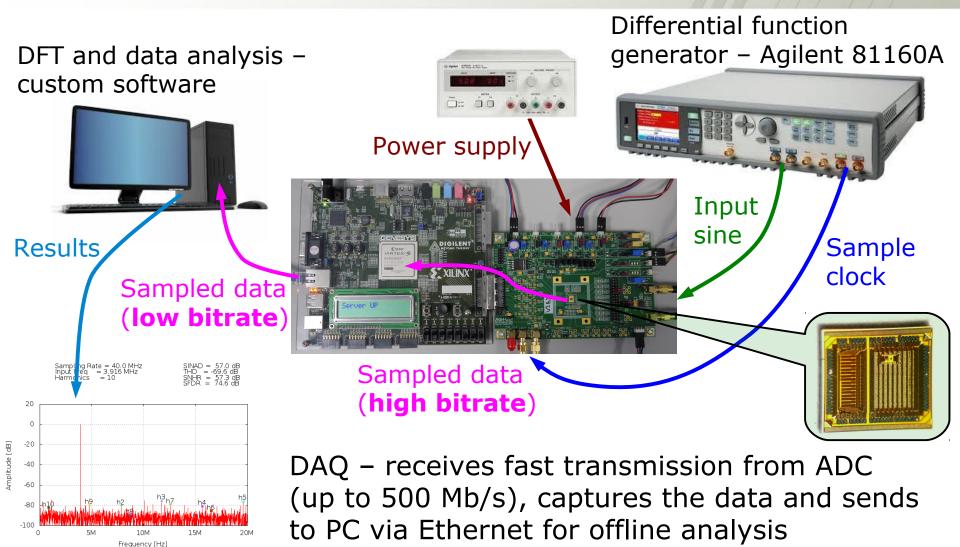

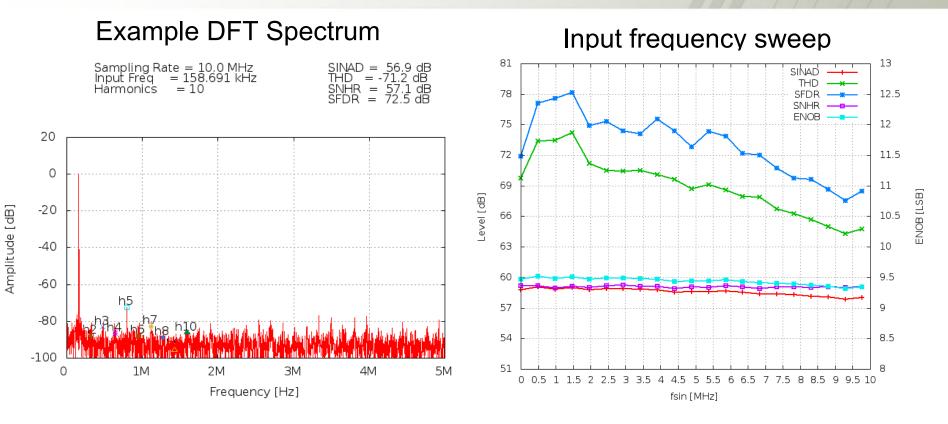

## 10-bit SAR ADC in IBM 130 nm Dynamic measurement results (@20 MS/s)

**ENOB~9.3** up to Nyquist input frequency for  $f_{sample} \sim 20$ MHz & P $\sim 0.7$ mW

ADC works for  $f_{sample}$  beyondt 40 MS/s, but above 20 MS/s ENOB start to decrease. Problem with jitter above 20 MS/s found..., will be fixed in next submission.

9

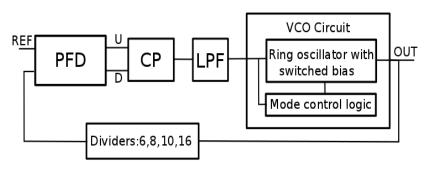

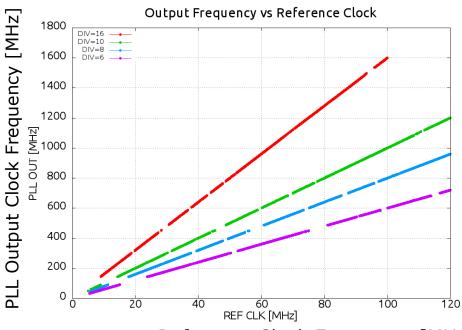

## Low power PLL in IBM 130 nm Architecture, design, and measurements

#### Main features:

- General purpose PLL block

- Very wide output frequency range: **10MHz**

- 3.5GHz (tested up to 1.6GHz)

- Gaps in frequency are found in the prototype to be eliminated...

- 16 VCO modes Automatically (or manually) changed

- Jitter 15-70 ps (to be improved...)

- Power consumption ~0.6mW@1GHz

- Different loop division factors: 6,8,10,16

- Size 300um x 300um

Reference Clock Frequency [MHz]

Very low power PLL has been developed and the prototype is fully functional.

Few issues (frequency gaps, jitter) need to be improved

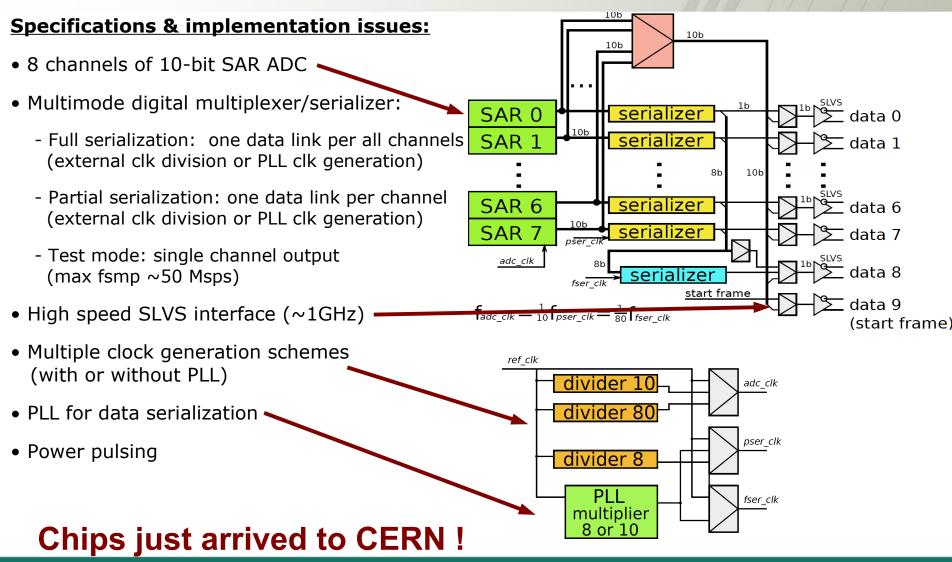

## 8-channel 10-bit SAR ADC in IBM 130 nm Architecture and Design

## TSMC CMOS 130nm story...

- CERN contract wit IBM finishes in 2015

- The future with IBM is not clear...

- We need to change the technology

- CERN is moving to TSMC 130 nm (radiation hardness needs to be verified...)

- •TSMC seems cheaper than IBM but one need to submit large chips (>= 50k\$)

- We are following CERN

- development in IBM 130 nm stopped

- first designs in TSMC 130 nm just starting

- looks like never ending story...

### **Summary and Plans**

# • New LumiCal readout in IBM 130 nm under development (but stopped)

- First 8 channel prototype of front-end electronics fabricated. First test show good results

- First prototypes of 10-bit SAR ADC, PLL, SLVS already fabricated and tested:

- 10-bit SAR ADC: results show good functionality, low power and ENOB~9.3

- PLL fully functional, some improvements foreseen for 2nd prototype

- SLVS interface works well at least up to 1 GHz

- 8 channel ADC with PLL based serialization, SLVS interface, just fabricated, will be tested soon...

- We need to change the technology again, most probably to TSMC 130 nm, design is just starting...

## Thank you for attention