Summary of the meeting at LBL about the FP420 3D detector layout

• Present:

C. Da Via, J. Hasi, C. Kenney, S. Parker, M. Garcia-Sciveres – inputs from Scott Kolya-

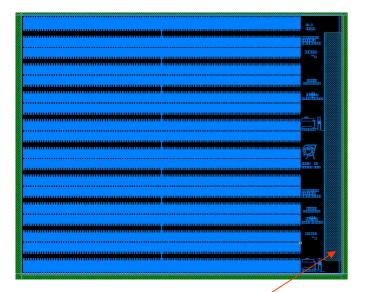

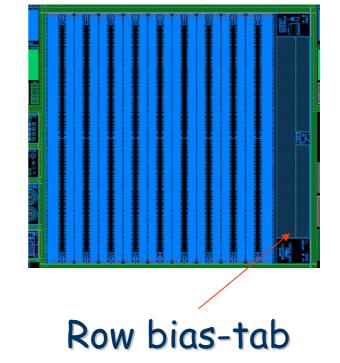

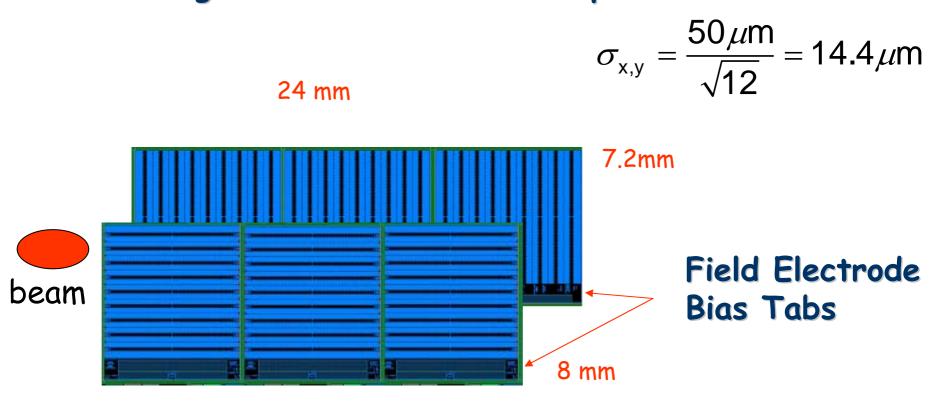

## H and V orientations : Field Electrode Bias Tab (C. Kenney)

Wire Bond or Conductive Adhesive 1 mm wide

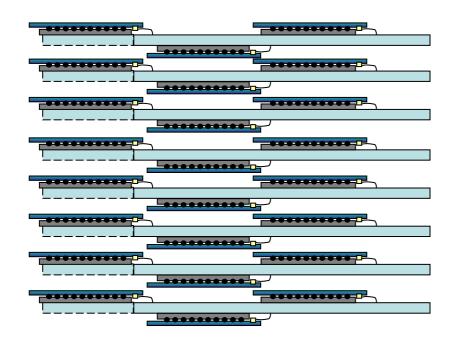

#### Combining horizontal and vertical planes

21.6 mm

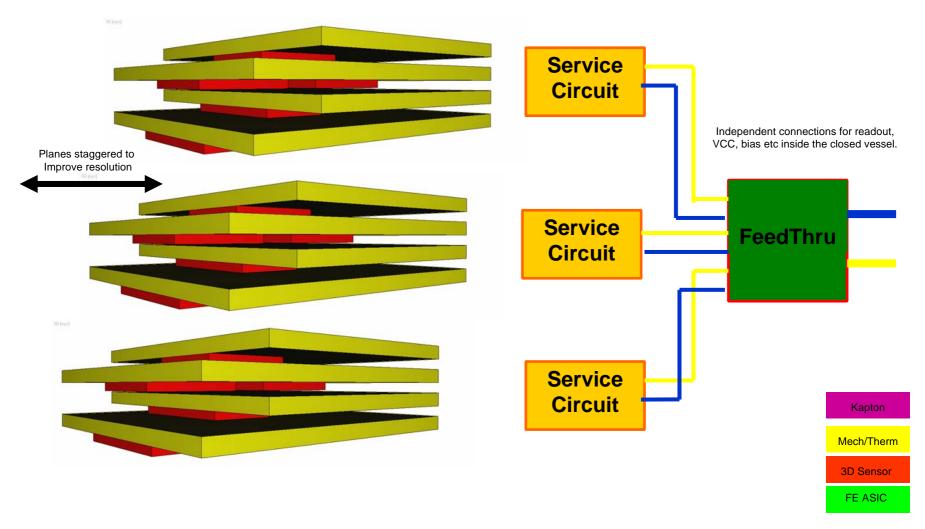

#### Detector Station built from a number of superlayer

Scott Kolya- Manchester

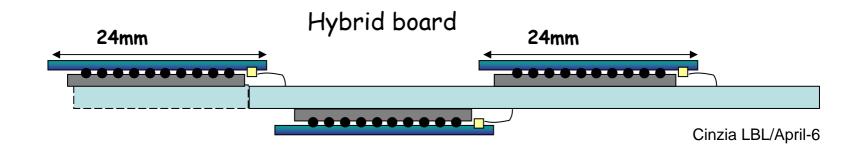

Cinzia LBL/April-6

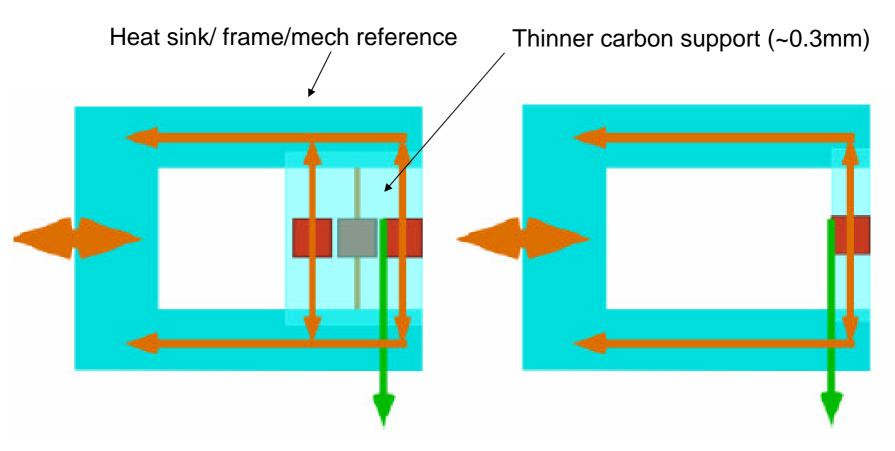

## Cooling options (Scott)

Cinzia LBL/April-6

### 3D + Atlas pixel parameters estimated

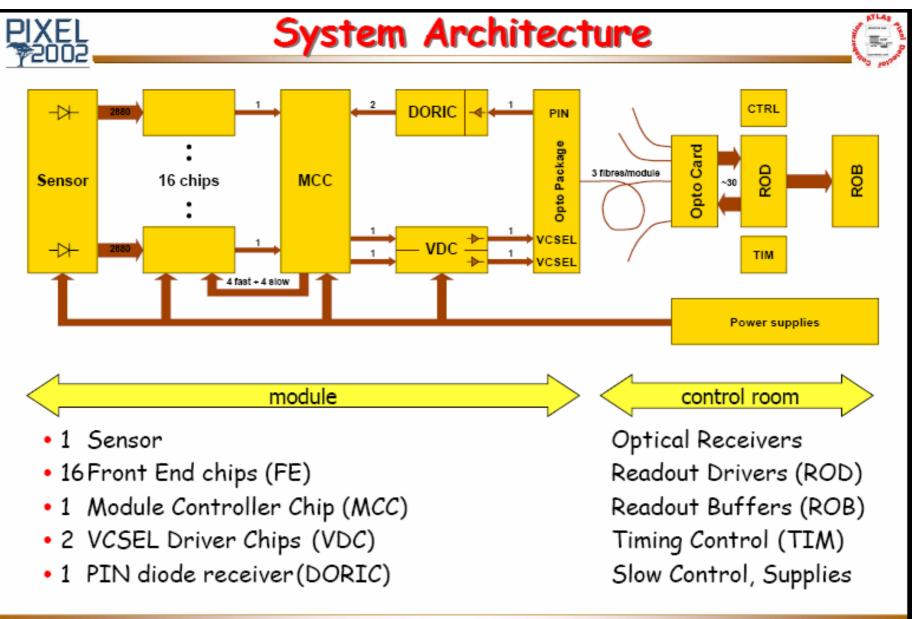

-power dissipation: (the depletion voltage for the sensors, two low voltages for the frontend chips and the module controller chip and three low voltages for the operation of the optical link: http://www.slac.stanford.edu/econf/C020909/skpaper.pdf)

#### 0.7W/cm2

0.4W/detector and 1.2W/plane. 12W / station (10 planes)

- -highest supported temperature ~105C hybrid

- ~200C detector+electronics

-thickness of 1 plane (detector+electronics+board) 0.5 mm+ 0.3 carbon-carbon support (detector region)

~2mm (hybrid frame) ~25mm/station (10 planes)

-weight ~36g / 1 board ~360g / station (10 planes)

## Side Cells (Chris)

Add More Electrodes to Side Cells

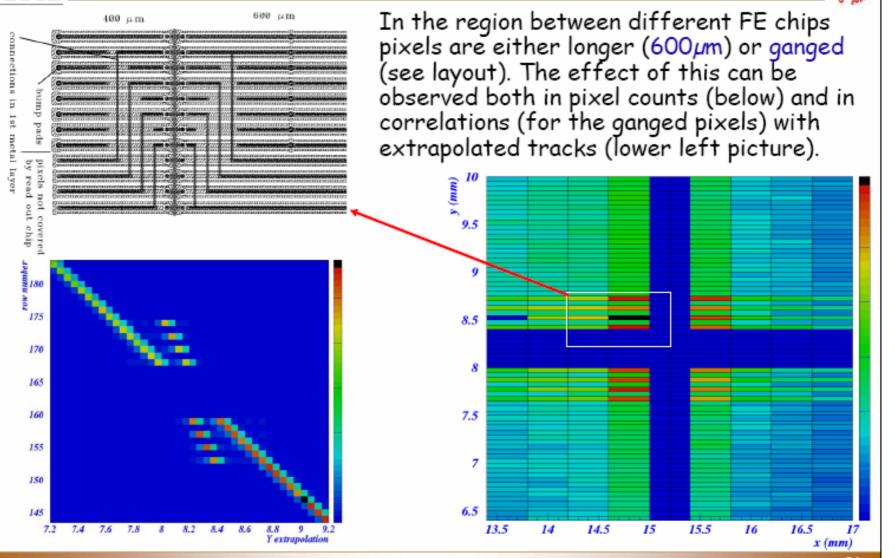

- 2E 600 microns

- 3E 134 microns

- 4E 115 microns

## **Bottom Cells (Chris)**

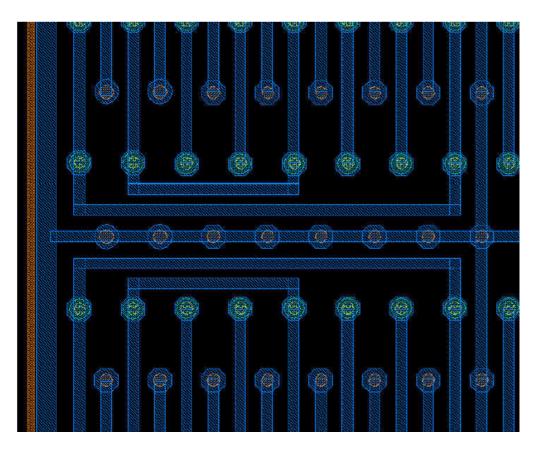

Gang Together Two Pairs of Pixels Separated by At Least 3 Intervening **Pixels** – Eliminate Ambiguity Adds 115 microns to Sensor Bottom Edge

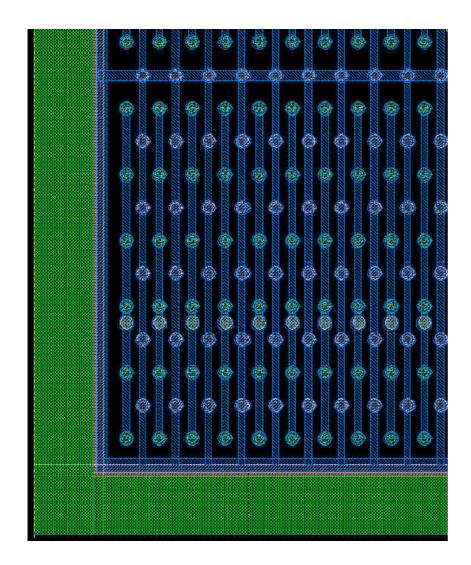

## Ganged and Long Pixels

Plans :

June-July06 lab test with bump-bonded 3D sensors (?) August 06 test beam Summer 06 test setup in house Autumn 06 module prototype Dec 06 preparation of Reports and draft-TDRs (Atlas and CMS)

1<sup>st</sup> step: Superplane prototype would require:

~10-FE chips + sensors 2 MCCs chips even with faulty channels) 1 opto-board (VDC DORIC?)

TPLL TPCC (PCC to type0 adapter board?)

2<sup>nd</sup> step supermodule:

~36 chips+sensors 6 MCC 5 opto-boards (VDC-DORIC?)

Burn-in setup? ROD?

Cinzia LBL/April-6

# Conclusions

- TPLL, TPCC are on their way to Cern

- Fully functional hybrid board

- MCC (faulty, will need to be diced)

- Opto-hybrid non advisable, problems with production

- Test bench should be ready before summer

# Test beam plan

- 1 wafer has been sent to IZM/Bonn to be bonded

- 10 detectors will be bump-bonded to single atlas pixel chips:

- 6 x 3E

- 2 x 2E

- 2 x 4E

Fpix/3D will be bump-bonded at Stanford