# Silicon Pixel Detectors for Tracking

N. Wermes Bonn University Pixel detectors for charged particle tracking/vertexing

$\rightarrow$  all large detectors (i.e. LHC) so far

readout

bump-bond

track

sensor

electronics

NMOS

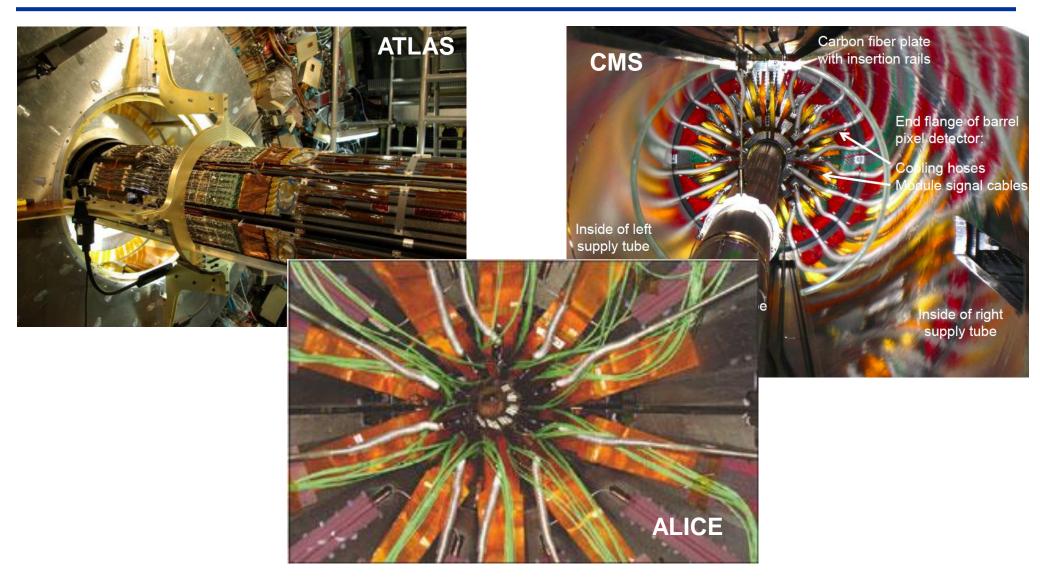

#### The "PAST": large area pixel detectors at the LHC

#### all based on "Hybrid Pixel Detectors"

#### The Hybrid Pixel Bubble Chamber

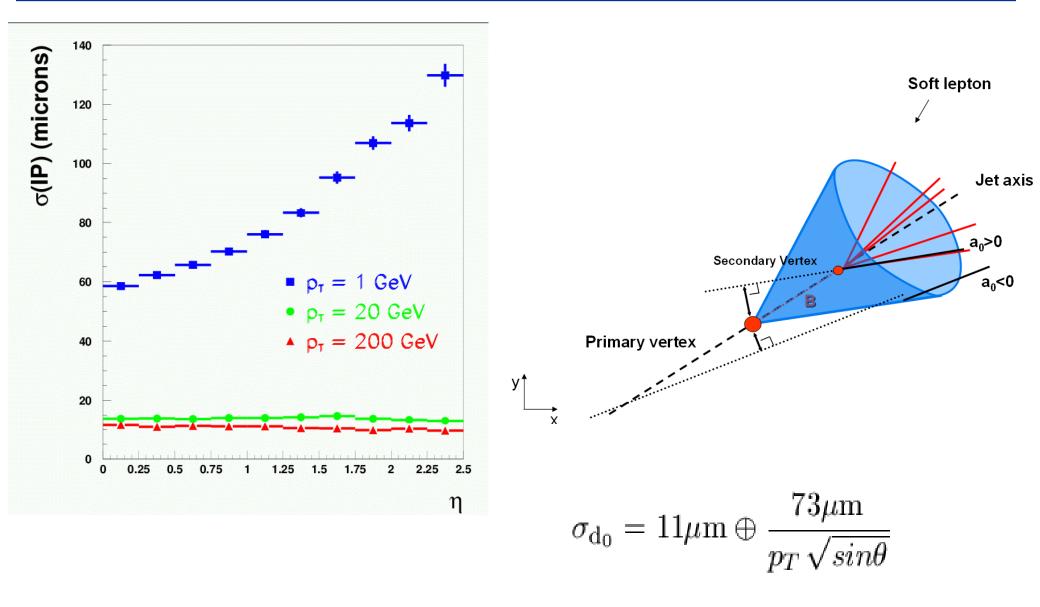

#### **Expected resolutions (ATLAS)**

#### **Principle of hybrid pixel detector readout**

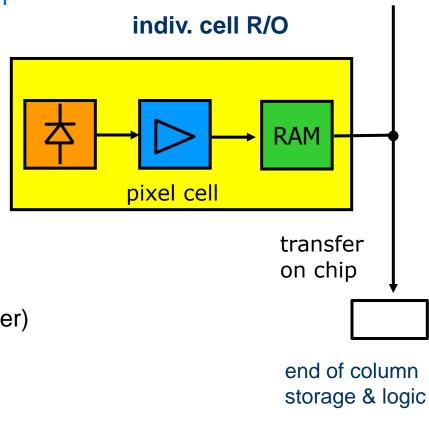

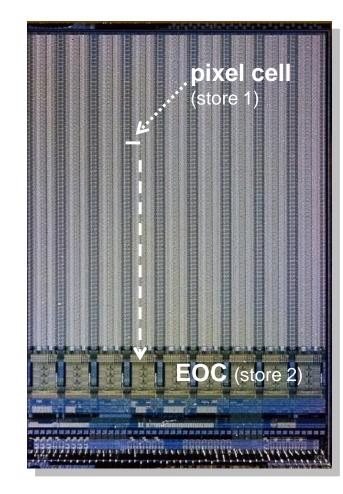

#### charge generation in sensor, integration in FE-chip

temporary on chip storage (digital or analog) trigger driven readout of individual hits

- pn-diode  $\rightarrow$  Q<sub>signal</sub>

- amplification and filtering  $\clubsuit$   $V_{\rm out}$

- pixel-wise storage: address, charge, time (BX)

- column-wise R/O

- transfer information to End of Column (wait for trigger)

- address

- charge (ToT)

- time

#### **Principle of hybrid pixel detector readout**

charge generation in sensor, integration in FE-chip

temporary on chip storage (digital or analog) trigger driven readout of individual hits

- pn-diode  $\rightarrow$  Q<sub>signal</sub>

- amplification and filtering  $\rightarrow$  V<sub>out</sub>

- pixel-wise storage: address, charge, time (BX)

- column-wise R/O

- transfer information to End of Column (wait for trigger)

- $\checkmark$  high rate capability

- $\checkmark$  radiation hard to 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>

- ✓ mature technology

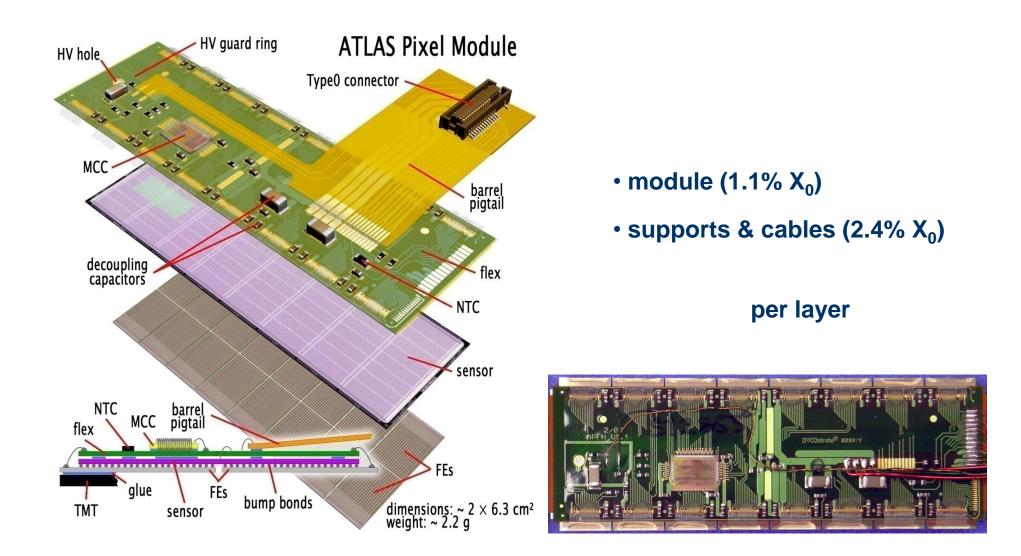

comparatively massive (>3% X<sub>0</sub>, mostly due to power and overall size)

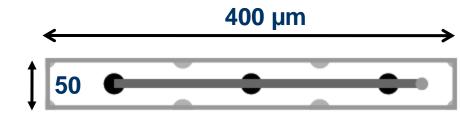

resolution ~10 μm (pixels sizes 50x400 μm<sup>2</sup> or 100x150 μm<sup>2</sup>)

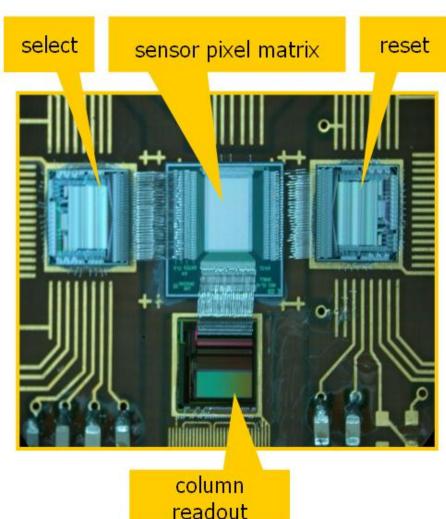

### A Hybrid Pixel Detector Module

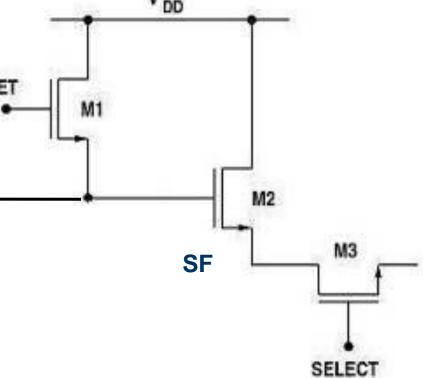

#### **Principle of (semi-) monolithic pixel detectors**

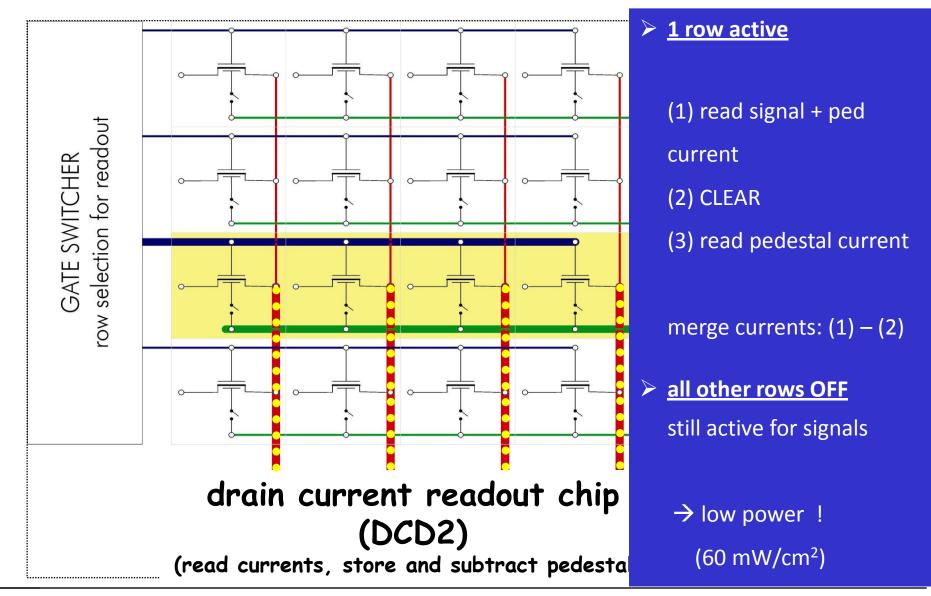

clear

and

selection

row

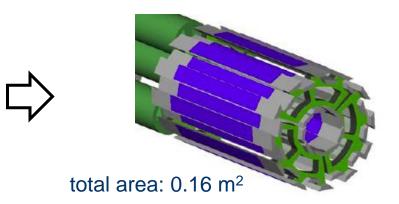

### **Principle of (semi-) monolithic pixel detectors**

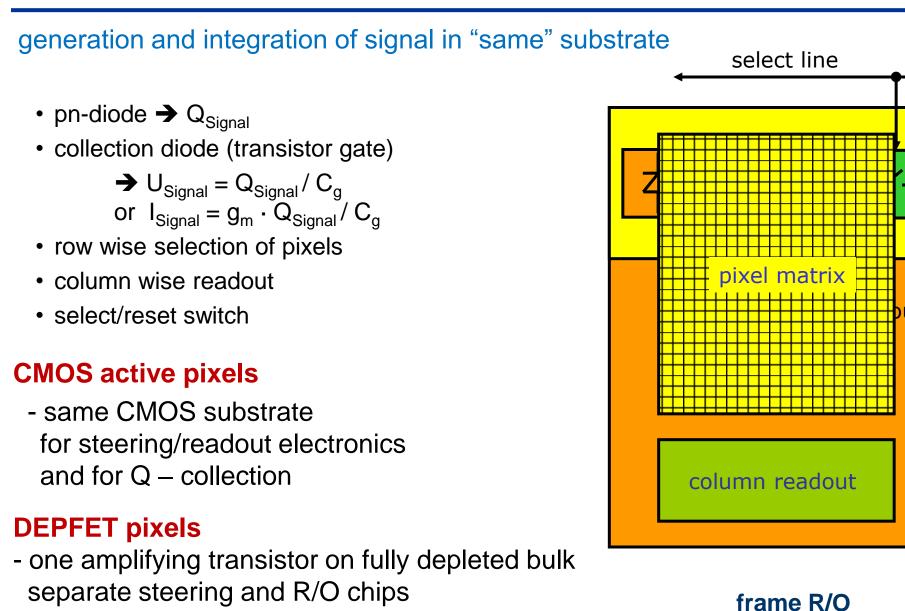

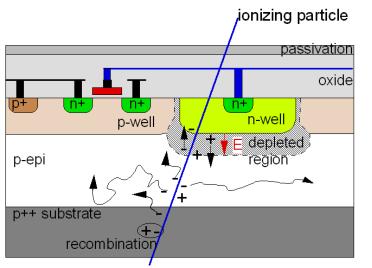

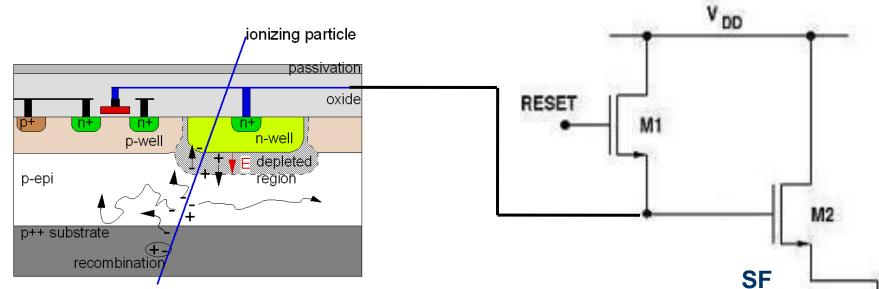

#### generation and integration of signal in "same" substrate

DEPFET

- pn-diode  $\rightarrow$  Q<sub>Signal</sub>

- collection diode (transistor gate)

→

$$U_{\text{Signal}} = Q_{\text{Signal}} / C_{g}$$

or  $I_{\text{Signal}} = g_{m} \cdot Q_{\text{Signal}} / C_{g}$

- row wise selection of pixels

- column wise readout

- select/reset switch

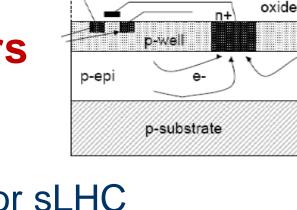

#### **CMOS** active pixels

same CMOS substrate for steering/readout electronics and for Q – collection

#### **DEPFET pixels**

- one amplifying transistor on fully depleted bulk separate steering and R/O chips

## Rate and radiation challenges at the innermost pixel layer

## **Hybrid Pixels**

|                                                                         | BX time                                                   | Particle Rate | Fluence                               | Ion. Dose                                      |

|-------------------------------------------------------------------------|-----------------------------------------------------------|---------------|---------------------------------------|------------------------------------------------|

|                                                                         | ns                                                        | kHz/mm²       | n <sub>eq</sub> /cm² per<br>lifetime* | kGy per<br>lifetime*                           |

|                                                                         |                                                           | K             |                                       |                                                |

| LHC (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> )                | 25                                                        | 1000          | 1.0 x 10 <sup>15</sup>                | 790                                            |

| superLHC (10 <sup>35</sup> cm <sup>-2</sup> s <sup>-1</sup> )           | 25                                                        | 10000         | 1016                                  | 5000                                           |

| SuperBelle (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> )         | 2                                                         | 400           |                                       | 50                                             |

| <b>ILC</b> (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> )         | 350                                                       | 250           | 10 <sup>12</sup>                      | 4                                              |

| <b>STAR@RHIC</b> (8x10 <sup>27</sup> cm <sup>-2</sup> s <sup>-1</sup> ) | 110                                                       | 3,8           | 1.5 x 10 <sup>13</sup>                | 8                                              |

| Monolithic Pixels                                                       | es<br>er nixels                                           | пес./         | umed lifetimes:                       |                                                |

|                                                                         | <ul> <li>smaller pixels</li> <li>less material</li> </ul> |               | ILC                                   | C, sLHC: 7 years<br>: 10 years<br>ers: 5 years |

LHeC-Workshop, 9/2/2008 – N. Wermes, Bonn

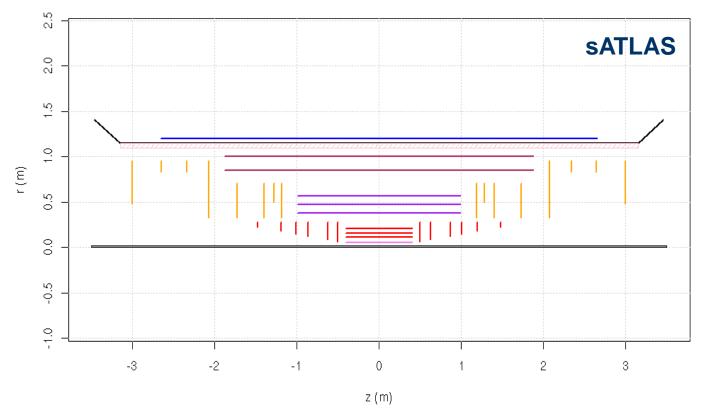

# **Pixels for super-LHC (2016)**

#### current directions

#### **note:** intermediate step $\rightarrow$ B-layer upgrade/replacements scenarios (~2012)

#### radiation hardness

## radiation hardness

$- \sim 10^{16} n_{eq}/cm^2$

-new sensor R&D ongoing: 3D silicon, planar (n in p), diamond

### • data rate

-output rate at innermost layer = 320 MHz = 4 x LHC

### material

-strong interplay between: resolution - secondaries - pattern/track algorithms

what is the best detector? more layers? less material?

-new powering concepts needed (serial, DC-DC)

-goal: 1.5-2%  $X_0 \Rightarrow$  factor 2 reduction wrt. LHC

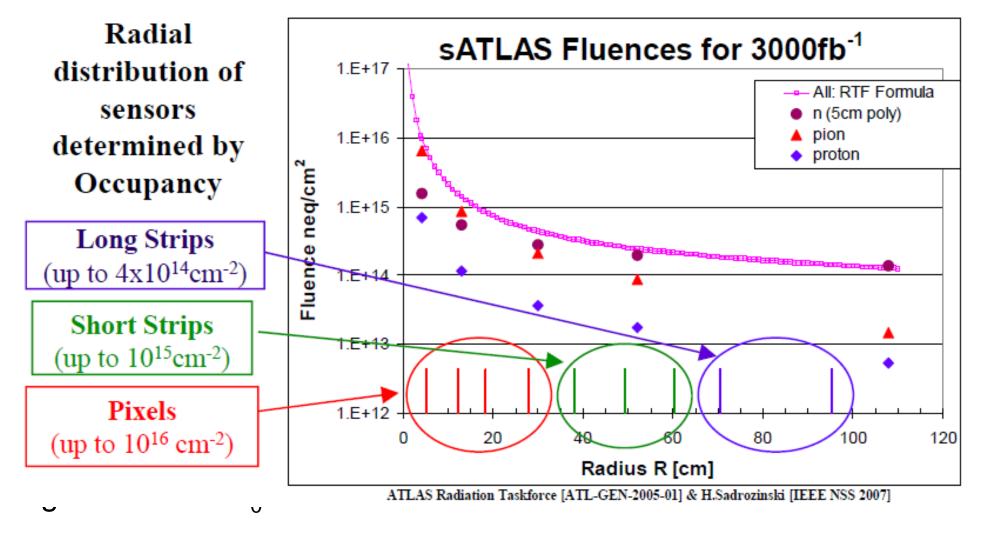

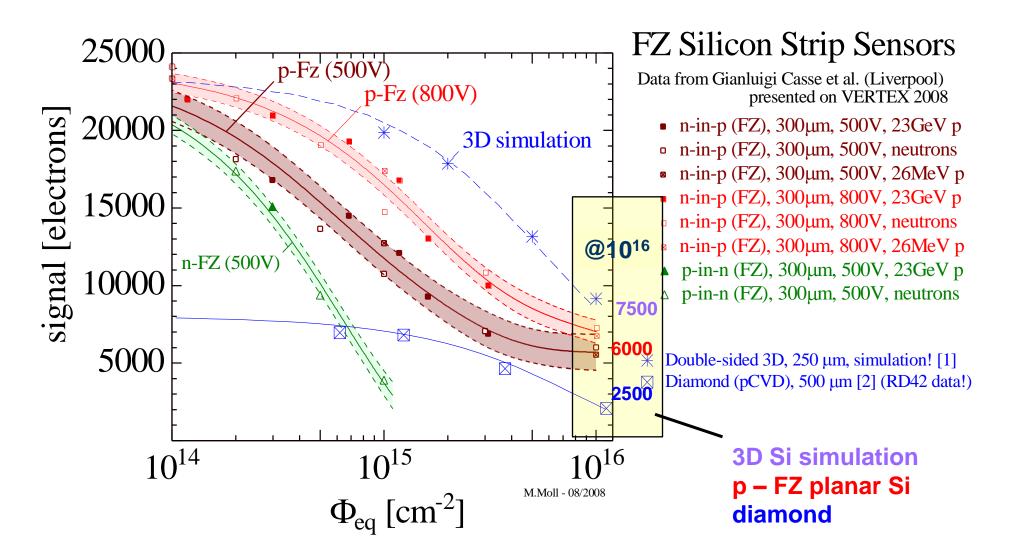

# sLHC Sensor R&D

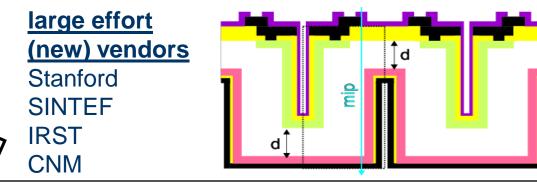

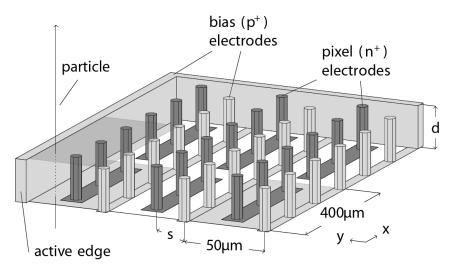

# **3D** silicon

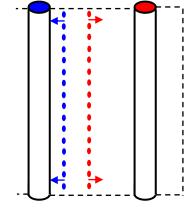

3D collaboration: C. da Via', S. Parker et al.

Technique: Deep Reactive Ion Etching (DRIE)

track parallel to electrode

**3D silicon**

- $\checkmark$  shorter drift distance  $\rightarrow$  fast

- ✓ lower voltages

- $\checkmark$  better radiation tolerance

- $\checkmark$  sensor edge can be an electrode

- inefficient in area of electrode manufacturing & costs = ?

LHeC-Workshop, 9/2/2008 – N. Wermes, Bonn

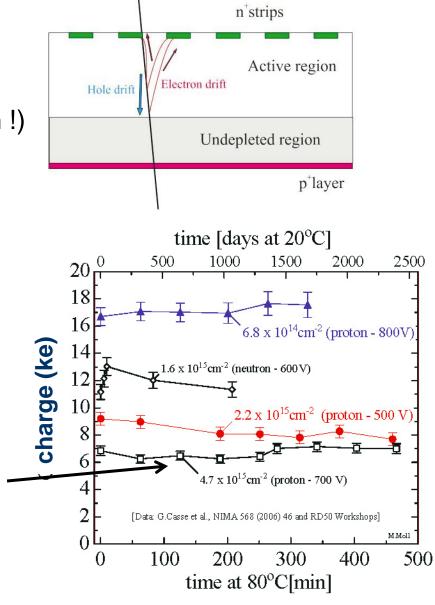

planar Si

## sLHC Sensor R&D

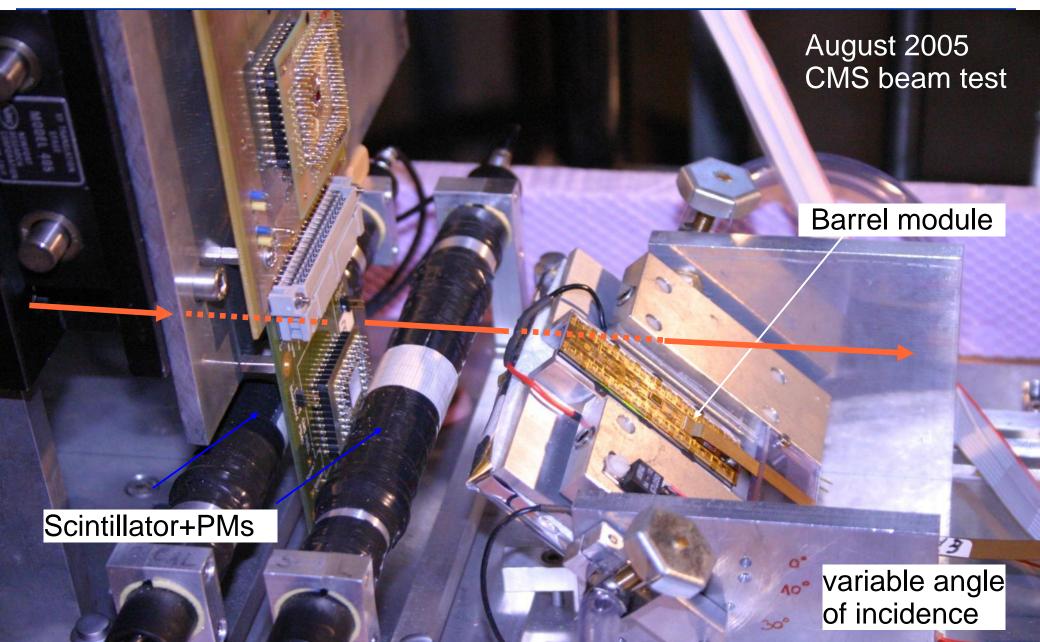

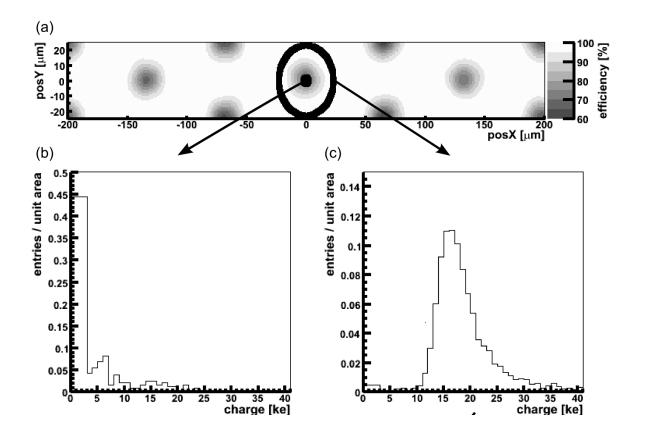

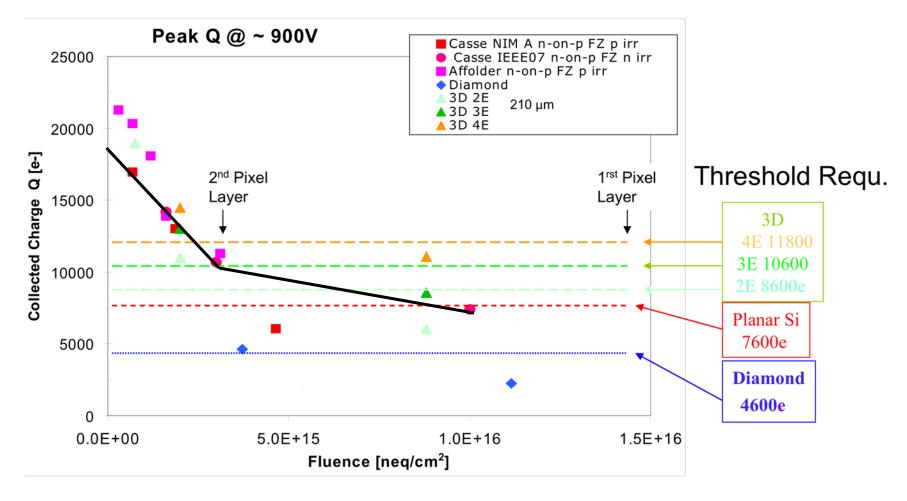

3D: test beam results

- Stanford devices, unirradiated

- pixel electronics (ATLAS FE-I3)

3E device = 3 electrodes/pix

$$\checkmark$$

V<sub>depl</sub> ~ 10 V

M. Mathes et al., IEEE TNS 2008 (accepted)

✓ efficiency 95.6% (0° tracks) 99.9% (15° tracks)

✓ spatial resolution as for planar pixels (~12 µm)

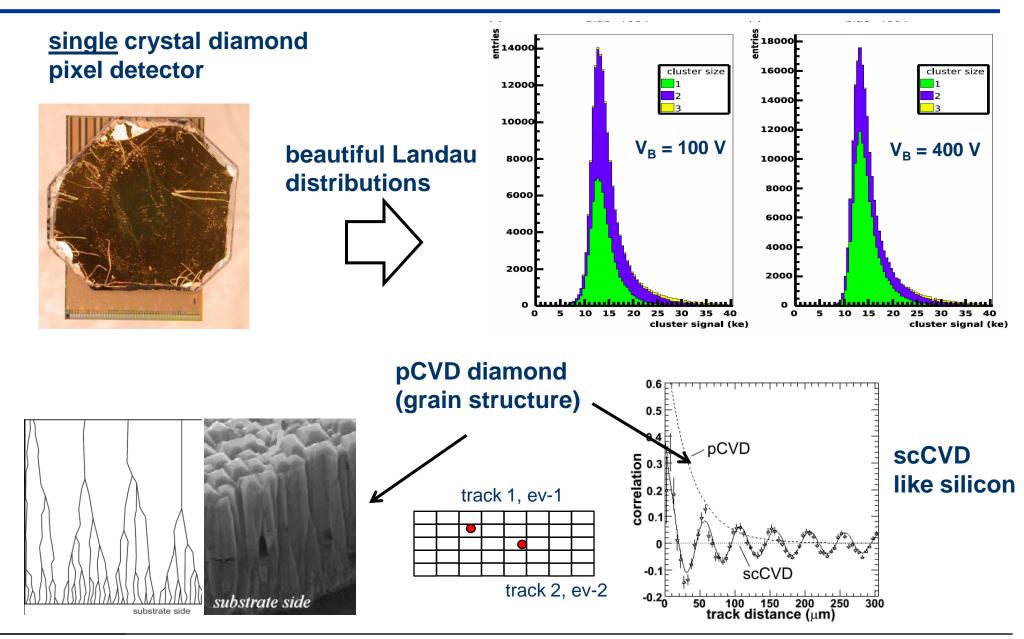

#### diamond (poly crystalline and single crystal)

RD42 collaboration H. Kagan, P. Weilhammer et al.

#### ✓ has finally become competitive (to Si)

✓ large band gap (x5) → no leakage current → no shot noise

✓ smaller  $\epsilon_r$  (x 0.5) → lower input capacitance → lower thermal and 1/f noise

✓ small Z=6 → large radiation length (x2 in g/cm<sup>2</sup>)

✓ narrower landau distribution (by 10%)

$\checkmark$  excellent thermal conductivity (x15)  $\rightarrow$  use as cooling structure

♦large w<sub>i</sub> (x 3.6) → small signal charge

fabrication more involved (wafer production, cutting) ... but "pixellation" almost trivial

using pixel-specific ENC formulae (CSA+filter) and measurements with 100 GeV  $\pi$

S/N per 0.1%  $X_0 \rightarrow$  Si : diamond  $\approx$  1 : ~1.4

✓ poly-CVD has been turned into 16 chip ATLAS modules

✓ sc-CVD sensors of few cm<sup>2</sup> size used as pixel detectors

### sLHC Sensor R&D

## sLHC Sensor R&D

# planar sensor R&D

- technology of choice for larger area (costs !)

- increase radiation tolerance (10<sup>16</sup> cm<sup>-2</sup> tough !)

- increase active area fraction

- large activity on Si materials

- -FZ/(M)CZ

- -p-type bulk (no type inversion)

- <u>trend</u>: n<sup>+</sup> on n → n<sup>+</sup> on p (FZ/MCZ)

- pixel electrodes on junction side

- single sided wafer processing (cost!)

- no reverse annealing for CCE meas.

- ~30% CC @ 5 x 10<sup>15</sup> cm<sup>-2</sup> (~7000 e<sup>-</sup>)

#### Pixels at sLHC: radiation tolerance

note: n<sub>eq</sub> (Si) normalization not correct for diamond & diamond better in S/N terms

### a personal opinion

- 3D silicon and CVD diamond (especially scCVD) are attractive

- $\checkmark$  for small area pixel detectors (1<sup>st</sup> layer) where costs do not play a major role

- $\checkmark$  radiation hardness is the major issue

- ✓ S/N counts !

- high quality wafer production at vendors must still be shown

- scCVD diamond perhaps not an option on the sLHC time scale? (unfortunately)

- only small single chip pixel modules demonstrated for 3D and scCVD

- $\checkmark$  large pixel modules with pCVD diamond

- for outer layers (fluence <  $10^{15}$  cm<sup>-2</sup>, area >5 m<sup>2</sup>) planar detectors are the choice

- $\checkmark$  promising Si material studies

- building and radiation testing of real modules is due

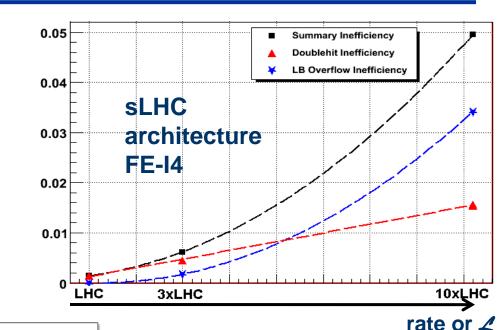

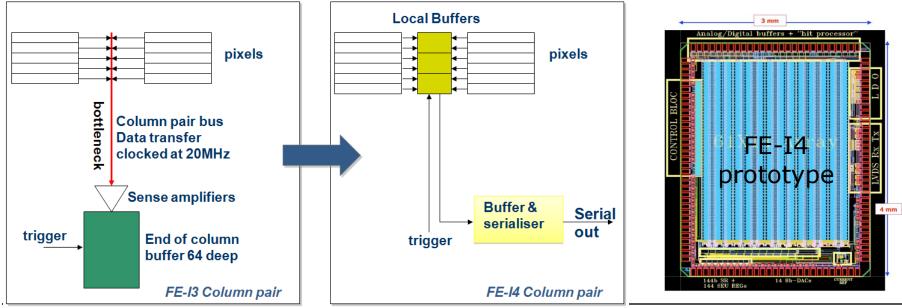

### sLHC data rates

Hit inefficiency rises steeply with the hit rate

**Bottleneck:** congestion in double column readout

⇒more local in-pixel storage (130 nm !)

>99% of hits are not triggered

⇒ don't move them

**1-**ε

LHeC-Workshop, 9/2/2008 - N. Wermes, Bonn

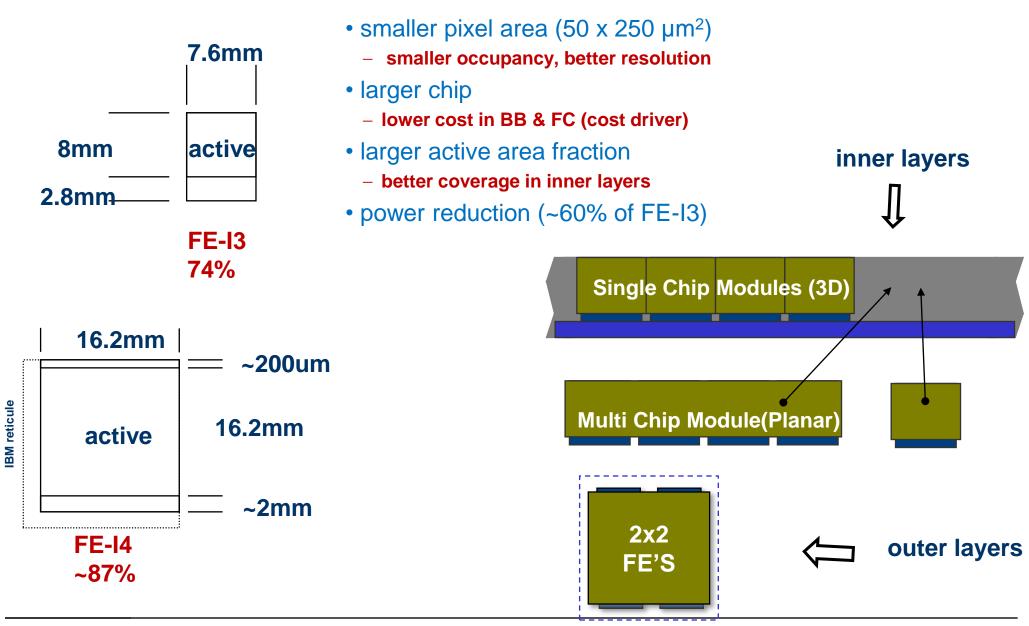

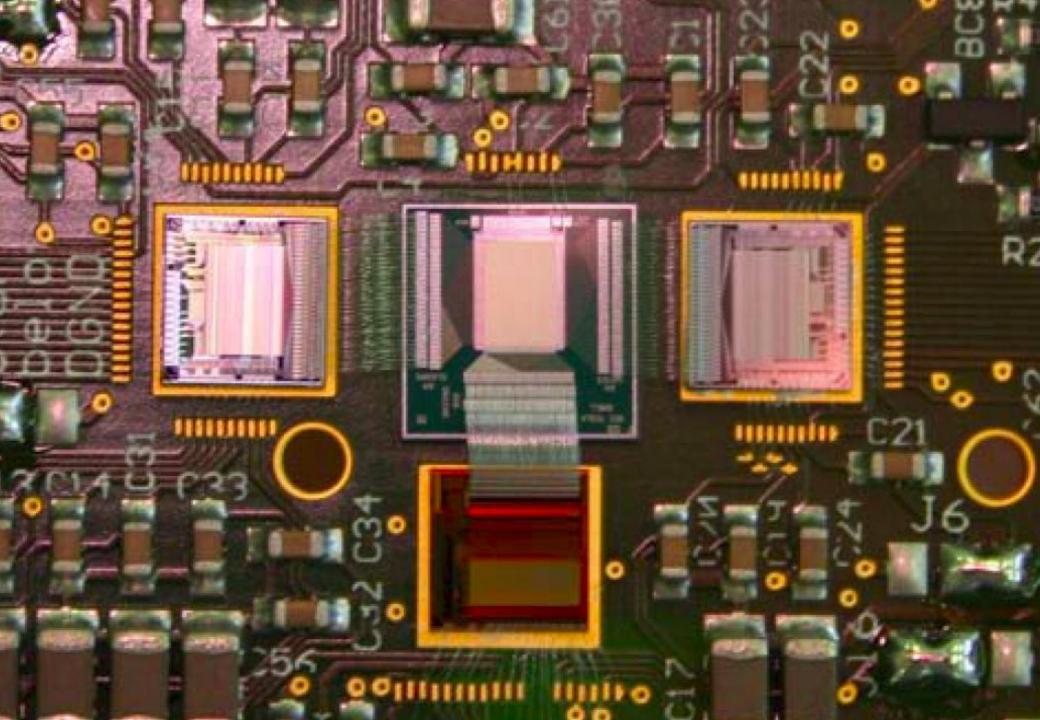

### Hybrid Pixel: sLHC FE - Chip and Modules

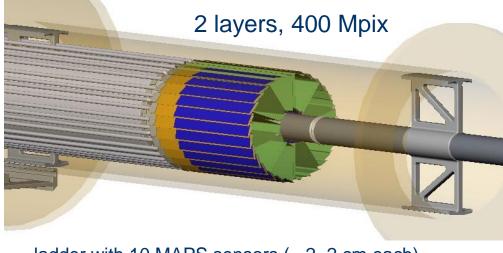

# (semi-) Monolithic Pixels STAR@RHIC, superBelle, ILC

## (Semi-) Monolithic Pixels Overview

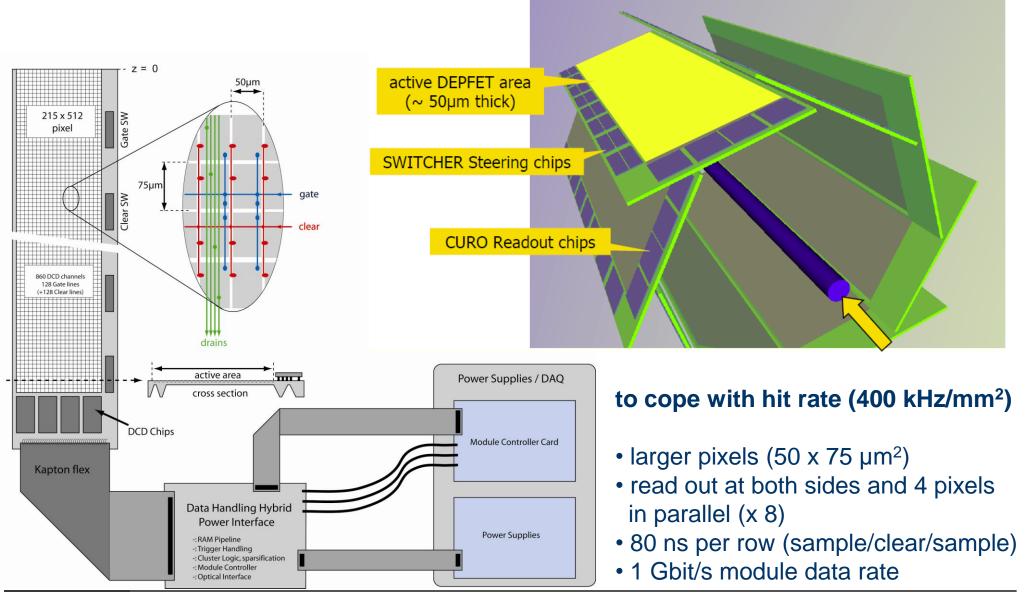

#### • **DEPFET** Pixels

- one transistor in pixel bulk

- Q-collection in fully depleted bulk

- R&D (for ILC) since > 10 years

- recently (2008): a 2 layer detector for superBelle

#### • Monolithic Active Pixels (MAPS-epi)

- Q collection in thin epi-layer

- need tricks for full CMOS

- R&D (for ILC) since ~ 10 years

- 2 (or 3) layer detector for STAR@RHIC

#### Monolithic Active Pixels (MAPS-Sol)

- full CMOS in active area

- Q collection in fully depleted bulk

- R&D started 2006

# will show selection of current efforts

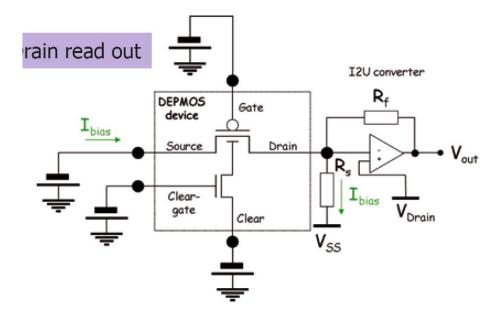

# **DEPFET** pixels

- p-channel MOSFET in pixel on a fully depleted bulk

✓ large signal

- ✓ fast collection

- ✓ small pixels (24 x 24 µm<sup>2</sup>)

- Internal gate (IG): deep (~1 $\mu m$ ) n-implant is potential minimum for e-

- Signal electrons accumulate in IG and modulate the transistor current ( $g_q \sim 400 \text{ pA/e}^-$ )  $\checkmark \text{ low } C_{\text{in}}$ , internal amplification  $\rightarrow$  low noise

- Accumulated charge removed by CLEAR ("reset")

- ✓ multiple R/O possible

- external reset needed (no reset noise if CLEAR complete)

- Transistor off during signal collection

✓ low power

- R/O of the (current) signal at transistor drains

steering & signal processing by external ICs

Collaboration: Bonn, Heidelberg, Karlsruhe, MPI Munich, Prague, Valencia

### DEPFET pixels: "rolling shutter" frame R/O

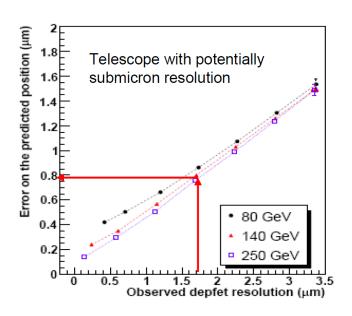

### **DEPFET** pixels: some features

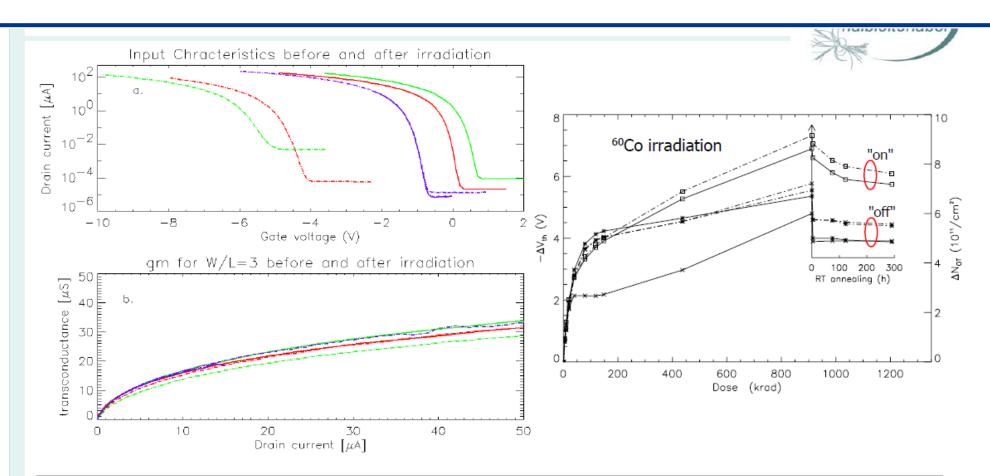

after 0.9 Mrad  ${}^{60}$ Co long shaping =10 µs ENC = 3.5 e<sup>-</sup>  ${}^{55}$ Fe

2000

ounts/channe

energy [eV]

- irradiation (0.9 Mrad γ, 3 x 10<sup>12</sup> p/cm<sup>2</sup>, 2 x 10<sup>11</sup> n/cm<sup>2</sup>)

- threshold shifts (~4 V) can be compensated (note: only 1 transistor per pixel)

- leakage current increase  $\rightarrow$  20 95 e<sup>-</sup>

- space resolution: < 2 μm

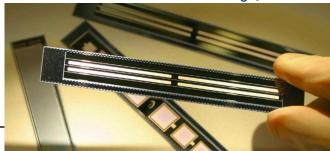

- material: < 0.15% X<sub>0</sub> per detector layer

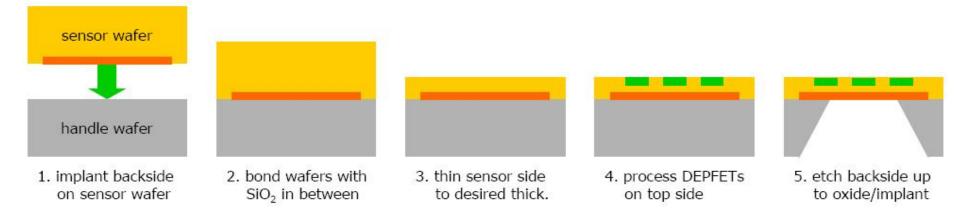

proven thinning process (anisotropic deep etching)

LHeC-Workshop, 9/2/2008 – N. Wermes, Bonn

#### Developments are for ILC $\rightarrow$ superBelle

#### low noise

- 1.6  $e^{\scriptscriptstyle -}$  for long shaping times (µs),

- goal: ~200e for fast R/O

- for ILC/superBelle R/O speeds (~12 MHz line rate)

- S/N = 120 for 450 µm thick sensors (test beam)

- $\rightarrow$  goal S/N = 20 40 for 50 µm thick sensors

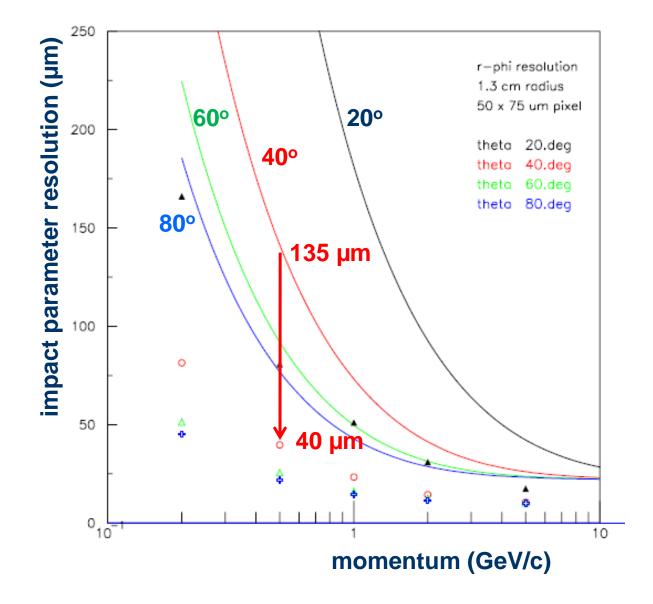

## **DEPFET** pixels for superBelle

LHeC-Workshop, 9/2/2008 - N. Wermes, Bonn

#### **DEPFET** pixels for superBelle: IP - resolution

#### simulation

# MAPS-epi

Meynants, Diericks, Scheffer, SPIE 3410:68-76 (1998) R. Turchetta, NIM-A 458:677-689 (2001)

<u>many activities</u>: France, UK, US, Italy (MAPS, CAPS, FAPS .....)

| MAPS vs Hybrid Pix  | MAPS | Hybrid<br>Pixel<br>Sensors |

|---------------------|------|----------------------------|

| Granularity         | +    | -                          |

| Material budget     | +    | -                          |

| Readout speed       | +    | ++                         |

| Radiation tolerance | +    | ++                         |

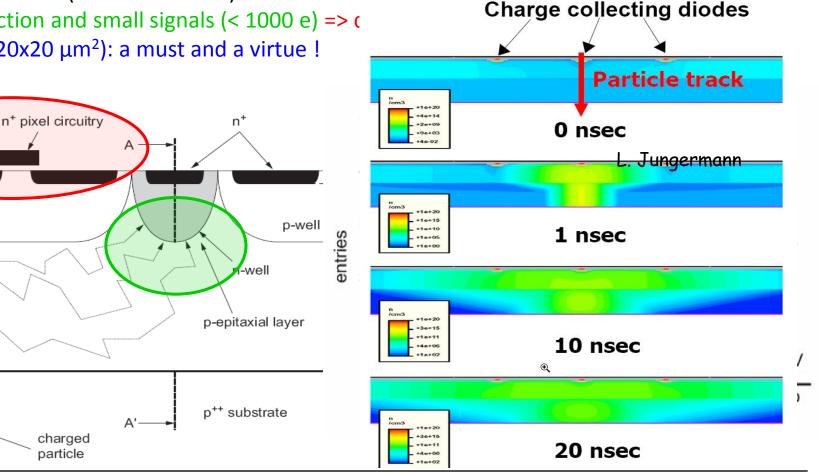

- Sensor and signal processing are integrated in the same silicon wafer

- ✓ commercial CMOS technology standard

- Signal created in low-doped epitaxial layer (~10-15 μm, e.g. AMS 0.35 μm)

- MIP signal <1000 electrons → challenge for IC design

- Q collection by thermal diffusion (~100 ns), reflective boundaries at p-well and substrate, collected at n-well/epi junction

→ charge spread to several pixels

- 100% fill-factor (note definition), thin (~50 μm)

- small pixel sizes (pitch 20 30 µm):

→ a must and a virtue → few µm resolution !

- Only NMOS transistors possible in active area (due to n-well/epi collection diode)

# MAPS-epi

Meynants, Diericks, Scheffer, SPIE 3410:68-76 (1998) R. Turchetta, NIM-A 458:677-689 (2001)

#### many activities: France, UK, US, Italy (MAPS, CAPS, FAPS .....)

| MAPS vs Hybrid Pix  | MAPS | Hybrid<br>Pixel<br>Sensors |

|---------------------|------|----------------------------|

| Granularity         | +    | -                          |

| Material budget     | +    | -                          |

| Readout speed       | +    | ++                         |

| Radiation tolerance | +    | ++                         |

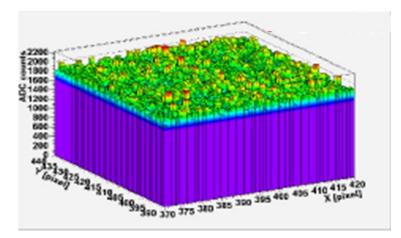

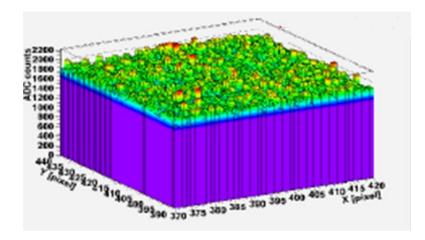

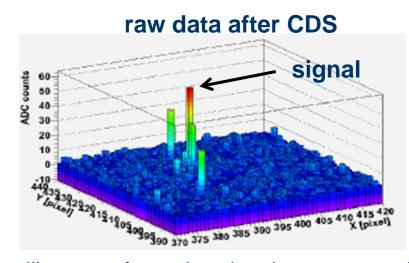

### MAPS-epi: CDS correlated double sampling readout

1<sup>st</sup> frame

#### 2<sup>nd</sup> frame

#### still: correct for pedestal and common mode

#### eliminate

- base levels

- 1/f noise

- fixed pattern noise

#### offline → goal: on-chip

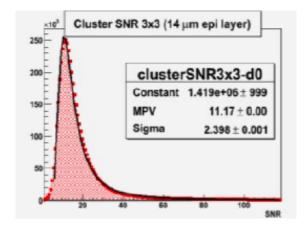

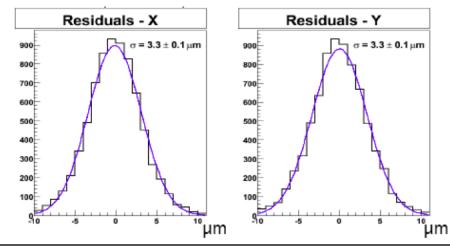

### MAPS-epi: EUDET telescope

#### DESY, CEA, CERN, CNRS, MPI, Bonn, Heidelberg, Geneva, Bristol, INFN

**S/N ~ 11**

3.3 µm resolution

LHeC-Workshop, 9/2/2008 - N. Wermes, Bonn

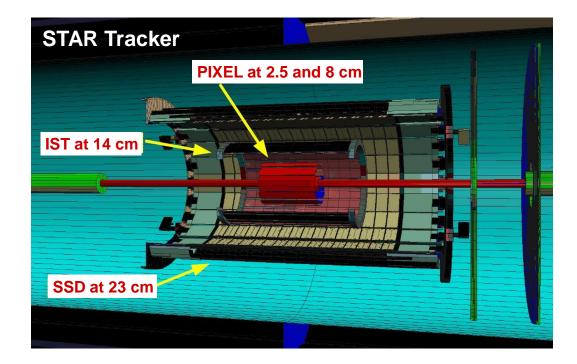

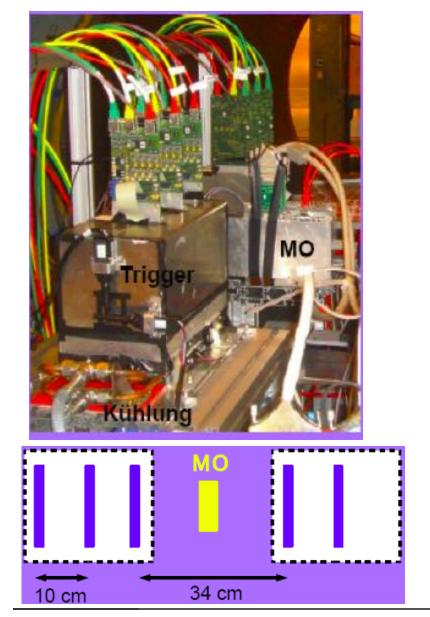

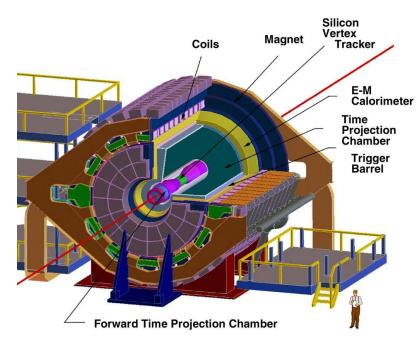

# MAPS-epi → meeting the challenge: **STAR@RHIC**

ladder with 10 MAPS sensors (~ 2 2 cm each)

# special feature goals pitch 20 – 30 $\mu$ m $\rightarrow$ spatial resolution < 10 $\mu$ m

50  $\mu$ m sensors  $\rightarrow$  0.28% radiation length/layer (!)

small power budget  $\rightarrow$  100 mW/cm<sup>2</sup>

integration time goal: <200  $\mu$ s (@ L= 8×10<sup>27</sup>)

must sustain 300 krad/yr and ~ $10^{13}$ /cm<sup>2</sup> n<sub>eq</sub> /yr

<u>groups</u> LBNL-Berkeley IPHC/DAPHNIA France

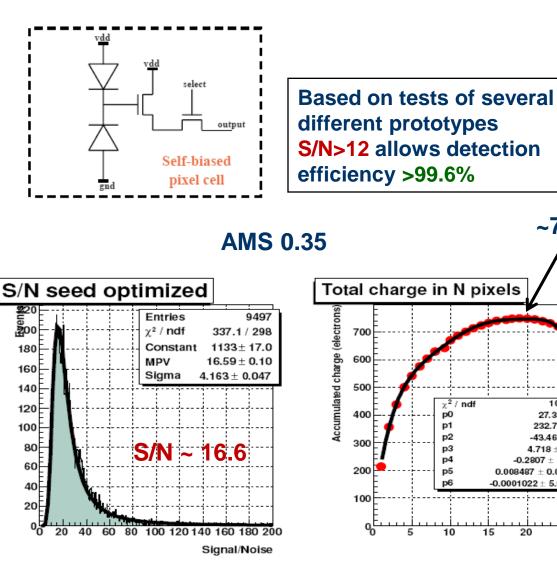

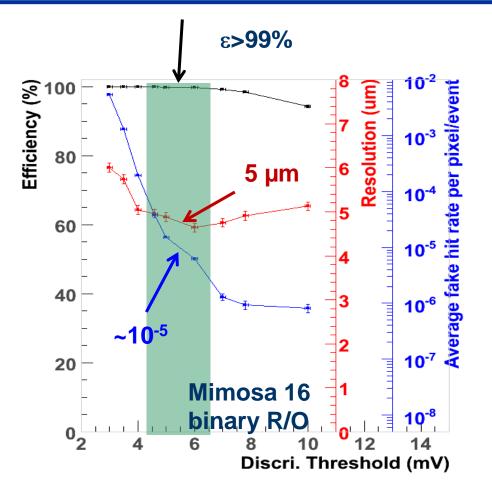

## MAPS-epi @STAR: current status

#### several prototypes

- MimoSTAR 2&3 (AMS 0.35)

- Mimosa 8/16 (TSMC 0.25/AMS 0.35)

#### tested features

- 25 µm pitch, 128 x 32 pix

- analog versus digital R/O digital faster (column parallel + MUX) but needs discriminators

- integration time still large (~ms) need 200 µs

- <u>on-chip</u> prototyped

- in-pixel CDS

- column level: discrimination zero suppression

- radiation:  $\rightarrow$  remove thick oxide near Q-collecting diode

Y. Degerli et al, IEEE TNS, vol 53, no 6, 2006, pp 3949 - 3955 Y. Degerli et al, IEEE TNS, vol 52, no 6, 2005, pp 3186 - 3193 ~750 e

100.8 / 18

$27.3 \pm 4.338$

$232.7 \pm 4.015$

$43.46 \pm 1.267$

$4.718 \pm 0.1816$

25

0.2807 ± 0.01294

0.008487 ± 0.0004458

-0.0001022 ± 5.916e-06

20

15

## MAPS-epi @STAR: current status

#### several prototypes

- MimoSTAR 2&3 (AMS 0.35)

- Mimosa 8/16 (TSMC 0.25/AMS 0.35)

#### tested features

- 25 µm pitch, 128 x 32 pix

- analog versus digital R/O digital faster (column parallel + MUX) but needs discriminators

- integration time still large (~ms) need 200 µs

- <u>on-chip</u> prototyped

- in-pixel CDS

- column level: discrimination

zero suppression

- radiation: → remove thick oxide near Q-collecting diode

#### achieved performance

Y. Degerli et al, IEEE TNS, vol 53, no 6, 2006, pp 3949 - 3955 Y. Degerli et al, IEEE TNS, vol 52, no 6, 2005, pp 3186 - 3193

## Main improvement R&D

1. improve the charge collection (speed and completeness)

2. go to "full" CMOS also in active area

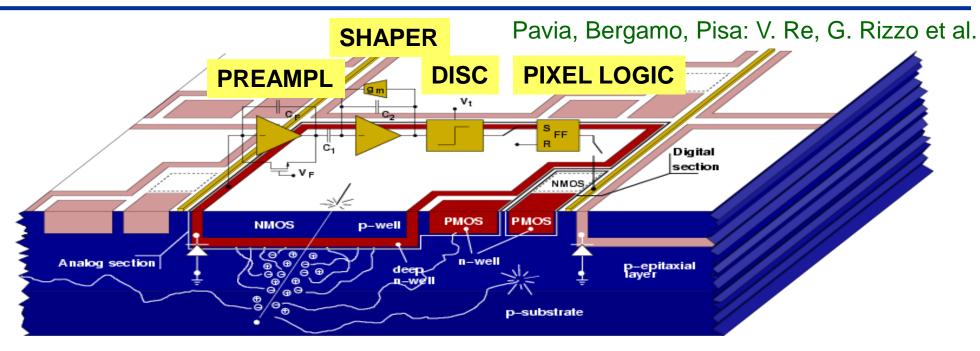

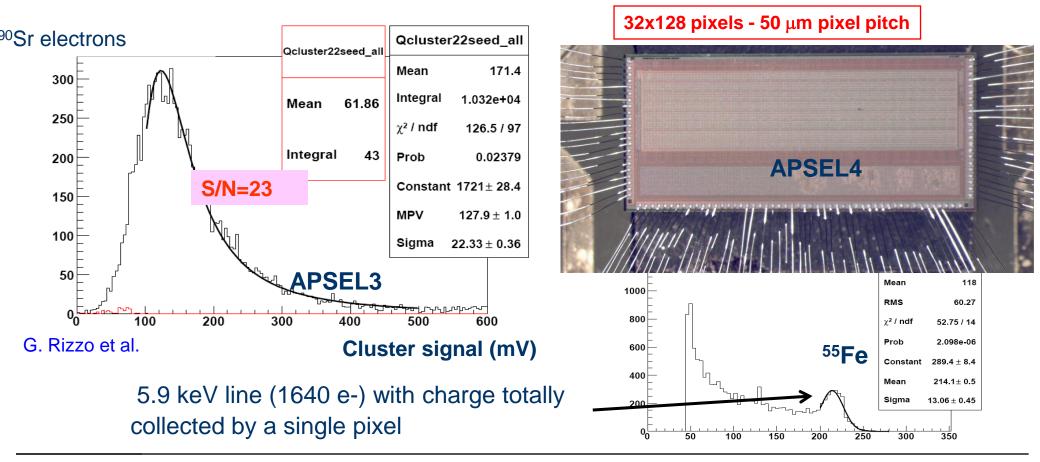

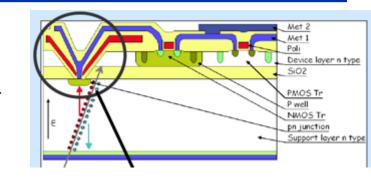

# MAPS-epi with deep n-well ( $\rightarrow$ enlarge the n-well diode)

• Extended Deep N-well collecting electrode (STM 130 nm triple well CMOS)

- ✓ obtain higher single pixel collected charge

- ✓ protect charge loss to competitive N-wells

- $\checkmark \Rightarrow$  can use PMOS transistors too

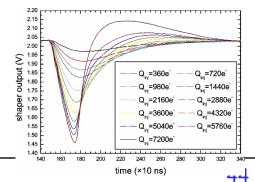

- ✓ complete single pixel processing chain (CSA + Shaper + Discr. + Logic) in active area

Fill factor (note definition) = DNW/total n-well area ~90% in the prototype structures

- Ambitious goal: a monolithic pixel sensor with similar readout functionalities as with hybrid pixels (sparsification, time stamping)

- Proof of principle with APSEL chip prototypes (STM 130 nm triple well CMOS)

- APSEL4: 32x128 matrix, sparse R/O and time stamping

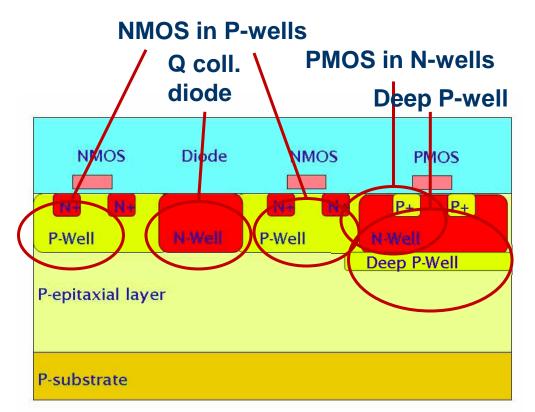

# MAPS-epi with deep p-well ( $\rightarrow$ shield the PMOS N-wells)

RAL, ICL, UBirmingham, J.A. Ballin, ..., R. Turchetta et al. Sensors (2008), ISSN 1424-8820

# INMAPS quadrupel well 0.18 µm CMOS process (6 metals)

- use deep p-implant (p-well) to shield the n-wells that contain PMOS transistors

- only diode n-well still exposed to charge from the epi-layer

- fill-factor is 100%

- deep p cannot be made too small

→ pixel size not too small

- several designs with full signal processing submitted (>150 transistors)

- e.g. CSA + shaper + comp. + logic

- 50 µm pixel pitch

- first prototype tests encouraging

- Q- collection in n-well diode increased by factor ~2

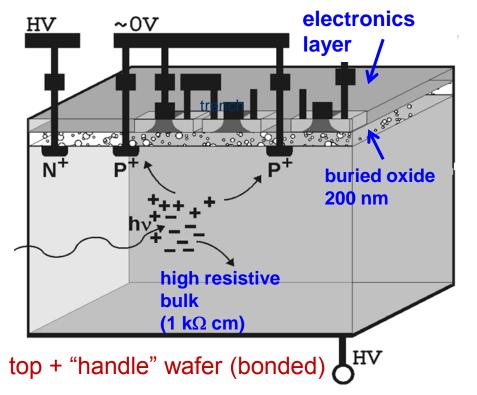

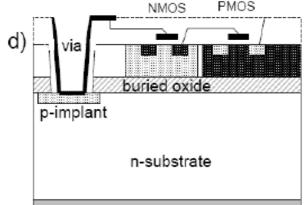

# **MAPS-Sol**

| MAPS              |     |     |

|-------------------|-----|-----|

| Sol vs epi        | ері | Sol |

| Granularity       | +   | +   |

| Material budget   | +   | +   |

| S/N               | -   | ++  |

| Level of maturity | +   | -   |

#### Sol

A thin Si layer (~100 nm) isolated with SiO<sub>2</sub> (each transistor in its own isolated island, shallow trench isolation, no junctions to bulk)

#### **MAPS-Sol:**

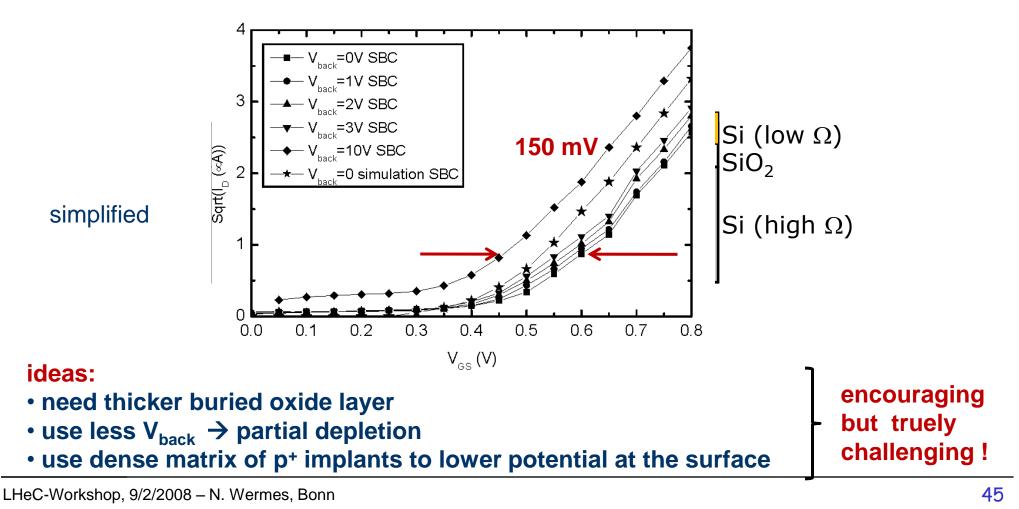

- A bonded wafer with high- $\Omega$  substrate + low- $\Omega$  top Si, separated by a buried oxide layer

- standard CMOS (NMOS, PMOS, MIM cap...) can be used

- ✓ efficient use of area for electronics

- vertical via contacts reaching through to implants in the high resistivity wafer

- ✓ no bump bonding

- ✓ small pixel size possible

- use of handle wafer in partial or full depletion determined by backside voltage

#### Full CMOS in active area charge collection in fully depleted bulk

LHeC-Workshop, 9/2/2008 – N. Wermes, Bonn

## **MAPS-Sol**

1995: F.X.Pengg, "Monolithic Silicon Pixel Detector in SOI Technology", PhD thesis, University of Linz, Austria, (1996)

2003: W. Kucewicz et al. Nucl.Instrum.Meth.A549:112-116,2005.

### **New initiative:**

```

FERMILAB (R. Yarema, G. Deptuch et al.)

+ Japan + Hawaii

```

with commercial vendors (not many !! ... "change in process flow") OKI (150 nm & 200 nm) & TSMC (250 nm)

## **Status**: prototype experience $\rightarrow$ feasilibility study

- many design variations submitted

- for HEP applications: single particle sensitivity for imaging applications: photon counting

- full blown CMOS electronics

CSA + shaper + discriminator + (counter)

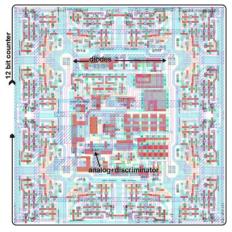

#### e.g.: 64x64 pix, 26 μm CSA + shaper + discr.

## the main problem: back gate effect

fully depleted high- $\Omega$  part couples into the channel  $\rightarrow$  acts as second gate  $\rightarrow$  substrate biasing leads to transistor threshold shifts

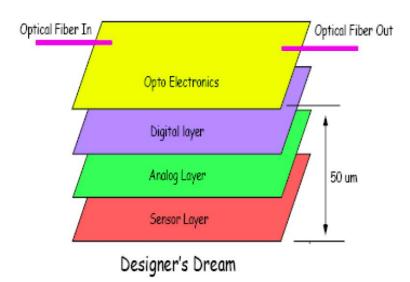

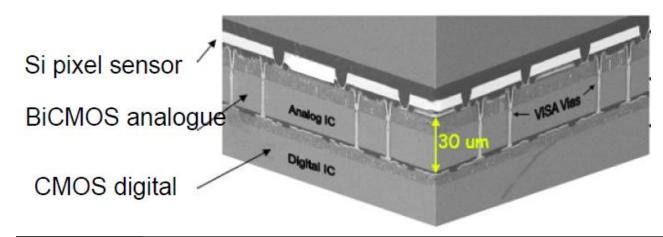

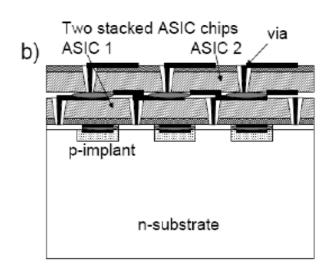

- several (tiers) of thinned semiconductor layers interconnected to form a monolithic unity

- different layers can be made in different technologies (high ohmic sensor, BiCMOS, deep sub-µ-CMOS, SiGe, opto-process, ...)

- driven by industry

- $\checkmark$  reduced R,L and C  $\rightarrow$  improves speed

- ✓ reduced interconnect power, x-talk

- ✓ reduced size

## first initiative @ Fermilab

France (many groups) Germany (MPI,Bonn) following

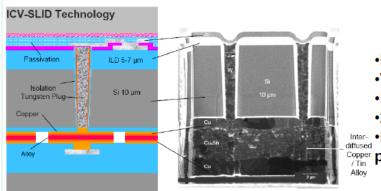

# **3D** integration

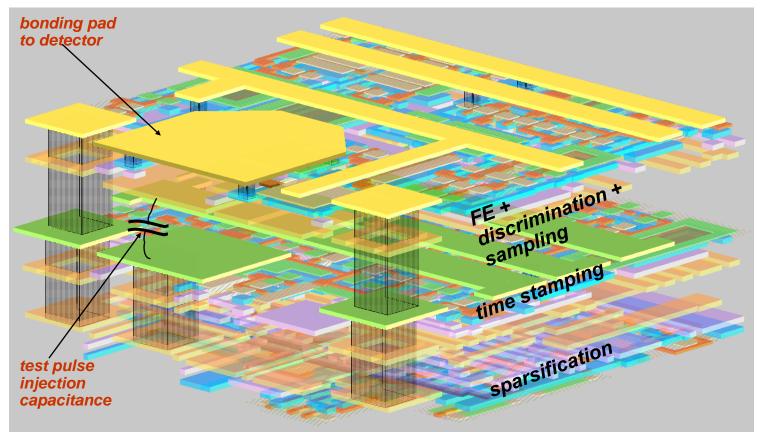

heavy R&D at Fermilab: R. Yarema, G. Deptuch et al. readout chip with time stamping and sparsification 3 tiers (no sensor yet) attempts with several foundries: Tezzaron, Chartered, IZM, RTI, Ziptronix, MITLL

## VIP: layout view with 3D Design Tool by Micro Magic:

# **3D** integration

## first step to 3D integration is ..

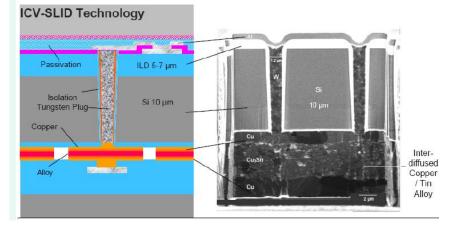

ICV = Inter Chip Vias TSV = Through Silicon Vias

- hole etching and chip thinning

- via formation with W-plugs

- 2.5  $\Omega$ /per via

- no significant impact on chip performance (MOS transistors).

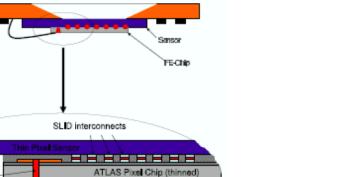

MPI-Munich & IZM/Munich

- build demonstrator using ATLAS pixel chip and pixel sensors made

Bonn & IZM/Berlin –use TSV for sLHC ATLAS module concepts

Post processed bond pad

(services)

Original bond pad

Wire bond connection

# Conclusions

## standard

AISC -chip

bump

p-implant

Active epi-laver

a)

## future

# Hybrid pixels

- matured with LHC

- only choice for sLHC

- needs heavy R&D on:

- sensor materials

- ICs and modules

- 3D integration

# **Monolithic**

- first real detectors in focus

- the way to the dream is coming closer

- needs heavy R&D on:

- full (CMOS) integration

- radiation tolerance

n-substrate

## Thanks for materials and discussions

- -Woitek Dulinski

- -Michal Szelezniak

- -Grzegorz Deptuch

- -Laci Andricek

- -Renato Turchetta

- -Hans-Günther Moser

- -Hans Krüger

- -Fabian Hügging

- -Marlon Barbero

- -David Arutinov

- -Giovanni Darbo

- -Maurice Garcia-Sciveres

- -Cinzia da Via'

- -Valerio Re

- -Harris Kagan

# **Backup Slides**

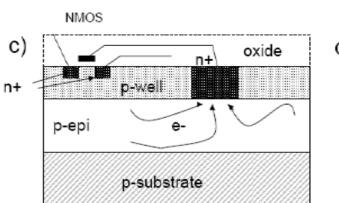

## **CMOS** Active Pixels

- charge coll. in several µm thin epi-layer by thermal diffusion to n-well/epi junction

- p-wells and substrate highly doped  $\rightarrow$  charges kept between reflection boundaries

- signals processed by standard CMOS circuitry integrated on sensor

- only nMOS in active area (due to n-well/epi collection diode)

- Q-collection time ~100 ns (due to diffusion)

- incomplete Q-collection and small signals (< 1000 e) => (

- small pixel sizes (< 20x20 μm<sup>2</sup>): a must and a virtue !

p-well

e.

B'-

## **Making thin Sensors**

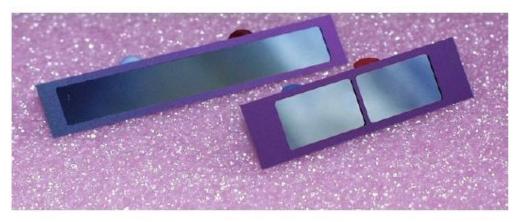

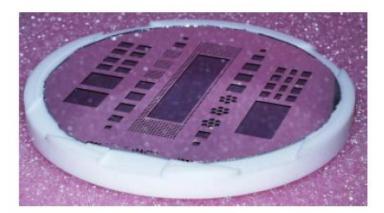

A novel technology to produce detectors with thin active area has been developed and prototyped (L. Andricek)

first 'dummy' samples: 50µm silicon with 350µm frame

thinned diode structures: leakage current: <1nA /cm<sup>2</sup>

| irradiation            | TID / NIEL fluence                             | $\Delta V_{th}$ | g <sub>m</sub> | I <sub>Leak</sub> in int. gate at RT <sup>(*)</sup> |

|------------------------|------------------------------------------------|-----------------|----------------|-----------------------------------------------------|

| gamma <sup>60</sup> Co | 913 krad / ~ 0                                 | ~-4V            | unchanged      | 156 fA                                              |

| neutron                | ~ 0 / 2.4x10 <sup>11</sup> n/cm <sup>2</sup>   | ~ 0             | unchanged      | 1.4 pA                                              |

| proton                 | 283krad / 3x10 <sup>12</sup> n/cm <sup>2</sup> | ~-5V            | ~ -15%         | 26 pA                                               |

(\*) 5..22 fA non irrad.

#### LHeC-Workshop, 9/2/2008 - N. Wermes, Bonn

Hartmut F.-W. Sadrozinski, LBL Pixel Upgrade, May 22, 2008

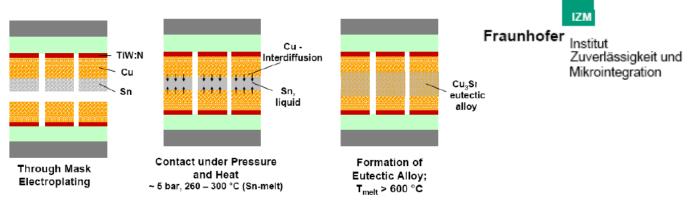

## **IZM SLID Process, ICV**

#### Metallization SLID (Solid Liquid Interdiffusion)

Alternative to bump bonding (less process steps "low cost" (IZM)).

Small pitch possible (< 20 μm, depending on pick & place precision).</li>

Stacking possible (next bonding process does not affect previous bond).

Wafer to wafer and chip to wafer possible.

#### ICV = Inter Chip Vias

Hole etching and chip thinning

Via formation with W-plugs.

Face to face or die up connections.

2.5 Ohm/per via (including SLID).

Interdiffused Copper performance (MOS transistors). Allow