## Status of CMS trigger upgrade (phasel)

P. Sphicas

Meeting with LHCC referees

June 3, 2014

#### **Outline**

- Trigger Upgrade Strategy

- Calorimeter trigger

- Muon trigger

- Level-1 software (online and offline)

- Outlook

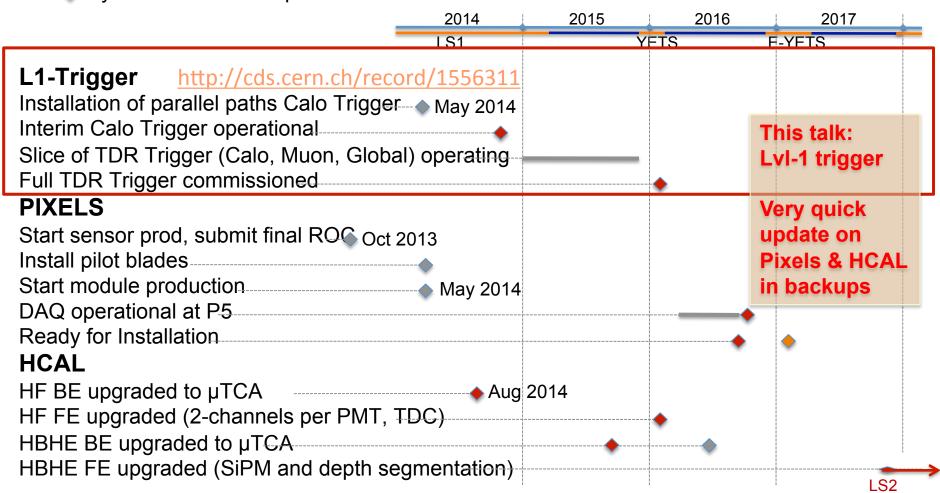

## CMS phase1 work in LS1→LS2 period

- Major milestone

- System comes into operation

## **Trigger Strategy**

#### Level-1 Trigger: reminder of plan

- Upgrade entire Level-1 trigger for

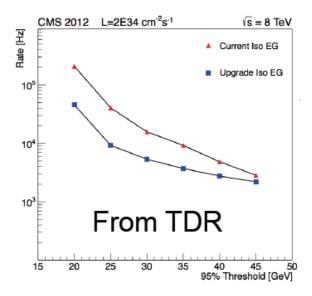

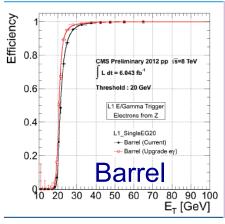

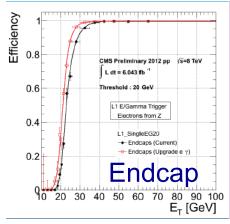

- Improved signal efficiency and background rejection for electron and tau triggers.

- Improved background rejection for muon triggers via improved momentum resolution.

- Pile-Up subtraction at Level-1

- Enable parallel commissioning of new trigger while keeping legacy (Run I) trigger fully operational

- The legacy trigger can be operated sufficiently well up to 40 PU (L=7.5x10<sup>33</sup> @ 50 ns)

- Furthermore: commission an interim calorimeter trigger (Stage-1) already in March 2015 to give

- Improved electron and tau triggers

- First algorithms for Pile-Up subtraction; needed for HI run.

- Complete commissioning, turn on new trigger: Jan 2016

#### Level-1 Trigger: reminder (II)

#### Electron isolation

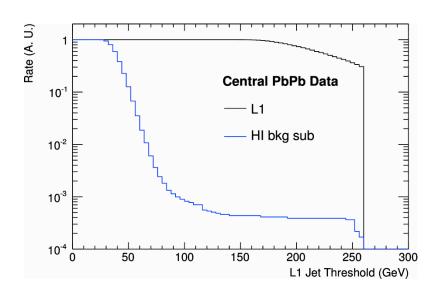

#### Heavy lons

Triggering on jets

without pileup

subtraction means

triggering on ~all

events

## **Calorimeter Trigger**

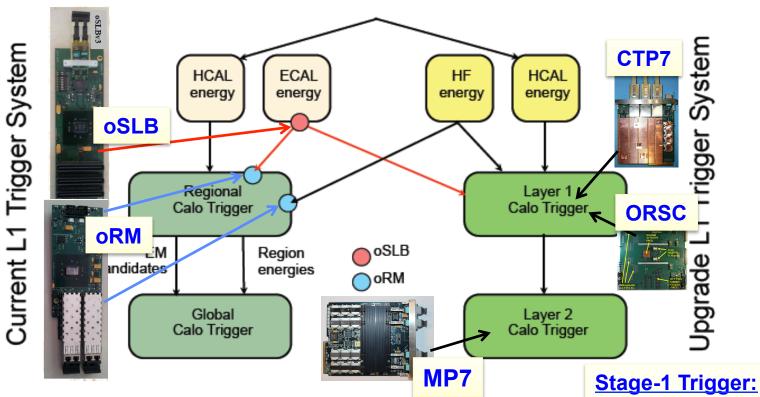

#### Calorimeter triggers in 2015 & 2016

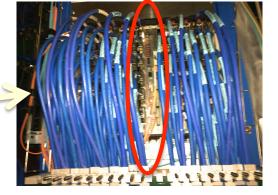

576 Optical Serial Link Boards (oSLBs)

565 Optical Receiver modules (oRMs)

allow commissioning new trigger in

parallel with operation of legacy trigger.

Links run at 4.8 Gbps synchronous mode.

oRMs & oSLBs installed.

Ongoing: fiber installation (and commissioning)

RCT + 18 ORSC →

2 MP7 (Layer-2)

2016 Trigger:

36 CTP7s (Layer-1) →

#### oSLB/oRM project: status & plan

- Early 2014: a new plan for production, testing and commissioning of the calo trigger optical interface; aims to complete the project by July CMS Global Run.

- 650 oSLBs and 650 oRMs were produced and tested by early April 2014.

- A detailed program of integration tests was carried out at Bld. 904 which insured reliable connectivity both with the legacy and the upgraded trigger as well as the HCAL electronics.

- A small number of crates of the new system took part successfully in the CMS Global Run Early in April 2014.

- Installation activities started on schedule in April 2014 and are proceeding according to plan. All devices have been already installed.

- Project is expected to be completed on schedule and participate in the July 2014 CMS Global Run.

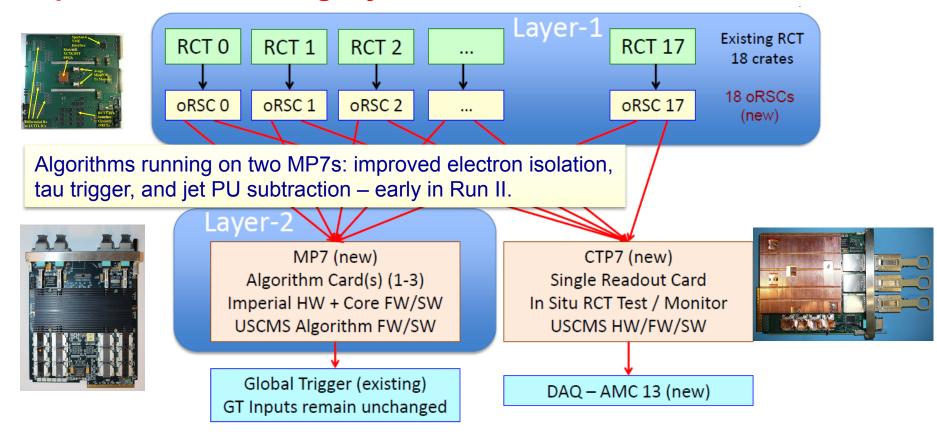

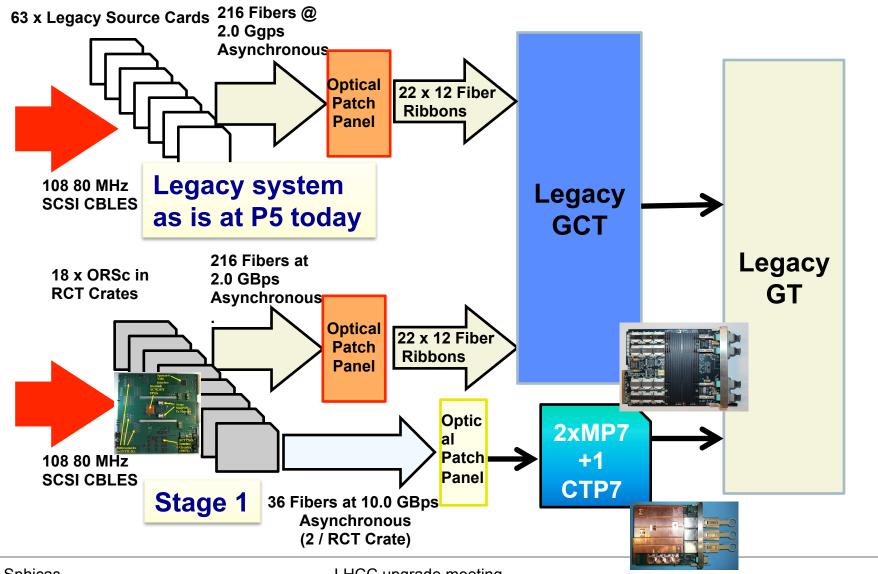

## **Stage-1 Calorimeter Trigger**

Stage-1: Regional Calorimeter Trigger (RCT) copper outputs (108 SCSI ECL 80 MHz cables) ® converted to 10 Gbps & 2Gbps optical signals which can drive Stage-1 MP7 processors and Legacy GCT.

#### Legacy trigger & Stage-1 coexist; Switching under software control

#### Calorimeter Trigger: stage 1 status

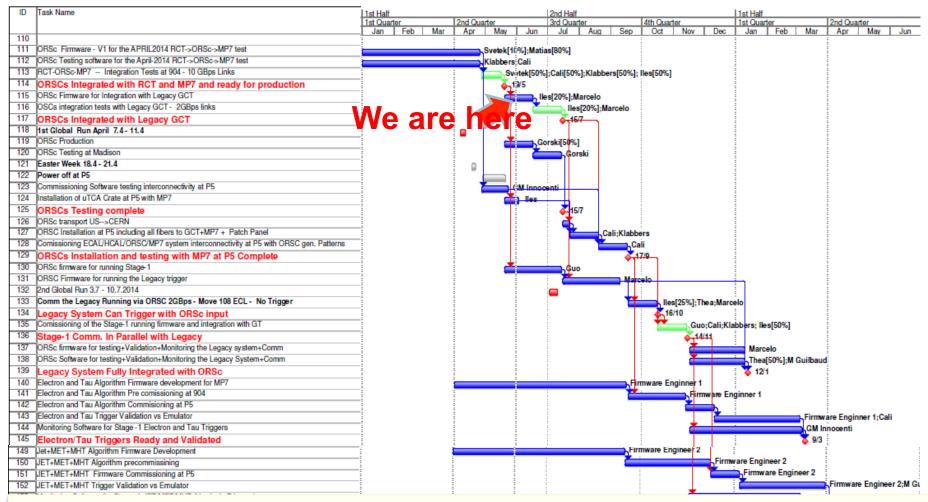

A Project Manager, detailed plan and milestones (in red) are in place. Project completion date: 31.3.15. Extra resources in firmware (4 FTE) have been found and are already in place to insure that this goal is met. Project is on track and met its first milestone (successful data transmission at 10 Gbps).

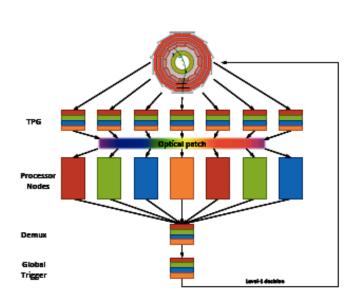

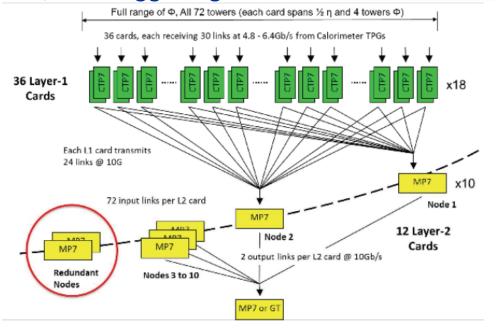

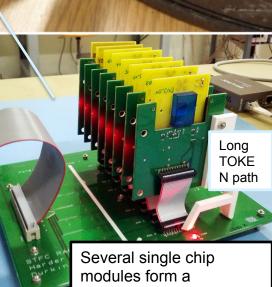

## Full Calo trigger upgrade (2016)

- Time Multiplexed Trigger design in two layers

- Enhanced Algorithm Flexibility

- Calorimeter data at full granularity

- Modular design, easy to upgrade and increase capabilities

- Layer 1: 36 CTP7 Processors

- Large Switching Array + some processing: constructs evts

- Layer 2: 12 MP7 Processors

- Each Processor receives full evts; runs trigger algorithms

CTP7 & MP7: Xilinx Virtex-7 10G links

## Calo trigger hardware (status)

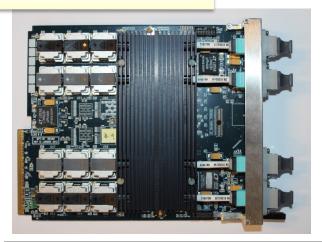

- MP7 (Calo Trigger Layer-2): 72 I/O Optical Links at 10 G, Virtex-7 690 FPGA

- In production; first 2 cards at CERN

- Large number of pre-production cards already in use at CERN and elsewhere

- Firmware in advanced state

- CTP7 (Calo Trigger Layer-1): 67 Rx, 48 Rx Links at 10 G Virtex-7 690 FPGA

- Under prototype testing since Jan 2014.

- One prototype at CERN since Apr 2014

- 3-4 preproduction prototypes Summer 2014

- Production to start in Oct 2014

- All Cards at CERN by end Mar 2015

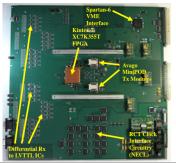

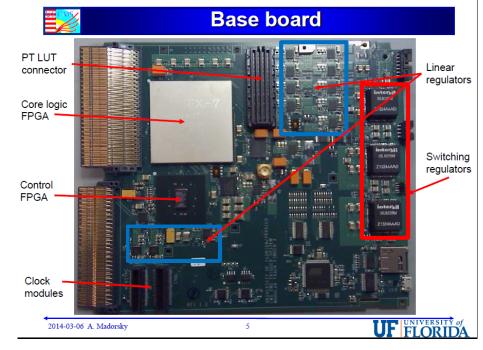

- ORSC (Stage-1 Layer-1): Xilinx Kintex-7 FPGA

- Production Started; installation starts end Jul

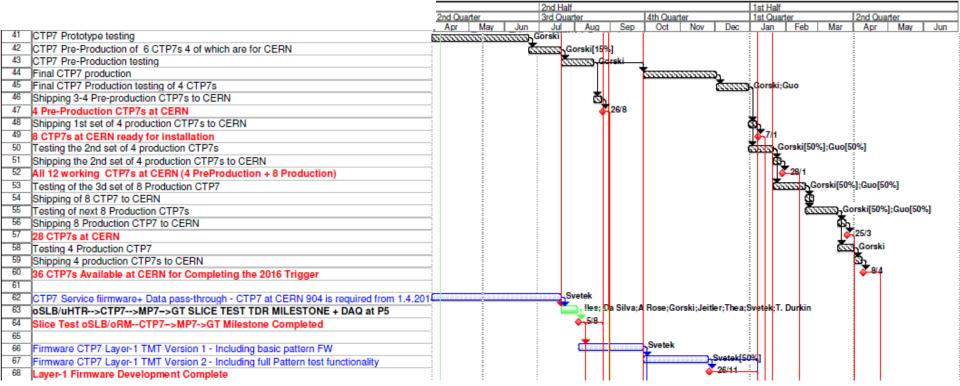

## Calorimeter trigger schedule (to 2016)

- Top-level Calorimeter Trigger Schedule: (details in back-slides)

- MP7 production complete: Jun 2014

- CTP7 production complete: Mar 2015

- Installation of Layer-2 hardware in Jul 2014

- Installation of Calorimeter Trigger: complete by Apr 2015

- Calo Trigger ready for parallel data taking: Jun 2015

- Detailed testing using data to be completed in Jan 2016 and commence operations as main CMS calorimeter trigger

- En route to this schedule: Calo-trigger Slice Test in July 2014 at CERN: major test of the calorimeter trigger and involves:

- ECAL and HCAL back-end data sources (oSLB and uHTR)

- The 2 TMT Trigger Layers: Layer-1 (CTP7) and Layer-2 (MP7)

- Data will be transmitted from the calorimeter back-end all the way to the calorimeter trigger output to the Global Trigger.

- It will test:

- Synchronization of the calorimeter trigger data chain

- First Version of firmware for Layer-1 and Layer-2 TMT

- TMT Trigger algorithms

## **Muon Trigger**

#### **Muon Trigger**

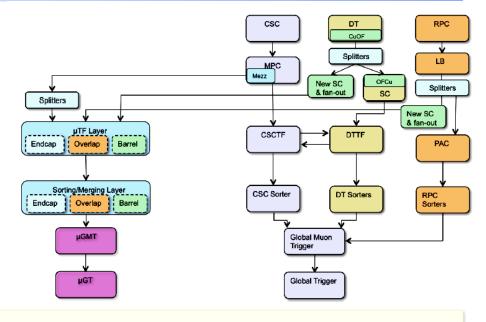

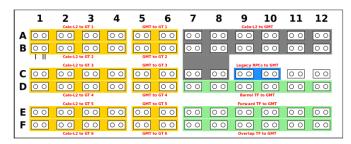

# Upgraded trigger consists of 3 muon Track Finders: Endcap, Overlap and Barrel

Each Track Finder processes data from the corresponding detectors

- Endcap TF: RPC & CSC

- Overlap TFs: CSC, DT, RPC

- Barrel TF: DT and RCC.

#### **Barrel Track Finder**

Jan 2016: switch to new LvI-1 muon trigger in. Run "Legacy" system till then Commissioning of new system: in parallel with operation (of legacy)

Plan: split input data for RPC and CSC to allow parallel operation. Also part of DT input data (parallel operation of a slice of the upgraded barrel TF)

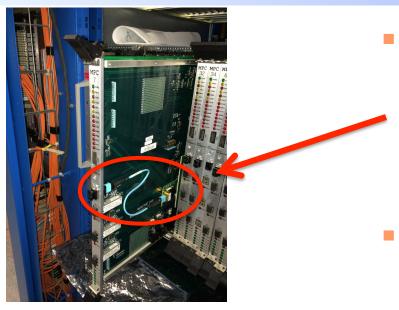

#### **New MPC Mezzanine Cards**

Several modified MPCs installed already in CSC peripheral crates:

- New mezzanine card on MPC with Spartan-6 FPGA and additional optical link connection for running upgrade in parallel

- Production and testing is in progress

- 60 for entire system

- New fibers have been installed from the experimental cavern to the underground counting room for the Track-Finders, and several MPCs installed

#### TwinMux Card – DT & RPC data

Designed to convert legacy 480 Mbps copper DT links and 1.6 Gbps GOL RPC links to 9.6 or 10 Gbps links

- Receives 72 DT copper links at 480 Mbps + 12 RPC GOL links at 1.6 Gbps and gives up to 12 x 10 Gbps links for the barrel track finders. It employs also a Virtex-7 FPGA which gives considerable pre-processing power

- Assembled boards to arrive this week

- Prototype testing is expected to continue up to Dec 2014

- Integration tests with MP7 and MTF7 to be scheduled at CERN in the fall 2014

#### **Muon Trigger**

#### MTF7 (Muon Trigger):

Extensive link testing (wide range of rates 1.6 –10 Gbps tested)

Currently: have 4 boards; one MTF7 already at CERN. Integration tests with MP7 ongoing

**Production: Summer 2014**

Much more work in progress: Barrel track finder (porting DTTF), Global Muon Trigger (using MP7s)

Calo and Muons together: Global Trigger

A very large amount of work remains

#### **Barrel Track Finder**

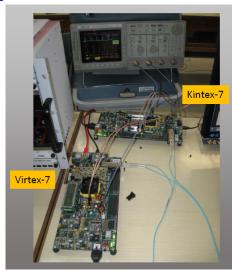

- Porting Legacy DTTF algorithms to MP7

- So far: Kintex-7 and Virtex-7 development cards have been used to develop firmware for algorithms and optical links

- Firmware being ported to MP7 processors.

- A Setup with a uTCA crate and one MP7 processor is operational.

- Firmware for 9.6 Gbps synchronous and 10 Gbps asynchronous links have been developed.

### Global muon trigger & Global trigger

- Hardware platform: MP7

- Base uGMT algorithm logic has been implemented:

- Sorting 3 x 36 muons → 8 muons

- Cancel-out logic

- Isolation assignment (incl. extrapolation to calo + PU subtraction)

- Estimated resource usage at 55% + DAQ logic

- Firmware at an advanced state

- Integration with MTF7 processor in progress

- Hardware platform: MP7

- Gaining experience with 10 Gbps links

- Register access via IPBUS

- 1<sup>st</sup> version of uGT menu available

- uGT firmware ongoing

- Patch panel defined

- Sep 2014: Test interconnect with Calo trigger

- Nov 2014: Integrate with Calo Trigger at P5

## **Software**

## Software (online and offline)

#### Online Software:

- Resource Loaded Plan for Online Software in place

- In sync with commissioning plan for both Stage-1 and 2016 HW

- Project is hampered by manpower needs

- Currently supported by 3 FTE

- Project needs at least another 3 FTE; finding extra resources is on of the priorities of the TriDAS management.

#### Offline Software:

- First Version of Stage-1 emulator available.

- To be released to the collaboration soon

- Emulators for the 2016 Trigger algorithms exist

- First version of emulators to be released in Summer 2014

- Results on e/gamma finder have been shown publicly

## **Overall Trigger Coordination**

- Trigger in 2015 will have to cope with:

- Factor 2 increase in luminosity

- Factor 2 or more increase in cross sections, depending on the process, in going from 8 TeV to 13 TeV

- Increased CPU time/event because of higher Pile Up (PU ≈ 40)

- Goal: to keep the same acceptance for Standard Model (e.g. Higgs) physics, and full sensitivity to new physics

- How to approach this goal:

- Tune the L1 menu using improvements in the HW

- Increase High Level Trigger output rate by up to a factor 2

- Optimize CPU-intensive code

- Improve quality of physics objects reconstructed in the HLT so as to use thresholds closer to those used offline

- Design more sophisticated triggers paths, using more conditions and more correlations

#### **Trigger Coordination: next steps**

- Optimize L1 menu and design more complex "L1 seeds" where needed

- Design new HLT menu using the improved objects for multiple scenarios

- Luminosities up to ≈ 1.6 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>

- Startup with 50 ns bunch crossing

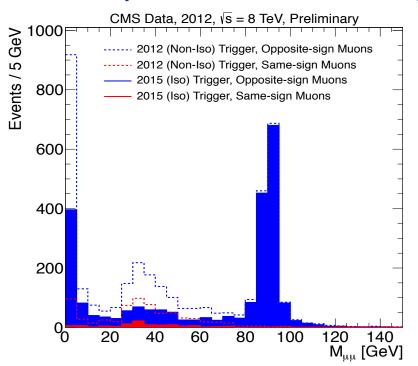

# Example: DoubleMuon trigger path

- Apply loose cut on tracker isolation (PF charged hadrons) to both legs

- Isolation suppresses the contribution from background

- Sizable rate reduction with no impact on the performance for signal-like muons

# Trigger Coordination: timeline and plans

#### Beg of July

- All elements ready to integrate first skeleton of trigger menu

- Need to evaluate overall CPU time (HLT farm procurement)

#### October

- Ready to implement trigger menu in "production" CMSSW release

- Further update of objects in sync with offline

- **►** E.g. improved treatment of OOT Pile UP

- Ready for MC production

#### Several other activities

- Finalize, together with detector DPG, Run Coordination and AlCa groups, calibration workflows and special triggers needed for recommissioning

- Updated ConfDB tool for trigger menu design and bookkeeping

- Back-end written; much faster now

- New interface being designed

- Redesign interfaces and on-line monitor in sync with new DAQ

- First version ready in July; will evolve in 2014

## **Summary/Outlook**

### **Summary/Outlook**

- Revisited TDR plans for 2016 trigger; new resourceloaded plan in place

- Generally on schedule, though tight

- Stage 1 for calo trigger: offers possibility of starting with (some of) the new trigger's features in 2015

- In case unforeseen high pileup; also for heavy-ion run

- Full upgrade (2016 trigger): proceeding

- Calorimeter: expect fully in place by mid-2015; six months to commission

- Muons: in place by early 2016

- Software: in progress, but need more FTEs

- Projects working on securing resources

- Next steps: from emulator(s) to trigger menus...

# Backups (Lvl-1 Trigger)

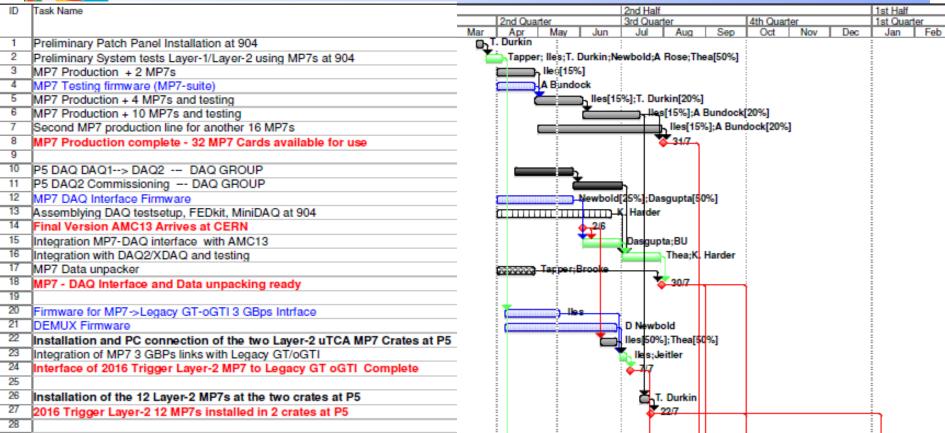

#### **2016 Trigger milestones**

#### Milestones up to July 2014

- ◆ 07.7 MP7 integration with Legacy GT 3 GBps links

- 14.7 Version-1 of algorithms ready in CMSSW and firmware

- 22.7 Layer-2 Crates at P5

- 22.7–4.8 Trigger Slice Test (oSLB/uHTR→CTP7→MP7→GT)

- 30.7 DAQ integrations (requires AMC13 cards plus software and firmware)

- 31.7 Finish Production of 32 MP7 boards

#### Milestones for CTP7s at CERN

- End Aug: 4; end Jan 2015: 12; end Mar: 28; 08.4.2015: 36 CTP7s at CERN

- Milestones related to commissioning of the trigger

- 10.9 1/3 Layer-1→ Patch-Panel (Layer-1%Layer-2)→Layer-2 commissioned

- 29.9 Integration with uGT complete

- 26.11 All Layer-1 firmware ready

- 11.2.2015 oSLB/HF-uHTR connected to trigger and slice test with uGT

- ◆ 12.02.2015 Start commissioning Barrel uHTRs with trigger

- 19.06.2015 System ready for parallel data taking

Task-1 (Preparations up to the Jul. 14 Slice Test)

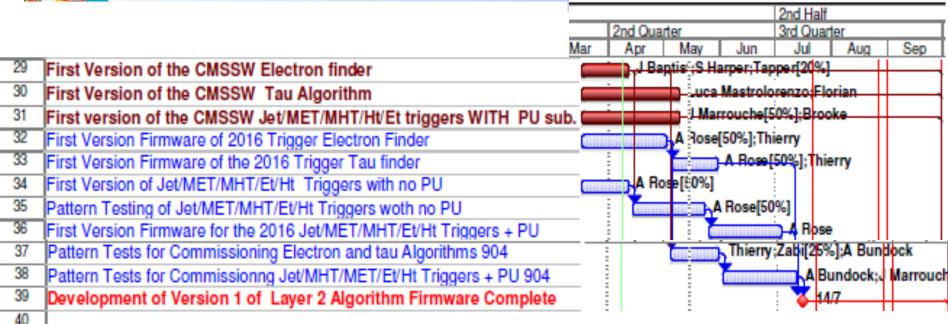

#### Tasks-2 (Layer-2 Algorithms)

- Dedicated to the development of the first version of the trigger algorithms

- Includes both emulators and firmware

- Ends with on bench algorithm versus emulator validation using patterns

- Tasks-3 (Layer-1 Production and Firmware)

- CTP7 production and delivery

- Two phases of firmware development

- First phase ends with Slice Test in July 2014

- Second phase ends in Nov 2014 when the commissioning of the triggers with calorimeter data starts

|    |                                                                          |                   |         | 2nd Half    |              |              |                |

|----|--------------------------------------------------------------------------|-------------------|---------|-------------|--------------|--------------|----------------|

|    |                                                                          | 2nd Quarter       |         | 3rd Quarte  | r            |              | I              |

|    |                                                                          | Apr               | May Jun | Jul         | Aug          | Sep          | J              |

|    | Firmware for testing the Patch Panel connections using MP7               | ( IBIBIBIBIBIBIBI | A Bun   |             | ┼┤╽          |              |                |

|    | Layer-1 - Layer -2 Patch Panel manufacture                               |                   |         | T. Durkin[1 | 5%]          |              |                |

|    | Layer-1 - Layer -2 Patch-Panel precabling at RAL                         |                   |         | —J₁.        | Durkin       |              |                |

|    | Layer-1 - Layer-2 Patch Panel shipping from RAL to P5                    |                   |         | o o         |              |              |                |

|    | Layer-1 - Layer-2 Patch Panel installation at CERN                       |                   |         | 0           | T. Dui       | kin          |                |

|    | oSLB/uHTR Patch Panel Design                                             |                   |         |             |              |              |                |

|    | oSLB/uHTR Patch Panel manufacture and procurement                        |                   |         |             |              |              |                |

|    | oSLB/oRM Patch Panel Transport to CERN                                   |                   |         |             | <b>↓</b> . Ⅱ |              |                |

|    | oSLB/uHTR to Layer -1 Patch Panel installation                           |                   |         | 1           | ₽Ⅱ           |              |                |

| 79 | Layer-1 Crate linstallation (6 uTCA crates for CTP7)                     |                   |         |             |              |              |                |

|    | Commissioning of Layer-2 and Layer-1/Layer-2 Patch Panel and 1/9 Layer-1 |                   |         |             | - 1          |              | dock;T. Durkin |

| 81 | Layer-2 + Patch Panel + 1/9 of Layer-1 Commissioned                      |                   |         |             |              | <del> </del> |                |

|    |                                                                          |                   |         |             |              | -            |                |

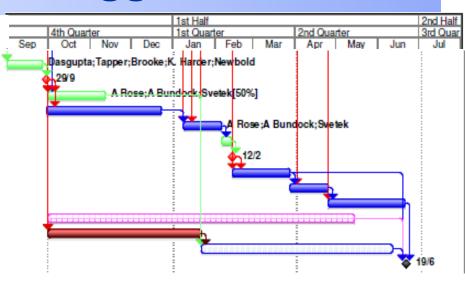

- Task-4 (Commissioning of the Patch Panels)

- Layer-1 → Layer-2 Patch-Panel

- ECAL and HCAL Patch-Panel (input to Layer-1)

| 83 | Integration of the 2016 Trigger at P5 with the DAQ and uGT                   |

|----|------------------------------------------------------------------------------|

| 84 | Layer-2 + Patch Panel + 1/9 of Layer-1 Connected to uGT and DAQ              |

| 85 | Commissioning of 2016 Trigger Part - 0 (V1 Firmware 12 MP7s+4 CTP7s) Pattern |

| 86 | Commissioning the 36 HF uHTR fibers to 4 Layer-1 CTP7s and Commissioning     |

| 87 | Commisioning - 12 MP7+ 8 CTP7 2016 trigger Patterns+ oSLB data               |

| 88 | Slice test oSLB+HF uHTR>CTP7>MP7->Demux->uGT                                 |

| 89 | 2016 Trigger Ready to connect to B/E HCAL uHTR System                        |

| 90 | Commissioning HCAL B/E uHTR system with trigger 12/36 Layer-1                |

| 91 | Commissioning of the HCAL B/E uHTR system with trigger 28/36 Layer-1         |

| 92 | Commissioning of the HCAL BE/uHTR systerm with trigger 36/36 Layer-1         |

| 93 | Online Monitoring Software for the 2016 Trigger                              |

| 94 | 2016 Trigger final Emulators                                                 |

| 95 | Final Firmware for the 2016 Trigger + Validation                             |

| 96 | 2016 Trigger Ready for Parallel Data Taking                                  |

|    |                                                                              |

#### Task-5 (Commissioning for Parallel Data taking)

- Integration with uGT and DAQ in Sep 2014.

- Start Connecting with ECAL and HF in the Fall of 2014.

- Start connecting the HB/HE uHTRs in Feb 2015.

- Ready for parallel data taking in Jun 2015.

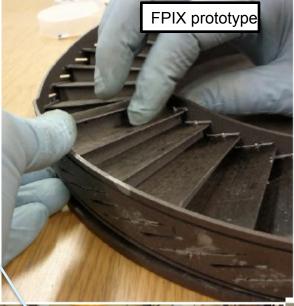

# Backups (Pixels)

# Pixel Phase I

Main items being submitted

TBM (Token Bit Manager) submitted;

**BPIX HDI (High-Density Interconnect) order out**

**FPIX HDIs prototypes received**

**BPIX** sensors pre-series received

**FPIX** sensors ready for PRR

**ROC** submission delayed

We are evaluating one non-understood result from test beam which is probably setup related

Does not affect module production schedule

Otherwise all ROC result excellent High rate capability tested OK Radiation tolerance tested OK

- Module construction centers ramping up, e.g.

- First digital BPIX module built outside PSI

- 20 bare modules built in US

- FPIX mechanical prototype almost complete

- Successful insertion test of BPIX and FPIX 3D print in CMS 2 weeks ago

- DC-DC chip and circuits all OK

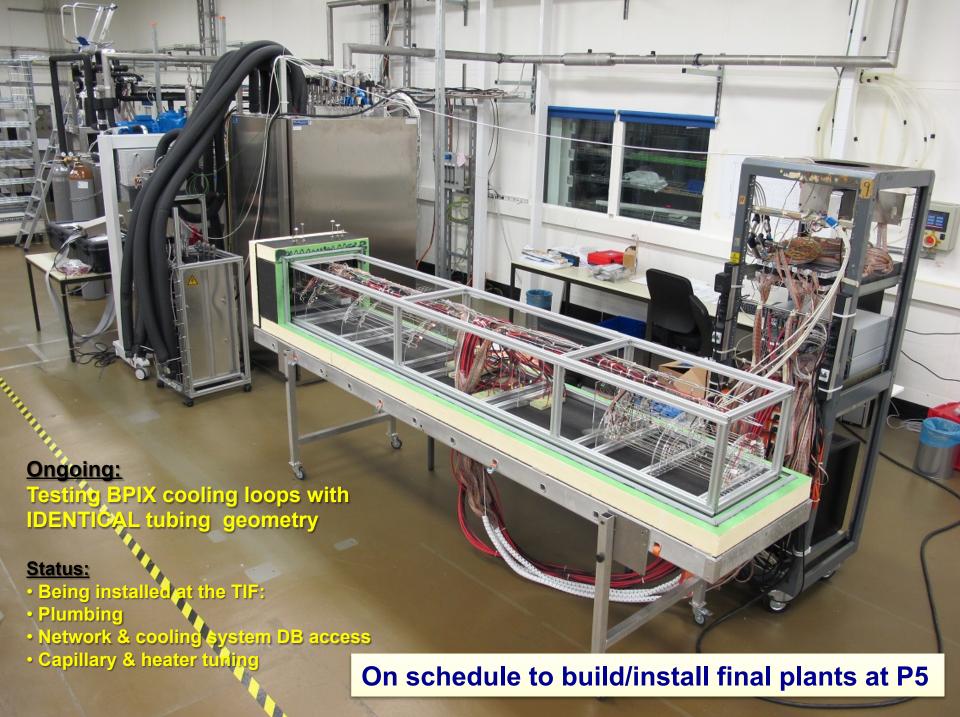

- CO2 Cooling on track to be installed during LS1 (see next slide)

- Opto components progress on all fronts

- Pilot Blade on track for installation during LS1

P. Sphicas CMS trigger upgrade status

elescope (no TRIVI

**FPIX**

module

under X-ray

# Backups (HCAL)

#### **HCAL Phase 1 Upgrade**

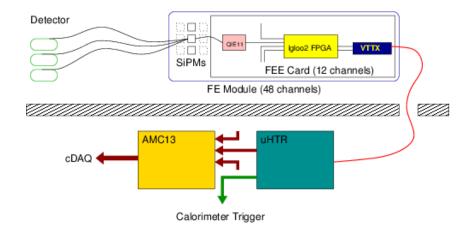

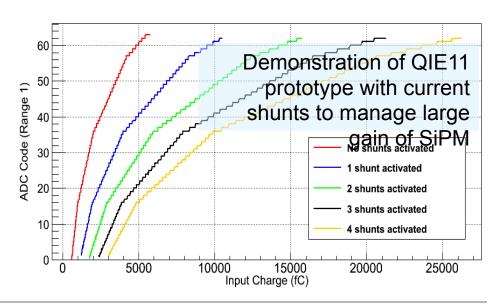

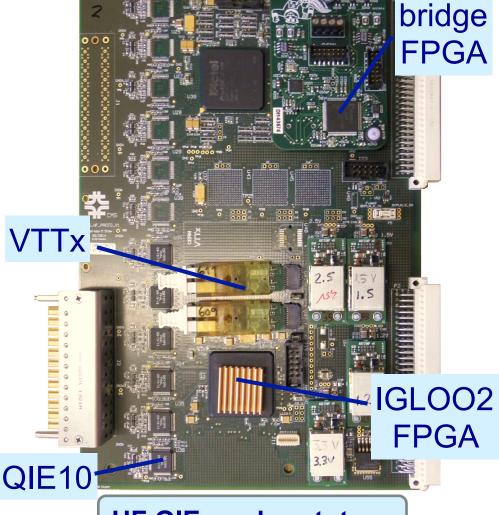

- HCAL Phase 1 consists of replacement of the HB/HE photodetectors with SiPMs, and the introduction of a new digitizer including TDC capability

- Installation is staged, starting with the HF offdetector electronics during LS1 and continuing with HF front-end electronics at the end of 2015 and ending with HB/HE during LS2

#### **HCAL Backend Upgrade Status**

- Commercial hardware completely delivered for HF, MCH and PM delivered for HB/ HE (crates on order)

- AMC13 production (30 modules for HCAL) nearly complete, 12 modules tested and shipped

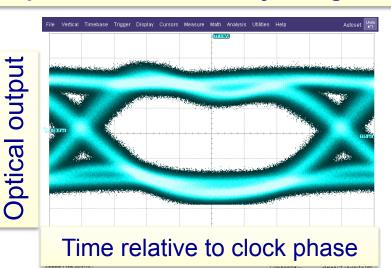

- uHTR all tests complete

- 6.4 Gbps trigger link quality excellent in both eye-diagrams and integration tests

- HF uHTR production in India ramping up

- US pre-production (HB/HE) underway

- First HF crate in operation at P5 by end of June; rest before Sep

Test fixture for uHTR DC/DC subassemblies, 12 such fixtures now in use in US, India

#### Optical transmitter: "eye diagram"

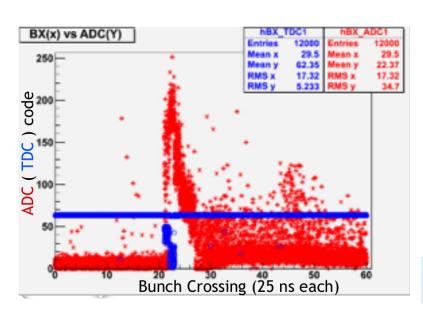

#### **HF Front-End Testbeam**

Full set of prototype electronics (QIE10 card, ngCCM, uHTR, AMC13) demonstrated in April during testbeam at FNAL

**HF QIE** card prototype