# Comparison of the AC and DC coupled pixels sensors read out with FE-I4 electronics

Gianluigi Casse\*, Marko Milovanovic, Paul Dervan, Ilya Tsurin

19/11/2014

# Motivation

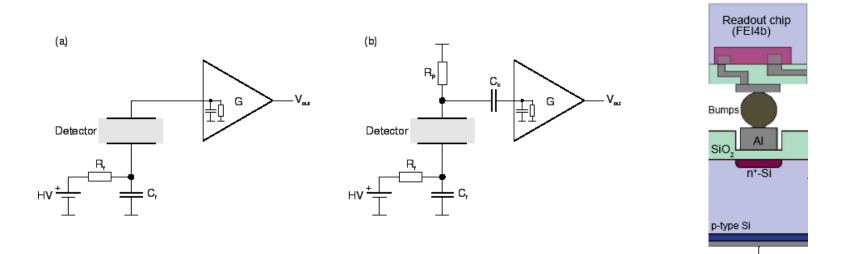

- High leakage current of DC coupled sensors is the source of shot noise in FE electronics. High amplifier currents distort signal shape and affect linearity and dynamic range of analogue circuits.

- AC coupling between implants and front-end is one possible solution to improve on these issues, especially after irradiation, as it blocks the leakage current from the detector to the amplifier.

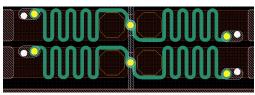

- Integration of coupling capacitances is performed in standard planar process and is basically the same as for strip sensors, by depositing SiO<sub>2</sub> with a thickness of around 100 nm on top pixelated implants.

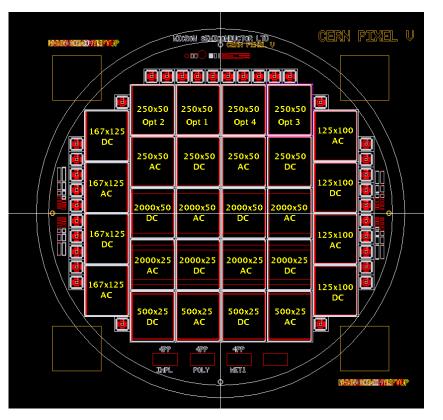

# **Production: CERN Pixel V – AC & DC coupled devices**

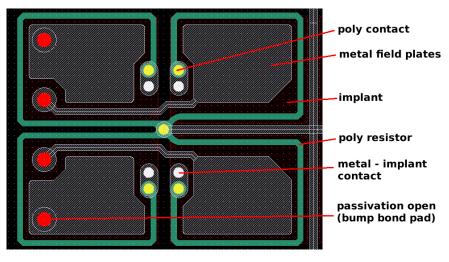

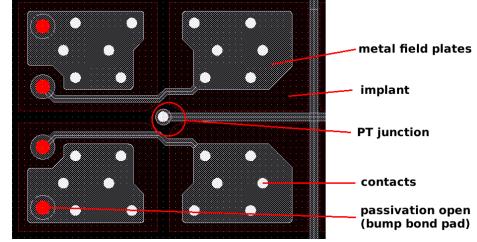

• The bias current is shunted by resistors, either made of polycrystalline silicon or implemented as a PT junction.

### 125x100 AC:

### <u>125x100 DC:</u>

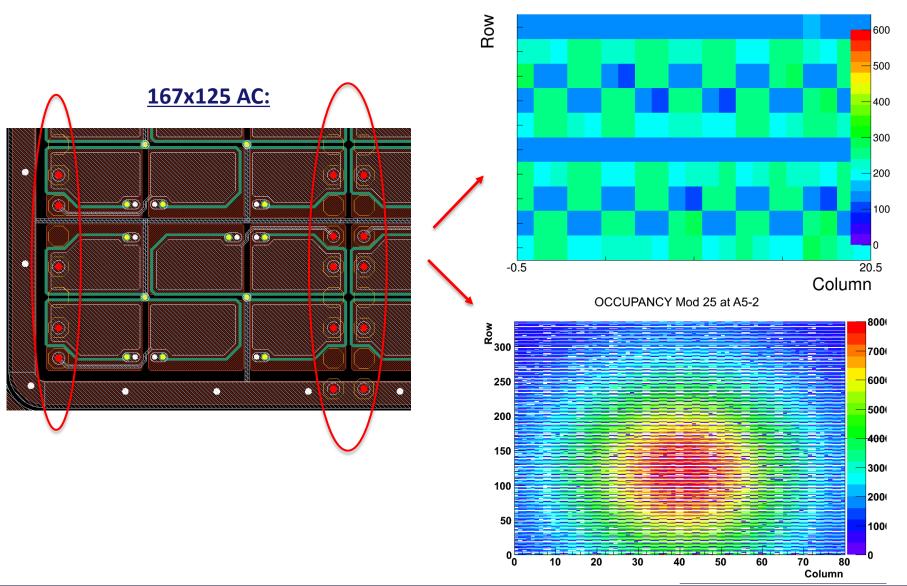

### 167x125 AC:

### 500x25 AC:

2000x50 (strixel) AC:

#### 19/11/2014

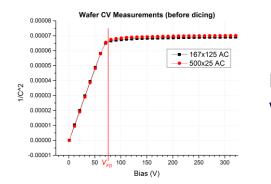

# $\underbrace{\overline{UNIVERSITY} \circ F}_{\text{LIVERPOOL}} \quad \text{CERN Pixel V} - 2873-25 \text{ (310um) AC wafer (10k}\Omega/\text{cm)}$

2873-25-S9 2000x50 DC → ADV2000x50-DC-4 2873-25-S17 500x25 DC → ADV500-DC-4 2873-25-S18 500x25 AC → ADV500-AC-1 2873-25-S23 167x125 DC → ADV167-DC-4 2873-25-S24 167x125 AC → ADV167-AC-1 • Single FE-I4 chip compliant sensors with alternative pixel geometries

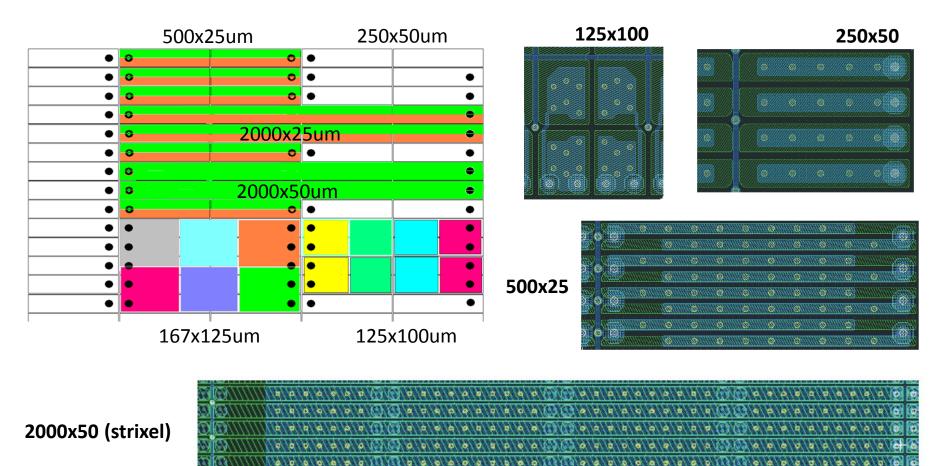

### Segmentation:

- 125x100 μm (square)

167x125 μm (square)

250x50 μm (standard)

500x25 μm (elongated)

2000x25 μm (strixel)

2000x50 μm (strixel)

- 26880 channels (100%) 16080 channels (60%) 26880 channels (100%) 26880 channels (100%) 6720 channels (25%) 3660 channels (12.5%)

- Features both AC and DC coupling, polysilicon/Punch Through Bias

- Production of 300, 200, 150, and 100 μm

- 4/10/13 kΩ bulk resistivity

Full depletion voltage ≈ 75V

#### 19/11/2014

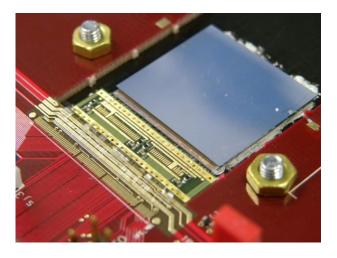

# Assembling and Testing

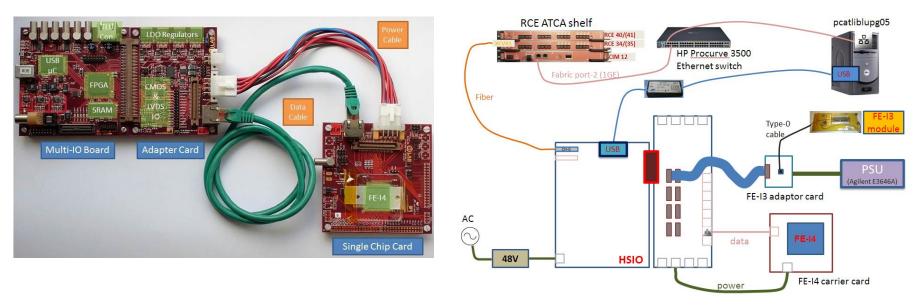

- The devices were bump-bonded at Advacam and assembled into modules using FEI4b Single Chip Cards (V1.1), PA5s and carbon-fibre support.

- Both chip LDOs are now supplied from VDDD at 1.8V.

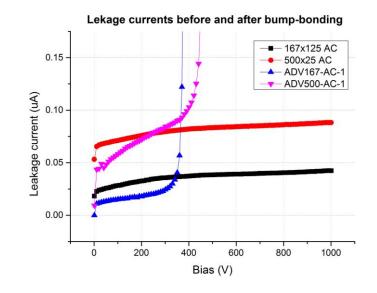

- IVs were taken and show the breakdown voltage to be between 400 and 450V.

### DAQs

RCE

### **USBPix**

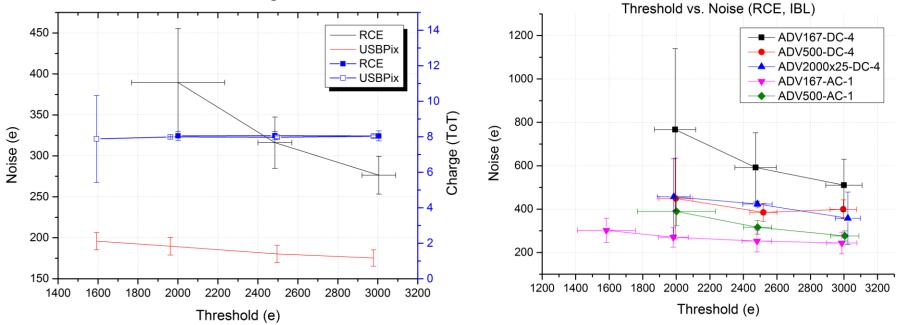

- All the devices were tuned (from 3000e to 1400e threshold, to 8ToTs@20ke) with both USBPix and RCE using standard or IBL primlists at 100V sensor bias.

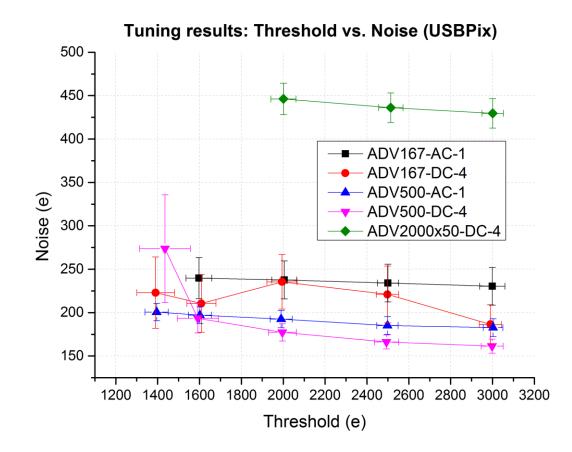

- Since the USBPix showed better results in terms of noise and threshold dispersion, these were used in this talk, while the Source Scans were performed mostly with RCE in Selftriggering mode (2000s) using a Strontium-90 source (370MBq).

- Since data acquisition is still under way (24/7), some results are incomplete, however still good for relative estimation and comparison.

### 19/11/2014

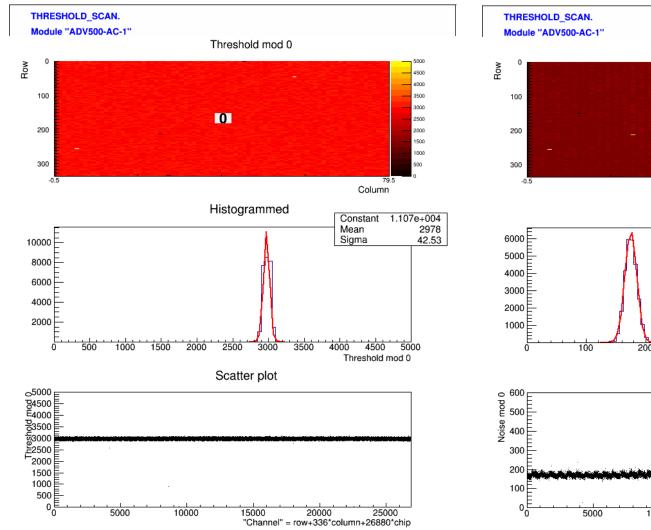

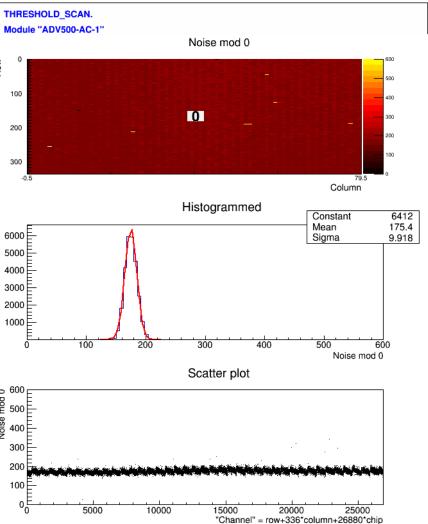

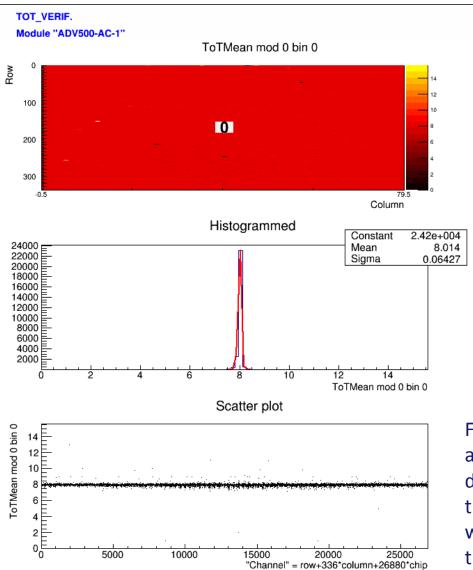

# <sup>UNIVERSITY OF</sup> ADV500-AC-1 – 3000e, 8ToT@20ke (100% ch.used)

# $\boxed{\textcircled{2}}$ <u>LIVERPOOL</u> ADV500-AC-1 – 3000e, 8ToT@20ke (100% ch.used)

FDAC tuning performance was almost the same for all the devices, regardless of the threshold/noise and therefore will not be shown anymore in this talk.

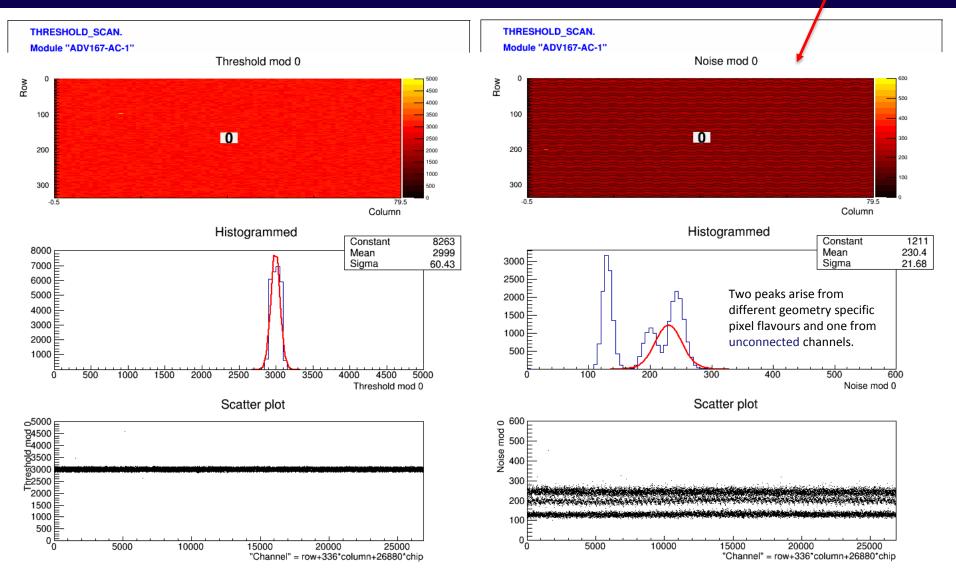

# $\sqrt[5]{\text{LIVERPOOL}}$ ADV167-AC-1 – 3000e, 8ToT@20ke (60% ch.used)

### \*Look at the backup slides for more details on specific pixel geometry!

19/11/2014

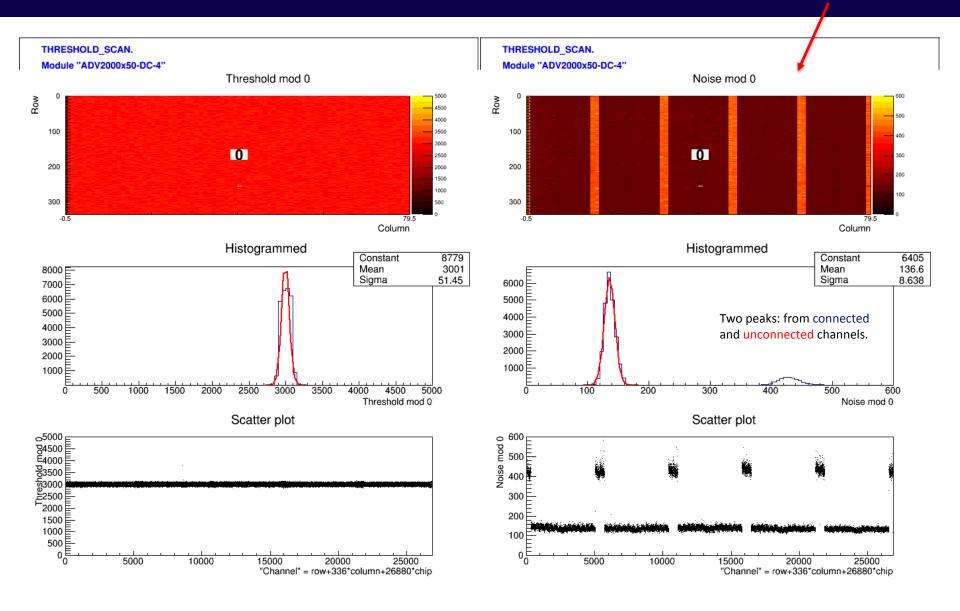

### <u>UNIVERSITY OF</u> ADV2000x50-DC-4 – 3000e, 8ToT@20ke (12.5% ch.used)

#### 19/11/2014

### 25th RD50 Workshop @ CERN, Geneva, 19-21 November 2014

# Threshold tuning summary for all DUTs

- Mean of double peak for connected pixels used for 167x125 geometry devices. Only connected pixels included for the strixel (2000x50) device.

- DC devices show slightly lower noise than AC coupled devices, however less stable.

- The strixel DC device shows much higher noise due to very long strips/interconnected pixels.

UNIVERSITY OF

VERPOO

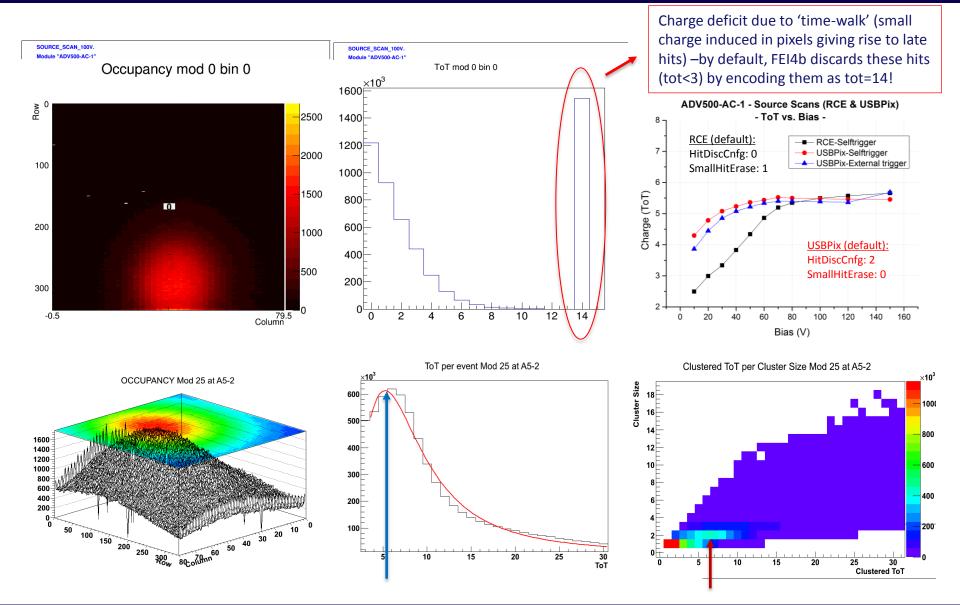

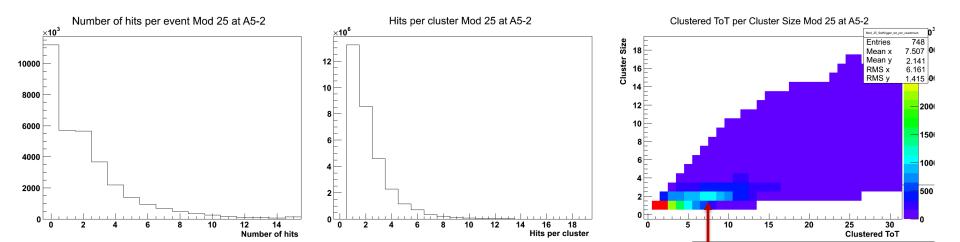

# ADV500-AC-1 – <sup>90</sup>Sr Source Scans@100V bias, 3000e threshold, 8ToTs@20ke (USBPix&RCE)

19/11/2014

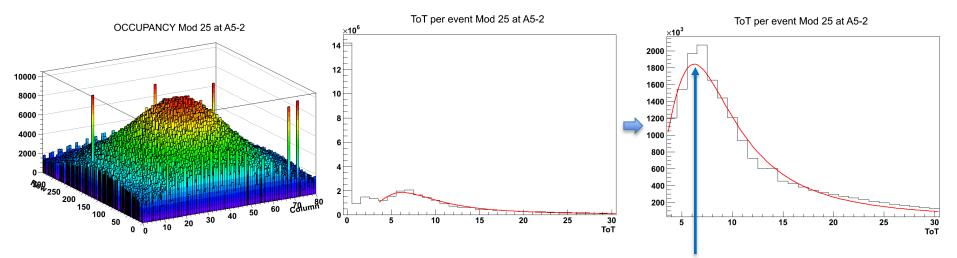

### ADV500-DC-4 – <sup>90</sup>Sr Source Scans, TH:3000e, 8ToTs@20ke (RCE)

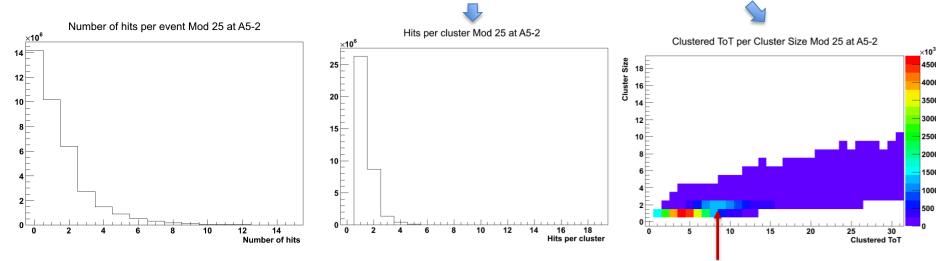

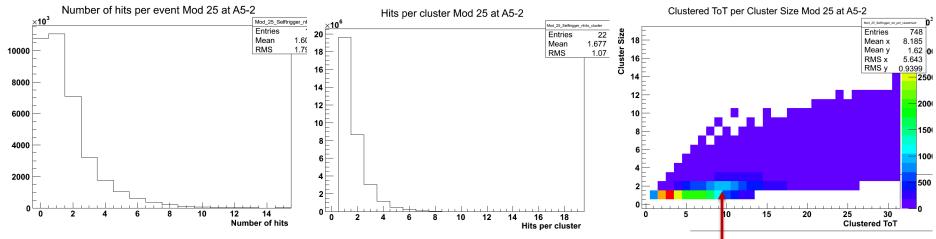

### ADV167-AC-1 – <sup>90</sup>Sr Source Scans, TH:3000e, 8ToTs@20ke (RCE)

### The smaller the cluster size, the smaller observed charge deficit!

19/11/2014

25<sup>th</sup> RD50 Workshop @ CERN, Geneva, 19-21 November 2014

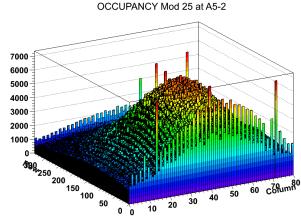

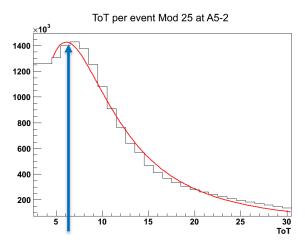

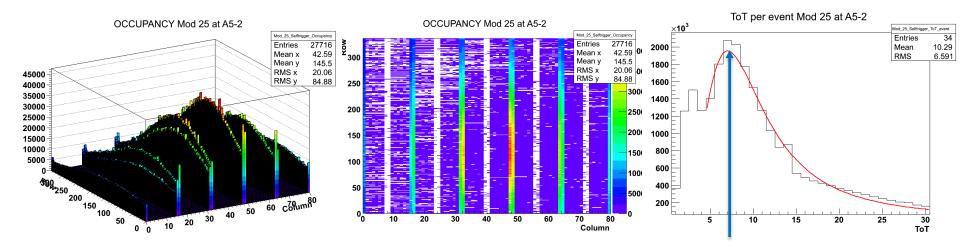

### ADV2000x50-DC-4 – <sup>90</sup>Sr Source Scans, TH:3000e, 8ToTs@20ke (RCE)

#### The strixel device has slightly larger clusters than 167x125 device due to long pixels.

\*The geometry specific pixel matrix of ADV167 can be found in backup slides.

### 19/11/2014

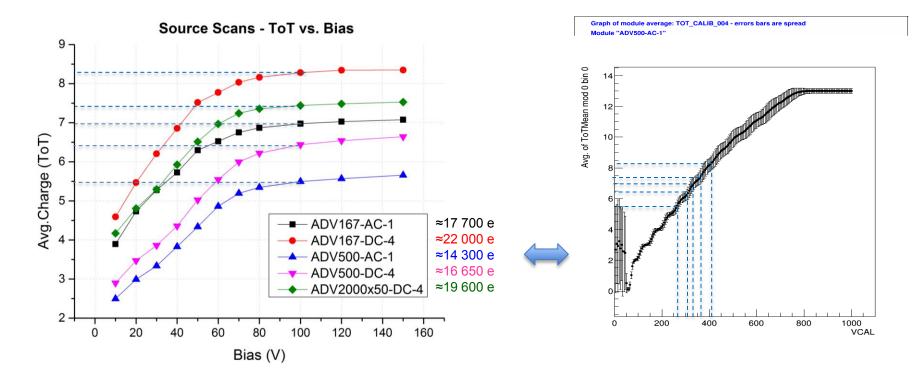

### Source Scans Summary

- Although absolute ToT/charge measurements are not available at the moment, it is possible to make relative charge collection comparison same geometry structures.

- The collected charge for AC coupled devices is only ≈10-20% less than for the DC ones.

- Still to test 125x100 AC and DC, as well as 2000x50 AC and resolve charge deficit issue.

AC coupled detectors show, before irradiation, significant charge collection efficiency and lower noise wrt DC coupled sensors with identical geometry. This is promising in view of possibly using this technique for improved performance of the sensors after irradiation. This can be further optimise if the design of the readout chip (FE-I4 in this case) is taking this type of coupling into account.

### BACKUP SLIDES

19/11/2014

# **UNIVERSITY OF Capacitances & SiO**<sub>2</sub> thickness calculation

• Two different test structures (C-DIF and C-SUB) were employed to calculate the gate and the field oxide thicknesses.

| C-DIF test structure                                                                                                                                                           |                            | C-SUB test struct                                                                               | ure                                                         | Readout chip<br>(FEI4b) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------|

| implant area: $1020 \times 1670 \ \mu\text{m}^2$ ( $1.70 \cdot 10^{-6} \ \text{m}^2$ )<br>metal area: $1000 \times 1450 \ \mu\text{m}^2$ ( $1.45 \cdot 10^{-6} \ \text{m}^2$ ) |                            | metal area: 1000 x 1450 μm <sup>2</sup>                                                         |                                                             |                         |

|                                                                                                                                                                                |                            | MOS capacitance                                                                                 | = 50 pF (35 pF / mm <sup>2</sup> )                          |                         |

| Depleted PN-junction capacitance = 0.7pF @50V (0.4 pF / mm <sup>2</sup> )                                                                                                      |                            |                                                                                                 |                                                             | Bumps                   |

| MOS capacitance = $250 \text{ pF}$ (170 pF / mm <sup>2</sup> ) Field o                                                                                                         |                            | Field oxide thickn                                                                              | ness = 1 μm                                                 | + SIO, AI               |

| Gate oxide thickness = 0.2 μm —                                                                                                                                                |                            |                                                                                                 |                                                             | n⁺-Si                   |

| Photo-diode measurements                                                                                                                                                       |                            |                                                                                                 |                                                             | p-type Si               |

| implant area = $4300 \times 4300 \ \mu m^2$ (1.8)                                                                                                                              | 35 · 10⁻⁵ m²)              |                                                                                                 |                                                             | T T                     |

| Depleted PN-junction capacitance =                                                                                                                                             | 14 pF @50V (0.75 pF / mm²) |                                                                                                 |                                                             |                         |

|                                                                                                                                                                                |                            | Inter-strip/pixel capacitance                                                                   |                                                             |                         |

| 167 x 125 um pixel AC single chip sensor measurement                                                                                                                           |                            | <br>D                                                                                           |                                                             |                         |

| implant area = 167 x 125 x 120 x 138 $\mu$ m <sup>2</sup> + (20000 + 17300) · 2 · 38 $\mu$ m <sup>2</sup> (3.5 · 10 <sup>-4</sup> m <sup>2</sup> )                             |                            | Bulk capacitance: 35 μm x 10500 μm =<br>0.37 mm <sup>2</sup> x 0.7 pF/mm <sup>2</sup> = 0.25 pF |                                                             |                         |

| Depleted PN-junction capacitance = 250 pF @50V ( $0.72 \text{ pF} / \text{mm}^2$ )                                                                                             |                            |                                                                                                 | Inter-strip/pixel capacitance $\approx 0.5 \text{ pF/cm}^2$ |                         |

### ADV167 pixel structure

Noise mod 0

19/11/2014

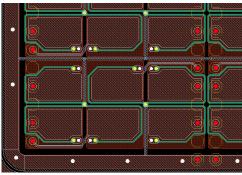

## **EXAMPLATE CERN** Pixel V alternative geometries – adaptive pixel size

- Compatible with FE-I4 UBM pads.

- Various pixel sizes, punch through/polysilicon biased, AC and DC coupled

# LIVERPOOL Threshold tuning results comparison: USBPix vs. RCE

ADV500-AC-1 Threshold Tuning with RCE & USBPix

• It was not possible to tune below 2000e for most of the devices using RCE.

7