# Alternative technologies for Low Resistance Strip Sensors (LowR) at CNM

CNM (Barcelona), SCIPP (Santa Cruz), IFIC (Valencia)

M. Ullán, V. Benítez, J. Montserrat, O. Beldarrain, M. Zabala, D. Quirion, M. Lozano, V. Fadeyev, A.A Grillo, H.F.-W. Sadrozinski

Contact person: Miguel Ullán

- Motivation

- Baseline solution

- Alternatives

- Titanium Silicide (TiSi<sub>2</sub>)

- Highly Doped Polysilicon (HDPoly)

- Conclusions & future work

### Motivation

- In the scenario of a beam loss there is a large charge deposition in the sensor bulk and coupling capacitors can get damaged

- Punch-Through Protection (PTP) structures used at strip end to develop low impedance to the bias line and evacuate the charge

But...

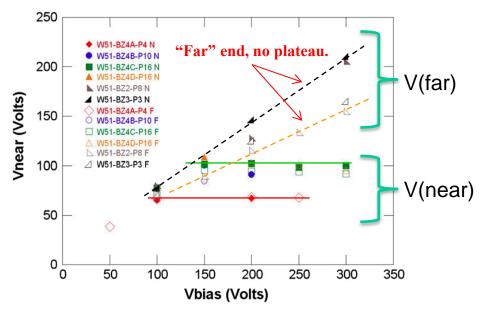

- Measurements with a large charge injected by a laser pulse showed that the strips can still be damaged

- The implant resistance effectively isolates the "far" end of the strip from the PTP structure leading to the large voltages

**Proposed Solution:**

To reduce the resistance of the strips: "Low-R strip sensors"

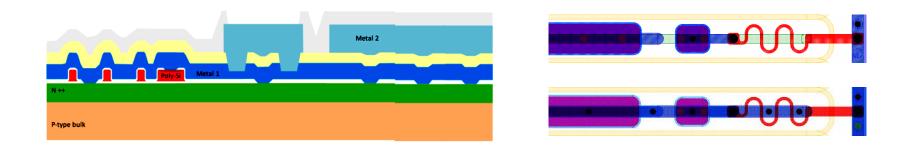

#### **Baseline** solution

- ► Deposition of Aluminum on top of the implant:  $R_{\Box}(Al) \sim 0.04 \ \Omega/\Box \implies 20 \ \Omega/cm$  (Drastic reduction of strip resistance!)

- Metal layer deposition on top of the implant (first metal) before the coupling capacitance is defined (second metal).

- Double-metal processing to form the coupling capacitor

- A layer of high-quality dielectric is needed between metals for the coupling cap.

Deposited on top of the first Aluminum (not grown)

- The second seco

- Plasma Enhanced CVD (PECVD) process at 300-400 °C

- Triple-layer: TEOS oxide (1000 Å) +  $Si_3N_4$  (1000 Å) + TEOS oxide (1000 Å)

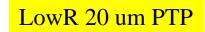

#### Laser scan results

✓ Vfar = Vnear

- ✓ A plateau is observed for both near and far laser injections on Vfar and on Vnear.

- ✓ When laser is fired on the near side, plateu is seen after 100 V bias. For the far side case, plateu is observed after 120 V.

- Technological difficulties:

- Double metal technology

- Low temperature deposited oxide quality

Other methods to obtain LowR sensors being studied:

- ➤ Titanium Silicide (TiSi<sub>2</sub>): allows the use of high temperature steps

✓ oxide deposition → oxide densification (high T) → higher quality

- Highly Doped Polysilicon (HDPoly): allows the growth of thermal oxide after it

- ✓ Oxide is grown on the polysilicon → high quality oxide

- ✓ Back to "standard" process

|         | sheet R (Ohm/#) | kOhm/cm | strip R (kOhm) |

|---------|-----------------|---------|----------------|

| Implant | 22              | 11      | 25.3           |

| Metal   | 0.04            | 0.02    | 0.05           |

| TiSi2   | 1.2             | 0.6     | 1.38           |

| Poly    | 2               | 1       | 2.3            |

Low-resistance strip sensors using these two alternative technological options have been fabricated at CNM

#### Titanium Silicide (TiSi<sub>2</sub>)

#### $\succ$ TiSi<sub>2</sub>

- Titanium Disilicide is a compound of Ti and Si

- It is formed using a high temperature process (RTA) on a layer of Ti deposited on Si

- A non-conductive layer of TiO<sub>2</sub> can also be formed which is non-conductive and has to be removed/avoided

- The extra remaining Ti is selectively etched →

→ the process is self-aligned

- Higher leakage current in diodes (for thin implants)

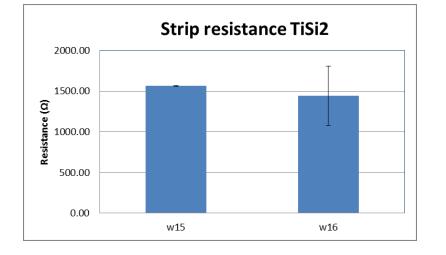

- ➢ TiSi₂ formation technology at CNM

- 100 nm Ti deposited

- RTA

- Low sheet resistance:  $\sim 1.2 \pm 0.03 \ \Omega/\Box$

- ✓ Good formation of TiSi<sub>2</sub> layer

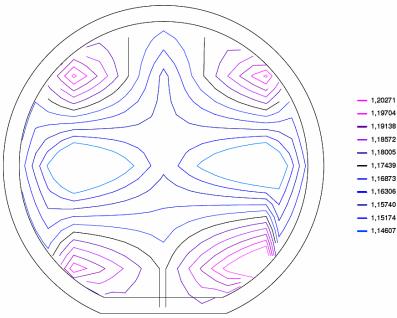

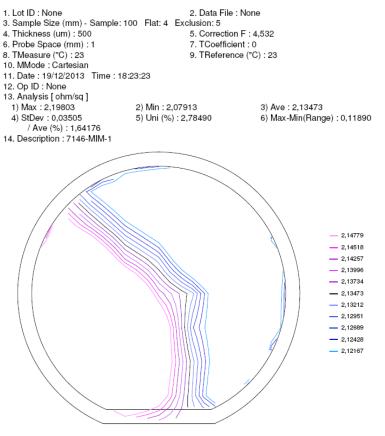

#### Contour Map

- ➢ TiSi₂ MiM capacitors fabricated

- Substrate is implanted as in strips

- A layer of TiSi<sub>2</sub> in created as bottom plate of the capacitors in contact with Si

- 300 nm of oxide deposited at low T (PECVD)

- Densification at 900 °C , 30 min

- Aluminim layer deposited and defined as top plate of the capacitors

- > Results

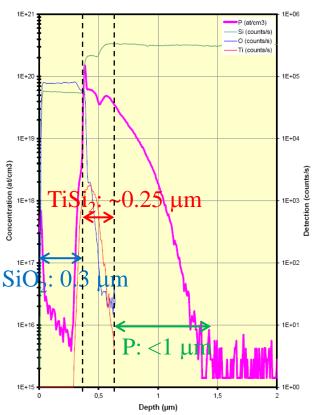

- SIMS (Secondary Ion Mass Spectrometry)

- $\circ$  Detection limit >10<sup>15</sup> cm<sup>-3</sup>

- $\circ$  No perfect calibration for TiSi<sub>2</sub>

- Negligible effect on implant depth

- $\circ$  TiSi<sub>2</sub> layer ~2.5 x Ti layer

- 98-100% yield up to 100 V

- Breakdown voltage >150 V

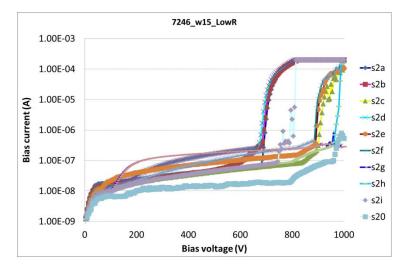

## TiSi<sub>2</sub> Sensors (preliminary)

- To form the low resistance strips a layer of TiSi<sub>2</sub> is formed on top of the implant

- ➤ Self aligned process → no additional mask required

- Good general performance of sensors

- More than order of magnitud reduction in strip resistance (~0.7 kΩ/cm)

- ➢ No additional leakeage current observed

## Highly Doped Polysilicon

- Polysilicon layer doped with liquid source (POCl<sub>3</sub>, "Phosphoryl chloride") in contact with the silicon implant (substitutes the metal layer)

- High doping levels reached at high temperatures (1050°C) and long times

- Possibility to grow a thermal oxide on top of the polysilicon layer to form the coupling capacitor

- Much higher quality oxide

- Although risk of lower breakdown voltages

- Higher thermal load of the process

- Risk of dopant precipitates later in the process

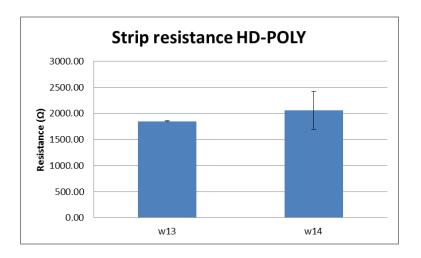

- HDPoly formation at CNM

- > DOE (thickness  $\uparrow$ , doping time  $\downarrow$ )

- Solution Good conductance:  $\sim 2.0 \pm 0.04 \ \Omega/\Box$

#### Contour Map

|             | W1   | w2   | w3   | w4   | w5   |

|-------------|------|------|------|------|------|

| Poly thickn | -    | -    | +    | +    | +    |

| doping (t)  | -    | +    | -    | +    | -    |

| Resist      | 2.13 | 1.70 | 2.02 | 1.65 | 2.00 |

| (Ohm/sq)    |      |      |      |      |      |

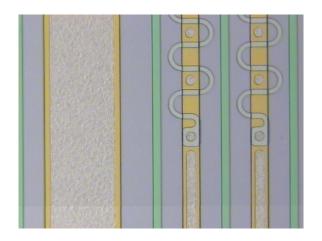

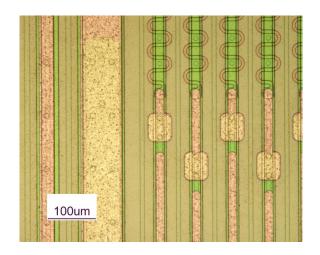

#### **Capacitors HDPoly**

SCIPP

- Capacitors:

- Substrate is implanted as in sensors

- Polysilicon is deposited and doped without mask (to form the bottom plate of the capacitors)

- Thermal oxide is grown afterwards (200 nm)

- Photolithography: to open contact to Poly

- Aluminum sputtering

- Photolithography: Capacitors' top plate definition and contact to poly (bottom plate)

- MIM capacitors

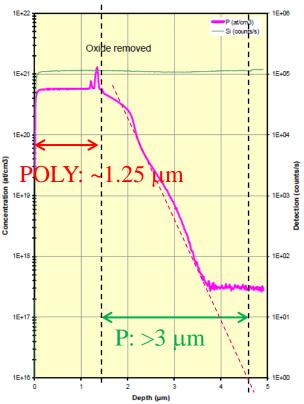

- SIMS (Secondary Ion Mass Spectrometry)

- $\circ$  Detection limit >10<sup>17</sup> cm<sup>-3</sup>

- Poly doping up to ~6 x  $10^{20}$  cm<sup>-3</sup> (implant ~2x10<sup>20</sup>)

- $\circ~$  Not negligible effect on implant depth (>3 um)

- Not important effect on sensor performance

- 98-100 % yield up to 20 V

- Breakdown @ 40-50 V

- 200 nm oxide thickness

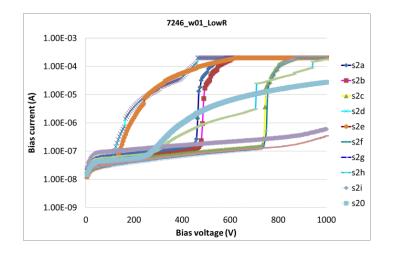

# HDPoly Sensors (preliminary)

- A layer of Polysilicon is deposited on top of the implant and then highly doped

- Good general performance of sensors

- One order of magnitud reduction in strip resistance (~1 kΩ/cm)

Centro Nacional de Microelectrónica

#### **Conclusions & future work**

- Low-resistance strip sensors (LowR) proposed to extend the protection afforded by PTP structure to the entire active area of the sensor

- Implementation with Aluminum layer already demonstrated (see presentation at last RD50 meeting: https://indico.cern.ch/event/307015/session/9/contribution/17/material/slides/1.pdf)

- $\checkmark\,$  New technological implementations have been fabricated

- ➤ Titanium Silicide (TiSi<sub>2</sub>) → Improved oxide quality

- ➢ Highly Doped Polysislicon (HDPoly) → High quality oxide + standard process

- $\checkmark$  Sensors fabricated and tested with good general performance

- Future work

- $\circ~$  Complete tests on new devices with TiSi\_2 and HDPoly

- Laser tests on alternative technological solutions

- Tests after irradiation

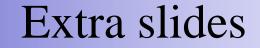

- > PTP design:

- Design of experiments (DOE): varying  $p, s \Rightarrow d$

| DOE                |   | N–P separation 's' [um] |    |         |  |

|--------------------|---|-------------------------|----|---------|--|

| DOE                |   | 12                      | 8  | 6       |  |

| P-stop             | 8 | 32                      | 24 | 20      |  |

| width 'p'          | 6 | 30                      | 22 | 18      |  |

| [um]               | 4 | 28                      | 20 | 16      |  |

| Total PTP distance |   |                         |    | nce 'd' |  |

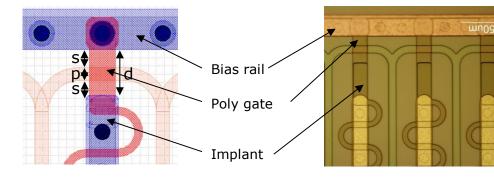

- ➤ Wafer design:

- In ATLAS-barrel-like sensors: "LowR sensors"

- 64 channels, ~2.3 mm long strips

- First metal connected to the strip implant to reduce R<sub>strip</sub>

- Each sensor with a different PTP geometry (with polysilicon bridge)

- 10 extra standard sensors for reference (no metal in implant). Identical design to the LowR but without metal strip on top of the implant