# Design and Measurements of the Inductive Adder Pulser

### J. Holma

### CERN TE/ABT, Geneva, Switzerland

### Acknowledgement M.J. Barnes CERN

# **Overview**

#### Background

- CLIC Layout with Damping Ring (DR) kickers

- Specifications for CLIC DR Extraction Kicker System

- Challenges and Issues

#### Inductive Adder Design

- Schematic

- Contributors to the Droop of the Output Waveform

- Compensation of Droop and Ripple

- Specifications for the First Prototype Inductive Adder

- Measurements on the Prototype Inductive Adder

- 3.5 kV Pulses w/o Modulation

- Passive Droop Compensation

- Active Droop Compensation

- Active Compensation of Droop and Ripple

- Summary and Future Work

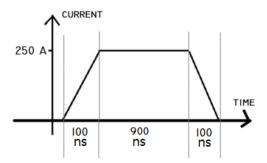

Ideal stripline current for 1 GHz option

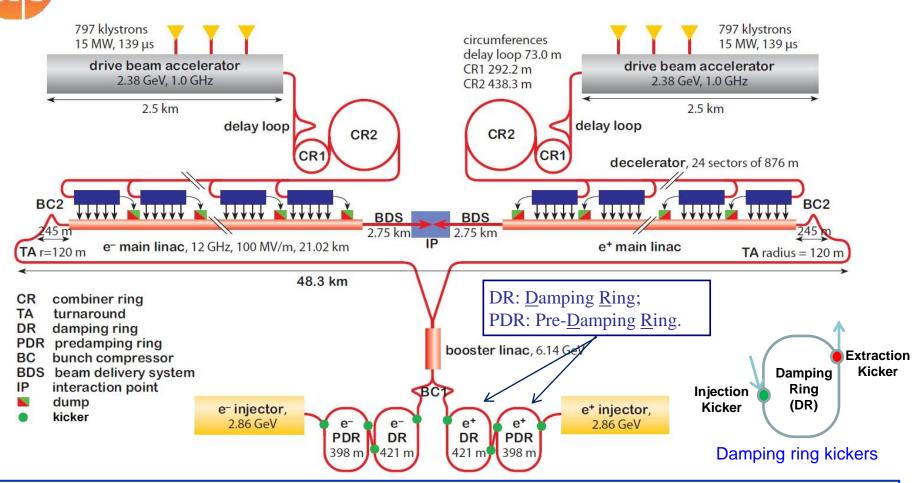

# **CLIC General Layout**

#### PDR & DR Kickers (•):

- One injection and extraction system per ring and per beam (8 systems);

- Damping rings reduce beam emittance; hence kickers must be high stability (low ripple);

- Low beam coupling impedance and good field homogeneity are required (talk by C. Belver-Aguilar).

### Specifications for the CLIC DR Extraction Kicker Systems

|                                                                | CLIC DR<br>(1 GHz   2 GHz)                                    |

|----------------------------------------------------------------|---------------------------------------------------------------|

| Pulse voltage (kV) (per Stripline)                             | ±12.5                                                         |

| Stripline pulse current [50 $\Omega$ load] (A)                 | ±250                                                          |

| Repetition rate (Hz)                                           | 50                                                            |

| Pulse flat-top duration (ns)                                   | ~160   ~900                                                   |

| Flat-top reproducibility                                       | ±1x10 <sup>-4</sup> (±0.01 %)                                 |

| Flat-top stability [inc. droop], (Inj.)per Kicker SYSTEM(Ext.) | $\pm 2x10^{-3} (\pm 0.2 \%)$<br>$\pm 2x10^{-4} (\pm 0.02 \%)$ |

| Field rise time (ns)                                           | 1000                                                          |

| Field fall time (ns)                                           | 1000                                                          |

| Beam energy (GeV)                                              | 2.86                                                          |

| Total kick deflection angle (mrad)                             | 1.5 (0.09 deg)                                                |

| Aperture (mm)                                                  | 20                                                            |

| Effective length (m)                                           | 1.7                                                           |

| Field inhomogeneity (%) [3.5mm radius]<br>[1mm radius]         | ±0.1 (Inj.)<br>±0.01(Ext.)                                    |

- NOTE:

- ➤ For rise/fall times, ≤ 100 ns desired!

- Close to 0 V intra-pulse (off-time) voltage required!

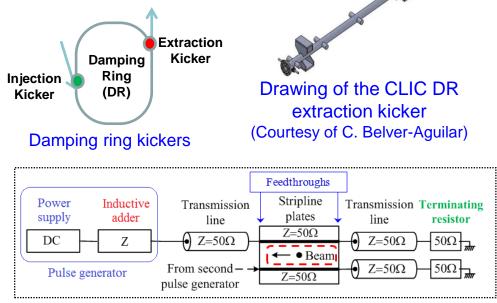

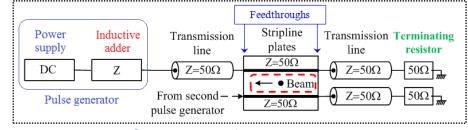

#### Schematic of a kicker system

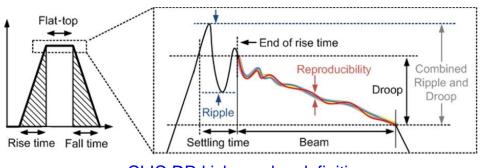

CLIC DR kicker pulse definition

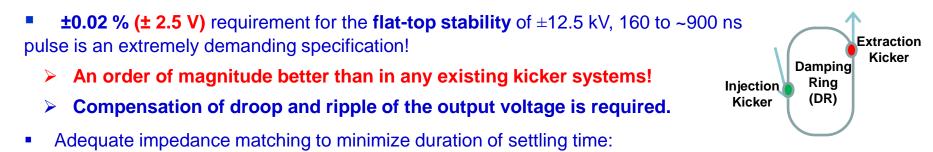

## **Challenges and Issues**

CLIC DR kicker pulse definition

Schematic of a kicker system

- > Impedance (and field homogeneity) of the stripline kicker has been optimized: unfortunately the impedance cannot be 50  $\Omega$  for both power-off (even) and power-on (odd) operation modes!

- Odd-mode impedance of the striplines is ~41 Ω (see talk by C. Belver-Aguilar), which causes settling time to be ~100 ns. Therefore the pulse flat-top duration is at least ~260 ns (2 GHz option)

- Suitable high precision measurements of the pulse in the laboratory: better relative precision than ±2.5 V in 12.5 kV required!

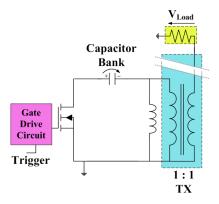

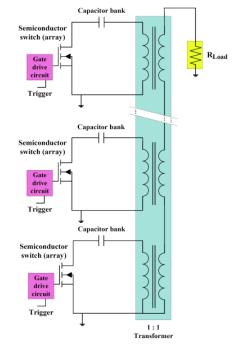

## **Inductive Adder**

- Many primary "layers", each with solid-state switches

- The output voltage is approximately the sum of the voltages of the primary constant voltage layers

- + Control electronics referenced to ground

- + No electronics referenced to high voltage despite the high voltage output of the adder

- + The output voltage can be modulated during the pulse with an analogue modulation layer

- + Modularity: the same design can potentially be used for kickers with different specifications (CLIC PDR & DR kicker modulators)

- + Redundancy and machine safety: if one switch or layer fails, the adder still gives full voltage or a significant portion of the required output pulse

- + Possibility to generate positive or negative output pulses with the same adder: the polarity of the pulse can be changed by grounding the other end of the output of the adder

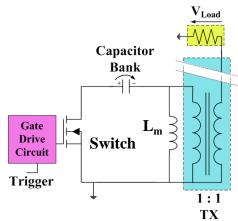

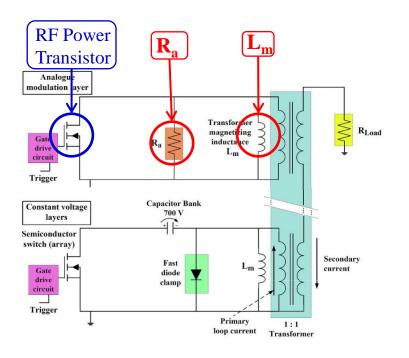

Schematic of an inductive adder

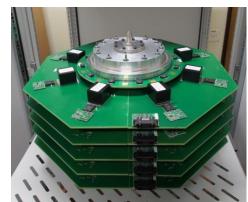

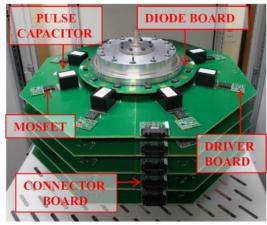

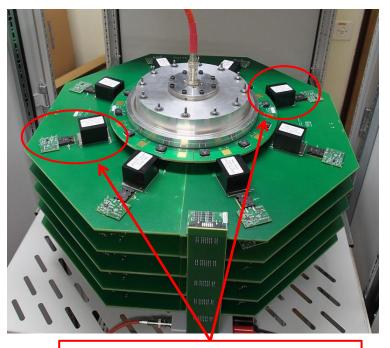

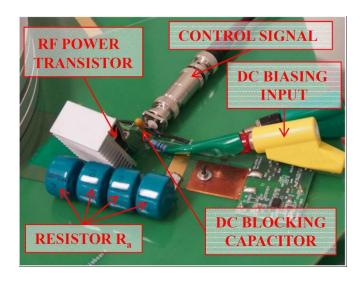

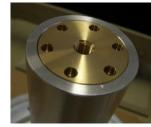

A prototype inductive adder

### Contributors to the Droop of the Output Waveform of an Inductive Adder

- > The droop of the output pulse of an inductive adder is caused by:

- The small voltage droop of the storage capacitor (**C**<sub>s</sub>) as it supplies charge during the pulse

- The resistive losses in the primary switch and in the primary circuit (R<sub>sw</sub>), which depends on the current through the magnetizing inductance (L<sub>m</sub>).

- > Only the voltage droop of the capacitors can be compensated by adding more capacitance per layer!

> The only methods to effectively decrease the droop, caused by a combination of resistive losses and magnetizing inductance of the transformer core, is to apply either passive or active analogue modulation (or both) for the output pulse.

> These methods are necessary to reach very low droop (<< 1 %).

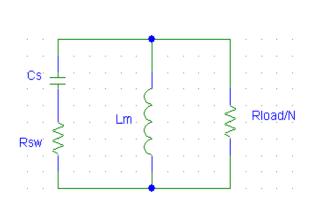

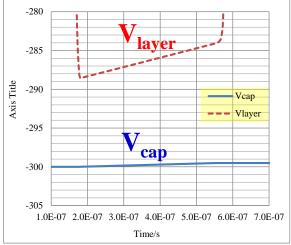

Simplified schematic of a constant voltage layer of an inductive adder

Simplified model of a layer of an inductive adder during the pulse

Capacitor voltage V<sub>cap</sub> and voltage of a layer V<sub>layer</sub> during a pulse. C<sub>s</sub> = 24 uF, Rsw = 0.34  $\Omega$  and R<sub>load</sub>/N = 10  $\Omega$ .

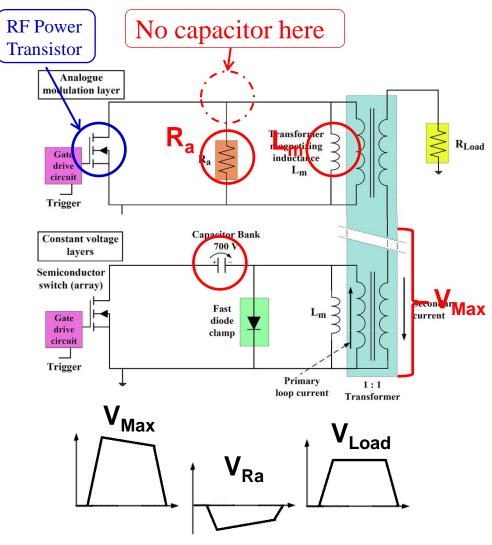

# Compensation of Droop and Ripple

- In analogue modulation layer, there is no storage capacitor but there is resistor R<sub>a</sub>

- Resistor R<sub>a</sub> is effectively in series with the load

- Load voltage during the flat-top:

$$V_{Load} \approx \frac{R_{Load}}{R_{Load} + R_a} V_{Max}$$

- $V_{Max}$  is the sum of the voltages over the layers except the analogue modulation layer:  $V_{Load} \le V_{Max}$ !

- Resistor R<sub>a</sub> is in parallel with magnetizing inductance L<sub>m</sub>

- Compensation modes:

- PASSIVE MODE: During the pulse, current through L<sub>m</sub> increases, which causes current through R<sub>a</sub> to decrease. Therefore, voltage over R<sub>a</sub> decreases, which causes V<sub>Load</sub> to increase. This voltage change is reverse in comparison with voltage droop caused by storage capacictors in other layers.

- ACTIVE MODE: A linear RF power transistor provides a shunt path for the current through resistor R<sub>a</sub>. Therefore, the voltage over R<sub>a</sub> can be controlled by controlling the current through the RF power transistor.

January 29, 2015

# Compensation of Droop and Ripple

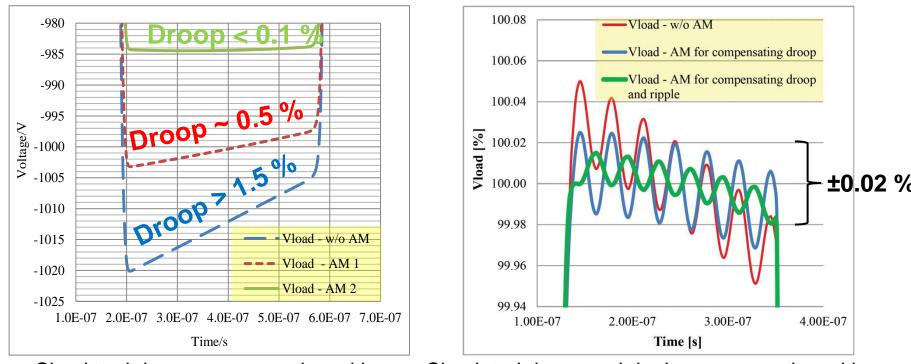

Simulated droop compensation with passive analogue modulation

Simulated droop and ripple compensation with active analogue modulation

- Passive analogue modulation partial droop compensation

- Active analogue modulation partial droop and ripple compensation

- For the CLIC DR kicker modulator, both PASSIVE and ACTIVE modulation methods will be applied!

January 29, 2015

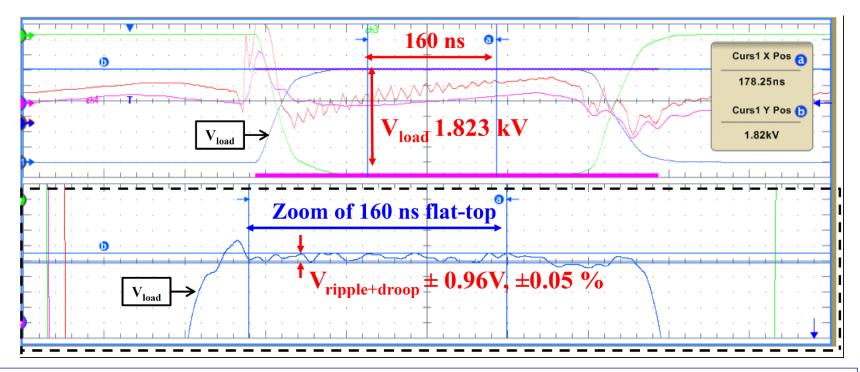

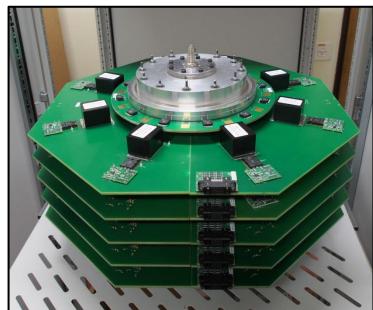

# A 5-Layer Prototype Inductive Adder

- The purpose of the prototype inductive adder has been:

- > To verify experimentally design steps for the high precision inductive adder

- > To test both passive and active analogue modulation

- To approach the required ±0.02 % flat-top stability for the output pulse, as specified for the CLIC DR extraction kicker modulator

| Design Parameter                      | Prototype<br>Inductive Adder | CLIC DR<br>Extraction<br>Kicker<br>Modulator |

|---------------------------------------|------------------------------|----------------------------------------------|

| Output Voltage (kV)                   | 3.5                          | 12.5                                         |

| Output Current [50 $\Omega$ load] (A) | 70 (250)                     | 250                                          |

| Voltage per layer                     | 700                          | 700                                          |

| Number of layers                      | 5                            | 20                                           |

| Pulse flat-top duration (ns)          | * <b>350</b> (900)           | 160 – 900                                    |

| Pulse rise time [0.1-99.9 %] (ns)     | 100                          | < 1000                                       |

| Pulse fall time [0.1-99.9 %] (ns)     | 100                          | < 1000                                       |

| Flat-top stability (for 160 ns)       | ±0.02 %                      | ±0.02 %                                      |

| Repetition rate (Hz)                  | 50                           | 50                                           |

\* limited by transformer cores, design value 900 ns

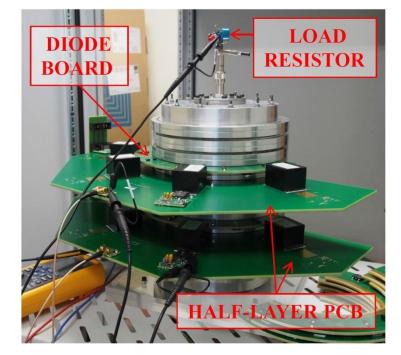

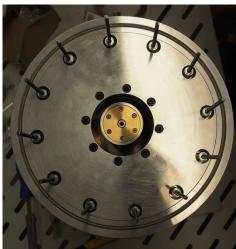

The prototype inductive adder with two half-layers inserted

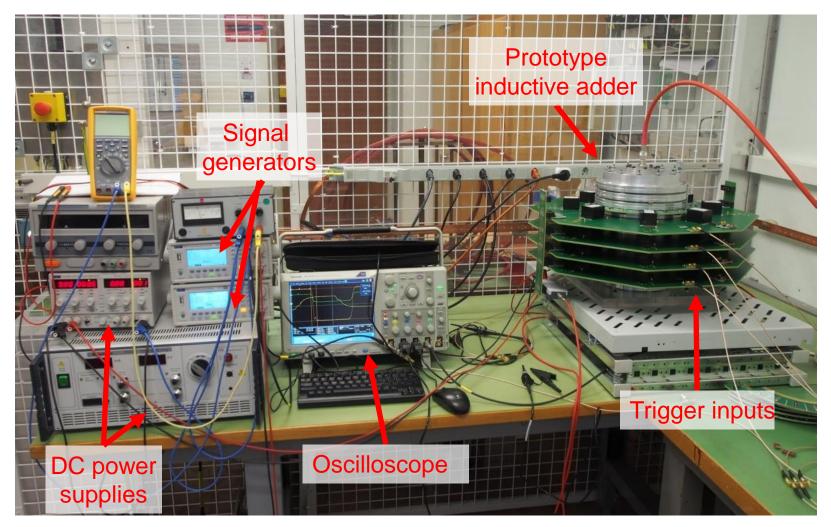

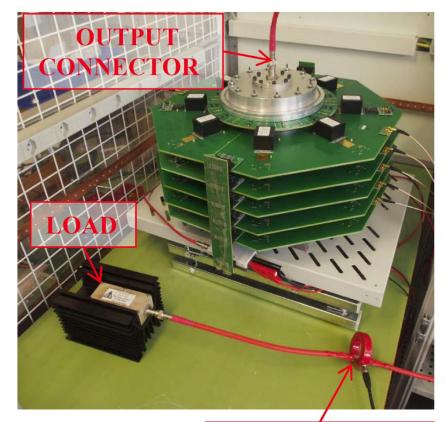

### Measurements on the 5-Layer Prototype Inductive Adder

#### The prototype inductive adder with the measurement setup

January 29, 2015

**CLIC WS 2015**

### Measurements on the 5-Layer Prototype Inductive Adder

### CURRENT TRANSFORMER

The prototype inductive adder with a current transformer and a load

In initial measurements, only one branch per half-layer PCB was powered! 2 branches per layer.

January 29, 2015

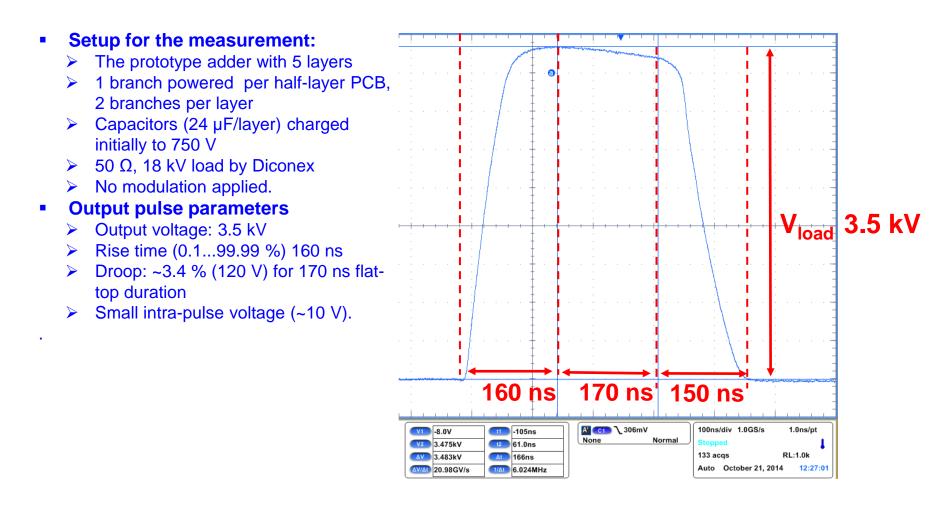

### Measurements: 3.5 kV Output Pulse - No Modulation

### Measurements: Passive Compensation of Droop and Active Compensation of Droop and Ripple

#### Setup for the measurement:

- The prototype adder with 4 constant voltage layers and an analogue modulation layer

- 1 branch powered per half-layer PCB, 2 branches per layer

- Capacitors (24 µF/layer) charged initially to 350...553 V.

- Passive or active analogue modulation applied

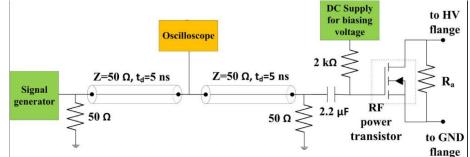

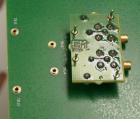

Schematic and layout of the active analogue modulation layer

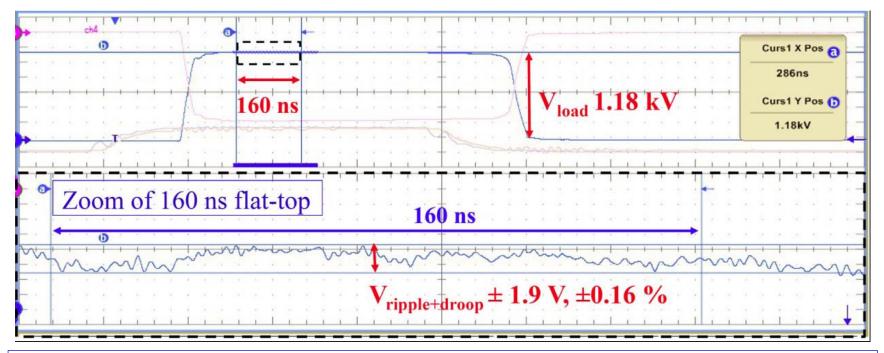

### Measurements: Passive Droop Compensation

#### • Setup for the measurement:

- 4 constant voltage layers and a passive analogue modulation layer

- > 1 branch powered per half-layer PCB, 2 branches per layer

- > Capacitors (24  $\mu$ F/layer) initially charged to 350 V (R<sub>a</sub> = 7.9  $\Omega$ )

#### Notes:

- Tektronix scope used (DPO 5034) has a nominal vertical resolution of 8 bits (< ±0.4%) can be improved with oversampling and averaging

- The curve is an average of 1000 measured pulses

- The optimal combination of  $R_a \& L_m$  depends on the output voltage!

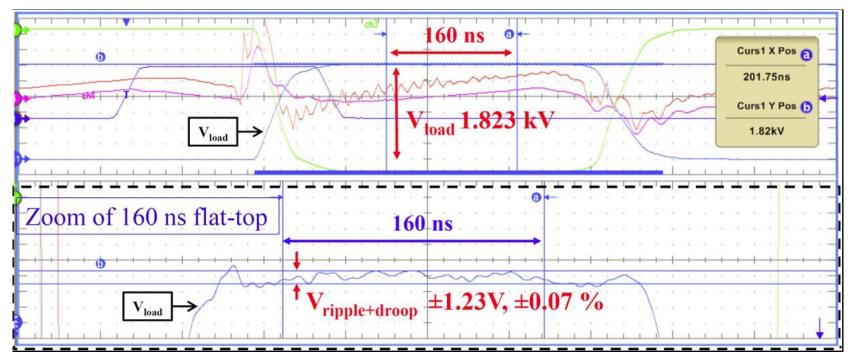

### Measurements: Active Droop Compensation

#### • Setup for the measurement:

- 4 constant voltage layers and a passive analogue modulation layer

- > 1 branch powered per half-layer PCB, 2 branches per layer

- Capacitors (24 μF/layer) initially charged to 551 V ( $R_a = 7.9 \Omega$ )

- Active droop compensation with piece-wise linear ramp function

#### **Notes:**

- The curve is average of 1000 measured pulses

- Repeat of the measurement with averaging of 4000 pulses resulted in  $\pm 1.17 \text{ V} (\pm 0.06 \%)!$

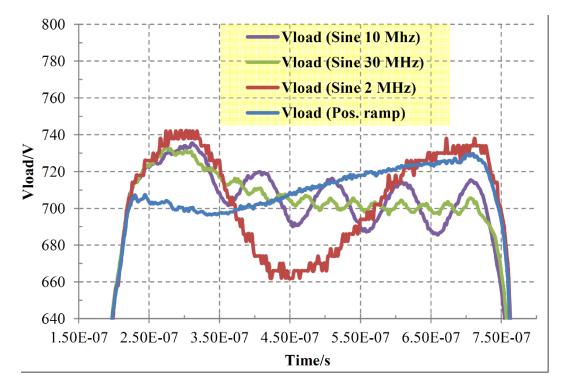

### Measurements: Active Ripple Generation

#### Setup for the measurement:

- 4 constant voltage layers and a passive analogue modulation layer

- 1 branch powered per half-layer PCB, 2 branches per layer

- > Capacitors (24  $\mu$ F/layer) initially charged to 200 V (R<sub>a</sub> = 7.9  $\Omega$ )

- Active ripple generation with a positive ramp (blue) and 2 MHz (red), 10 MHz (purple) and 30 MHz (green) sine waves.

#### Note:

• Modulation range: ~10 % of the maximum output voltage

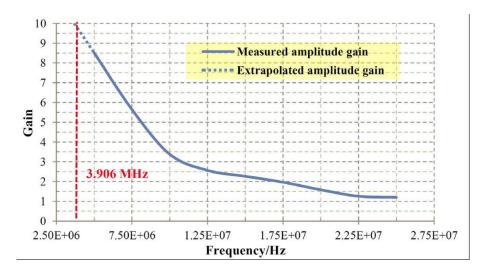

### Measurements: Active Ripple Compensation

#### Setup for the measurement:

- The prototype adder with 5 layers

- 1 branch powered per half-layer PCB,

2 branches per layer

- Capacitors (24 µF/layer) charged initially to 551 V

- Active analogue modulation layer

- Modulation signal: a ramp + a sine wave with a frequency of 5...25 MHz.

#### Steps for active ripple compensation

- Gain and phase responses for the injected compensation signal from the signal generator to the load voltage were measured

- Correction factor were defined for compensation signal

- Load voltage was measured

- Fast Fourier Transformor (FFT) was applied to define the most significant ripple components

- A compensation signal, consisting of ramp to compensate the droop and a a sine wave to compensate the most significant ripple component was created.

- The compensation signal was applied and the load voltage was measured.

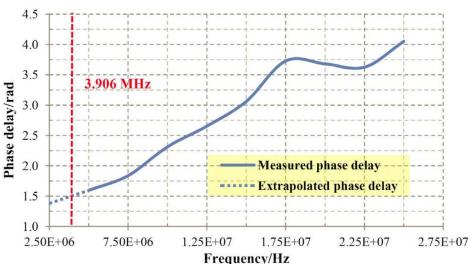

### Measurements: Active Ripple Compensation

#### Setup for the measurement:

- > 4 constant voltage layers and a passive analogue modulation layer

- > 1 branch powered per half-layer PCB, 2 branches per layer

- Capacitors (24  $\mu$ F/layer) initially charged to 551 V (R<sub>a</sub> = 7.9 Ω)

- Active droop and ripple compensation

#### **Notes:**

- The curve is an average of 1000 measured pulses

- Repeat of the measurement with averaging of 4000 pulses resulted in  $\pm 1.02 \text{ V} (\pm 0.06 \%)!$

### **Evaluation of Accuracy of the Measurements**

- The effective bit length of a 8-bit ADC is 6-7 bits.

- The effective bith length of the oscilloscope can be increased with the following means

- Oversampling (OS)

- Ensemble averaging (EA)

- Both these methods were applied

- Accuracy of the measurements

- > Active droop compensation:

- The best measurements: ±0.06 % (± 1.17 V)

- The effective number of bits of the ADC:

6 (effective length of bits) + 1 (OS,4x) +

6 (EA,4k) = 13

- Absolute precision: **0.37 V** (in the range of 3 kV)

- > Active droop and ripple compensation:

- The best measurements :**±0.05 %** (**± 0.96 V**)

- The effective number of bits: 6 + 1 (OS,4x) + 5 (EA,1k) = 12

- Absolute precision: **0.73 V** (in range of 3 kV).

- With EA of 4k, the numbers were ±0.06 % (± 1.02 V), 13 bits and 0.37 V.

| Mod.<br>method                  | PM<br>(d) | AM (d)                   | AM (d&r)                 |

|---------------------------------|-----------|--------------------------|--------------------------|

| ΔU <sub>d+r</sub> (%)           | ±0.16     | ±0.07 (1k)<br>±0.06 (4k) | ±0.05 (1k)<br>±0.06 (4k) |

| $\Delta U_{d+r}$ (V)            | ±1.9      | ±1.23 (1k)<br>±1.17 (4k) | ±0.96 (1k)<br>±1.02 (4k) |

| Res <sub>Enh,OS</sub><br>(bits) | 0         | 1<br>1                   | 1<br>1                   |

| Averaging<br>(n)                | 100       | 1000<br>4000             | 1000<br>4000             |

| Res <sub>Enh,EA</sub><br>(bits) | 3.3       | 5 (1k)<br>6 (4k)         | 5 (1k)<br>6 (4k)         |

| V <sub>r,ADC</sub> (V)          | 2000      | 3000 (1k)<br>3000 (4k)   | 3000 (1k)<br>3000 (1k)   |

| Res <sub>Rel</sub> (%)          | 0.16      | 0.024 (1k)<br>0.012 (4k) | 0.024 (1k)<br>0.012 (4k) |

| Res <sub>Abs</sub> (V)          | 3.2       | 0.73<br>0.37             | 0.73<br>0.37             |

$\Delta U_{d+r}$  = combined droop and ripple (flat-top instability), Res<sub>Enh,OS</sub> = resolution enhancement by oversampling (averaging of samples), Res<sub>Enh,EA</sub> = resolution enhancement by ensemble averaging (averaging of pulses), V<sub>r</sub> = voltage range of a measurement channel, Res<sub>Rel</sub> = relative accuracy, Res<sub>Abs</sub> = absolute accuracy

Two 5-layer, 3.5 kV prototype inductive adders have been built and tested at CERN

Both passive and active analogue modulation methods tested to improve the flat-top stability of the output pulses

➤ The best measured flat-top stability for 160 ns pulse flat-top has been ±0.05 % (±0.96 V) at 1.8 kV, which was reached by applying active droop and ripple compensation.

➤The final goal is to reach the stability requirement for the CLIC DR extraction kicker modulator (±0.02 %)

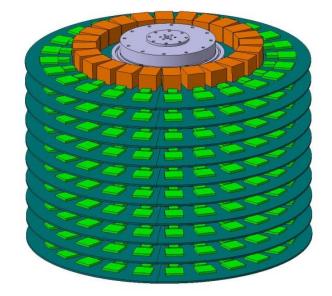

#### The full-size 12.5 kV, 250 A, CLIC DR kicker prototype inductive adders are currently being designed at CERN

➤ The design of 12.5 kV inductive adders is based on the design of the two 5-layer prototype inductive adders.

# **Future Work**

Improve the precision of the active analogue modulation, to meet ±0.02 % requirement for the combined droop and ripple:

Measurements with new magnetic cores, pulse duration up to 900 ns

➤ A new active analogue modulation layer with improved precision of ripple compensation (an RF amplifier between the RF MOSFET and a signal generator)

- Measurements with a 16-bit oscilloscope

- Measurements of two 12.5 kV inductive adders with a stripline kicker installed in a beamline in an accelerator test facility

- Other possible applications for inductive adder technology at CERN:

- FCC kicker systems (20 kV, 3.6 kA, 2.5 μs)

- ➢ PS KFA kicker system (40 kV, 1.5 kA, 2.6 µs)

3D model of a future inductive adder at CERN (Courtesy of P. Faure)

### Questions & Comments?

**CLIC WS 2015**

January 29, 2015

# **References and Bibliography**

- 1. Holma J., Barnes M.J.: "The Prototype Inductive Adder With Droop Compensation for the CLIC Kicker Systems.", IEEE Trans. Plasma Sci., Vol. 42, No. 10, Oct. 2014.

- 2. Holma J., Barnes M.J., Belver-Aguilar C.: "Measurements on a Prototype Inductive Adders with Ultra-flat-top Output Pulses for CLIC Kicker Systems", Proc. IPAC'14, Dresden, Germany, June 15-20, 2014.

- 3. Holma J., Barnes M.J.: "Initial Measurements on a Prototype Inductive Adder for the CLIC Kicker Systems", Proc. of PPC'13, San Francisco, CA, USA, June 16-21, 2013.

- 4. Holma J., Barnes M.J., Ovaska S.J.: "Modelling of Parasitic Inductances of a High Precision Inductive Adder for CLIC", Proc. of IPAC'13, Shanghai, China, May 12-17, 2013.

- 5. Holma J., Barnes M.J.: "Sensitivity Analysis for the CLIC Damping Ring Inductive Adder", Proc. of Int. Power Modulators and High Voltage Conference, San Diego, CA, USA, Jun. 3-7, 2012.

- 6. Holma J., Barnes M.J.: "Evaluation of Components for the High Precision Inductive Adder for the CLIC Damping Rings", Proc. of IPAC 2012, New Orleans, USA, May 20-26, 2012.

- 7. Holma J., Barnes M.J.: "Pulse Power Modulator Development for the CLIC Damping Ring Kickers", CLIC-Note-938, CERN, Geneva, Switzerland, April 27, 2012.

# **Spare Slides**

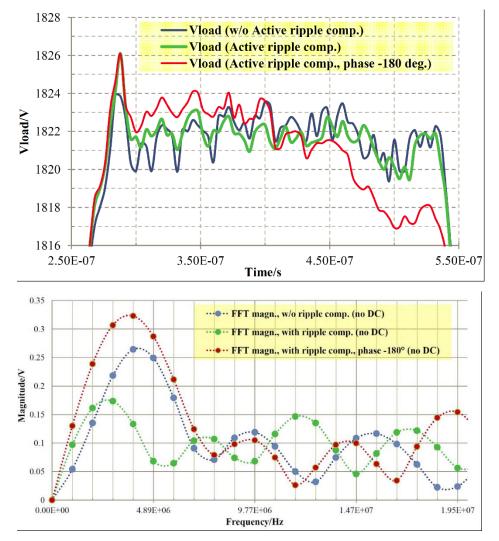

### Demonstration of Active Ripple Compensation in Time and Frequency Domains

#### Time domain

- Original waveform: load voltage with ramp compensation applied (blue)

- Compensated waveform (green): the droop and the most significant ripple frequency has been compensated

- A ripple component deliberately amplified (red): the most significant ripple component has been amplified (phase shift of the ripple component -180 degrees in comparison with the green curve)

#### Frequency domain

- Magnitudes of FFTs of the original load voltage (blue), ripple compensation applied (green) and a ripple component amplified (red).

- FFT of original waveform: load voltage with ramp compensation applied (blue)

- FFT of compensated waveform (green): the droop and the most significant ripple frequency has been compensated

- FFT of a the waveform in which a ripple component has been amplified (red): phase shift of a ripple component -180 degrees in comparison with the green curve