### **HV-CMOS Simulation**

Matthew Buckland

University of Liverpool

CERN

#### **Outline**

- . TCAD

- The study of two biasing schemes

- HV-CMOS submission/reticle edge study

- Summary

#### **TCAD**

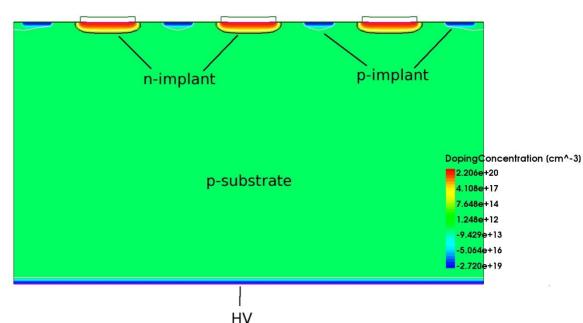

- Computer simulations for semiconductor devices

- Simple diode, n-in-p device

- 3 diode array, (90x50)µm

- Resistivity =  $1000\Omega$ cm

- Implant doping 1x10<sup>20</sup>cm<sup>-3</sup>

- Full RD50 radiation model

- Bias = -60V

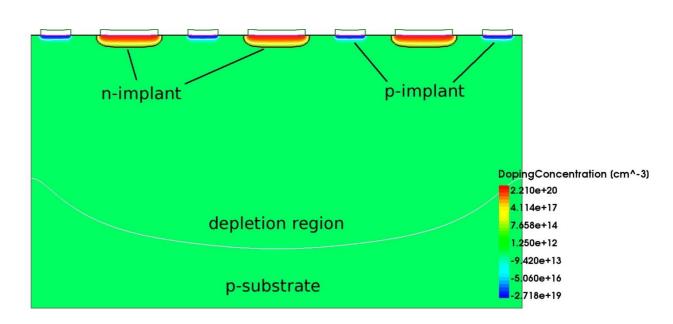

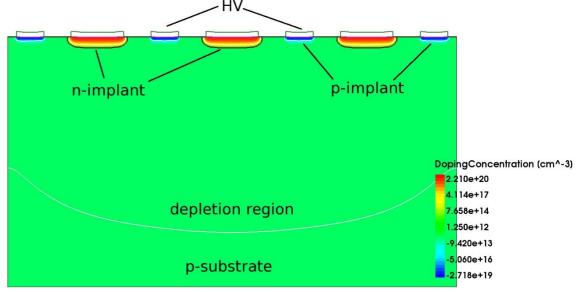

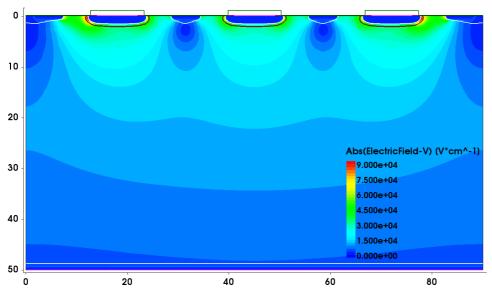

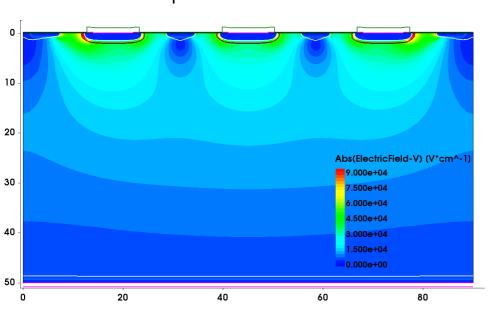

## The Two Bias Schemes compared

HV top

- HV back (p-implants floating)

- Full depletion at -60V (50µm thickness)

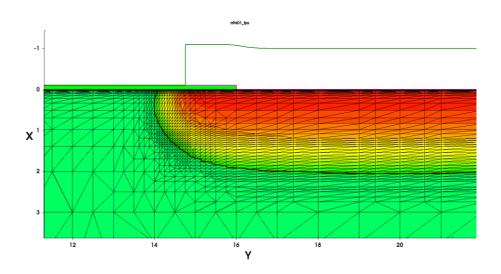

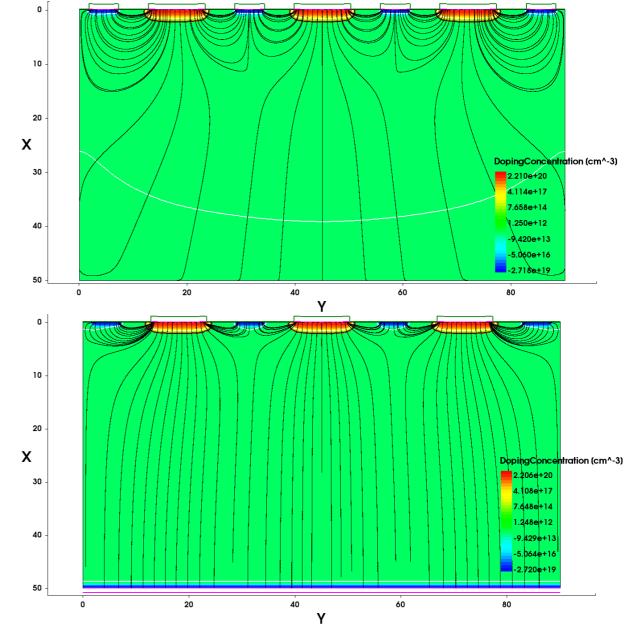

## E-field Lines Comparison

HV top

- HV back

- More uniform field

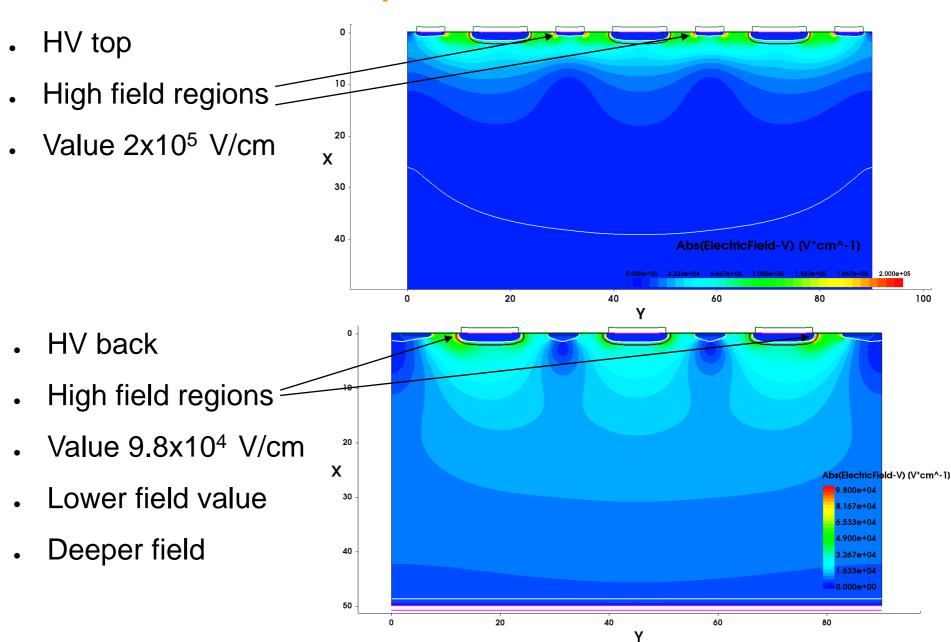

### E-field Value Comparison

CLIC Workshop, CERN 2015

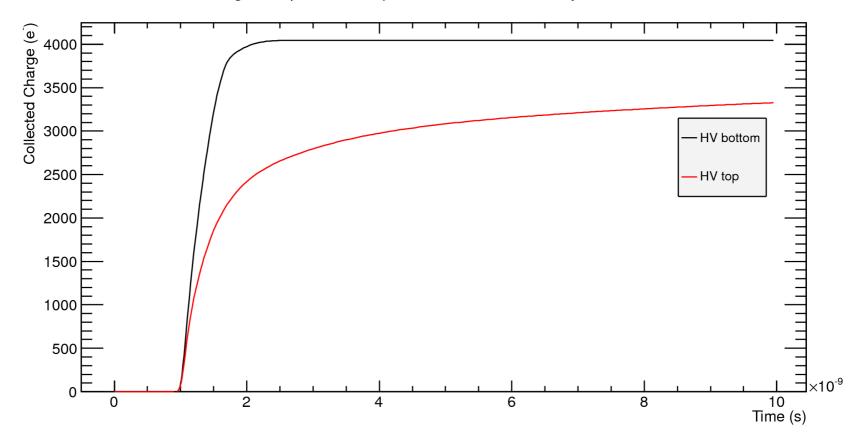

## **Charge Collection Comparison**

- Mip enters at 1ns at width of 45µm, 80eh pairs per µm

- Deposits total charge of 4000e<sup>-</sup>

- Back bias full charge collection at 2ns compared to ≈60% for HV top

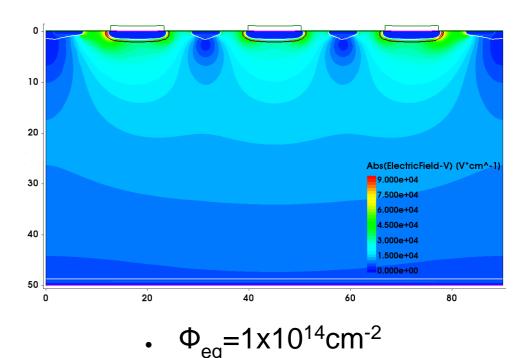

#### E-field with Radiation

•  $\Phi_{eq} = 1 \times 10^{13} \text{cm}^{-2}$  (CLIC)

$$\Phi_{eq} = 1 \times 10^{15} \text{cm}^{-2}$$

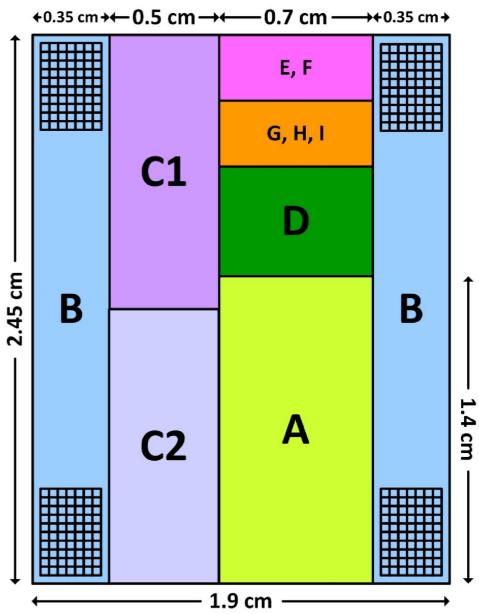

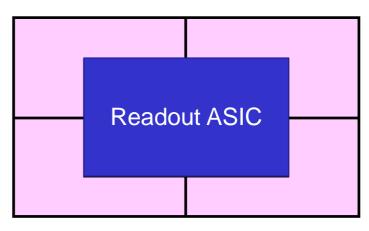

## Floorplan

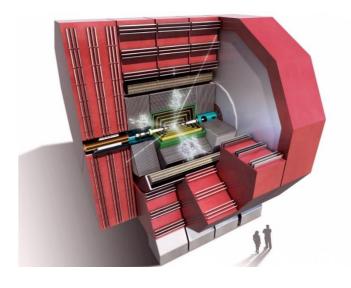

- Planned AMS350 submission (Liverpool, Geneva, KIT, Bern)

- Section B

- Dedicated part to test fan out structure in metal layers

- Macro pixels with pixel readout

- Read larger area sensor with single pixel ASIC

E.Figueras. Engineering run with 0.35µm CMOS HV from AMS. Floorplan.

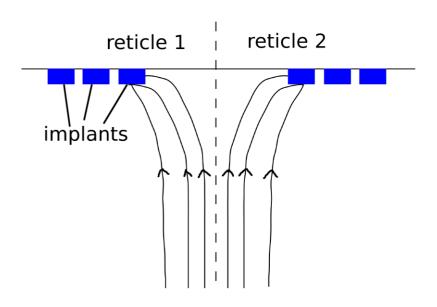

# E-field at Edges of Reticles

- Test possibility of using undiced sensor

- If one to one ASIC sensor still easier tilling

- Or use macro pixel sensors (multi-reticle) with one ASIC

- Need TCAD study for charge collection at the reticle edges

- Look at design rules in this region

- Optimise design for best charge collection

4 CMOS reticles, 1 ASIC

## Summary and Future Work

- Study of top vs. back bias

- Full depletion at lower bias for HV back

- More uniform fields

- Lower value high field region

- Want to study the possibility of undiced sensors (either easier tiling or macro pixel assemblies)

- TCAD study of signal collection at the edge