Advanced European Infrastructures for Detectors at Accelerators

# **Timepix readout**

Michael Lupberger University of Bonn

AIDA Final Meeting December 10 2014, CERN

AIDA is co-funded by the European Commission within the Framework Programme 7 Capacities Specific Programme, Grant Agreement 262025

Subtask 9.2.3 (CEA, Bonn, NIKHEF): Common **readout systems** for gaseous detectors. Auxiliary electronics for the read-out of **pixellated front-end chips**, aimed at highly granular pixel read-out of **gas detectors**, are to be developed.

Subtask 9.2.3 (CEA, Bonn NIKHEF):

Common readout systems for gaseous detectors.

Auxiliary electronics for the read-out of

pixellated front-end chips, aimed at highly granular pixel

read-out of gas detectors, are to be developed.

Subtask 9.2.3 (CEA, Bonn NIKHEF): Common readout systems for gaseous detectors. Auxiliary electronics for the read-out of pixellated front-end chips, aimed at highly granular pixel read-out of gas detectors, are to be developed. <u>Scalable Readout System (SRS)</u>

Subtask 9.2.3 (CEA, Bonn, NIKHEF):

Common readout systems for gaseous detectors.

Auxiliary electronics for the read-out of

**pixellated front-end chips** aimed at highly granular pixel read-out of **gas detectors**, are to be developed.

Timepix3 chip

Subtask 9.2.3 (CEA, Bonn, NIKHEF): Common readout systems for gaseous detectors. Auxiliary electronics for the read-out of **pixellated front-end chips**, aimed at highly granular pixel read-out of gas detectors, are to be developed. <u>Speedy Plxel Detector Readout (SPIDR)</u>

#### Outline

- Introduction

- Timepix Readout

- Chip

- SRS

- Implementation

- Timepix3 Readout

- Chip

- SPIDR

- Implementation

- Summary and Outlook

- Slow readout speed

- Challenges for the readout (2011): - (Available) for only up to 8 chips, no scalability

- Frame based readout (1 Mbit of data)

- 14 bit counter in each pixel (ToA or ToT) - Noise threshold  $\sim 500e^{-}$  (ENC  $\approx 90e^{-}$ )

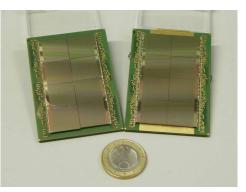

- Active surface:  $1.4 \times 1.4 \text{ cm}^2$

- Pixel size 55 x 55  $\mu$ m<sup>2</sup> on 256 x 256 array

- AIDA

- Universal readout chip

- **Properties:**

universität**bonn**

### Starting point 2011

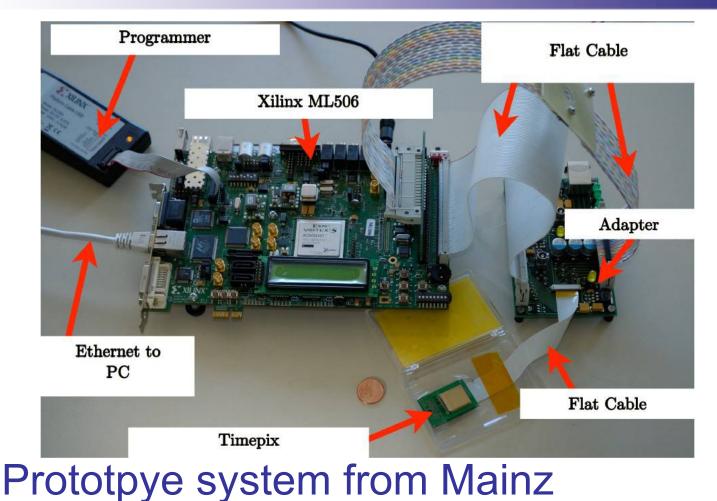

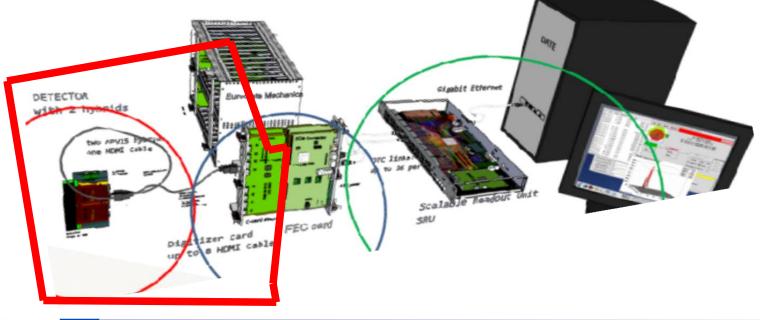

Goal: SRS

Developed within RD51 (OpenSource)

- Provides common hard- and firmware

- Uses cheap standard components

- User part: chip carrier, adapter card, FPGA firmware

#### SRS

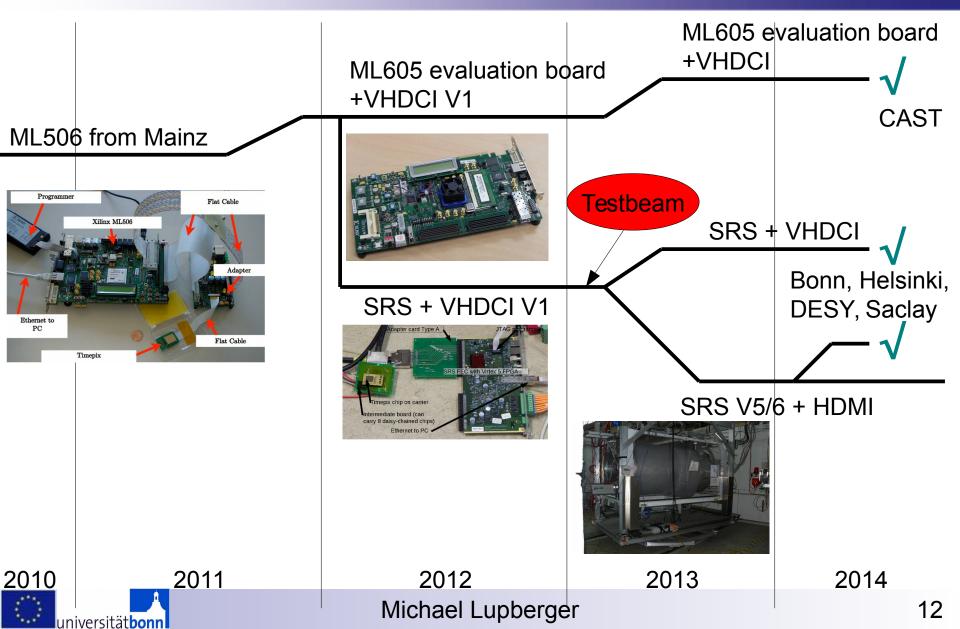

Implementation in SRS

- Single Timepix or Octoboard

- Intermediate board

- A type adapter card

- SRS FEC with

Virtex5/6 FPGA

- Ethernet to PC

#### Michael Lupberger

#### System evolution

universität**bonn**

## Highlights

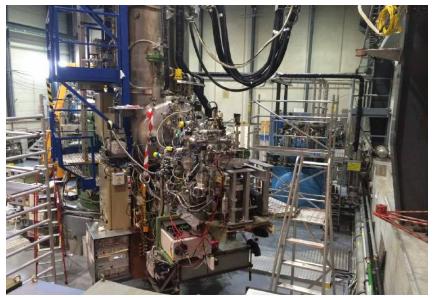

System verification at DESY testbeam 2013

#### Timepix readout at CAST 2014 run period

#### Timepix3

#### • Available since September 2013

|                   | Timepix                                                                      | Timepix3                                                                              |

|-------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Pixel matrix      | 256 x 256                                                                    |                                                                                       |

| Pixel size        | 55 μm x 55 μm                                                                |                                                                                       |

| Technology        | 250 nm CMOS                                                                  | 130nm CMOS                                                                            |

| Readout           | 1. Frame based                                                               | <ol> <li>Data driven</li> <li>Frame based</li> </ol>                                  |

| Zero suppression  | no                                                                           | yes                                                                                   |

| Acquisition modes | <ol> <li>Charge (TOT)</li> <li>Time (TOA)</li> <li>Event counting</li> </ol> | <ol> <li>1. TOT and TOA</li> <li>2. TOA</li> <li>3. Event counting and TOT</li> </ol> |

- Challenges for readout

- Not available

universität**bonn**

- High data rate: 5.12 Gbit/s

- Speedy Plxel Detector Readout

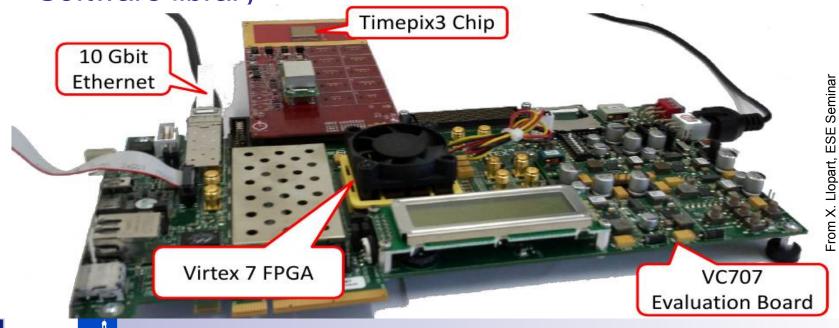

- Based on Xilinx evaluation board (Virtex7 FPGA)

- 10 Gbit/s Ethernet

- Timepix3/Medipix3 adapter card on FMC connector

- Software library

Michael Lupberger (On behalf of our NIKHEF colleagues) 15

#### SPIDR

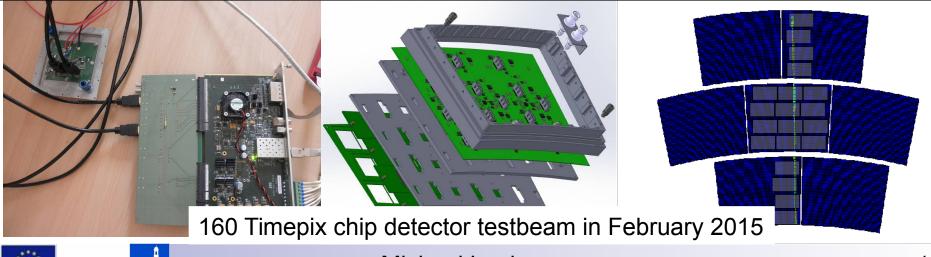

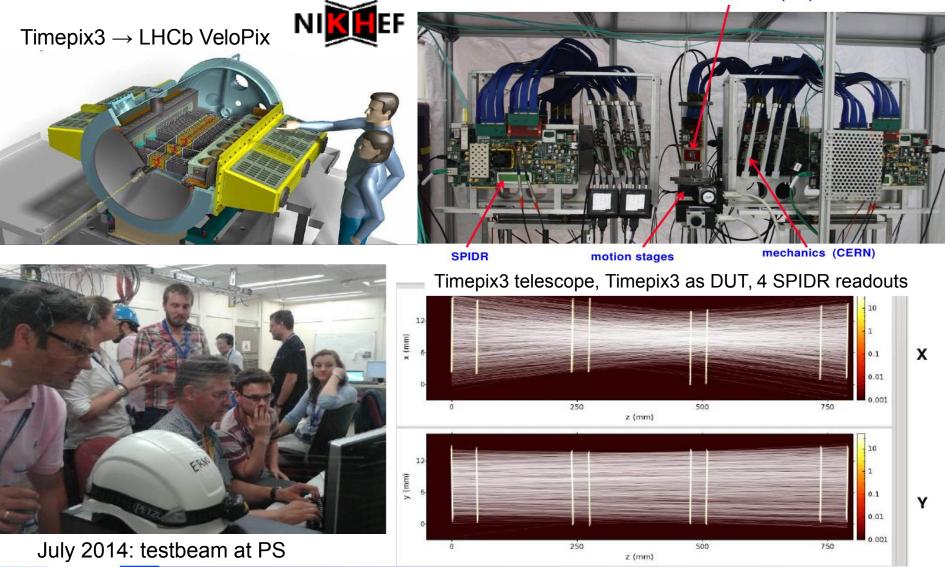

- NIKHEF Timepix3 adapter board

- CERN Timepix3 chip carrier and adapter board to FMC

## Highlights

Device under Test (DuT)

Michael Lupberger (On behalf of our NIKHEF colleagues) 17

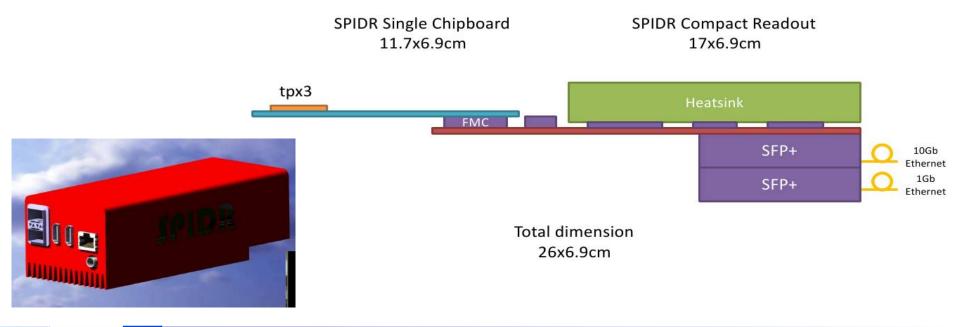

#### Compact SPIDR

- Dedicated board with FPGA, FMC plug, 10Git/s and 1 Gbit/s Ethernet

- Prototype finished, 3 boards in production

#### **AIDA** contribution

- MS 41: Intermediate state (Month 23)

- D9: Deliverable (Month 40)

- Estimated indicative person-months: 27

- AIDA financial contribution as requested

- Financial contribution from institutes as required

- Subtask 9.2.3 successfully finished

- Readout for two pixellated front-end chips:

- Timepix: small system on Xilinx evaluation board integration in SRS for larger systems

- Timepix3: SPIDR on Xilinx evaluation board

- compact SPIDR on small dedicated PCB

- Demonstration of readout in testbeam

- Systems are used in experiments

- Advancements ongoing

#### Thanks

People in Subtask 9.2.3:

- NIKHEF: Nigel Hessey, Martin van Beuzekom, Jan Visser, Bas van der Heijden

- CEA Saclay: David Attié, Paul Colas

- Uni Bonn: Klaus Desch, Jochen Kaminski, Michael Lupberger