# ALICE Inner Tracking System (ITS) Upgrade Overview

L. Musa (ALICE ITS Project Leader) - CERN

4<sup>th</sup> ALICE ITS, MFT and O2 Asian workshop Pusan, South Korea, 15-16 December 2014

# ALICE ITS Upgrade Overview

# **Status and Plans**

#### OUTLINE

- Upgrade of the ALICE ITS: motivations and specifications

- Layout and main components of the new ITS

- Status and plans

- Conclusions

Disclaimer: this talk is not a comprehensive review of the ITS upgrade but rather focuses on the aspects of the project relevant with Asian contribution

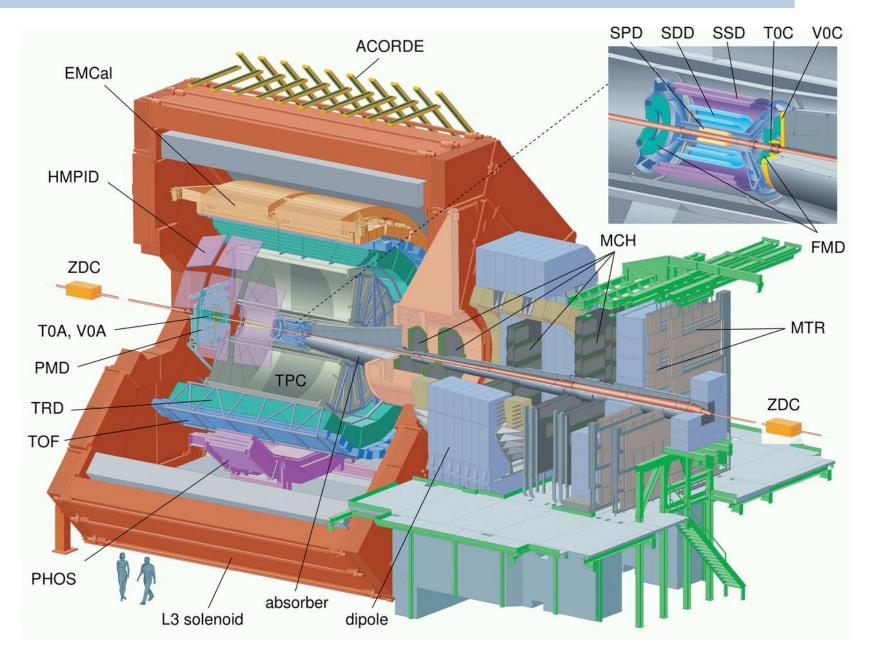

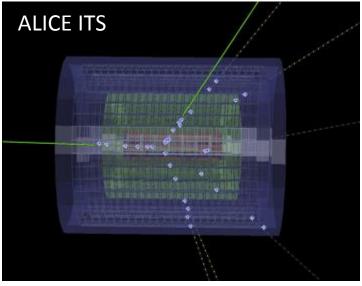

### The Current ALICE Detector

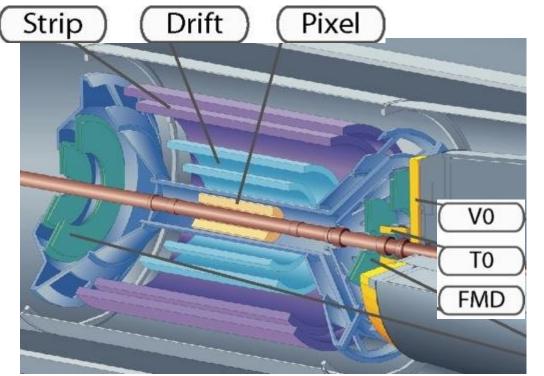

# The Current ALICE Inner Tracking System

#### Current ITS

6 concentric barrels, 3 different technologies

- 2 layers of silicon pixel (SPD)

- 2 layers of silicon drift (SDD)

- 2 layers of silicon strips (SSD)

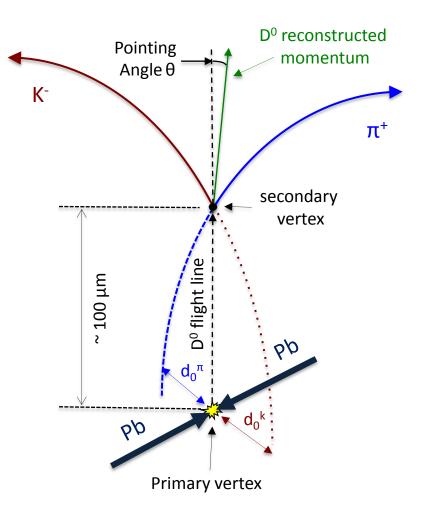

# Performance – Secondary vertex determination

#### Example: D<sup>0</sup> meson

#### Open charm

| Particle              | Decay Channel                        | <b>c</b> τ (μm) |  |

|-----------------------|--------------------------------------|-----------------|--|

| D <sup>0</sup>        | K <sup>-</sup> π <sup>+</sup> (3.8%) | 123             |  |

| D+                    | K⁻ π⁺ π⁺ (9.5%)                      | 312             |  |

| D <sub>s</sub> +      | K⁺ K⁻ π⁺ (5.2%)                      | 150             |  |

| $\Lambda_{c}^{\star}$ | p K⁻ π⁺ (5.0%)                       | 60              |  |

How precisely is d<sub>0</sub> measured with the current ITS detector?

Analysis based on decay topology and invariant mass technique

### ALICE ITS Upgrade – Impact parameter resolution

Very good MC description colliding system 600 300  $d_{0,xy}$  resolution ( $\mu m$ )  $d_{0,xy}$  resolution ( $\mu m$ ) ALICE ALICE 500 250 pp  $\sqrt{s} = 7 \text{ TeV}$ charged particles 400 ▲ pp  $\sqrt{s} = 7 \text{ TeV}$ 200  $\bigtriangleup$ data, pions **p**-Pb  $\sqrt{s_{NN}} = 5.02 \text{ TeV}$ data, kaons 300 data, protons • Pb-Pb  $\sqrt{s_{NN}} = 2.76 \text{ TeV}$ 150 MC, pions MC, kaons 200 100 MC, protons 100 50 0 0 0.3 0.4 2 3  $10^{-1}$ 10 1 p<sub>T</sub> (GeV/c)  $p_{\tau}$  (GeV/c) ALICE, Int. J. Mod. Phys. A29 (2014) 1430044 ALICE, Int. J. Mod. Phys. A29 (2014) 1430044

Very weak dependence on the

110 - 120  $\mu$ m at p<sub>T</sub> = 500 MeV/c

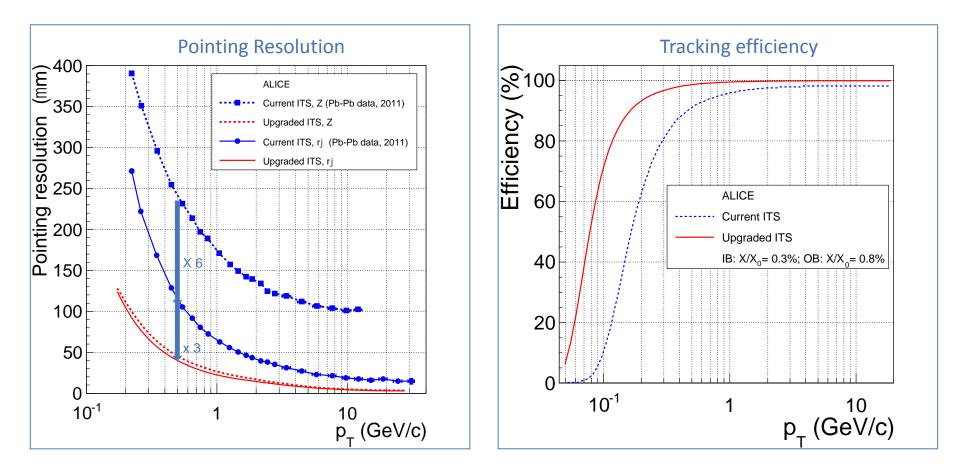

- 1. Improve impact parameter resolution by a factor of ~3

- Get closer to IP (position of first layer): 39mm ⇒22mm

- Reduce  $x/X_0$  /layer: ~1.14%  $\Rightarrow$  ~ 0.3% (for inner layers)

- Reduce pixel size: currently 50μm x 425μm 🜩 28μm x 28μm

- 2. Improve tracking efficiency and  $p_T$  resolution at low  $p_T$

- Increase granularity:

- 6 layers **>** 7 layers

- silicon drift and strips ➡ pixels

- 3. Fast readout

- readout Pb-Pb interactions at > 50 kHz and pp interactions at  $\sim 2 \times 10^5$  Hz (currently limited at 1kHz with full ITS and  $\sim 3$ kHz without silicon drift)

- 4. Fast insertion/removal for yearly maintenance

- possibility to replace non functioning detector modules during yearly shutdown

Install detector during LHCC LS2 (2018-19)

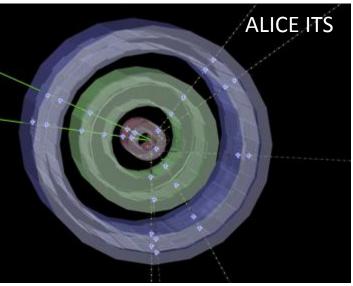

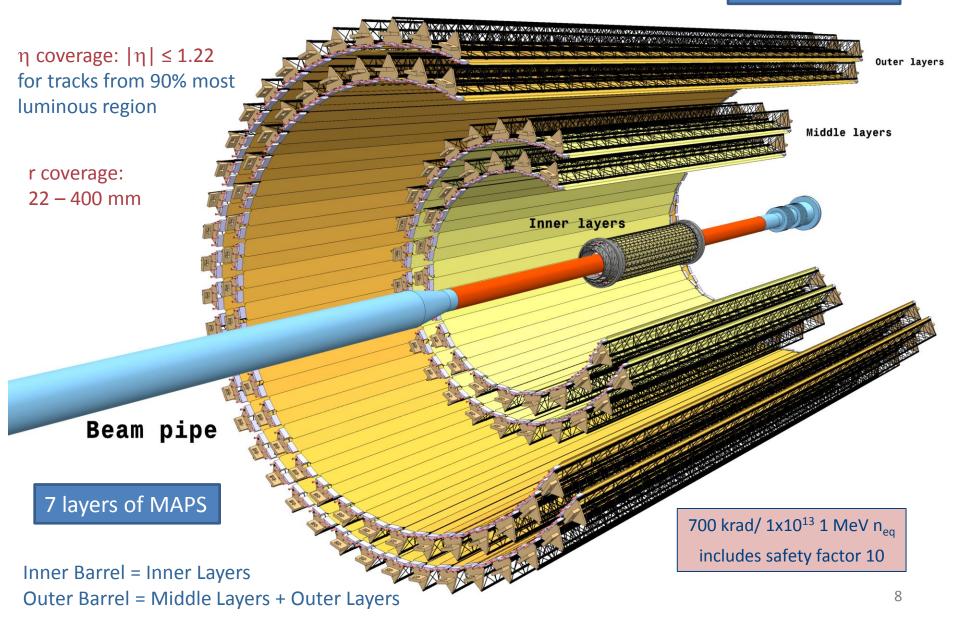

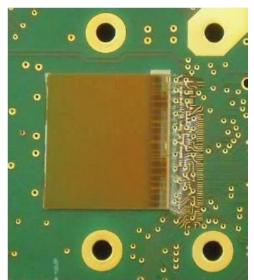

### **New ITS Layout**

12.5 G-pixel camera (~10 m<sup>2</sup>)

# Performance of new ITS

$\sim$ 40  $\mu$ m at p<sub>T</sub> = 500 MeV/c

### **Inner Barrel**

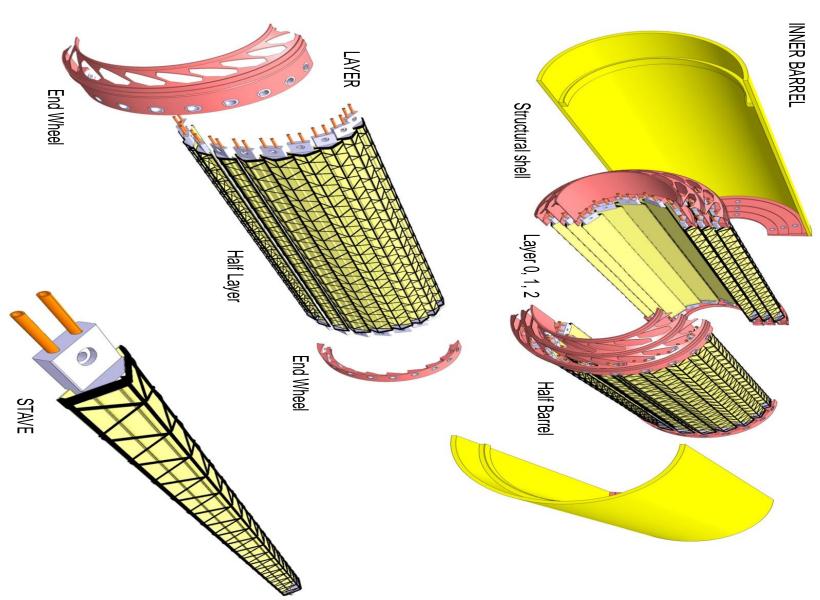

### New ITS Layout - Inner Barrel

<Radius> (mm): 23,31,39

Nr. of staves: 12, 16, 20

Nr. of chips/layer: 108, 144, 180

Power density: < 100 mW/cm<sup>2</sup>

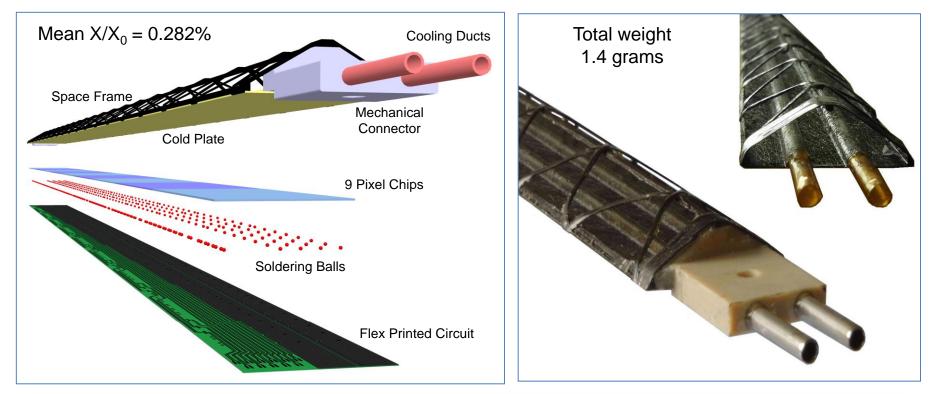

Length in z (mm): 270 Nr. of chips/stave: 9 Material thickness: ~ 0.3% X<sub>0</sub> Throughput (@100kHz): < 80 Mb/s×

# **PIXEL** Chip

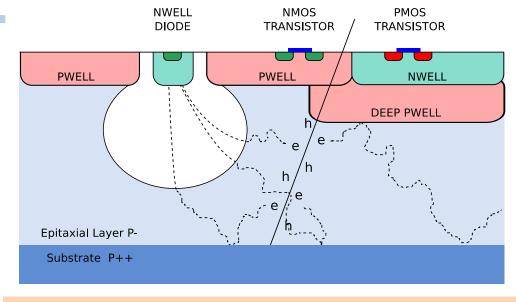

Monolithic PIXEL chip using Tower Jazz CMOS 0.18 µm

- Chip size: 15mm x 30mm

- Pixel pitch  $\sim$  30  $\mu$ m

- Spatial resolution  $\sim$  5  $\mu$ m

- Power density < 100 mW/cm<sup>2</sup>

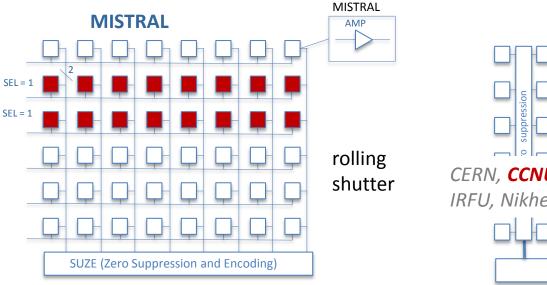

- Architectures: MISTRAL, ALPIDE

#### Deep p-well allows truly CMOS circuit inside pixel

# Pixel Chip - ALPIDE and MISTRAL full-scale prototypes in 2014

MISTRAL FSBB-M0 (Full Scale Building Block Mistral 0)

- About 1/3 of a complete sensor (approx. 9mm x 17mm)

- 416 x 416 pixels of **22μm x 33μm** (final chip **36μm x 62μm**)

- 40μs integration time (final chip ~ 20μs)

- Full chain working (front-end, discr., zero suppression)

- Chips (non irradiated) characterized at SPS

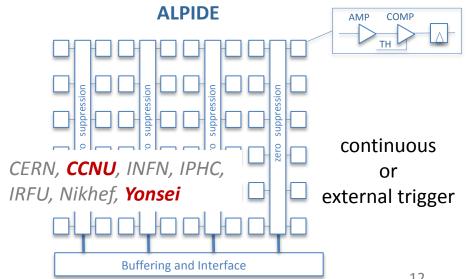

#### ALPIDE Full Scale prototype

- Dimensions: 30mm x 15 mm

- About 0.5 M pixels **28μm x 28μm**

- 40 nW front-end (4.7mW / cm<sup>2</sup>)

- ~40mW/cm<sup>2</sup> total

- Pulse width ~5 μs

#### Figure: Two FSBB M0

Chips characterized at PS, SPS, Frascati

- $\Rightarrow$  Results presented by Magnus

- $\Rightarrow$  Characterization at Korea test beam, analysis ongoing

Figure: picture of pALPIDEfs

#### ALPIDE: baseline solution

- Based on the results obtained in about 8 months of characterization, the current version of ALPIDE (p-ALPIDE1) represents already a suitable solution for the detector construction

- Completion and optimization of the chip via three new iterations

| Version      | Description                                                                                                          | Subm (to TJ) | Delivery | Test            |

|--------------|----------------------------------------------------------------------------------------------------------------------|--------------|----------|-----------------|

| pALPIDE-2    | final interface but no HSO                                                                                           | Dec 14       | Feb 15   | Feb – Jun<br>15 |

| pALPIDE-3    | Pixel FEE optimization, HSO (1.2 Gbit/s),<br>in-pixel multi-event buffer, standard-cell<br>version of matrix readout | Apr 15       | Jun 15   | Jun - Oct       |

| ALPIDE final | Possible minor improvements                                                                                          | Aug 15       | Oct 15   | Nov - Jan       |

- Production (~1400 wafers) starts Feb '16

- Module and stave development programme in 2015 based on ALPIDE prototypes => presentations of Petra, Antonello and Vito

# Pixel chip – plans till production (2/2)

#### MISTRAL-O (optimized for the Outer Barrel): fallback solution

The development of MISTRAL-O will be brought to completion, including the integration in the detector module and stave

- Mature architecture: based on the MIMOSA family

- Pixel pitch  $\sim$ 36µm x 62µm for a power of  $\sim$ 100mW/cm<sup>2</sup>

- The characterization of MISTRAL (22 $\mu m$  x 33 $\mu m$ ) FSBB in 2014 produced good results

- The basic building blocks have been qualified as standalone circuits in '13 and '14

| Version   | Description                                      | Subm (to TJ) | Delivery | Test             |

|-----------|--------------------------------------------------|--------------|----------|------------------|

| MISTRAL-O | (first) prototype with all final functionalities | June '15     | Sep '15  | Oct – Dec<br>'15 |

• Qualification of OB modules and stave based on MISTRAL-O: Jan '15 – Apr '16

# Plans for 2015 (and 2016) – Pixel Chip

#### Production and test of pixel chips

- Procurement of high resistivity silicon wafers (1500 wafers): 2015

- QA of raw silicon wafers (~10% of the total number): Jul '15 Feb '16

- Verification of physical and electrical properties (measurement of resistivity) => TMEC (Thailand)

- CMOS Manufacturing

- 4 lots, 340 wafers each: Feb '16 Jun '17 => TowerJazz

- CMOS QA

- A new lot starts only after the test (wafer probe test) of about 5% of previous lot => Yonsei (Korea) (tbc)

- Ni-Au plating => (e.g. Pactech) market survey and tendering started

- Thinning & Dicing => (mechanical or Laser? ) e.g. Rockwood, Stars

- Chip Test (Electrical, visual) => Yonsei, LIPI (Visual Inspection)

## Plans for 2015 – Module assembly

Construction of Modules and staves for the Inner Barrel and Outer barrel

- Procurement of Module Assembly Machine (MAM) => see Antonello

- First delivery (CERN): Jun '15

- Others: (Bari, Liverpool, Pusan, Strasbourg, Wuhan (tbc)): Jan–Jun '16

- Qualification of MAM and assembly procedure at CERN (participation of all teams involved in Module construction): Jul–Sep '15

- Qualification (acceptance test) of MAM

- Verification and optimization of assembly procedure

- Verification and optimization of test procedure

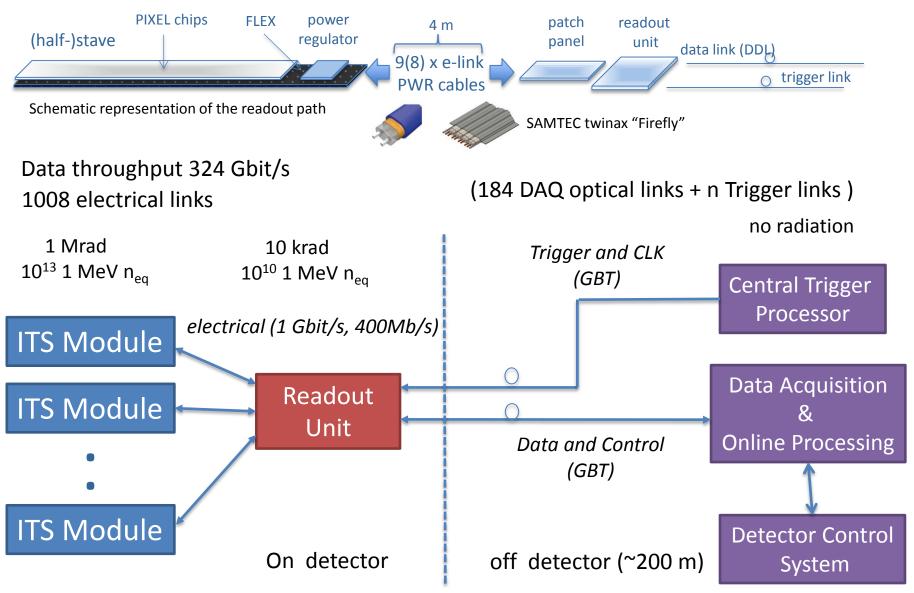

## Plans for 2015 – Readout electronics

#### Readout Electronics: plans for 2015

- Electrical signaling and communication protocol between RU and detector module defined

- Test of data transmission and bit error rate: done in 2014

- Commercial LVDS transceivers (Nikhef, Prague, Kosice)

- To be done

- Test communication via high-speed link (400 Mbit/s, 1.2 Gbit/s)

- Test communication using parallel bus and control lines

- pALPIDE-3

- Test system developed by Bari => see Vito

- Develop an FPGA-based system emulator COMSATS

- Readout Unit prototype integrating link to CRU and Trigger

# **Conclusive Remarks**

Important contribution of Asia to many critical aspects of R&D and construction. Some of the activities are well advanced (

), some are ramping-up (), other have not yet started and need to be confirmed/consolidated ()

- China:

- Pixel chip design, detector and physics simulations

- OB module construction, readout electronics

- Korea:

- Pixel chip design, pixel chip characterization, physics simulations

- Pixel chip mass test, module construction, module construction QA

- Indonesia: Pixel chip mass test QA

- Pakistan: Pixel Chip TCAD simulations, FPGA-based system level simulation of stave readout

- Thailand:

- Detector simulation, pixel chip characterization, silicon µ-channels

- QA for CMOS raw wafers, CMOS wafers (laser) dicing

SPARES

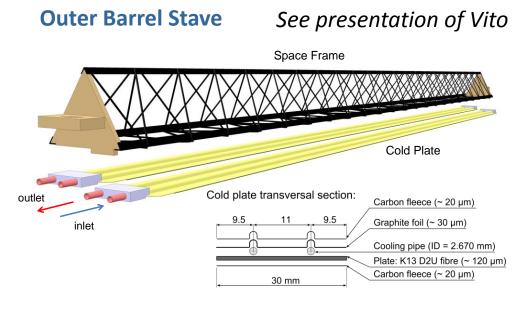

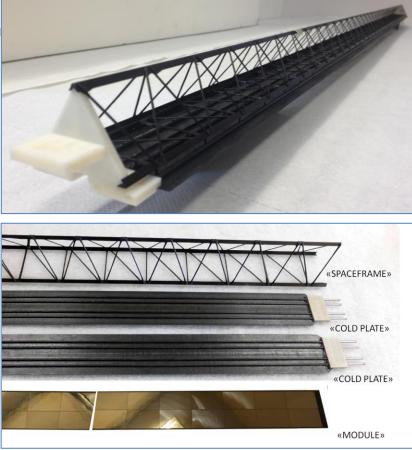

### **Outer Barrel Support Structure and Assembly**

Main structural elements have been prototyped in 2014

# **Outer Barrel**

#### Outer Barrel (OB)

- <radius> (mm): 194, 247, 353, 405

- Nr. staves: 22, 28, 40, 46

- Nr. Chips/layer: (ML), (OL)

- Power density < 100 mW / cm<sup>2</sup>

Length (mm): 843 (ML), 1475 (OL) Nr. modules/stave: 4 (ML), 7 (OL) Material thickness:  $\sim 0.8\% X_0$ Throughput (@100kHz): < 3Mb/s × cm<sup>-2</sup>

# Readout – general scheme and data throughput