### ACTIVITY II: ALICE ITS READOUT ELECTRONICS SERIAL LINK CHARACTERIZATION

Hira Ilyas Madiha Tajwar Jibran Ahmed Raise Ikram (carrier board) Dr. Attiq Ur Rehman

# TASKS

# • Firmware development for serial link characterization

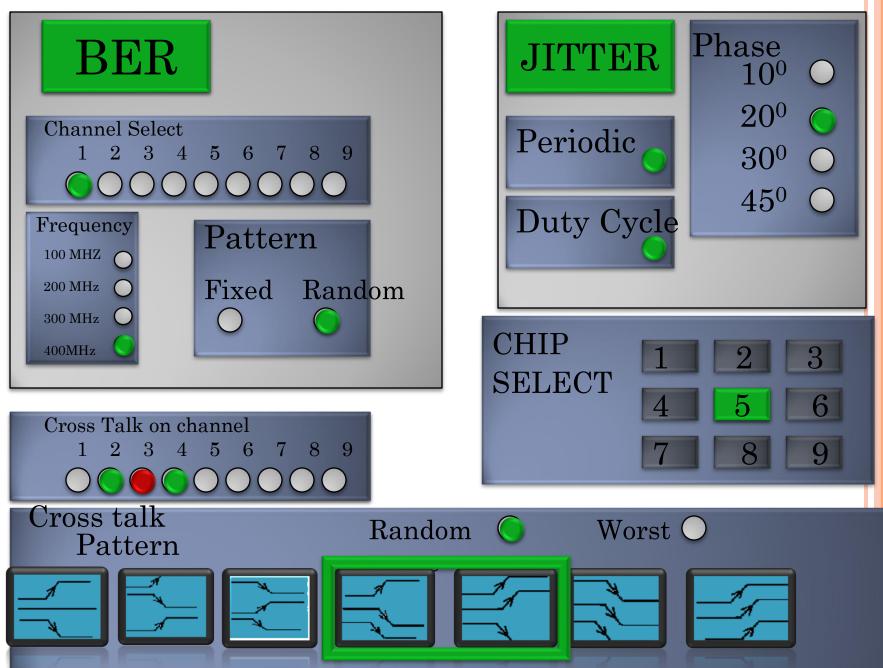

GUI BET Crosstalk analysis Jitter analysis

• Carrier board schematic and layout (possibly)

• Hardware testing

# GUI LAYOUT

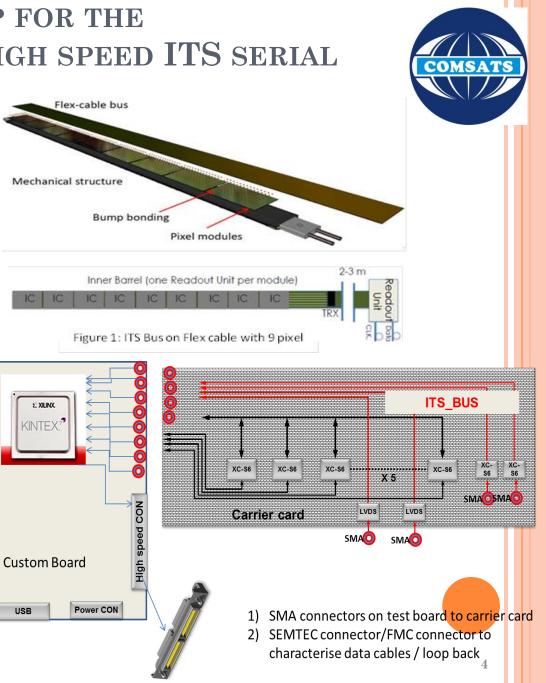

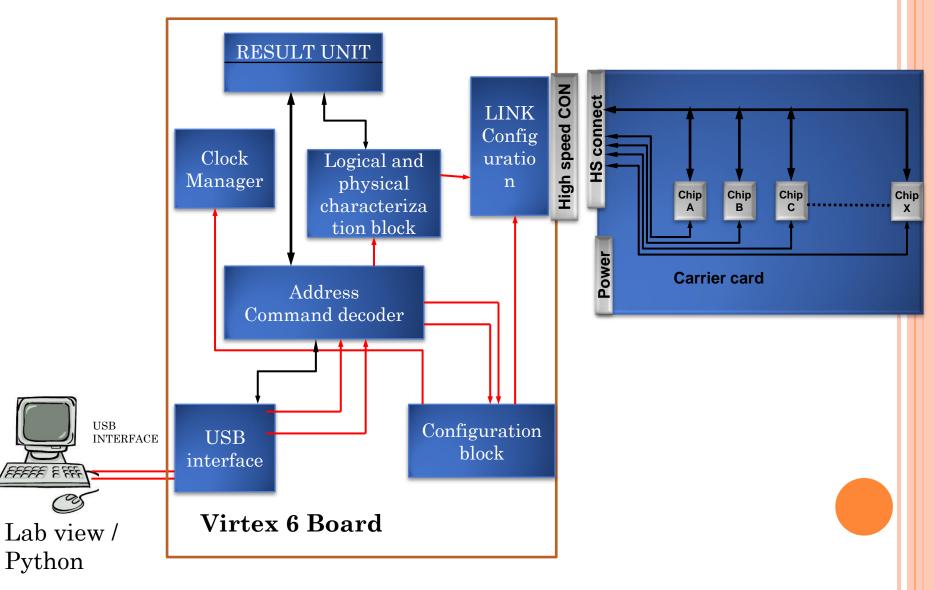

### DESIGN OF A TEST SET-UP FOR THE CHARACTERIZATION OF HIGH SPEED ITS SERIAL DATA LINKS

#### Objectives

- Bit error rate evaluation at various data rates

- Cross talk analysis between data links

- Power analysis

#### Key Tasks

- Specification design of the test plan (can be seen in GUI)

- Schematic design of test board

- Firmware development

# TEST SETUP

### BIT ERROR RATE TESTING

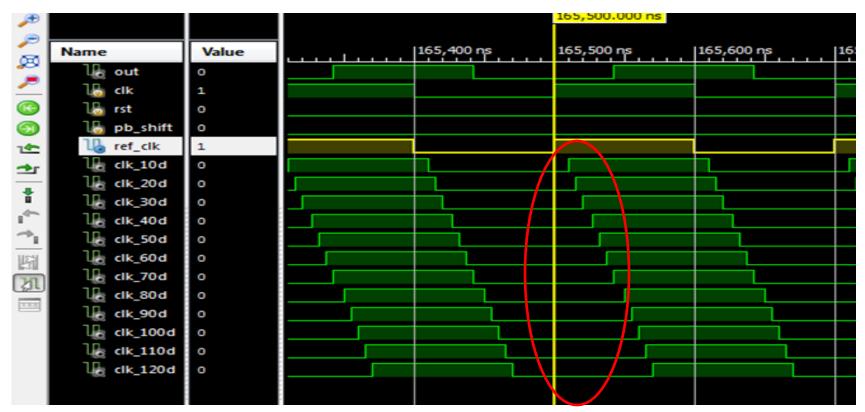

# • Generating clocks with different phases and frequencies to characterize BER.

Using system clock as input, generating different shifts with as minimum resolution as possible.

Integrating shifted clocks to check BER

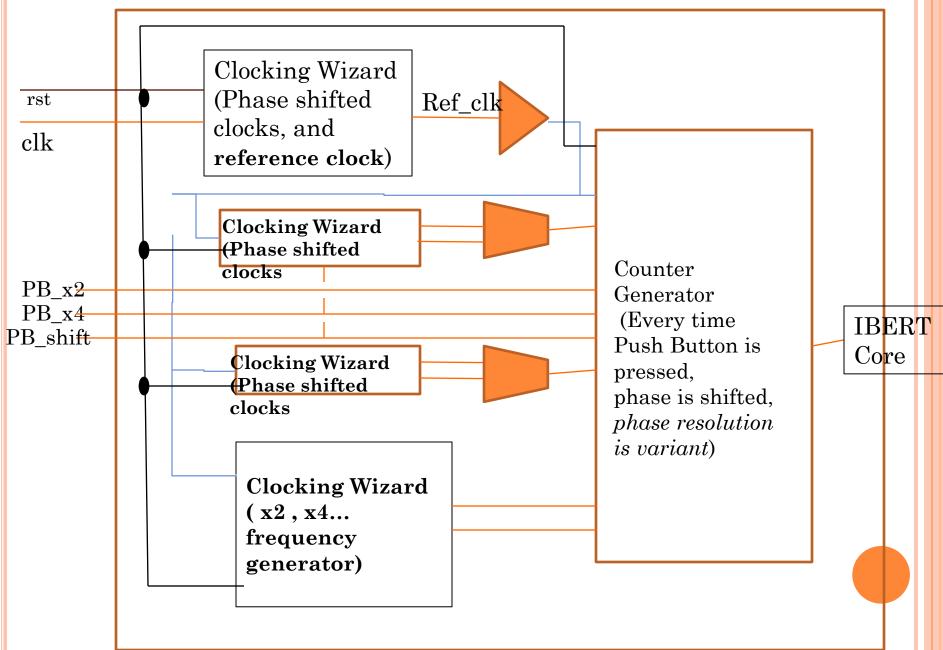

### DATA FLOW DIAGRAM of Clock generation

• ref\_clk is taken as input clk 50MHz upto 1GHz, rest are shifted clocks with different phase and frequency compared to ref\_clk.

• shifted clocks with 50 MHz, have been generated. Each being shifted to  $10^{\circ}$  (simulation,  $9^{\circ}$  to  $11^{\circ}$ actual) as compared to last shift.

• These clocks will now taken as input to check BER, at different phases and frequencies

# **FUTURE WORK**

- Different data patterns are sent at different phases and frequencies.

- Jitter Analysis to be done on different clocks.

- To figure out at what phase and frequency, optimum results are achieved.

# IBERT

- The ChipScope<sup>™</sup> Pro Integrated Bit Error Ratio Tester (IBERT) core for Virtex-6 GTX transceivers is a customizable core that can be used to evaluate and monitor the health of Virtex-6 GTX Transceivers.

- The design includes pattern generators and checkers implemented in FPGA logic, as well as access to the ports and dynamic reconfiguration port (DRP) attributes of the GTX transceivers.

- Software Requirements Core Generator

Chip-scope Pro Analyzer

0

**Hardware Requirements** Virtex-6, ML605 SMA Cables

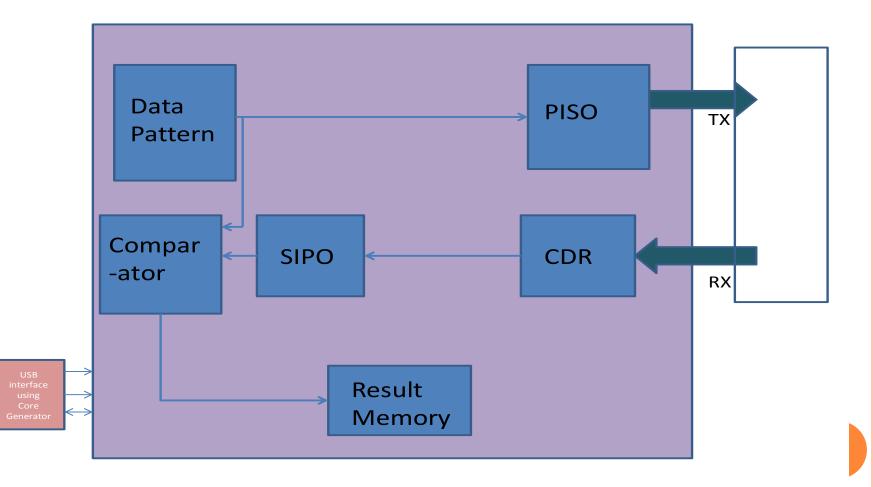

## DESIGN OF BIT ERROR RATE TESTER

# HARDWARE SETUP AND INITIAL SETTINGS & RESULTS

| BERT Console - DEV:1 MyDev | ice1 (XC6VLX240T) UNIT:1_0 Myle | BERT V6 GTX1_0 (IBERT V6 GTX) |                  |                  |

|----------------------------|---------------------------------|-------------------------------|------------------|------------------|

| MGT/BERT Settings DRP S    | ettings Port Settings Swe       | ep Test Settings              |                  |                  |

|                            | GTX_X0Y16                       | GTX_X0Y17                     | GTX_X0Y18        | GTX_X0Y19        |

| - MGT Alias                | GTX0_116                        | GTX1_116                      | GTX2_116         | GTX3_116         |

| - Tile Location            | GTX_X0Y16                       | GTX_X0Y17                     | GTX_X0Y18        | GTX_X0Y19        |

| - MGT Link Status          | No Link                         | No Link                       | 5.004 Gbps       | No Link          |

| - MGT Edit Line Rate       | 5.0 Gbps                        | 5.0 Gbps                      | 5.0 Gbps         | 1.25 Gbps        |

| - TX PLL Status            | LOCKED                          | LOCKED                        | LOCKED           | LOCKED           |

| - RX PLL Status            | LOCKED                          | LOCKED                        | LOCKED           | LOCKED           |

| - Loopback Mode            | None                            | None                          | None             | None             |

| - Channel Reset            | Reset                           | Reset                         | Reset            | Reset            |

| - TX Polarity Invert       |                                 |                               |                  |                  |

| - TX Error Inject          | Inject                          | Inject                        | Inject           | Inject           |

| - TX Diff Output Swing     | 590 mV (0110) 💌                 | 590 mV (0110) 💌               | 590 mV (0110) 💌  | 590 mV (0110)    |

| - TX Pre-Emphasis          | 0.000 dB (0000)                 | 0.000 dB (0000)               | 0.250 dB (0010)  | 0.000 dB (0000)  |

| - TX Post-Emphasis         | 0.000 dB (00000)                | 0.000 dB (00000)              | 0.000 dB (00000) | 0.000 dB (00000) |

| - RX Polarity Invert       |                                 |                               |                  |                  |

| - RX AC Coupling Enable    | V                               | V                             | V                | <b>V</b>         |

| - RX Termination Voltage   | MGTAVTT *                       | MGTAVTT *                     | MGTAVTT *        | MGTAVTT *        |

| - RX Equalization          | 0                               | 0                             | 0                | 0                |

| - DFEEYEDACMON             | 19.3 mV                         | 6.4 mV                        | 51.6 mV          | 58.1 mV          |

| - DFETAPOVRD               | V                               | <b>V</b>                      | <b>v</b>         | V                |

| - DFETAP1                  | 0                               | 0                             | 0                | 0                |

| - DFETAP2                  | 0 💌                             | 0                             | 0                | 0                |

| - DFETAP3                  | 0 💌                             | 0                             | 0                | 0                |

| - DFETAP4                  | 0                               | 0                             | 0                | 0                |

| - RX Sampling Point        |                                 |                               | 5 0.039 UI       |                  |

<u>Hardware</u> <u>setup</u>

#### <u>IBERT Initial</u> <u>Settings</u>

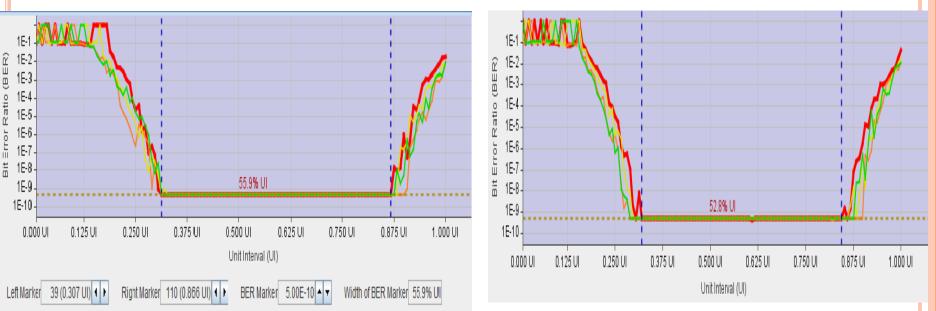

### Bathtub Curve to Calculate Bit Error Rate (SMA)

#### • <u>Line rate: 2.5 Gbps. Frequency 200Mhz</u>

Length 1foot

Length 2feet

### UI of bathtub curve @ System Freq 200Mhz

| Line rate  | 1 Foot  | 2 Feet |

|------------|---------|--------|

| 2.5 Gbps   | 55.9%   | 52.8%  |

| 3.125 Gbps | 44.5%   | 38.6%  |

| 5 Gbps     | 36.2.3% | 32.3%  |

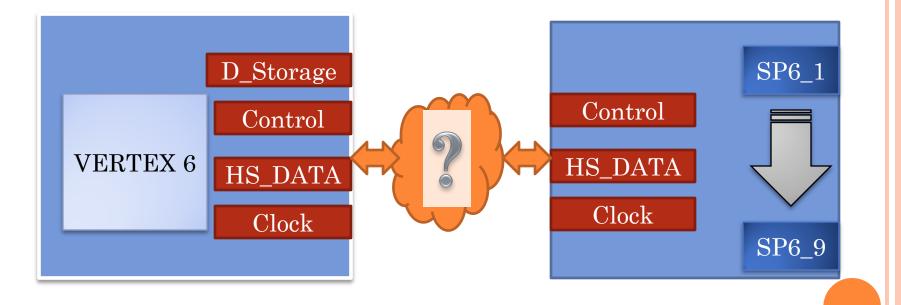

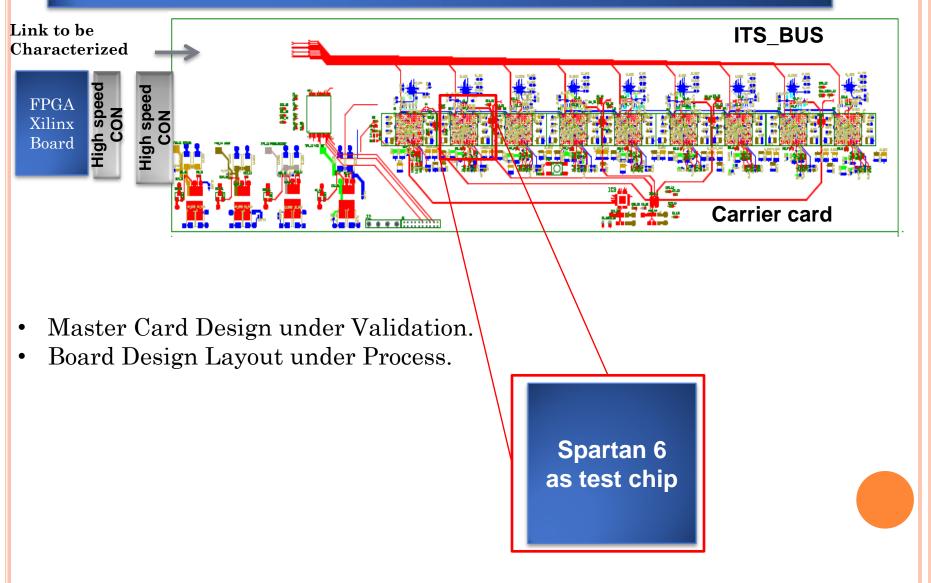

# BOARD LEVEL COMPATIBILITY BETWEEN MASTER CARD & CARRIER CARD

### CARRIER BOARD SCHEMATIC AND LAYOUT

### CONTROL

# Master Card

- Master Clock 40 MHz

- Chip Select IC

- Controlling Carrier Card

- JTAG Header

- External Programming

# Carrier Card

- Chip Select IC

- Enabling Spartan-6 on Carrier Card

- JTAG Header

- Programming Through Master Card

### HIGH SPEED DATA

- Connector Configuration

- Routing Technique

- Differential Pair

- Length Tuning

- Signal Integrity Analysis

- Connector Configuration

- Routing Technique

- Differential Pair

- Length Tuning

- Signal Integrity Analysis

#### PURPOSED DESIGN TO TEST SERIAL LINK CHRACTERIZATION

# HARDWARE SETUP

#### Agilent Infiniium 9000 Series Oscilloscopes

Keysight 81150A Pulse Function Arbitrary Noise Generators

ML605-Vitex 6