# **SRS+Timepix readout**

#### Michael Lupberger

University of Bonn

RD51 Miniweek 10.12.2014, CERN

#### **Outline**

- Timepix Chip

- Small system

- Medium system

- What to do with it

- FEC6 experience

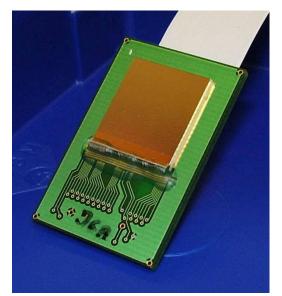

## Timepix chip

#### Properties:

- active surface: 1.4 x 1.4 cm<sup>2</sup>

- pixel size 55 x 55 µm²

- 256 x 256 pixel array

- 14 bit counter in each pixel (ToA or ToT)

- Noise threshold ~500e⁻ (ENC ≈ 90e⁻)

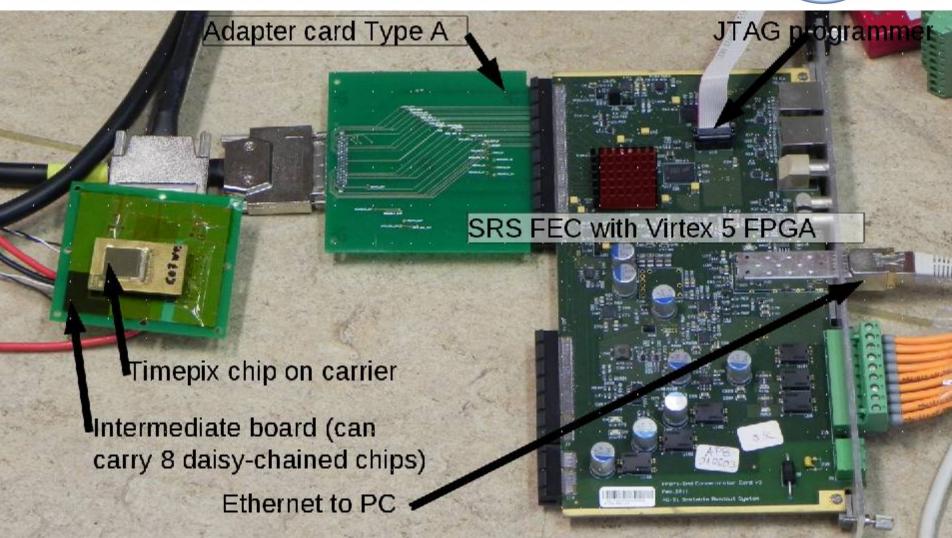

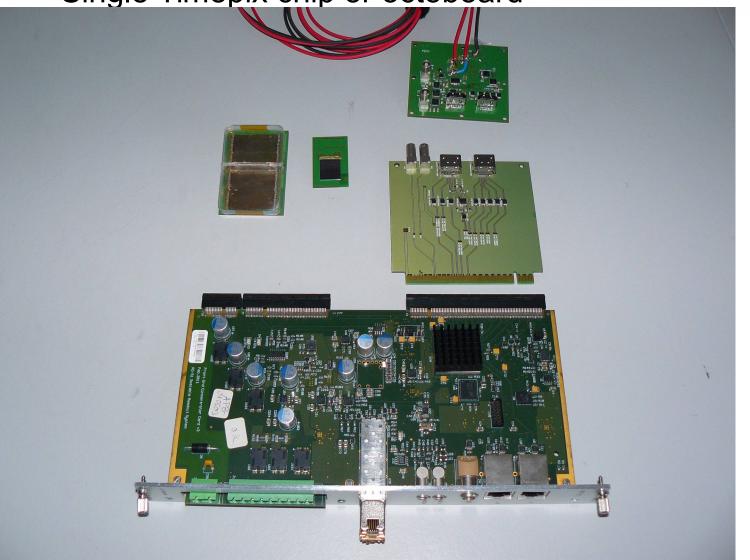

## **SRS+Timepix: chain**

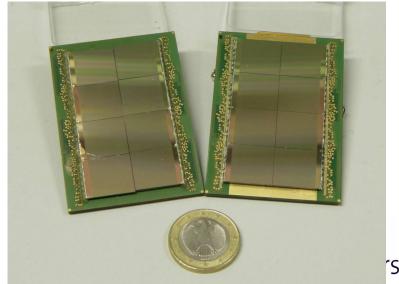

Single Timepix chip or octoboard

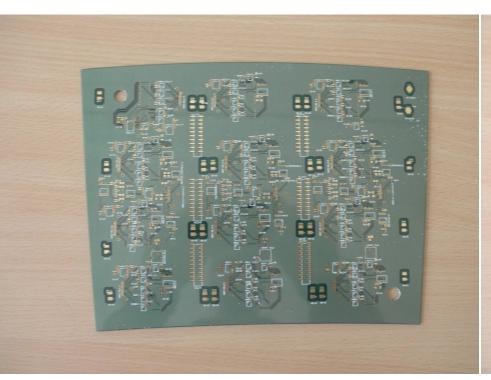

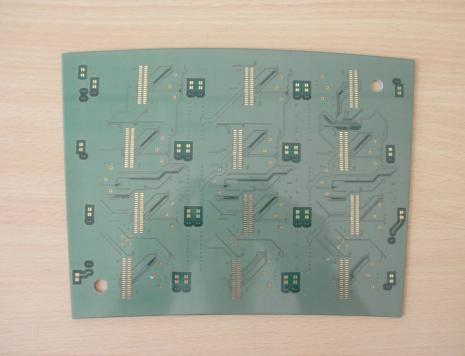

Intermediate board with HDMI connectors

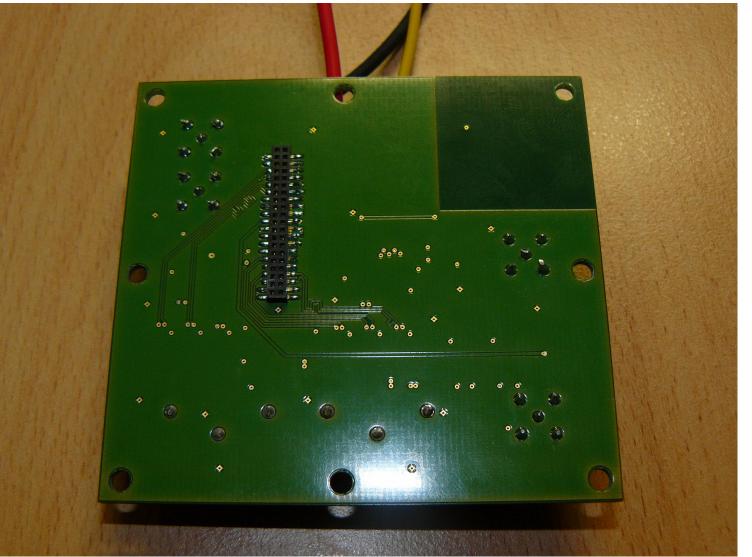

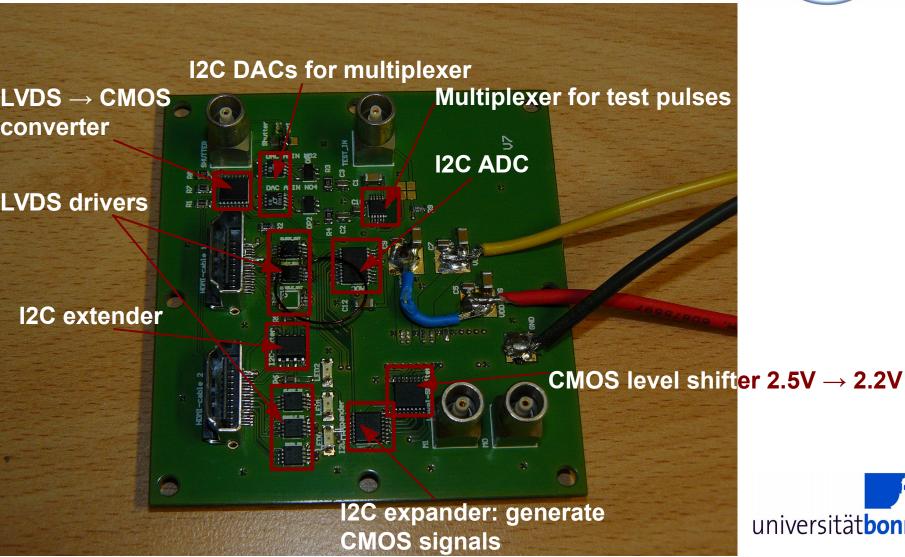

#### Intermediate board with HDMI connectors

A card

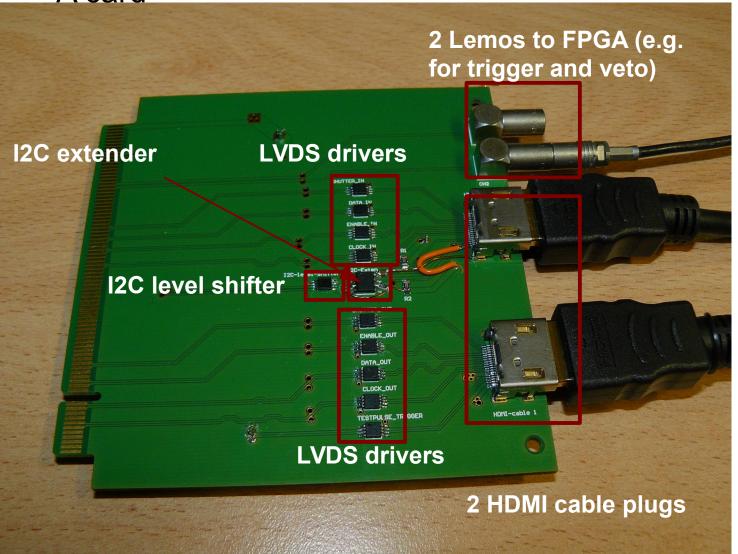

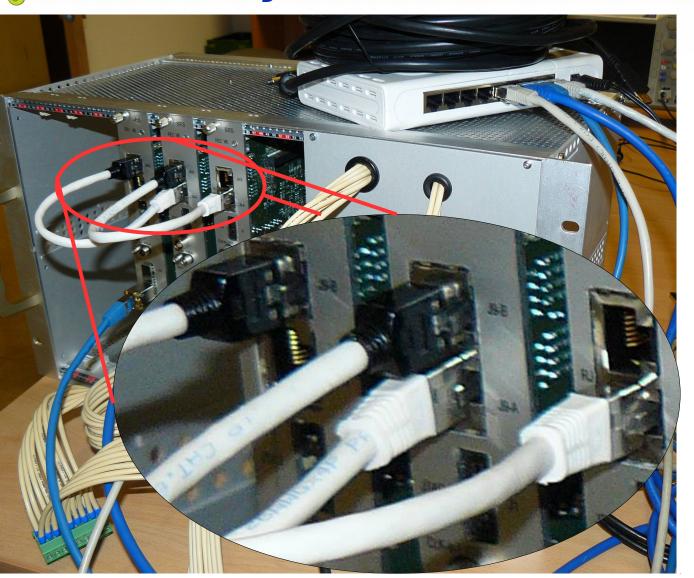

#### C Card on FEC6

3 FEC6 with C-Cards

Each FEC/C-Card: 5 HDMI plugs: 1 for slow control 1 per octoboard

=> 4 octoboards/ FEC

Up to 15m HDMI

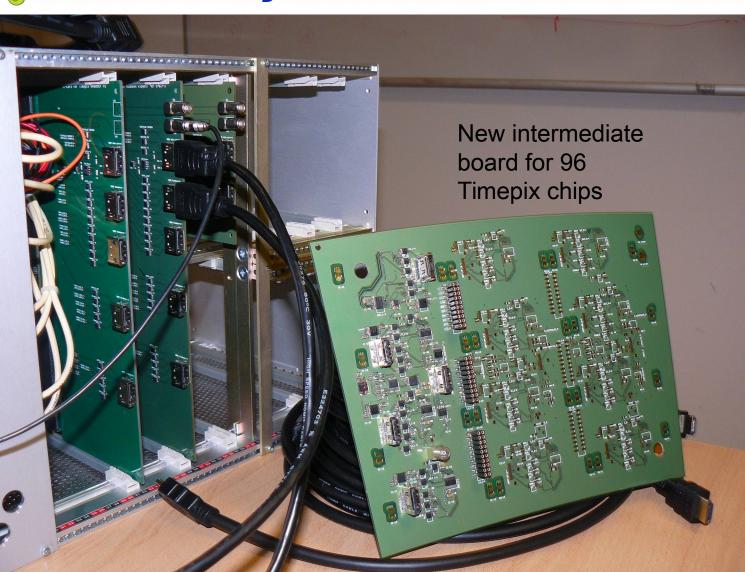

3 FEC6 with C-Cards

Each FEC/C-Card: 5 HDMI plugs: 1 for slow control 1 per octoboard

=> 4 octoboards/ FEC

New intermediate board for 96 Timepix chips

Clock synchronisation using DTC link

Master FEC: clk200 from oscillator Clk40 and clk 200 out

Slave FECs:

Clk200 from Master

Clk40 from clk200

Synchronise clk40

With clk40 from master

Trigger:

From NIM\_in or DTC

Slave → Master

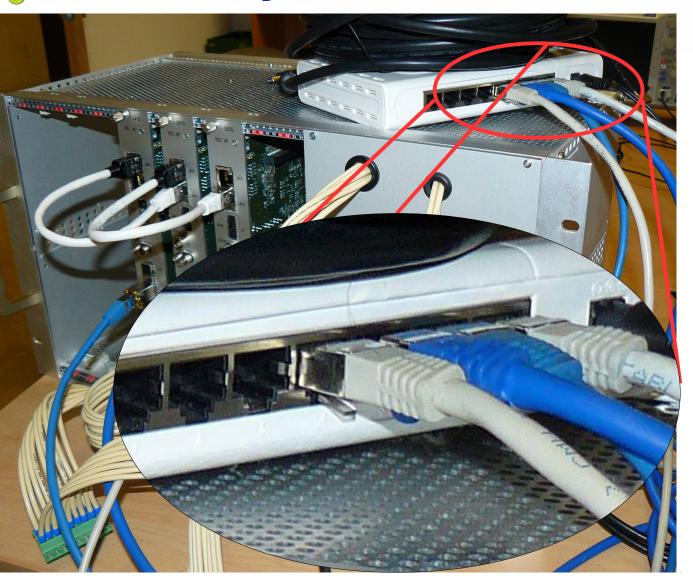

Gigabit Ethernet switch

Software communicates with FECs by IP/MAC address

SFP used at each FEC

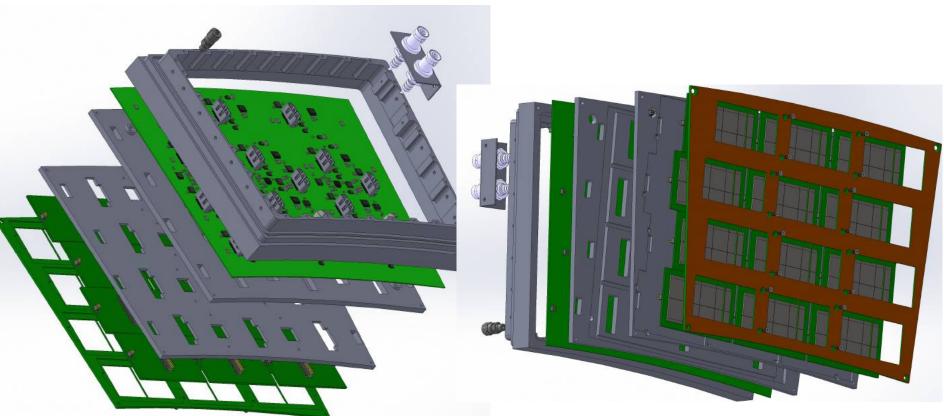

Intermediate board for LCTPC module (96 chips on 12 octoboards) read out by 3 FECs

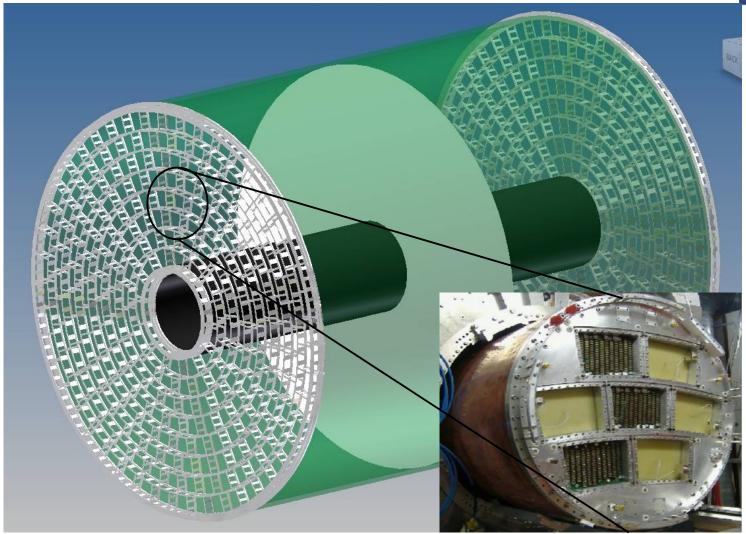

# **LCTPC Module**

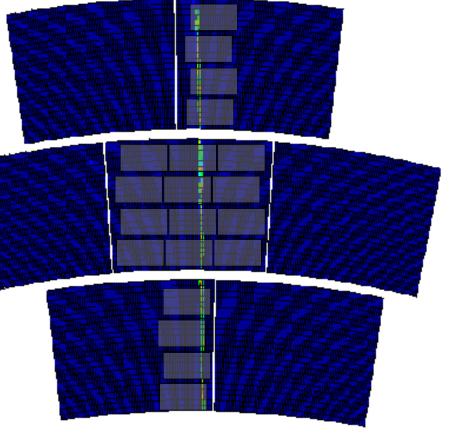

#### Testbeam 2015

- DESY: LCTPC Prototype: TPC for up to seven modules

- 1 fully and two partly equipped with Timepix chips

- 160 chips

- 5 FECs

- Need to borrow

2 FEC6

#### Readout system

#### SRS C-Card + FEC6 in operation

- 1 design error found (powering of LVDS drivers) due to difference between FEC5 and FEC6

- 1 LVDS driver defect

- Development of firmware almost finished

- Test with one octoboard of naked Timepix chips connected to any one of the four slots

- Set DACs (FSR) in chip and read back chip ID  $\sqrt{\phantom{a}}$

- Set matrix and read it back  $\sqrt{\phantom{a}}$

- Zero suppressed readout √

- Zero suppressed readout while sending data of last frame  $\sqrt{\phantom{a}}$

- Software: needs extension for several FECs multithreaded

- Several FECs serail

## **Large system**

#### FEC 6 experiences

- Problems with powering at beginning

- $\rightarrow$  Confusion with production and 0  $\Omega$  resistors

- Problems with Spansion memory

- → Confusion with memory size

- Problems with Jitter cleaner

- → not used after discussion with Raul

- NIM\_out signal looks strange?

- → maybe change resistor in NIM\_out network?

- Cooling seems to be sufficient

- FEC5/FEC6 compatibility: difficult for clock\_in signals at PCI plug, VPIO3\_3 not available any more

FEC6 works excellent!

## Summary

#### Implementation of Timepix in SRS almost finished

- Small system verified at Testbeam 2013

- Medium size system

- Firmware almost finished

- Hardware ready

- Detector in preparation

- Testbeam in spring 2015