A. Annovi M. Beretta R. Beccherle N. Biezus S.Citraro **F. Crescioli**<sup>1</sup> P. Giannetti M. A. Mirzaei V. Liberali Y. Piadyk E. Rossi A. Stabile

> <sup>1</sup>(LPNHE - IN2P3 - CNRS) seconded to CAEN SpA

EPS-HEP 2015 - 22-29/07/2015 - Vienna

▲□▶ ▲□▶ ▲目▶ ▲目▶ 目 のへで

## Outline

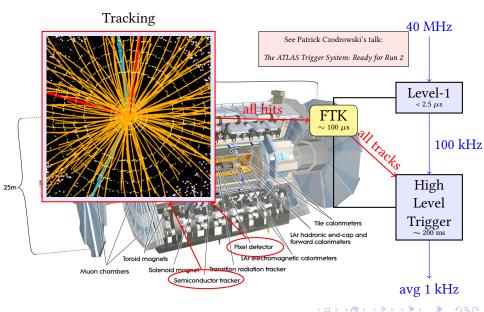

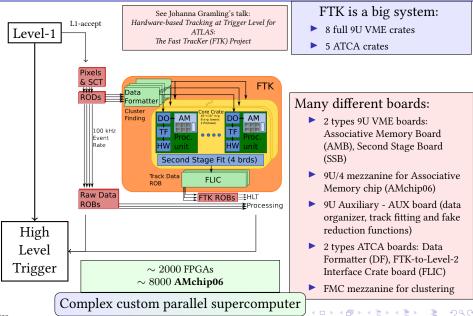

- Introduction to the FTK tracking algorithm

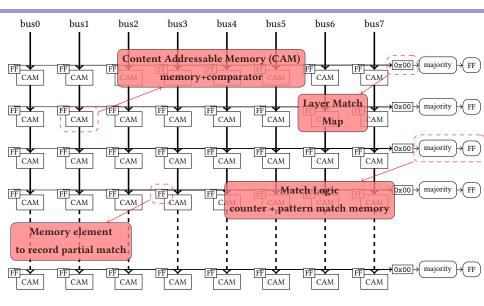

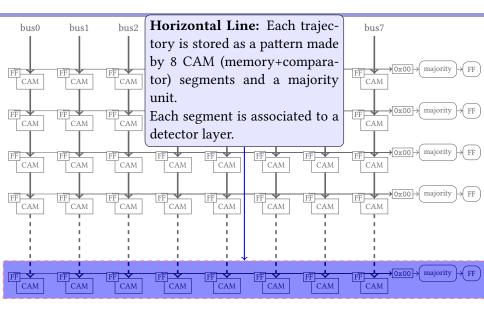

- Associative Memory function and architecture

- AMchip05

- Features

- Performances

- Role in FTK

- Pattern bank optimization and variable resolution

▲ロト ▲ □ ト ▲ □ ト ▲ □ ト ● ● の Q ()

- Toward HL-LHC

- Conclusions

FTK AMchip05: an Associative Memory Chip Prototype for Track Reconstruction at Hadron Collider Experiments — The ATLAS experiment and its TDAQ

FTK AMchip05: an Associative Memory Chip Prototype for Track Reconstruction at Hadron Collider Experiments The ATLAS experiment and its TDAQ

#### $\chi^2 = \sum_{ij} f_i \cdot F_{ij}^{-1} \cdot f_j = \sum_i \tilde{f}_i^2$ FTK is based on a two step algorithm $F_{ii} \simeq \sum_{kl} \frac{\partial f_i}{\partial r_l}$ Associative memory Constraint Tangent Plane Preloaded with the pattern bank Find patterns in a complex event in real time Act as a filter to reduce the complexity of fitting stage Modular algorithm: scalable and parallelizzable. Extremely fast associative memory hardware. $\tilde{f}_i(\vec{x}) \simeq \vec{v}_i \cdot \vec{x} + c_i$ $p_j(\vec{x}) \simeq \vec{w}_j \cdot \vec{x} + q_j$ PATTERN 5 PATTERN 4 Linearized track fit PATTERN PATTERN 3 PATTERN N . HIT # 144 Performed only on patterns found by the AM Combinatorial problem reduced: essential in crowded events with high pile-up Fast in FPGA

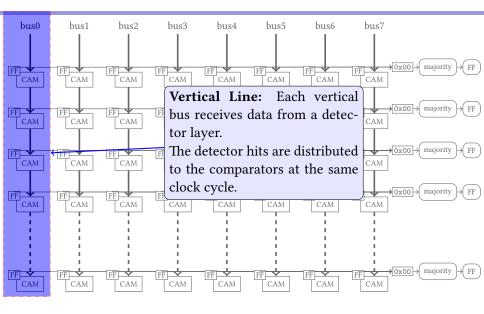

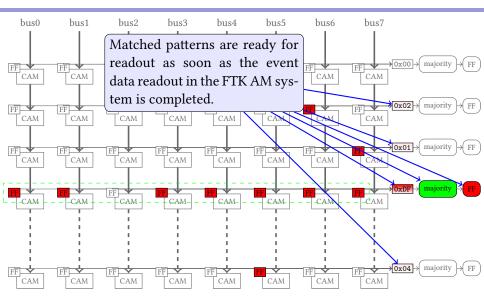

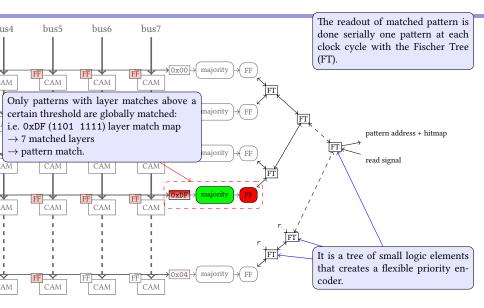

#### Associative Memory internal structure

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ のへぐ

FTK AMchip<br/>05: an Associative Memory Chip Prototype for Track Reconstruction at Hadron Collider Experiments<br/>  $\hfill AMchip05$

## AMchip05

### Main features:

- ► Two Associative Memory architecture designs:

- 2k patterns XORAM arch

- 1k patterns TOP2\_LV arch

- 65 nm TSMC technology

- Full custom CAM-cell

- Standard Cells control logic

- ► 100 MHz target operating frequency

- 2 Gbps inputs for hits (x8 bus)

- ► 2.4 Gbps inputs/output for patterns

- Variable resolution

- 2 to 9 bits configurable as ternary

AMchip05 is the last prototype. **AMchip06** - the chip that will be installed in FTK - is functionally identical, but with **128k patterns**.

3

イロト 不得 とうほう イヨン

FTK AMchip<br/>05: an Associative Memory Chip Prototype for Track Reconstruction at Hadron Collider Experiments<br/>  $\hfill AMchip05$

## AMchip05 Tests

- High-speed serial data transfer verified on testbench

- Direct testing: BER < 10<sup>-12</sup> errors/s @ 2 Gbps

- Stable link up to 3.2 Gbps

- XORAM Pattern bank tested

- O(10<sup>10</sup>) randomized pattern bank data/hits tests

- ► ~98% of chips with zero errors out of ~180 tested

▲□▶▲□▶▲□▶▲□▶ ▲□ ● のへで

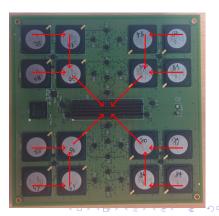

## AMchip05 Integrated on the LAMB

- ▶ 16 AMchip05 per LAMB

- Hit data is distributed in parallel to all chips

- Pattern readout is arranged in 4 trees

- Each AMchip05 can receive patterns from 2 neighbouring chips

- It merges its own internal patterns with the received patterns to the output

- Chips can be arranged in a binary-tree structure to increase pattern size without adding pattern inputs in the FPGA

Each FTK processor unit covering  $\frac{1}{128}$  of the detector has one Associative Memory Board (AMB), each AMB has 4 LAMB mezzanines  $\rightarrow$  8 Mpatt with AM-chip06

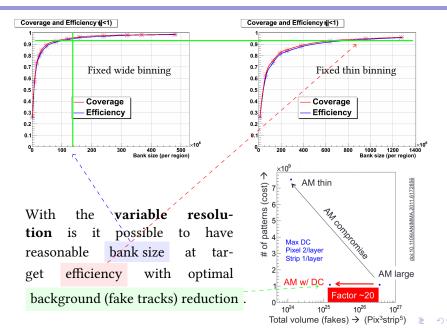

#### Variable Resolution feature

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ のへぐ

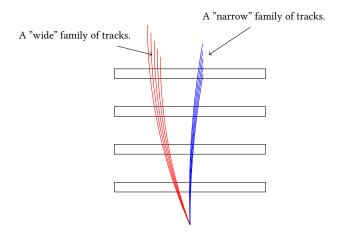

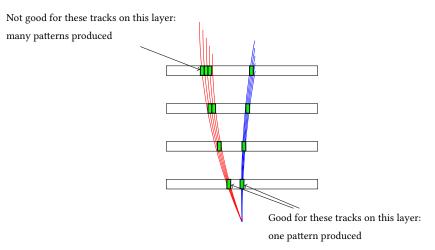

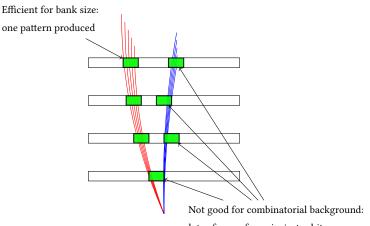

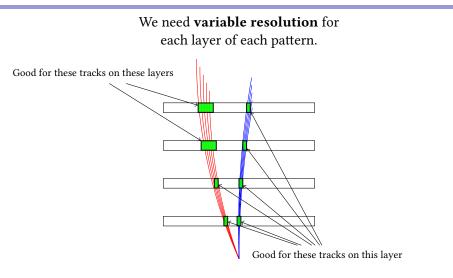

Regions of track parameter space might have different variance on different layers.

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ のへぐ

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ のへぐ

# Variable resolution is possible by encoding *don't care* bits in the pattern.

A simple 2D layer with 32 pixels 4  $\times$  8.

Each pixel is identified by a number.

| 00000 | 00001 | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 |

| 10000 | 10001 | 10010 | 10011 | 10100 | 10101 | 10110 | 10111 |

| 11000 | 11001 | 11010 | 11011 | 11100 | 11101 | 11110 | 11111 |

A 5-bit encoded value will match a certain pixel. 00101

| 00000 | 00001 | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 |

| 10000 | 10001 | 10010 | 10011 | 10100 | 10101 | 10110 | 10111 |

| 11000 | 11001 | 11010 | 11011 | 11100 | 11101 | 11110 | 11111 |

> Using *don't care* on a bit will match two pixels  $\rightarrow$  a **lower resolution pixel** 0110X

| 00000 | 00001 | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 |

| 10000 | 10001 | 10010 | 10011 | 10100 | 10101 | 10110 | 10111 |

| 11000 | 11001 | 11010 | 11011 | 11100 | 11101 | 11110 | 11111 |

*don't care* can be placed to select

different shapes.

| 00000 | 00001 | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 |

| 10000 | 10001 | 10010 | 10011 | 10100 | 10101 | 10110 | 10111 |

| 11000 | 11001 | 11010 | 11011 | 11100 | 11101 | 11110 | 11111 |

More than one *don't care bit*

can be used.

XX110

| 00000 | 00001 | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 |

| 10000 | 10001 | 10010 | 10011 | 10100 | 10101 | 10110 | 10111 |

| 11000 | 11001 | 11010 | 11011 | 11100 | 11101 | 11110 | 11111 |

Various shapes and resolutions

are possible.

| 00000 | 00001 | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 |

| 10000 | 10001 | 10010 | 10011 | 10100 | 10101 | 10110 | 10111 |

| 11000 | 11001 | 11010 | 11011 | 11100 | 11101 | 11110 | 11111 |

FTK AMchip05: an Associative Memory Chip Prototype for Track Reconstruction at Hadron Collider Experiments

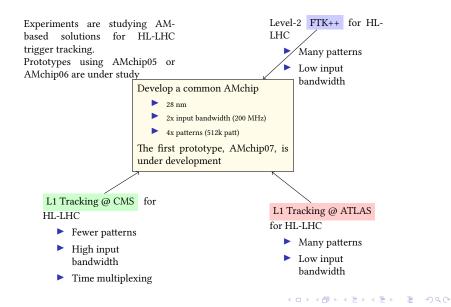

AMchip in future applications

FTK AMchip<br/>05: an Associative Memory Chip Prototype for Track Reconstruction at Hadron Collider Experiments<br/>  $\hfill Conclusions$

- AMchip05 is the latest prototype for FTK before AMchip06 production

- It is identical to the production version except the pattern bank size (3k vs 128k)

- It has been extensively tested in laboratory and on the FTK LAMB prototypes

- The chip works as expected and within specifications

- ► The AMchip05/06 architecture has configurable ternary bits

- It enables the variable resolution of patterns

- It is possible an optimization of the bank size with a significant gain in FTK efficiency

- This gain has a direct impact in FTK trigger application to select physics objects

- AMchip05/06 is the last chip for FTK @ LHC

- The development of the next generation for HL-LHC and other applications has started

- ► It will benefit from the experience of AMchip05

- ▶ We will move to 28 nm technology

FTK AMchip05: an Associative Memory Chip Prototype for Track Reconstruction at Hadron Collider Experiments

AMchip development has been supported by