# Common Readout Unit (CRU)

# A New Readout Architecture for ALICE Experiment

#### **Jubin Mitra**

VECC, Kolkata, India

For the ALICE Collaboration

# **TWEPP 2015**

Topical Workshop on Electronics for Particle Physics

28 September - 02 October 2015 IST - Lisbon - Portugal

#### **Outlook**

- 1) Motivation of building CRU

- 2) Understanding CRU connection and functionality

- 3) How we choose the CRU form factor

- 4) Firmware Development Status

#### Part I:

Motivation of Building CRU

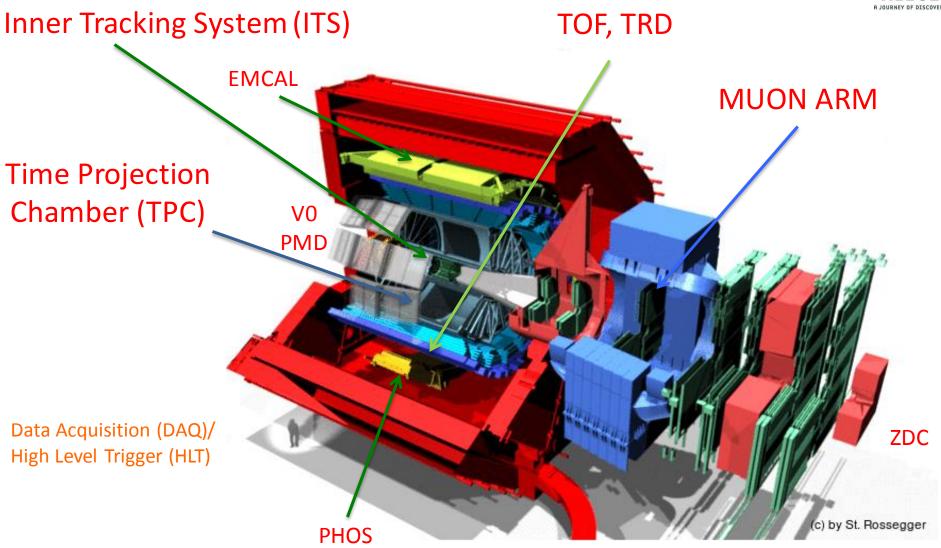

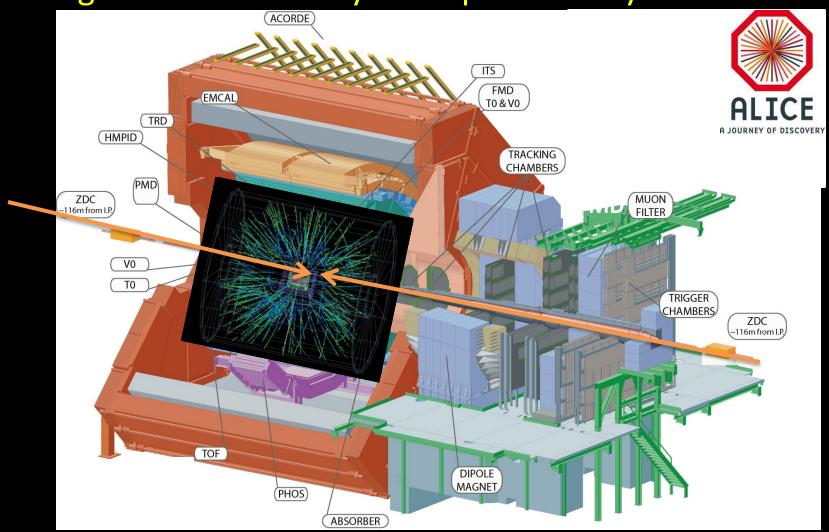

#### **ALICE at CERN-LHC (Now)**

ALICE is a dedicated experiment for study of Quark-Gluon Plasma (QGP)

with pp, p-Pb and Pb-Pb collisions at the LHC

#### **ALICE Upgrade: > 2021**

#### **New Inner Tracking System (ITS)**

Improved pointing precision

Less material -> thinnest tracker at the LHC

25x10<sup>9</sup> channels

#### **Time Projection Chamber (TPC)**

New Micropattern gas detector technology

Continuous readout

New Central Trigger Processor (CTP)

#### Online Offline Systems (O2)

- New architecture

- On line tracking & data compression

- 50kHz PbPb event rate

# New Si tracker Improved MUON pointing precision MUON ARM continuous

continuous readout electronics

#### TOF, TRD

Faster readout

New Trigger Detectors (FIT)

Muon Forward Tracker (MFT)

(c) by St. Rossegger

## Why Do We Need CRU?

| LS1 (2013-14)                                                                      | ALICE                              | After LS2 * (2019 - 20)                                                                                                                        |

|------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Present<br>(RUN2)                                                                  | UPGRADE                            | Future<br>(RUN3/RUN4<br>– YEAR 2021)                                                                                                           |

| 1 nb <sup>-1</sup> (PbPb)                                                          | Collisions and Collection          | >10 nb <sup>-1</sup> (PbPb)<br>6 pb <sup>-1</sup> (pp)<br>50 nb <sup>-1</sup> (pPb)                                                            |

| 10 <sup>27</sup> cm <sup>-2</sup> s <sup>-1</sup>                                  | At Peak Luminosities               | 6 x 10 <sup>27</sup> cm <sup>-2</sup> s <sup>-1</sup>                                                                                          |

| 8 kHz (PbPb)                                                                       | Corresponding to Collision Rate Of | 50 kHz (PbPb)<br>200 kHz (pp and pPb)                                                                                                          |

| 500 Hz (PbPb)                                                                      | Maximum Readout<br>Rate            | >200 kHz (PbPb)<br>1 MHz (pp)                                                                                                                  |

| Hardware triggers • Event multiplicity • Calorimeter energy • Track p <sub>T</sub> | Trigger Mechanism                  | <ul> <li>A minimum bias event<br/>(Non- Upgraded detector)</li> <li>A self-triggered<br/>Continuous fashion<br/>(upgraded detector)</li> </ul> |

| To summarize:                                                                      |                                    | 1                                                                                                                                              |

TO HANDLE THE DATA FLOW TRAFFIC OF ABOUT 1 TB/S

#### Part II:

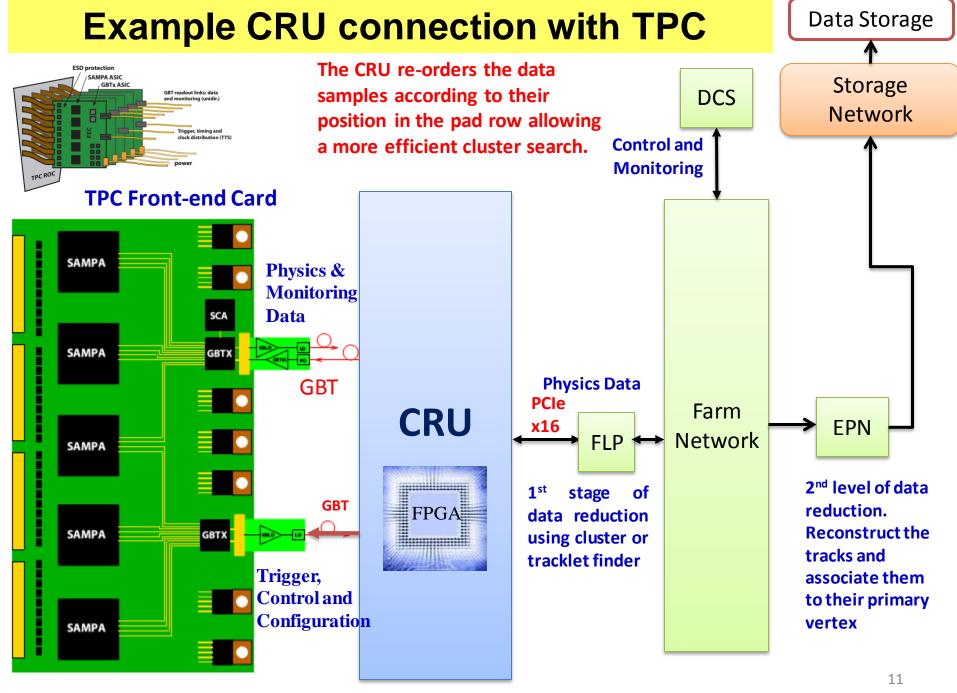

Understanding CRU Connection

And

Functionality

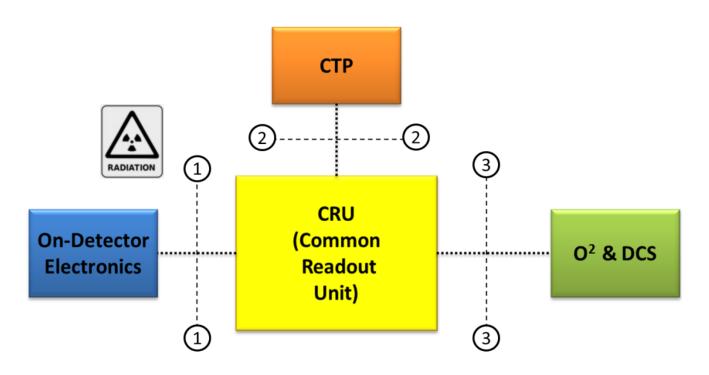

#### **Common Readout Unit (CRU)**

#### CRU has three interfaces:

- 1 GBT Link (Radiation Tolerant High Speed Optical Link)

- 2 To be decided (GBT/10Gigabit PON)

- 3 **DDL3 link ( PCle Gen 3 x16)**

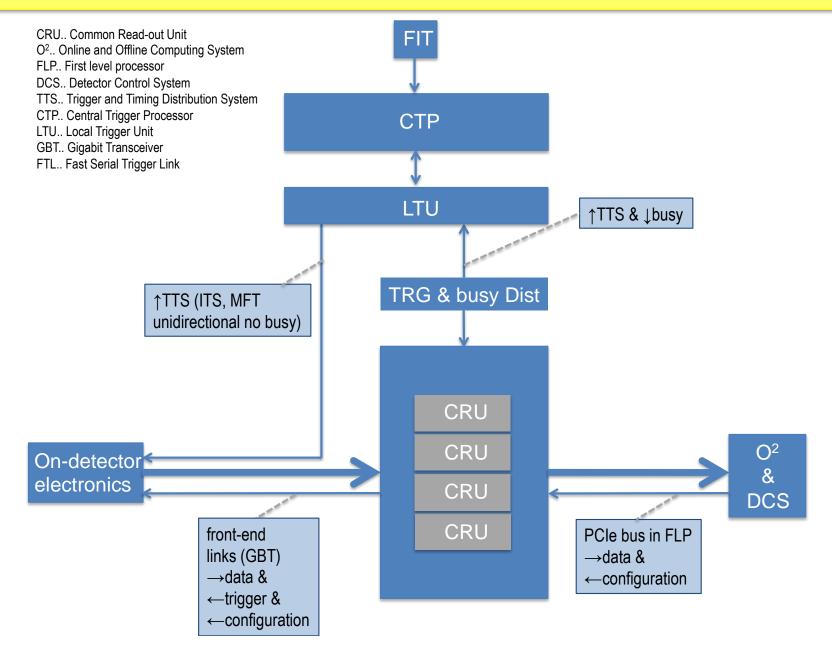

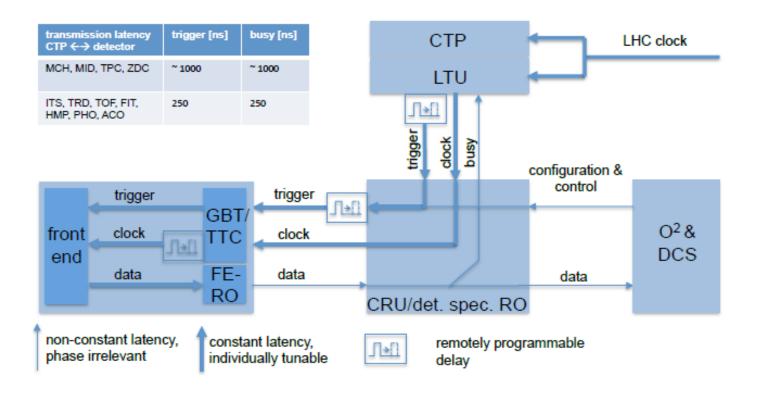

#### Read-out and Trigger Distribution System

## **ALICE** Detector readout board types

| Detector   | Link   | Number of links  |                    | Read-out        | Number of boards |        |     |

|------------|--------|------------------|--------------------|-----------------|------------------|--------|-----|

|            | type   | DDL1<br>(2 Gbps) | DDL2<br>(4-5 Gbps) | GBT<br>(4.8 Gbp | board type       | C-RORC | CRU |

| ACO        | DDL1   | 1                |                    |                 | C-RORC           | 1      |     |

| CPV        | DDL1   | 6                |                    |                 | C-RORC           | 1      |     |

| CTP        | GBT    |                  |                    | 14              | CRU              |        | 1   |

| <b>EMC</b> | DDL2   |                  | 20                 |                 | C-RORC           | 4      |     |

| FIT        | DDL2   |                  | 2                  |                 | C-RORC           | 1      |     |

| HMP        | DDL1   | 14               |                    |                 | C-RORC           | 4      |     |

| ITS        | GBT    |                  |                    | 495             | CRU              |        | 23  |

| MCH        | GBT    |                  |                    | 550             | CRU              |        | 25  |

| MFT        | GBT    |                  |                    | 304             | CRU              |        | 14  |

| MID        | GBT    |                  |                    | 32              | CRU              |        | 2   |

| PHS        | DDL2   |                  | 16                 |                 | C-RORC           | 4      |     |

| TOF        | GBT    |                  |                    | 72              | CRU              |        | 3   |

| TPC        | GBT    |                  |                    | 5832            | CRU              |        | 324 |

| TRD        | Custom |                  |                    | 1044            | CRU              |        | 54  |

| ZDC        | GBT    |                  |                    | 1               | CRU              |        | 1   |

| Total      |        | 21               | 38                 | 8344            |                  | 15     | 447 |

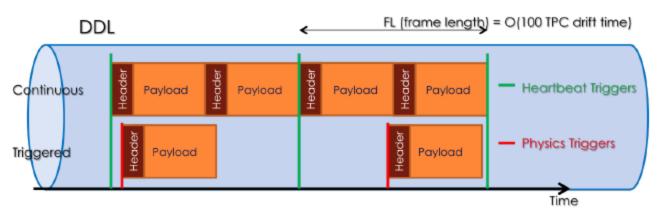

### **Trigger Types**

| Level | Trigger       | Trigger | Trigger       | contributing            |

|-------|---------------|---------|---------------|-------------------------|

|       | ${\bf Input}$ | output  | decision      | detectors               |

|       | to CTP        | at CTP  | at detector * |                         |

|       | [ns]          | [ns]    | [ns]          |                         |

| LM    | 425           | 525     | 775           | FIT                     |

| L0    | 1200          | 1300    | 1500          | ACO, EMC, PHO, TOF, ZDC |

| L1    | #6100         | #6200   | #6400         | EMC, ZDC                |

Usage of **Interaction Trigger**Usage of **Heartbeat Trigger**

- → Triggered Readout

- **→** Continuous Readout

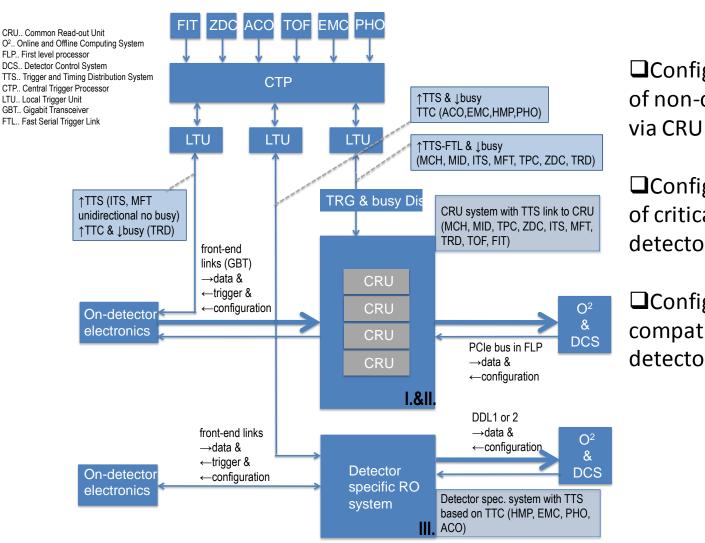

# Trigger, Timing and Clock Distribution System (TTS)

- ☐ Configuration I: Transmission of non-critical trigger and data via CRU

- ☐ Configuration II: Transmission of critical trigger directly to the detector and data via CRU

- ☐ Configuration III: Back-end compatibility for Legacy detectors

#### Part III:

How we choose the CRU form factor?

#### **CRU Form Factor Evaluation**

| Features                           | Prototype version 1 | Prototype version 2 |

|------------------------------------|---------------------|---------------------|

| DDL3                               | 10 Gigabit Ethernet | PCIe Gen 3          |

|                                    |                     |                     |

| Trigger and Busy line Distribution | ATCA                | Processor           |

**Advantage**

Disadvantage

Modularity

Not Enough memory for data clustering not Compatibility of the board depends on possible

Directly connected to the  $O^2$

future PCs PCIe form factor

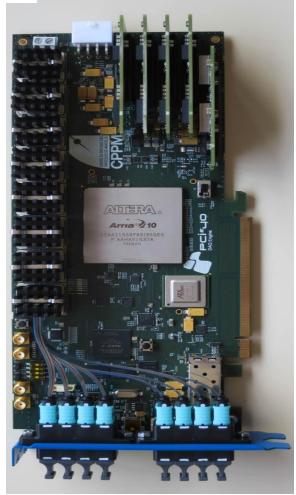

#### CRU CANDIDATE BOARDS EVALUATED

#### **AMC 40**

Developed By: CPPM Marseille

#### Stratix V vs Arria 10 FPGA

|                                        | Stratix V       | Arria 10                 |

|----------------------------------------|-----------------|--------------------------|

|                                        |                 |                          |

|                                        | (High End FPGA) | (Mid End Latest FPGA)    |

|                                        | 5SGXEA7N2F45C3  | 10AX115S4F45I3SGES       |

| Chip Technology                        | 28 nm           | 20 nm                    |

| Core voltage                           | 0.85V           | 0.95V (For ES) else 0.9V |

| ALMs                                   | 234720          | 427200                   |

| Total I/Os                             | 1064            | 960                      |

| GXB Channel PMA and PCS/ HSSI channels | 48              | 72                       |

| PCIe Hard IP Blocks                    | 4               | 4                        |

| Memory Bits                            | 52428800        | 55562240                 |

| DSP Blocks                             | 256             | 1518                     |

| 27 x 27 Multiplier                     | 256             | 1518                     |

| Fractional PLL                         | 28              | 32                       |

| DLLs                                   | 4               | -                        |

| I/O PLLs                               | -               | 16                       |

| <b>Global Clocks</b>                   | 16              | 32                       |

| HPS CPU Core                           | -               | 0                        |

#### Part IV:

Firmware Development Status

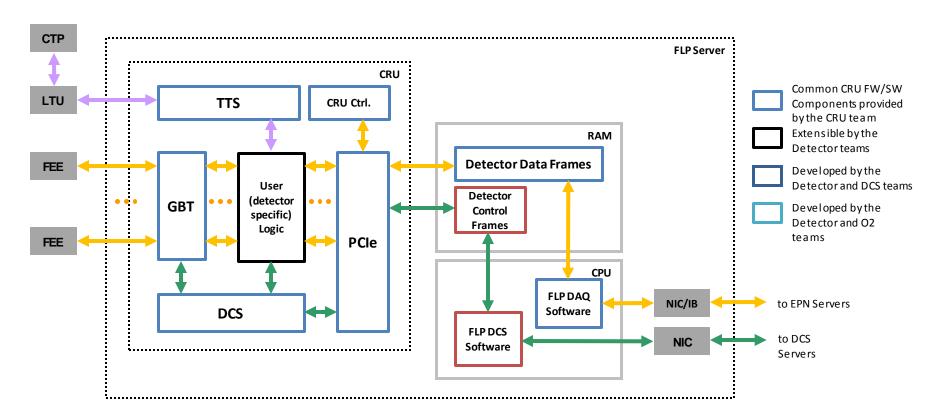

#### **CRU** internal block connections

- CTP Central Trigger Processor

- DCS Detector Control System

- EPN Event Processing Node

- FLP First Level Processor

- GBT Giga-Bit Transceiver

- LTU Local Trigger Unit

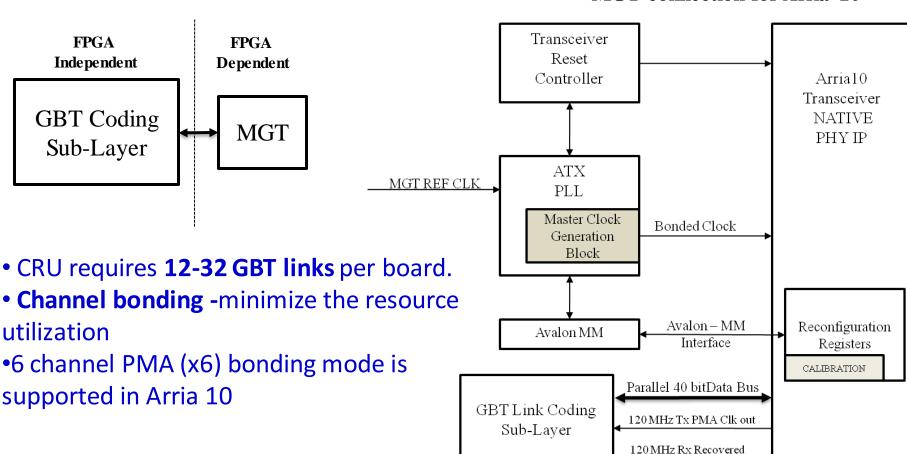

### **GBT**: Design Implementation on Arria 10

GBT Interface links are error resilient data communication protocol developed by CERN for high energy physics experiment.

MGT connection for Arria 10

PMA Clk out

#### **GBT**: Operating at 4.8 Gbps Using 120 MHz External Jitter

Cleaner

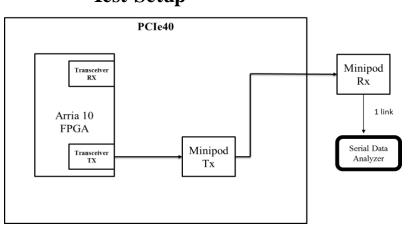

#### **Test Setup**

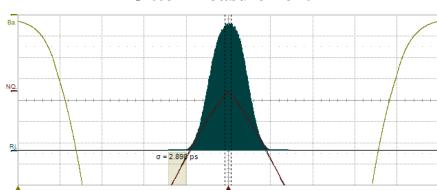

#### **Jitter Measurement**

The random component of the Jitter is specified using statistical terms.

**Standard Deviation** = 2.898 ps

Eye Width = 176.8 psEye Height = 373 mV

**Bit/Rate** = 4.7996

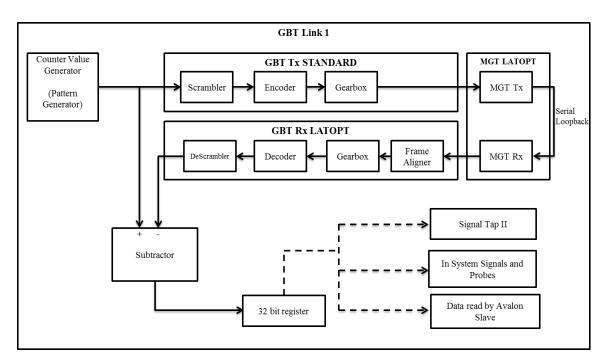

### **GBT**: Latency Measurement

#### Latency measured between

Tx Data Frame – GBT Tx – MGT Tx (Serialization) – Optical Loopback --MGT Rx (De-serialization)

- GBT Rx - Rx Data Frame

| k Data Frame | GBT         |             |             |                   |  |

|--------------|-------------|-------------|-------------|-------------------|--|

|              | Tx Standard | Tx Standard | Tx Latency  | Tx Latency        |  |

|              |             |             | Optimize d  | Optimized         |  |

|              | Rx Standard | Rx Latency  | Rx Standard | Rx Latency        |  |

|              |             | Optimize d  |             | <b>Optimize d</b> |  |

| Latency      | 450 ns      | 350 ns      | 200 ns      | 150 ns            |  |

| Measured     | 430 hs      | 330 hs      | 200 hs      | 130 ns            |  |

# Transmission Side Phase latency is very stringent as it is used for timing information transmission

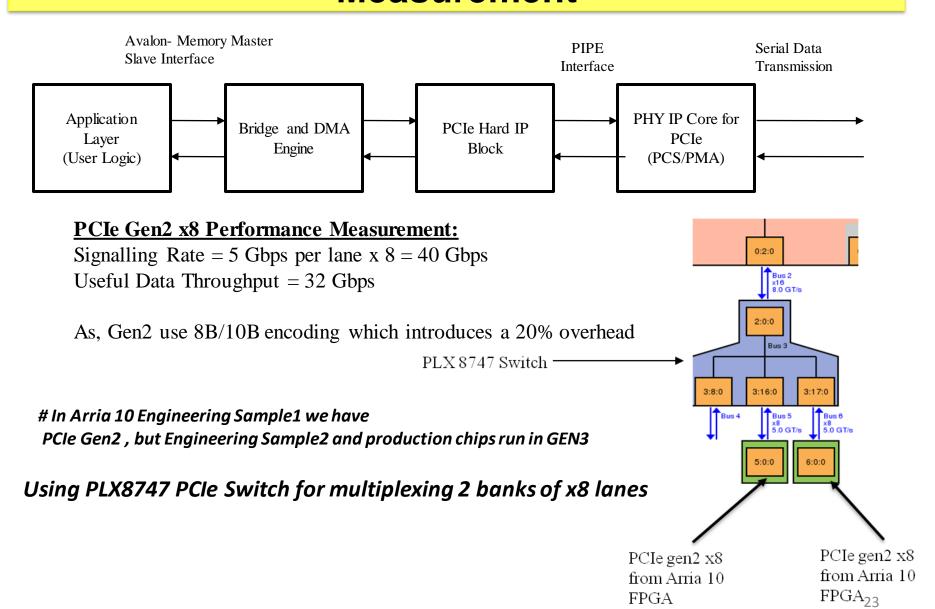

# DDL3: PCIe Link Testing and DMA Performance Measurement

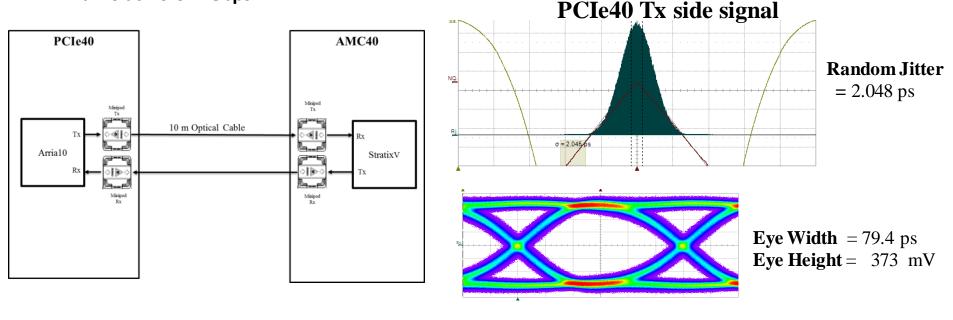

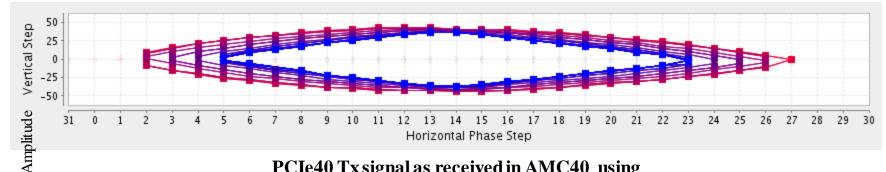

# **Avago MiniPOD™ performance study**

12 channel Transceiver tool kit design for board to board communication between Stratix V and Arria 10 at 10.312Gbps

PCIe40 Tx signal as received in AMC40 using Transceiver Tool kit (TTK)

# A Test Configuration for Firmware Resource Estimation

For power and resource estimation of CRU a low level interface is made:

- 48 bidirectional GBT link + x16 PCle Gen 3

- + SFP+ (Transceiver Toolkit design)

- It is composed of total 65 High speed links each attached with its dedicated pattern generator and pattern checker

- The entire design is integrated in Altera QSYS Integration tool

- In this design it is assumed to operate PCIe40 in extended configuration

- No user or glue logic is taken into account in this preliminary resource estimation

| Aggregated Links                                                    | Logic Utilization          | HSSI SERDES Utilization |

|---------------------------------------------------------------------|----------------------------|-------------------------|

| 48 GBT link + x16 PCIe Gen 3 +<br>SFP+ (Transceiver Toolkit design) | 34,614 / 427,200<br>(8%)   | 65/72 (90%)             |

| 36 GBT link + x16 PCIe Gen 3 +<br>SFP+ (Transceiver Toolkit design) | 32,247 / 427,200<br>(7.5%) | 53/72 (74%)             |

| 24 GBT link + x16 PCIe Gen 3 + SFP+ (Transceiver Toolkit design)    | 29,771 / 427,200<br>(7%)   | 41/72 (57%)             |

## **Summary and Outlook**

- The CRU in ALICE is designed to cope up with increased beam energy and luminosity of LHC for RUN3 and beyond

- CRU acts as the interface between:

- the on-detector electronics

- Online and Offline computing system (O2)

- the Trigger Timing System (TTS)

- Already done:

- Survey of prototype boards

- Implementation of GBT for Arria 10

- PCIe functional testing and how to use the IP cores

- A resource estimation before full firmware implementation

- Plans for near future:

- Finishing the Interface specification (External and Internal)

- Integration of CRU firmware/hardware building blocks

- Built and test pilot system

- Detector specific firmware development (Done by the sub-detector groups)

#### **Technical Team Members**

Variable Energy Cyclotron Centre (VECC)

Jubin MITRA Shuaib Ahmad KHAN Tapan Kumar NAYAK

University of Jammu

Anik GUPTA

**Bose Institute**Sanjoy MUKHERJEE

University Of Calcutta Rourab PAUL Amlan CHAKRABARTI

Wigner Research Centre for Physics

Erno DAVID Tivadar KISS

**CERN**

Filippo COSTA

#### **Leaders of Interfacing Groups:**

- •Peter CHOCHULA (DCS)

- •Marian KRIVDA (TTS)

- •Pierre Vande VYVRE (O2)

- •Alex KLUGE (Electronics Coordinator)

With Active help and Support from LHCb group:

CPPM, Marseille

Jean-Pierre CACHEMICHE and others

#### **Questions**

# Backup

### **ALICE Upgrade Strategy**

#### ❖ Goal:

- High precision measurements of rare probes at low transverse momentum, which cannot be selected with a trigger

- Target to record Pb-Pb collisions at higher luminosity to gain a factor 100 in statistics over present Run1+Run2

- Readout all Pb-Pb interactions at a maximum rate of 50kHz (i.e.  $L = 6x10^{27} \text{ cm}^{-2} \text{ s}^{-1}$ ) which is roughly 6 times of present rate

- Perform online data reduction based on reconstruction of clusters and tracks

- A separate data processing unit is needed for detector data multiplexing, processing and formatting before online data reduction.

Implementation of a novel readout architecture Common Read-out Unit (CRU).

#### **UPGRADE EFFORT**

#### **Detector Data Rate And Channels**

| Det | #                   | Run1&2  | upgrade | FE ASIC     |

|-----|---------------------|---------|---------|-------------|

|     | channels            | RO rate | RO rate | )           |

|     |                     | [kHz]   | [kHz]   |             |

| TPC | $5 \times 10^{5}$   | 3.5     | 50      | 17000 SAMPA |

| MCH | $10^{6}$            | 1       | 100     | 33000 SAMPA |

| ITS | $25 \times 10^9$    | 0.5     | 100     | 25000 ASICs |

| MFT | $500 \times 10^{6}$ |         | 100     | 896 ASICs   |

| MID | $21 \times 10^3$    | 1       | 100     | 4000 FEERIC |

| ZDC | 22                  | 8       | 100     | )           |

| TOF | $1.6 \times 10^5$   | 40      | 100     | )           |

| FIT | 160 + 64            | 80      | 100     |             |

| ACO | 120                 | 100     | 100     | )           |

| TRD | $1.2 \times 10^{6}$ | _1_     | 39      |             |

| EMC | $18 \times 10^3$    | 3.7     | 42      |             |

| PHS | $17 \times 10^3$    | 3.7     | 42      |             |

| HMP | $1.6 \times 10^{5}$ | 2.5     | 2.5     |             |

ALICE is giving answer to some of our basic questions using the extraordinary tools provided by the LHC

Collisions at the CERN Large Hadron Collider (LHC): proton-proton, proton-lead, lead-lead

#### Read-out control signal flow through CRU

• **CLOCK:** Common Reference Timing Signal + the LHC clock

• TRIGGER: PHYSICS TRIGGER + HEARTBEAT TRIGGER + BUNCH

CROSSING ID + ORBIT COUNTER VALUE

• BUSY: When Trigger rate > Detector Readout Capabilities. One signal

covers for entire sub-detector.

• **DATA:** Detector specific data payload with header and timestamp