**TWEPP 2015** Lisbon, Portugal

# **QIE12: A New High-Performance ASIC** For the ATLAS TileCal Upgrade

<u>Gary Drake<sup>1</sup></u>, Sergei Chekanov<sup>1</sup>, Alexander Paramonov<sup>1</sup>, Jimmy Proudfoot<sup>1</sup>, Robert Stanek<sup>1</sup>, Tom Zimmerman<sup>2</sup>

<sup>1</sup>Argonne National Laboratory, Lemont, IL USA

<sup>2</sup>Fermi National Accelerator Laboratory, Batavia, IL USA

**On Behalf of the ATLAS Tile Calorimeter System**

## The TileCal Upgrade Readout Architecture

- Front-End Components **Front-End Main Board** On Detector USA15 Analog & Digital **Front-End Board** MainBoard Daughte Analog & Digital MainBoard MainBoard MainBoard TTC **Daughter Board** Kintex-7 FPGA **Optical Link (Luxtera)** ΗV Analog & Digital DCS LVPS **HV Control Board**

- Prototype Development Program for the Phase 2 Upgrade

- Replacement of All Front-End & **Back-End Electronics**

- 3 Front-End Technologies being **Considered for PMT Readout :**

- > 3-in-1 (Discrete Design)

- > FATALIC (Custom ASIC)

- **QIE: Charge Integrator and Encoder**

#### > Custom ASIC, 350 nm SiGe

- **Designs in Progress**

- Test Beam Starting

- **Technology Decision:** *Summer, 2016*

### > Analog & Digital

- Low Voltage Power

- Analog & Digital

- **COTS POL Regulators**

- Analog & Digital

## General Features of the QIE12

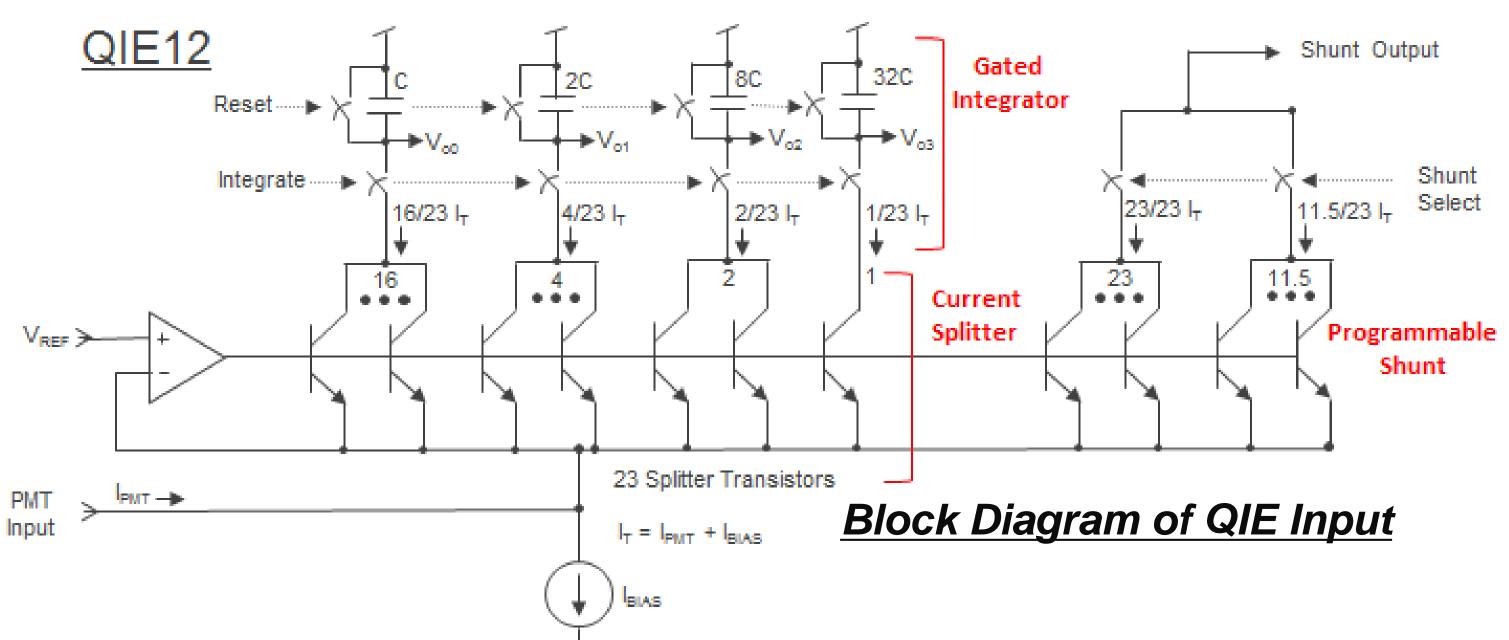

- "Current Splitter" with Gated Integrator

- No Pulse Shaping

- Pseudo-Logarithmic Response

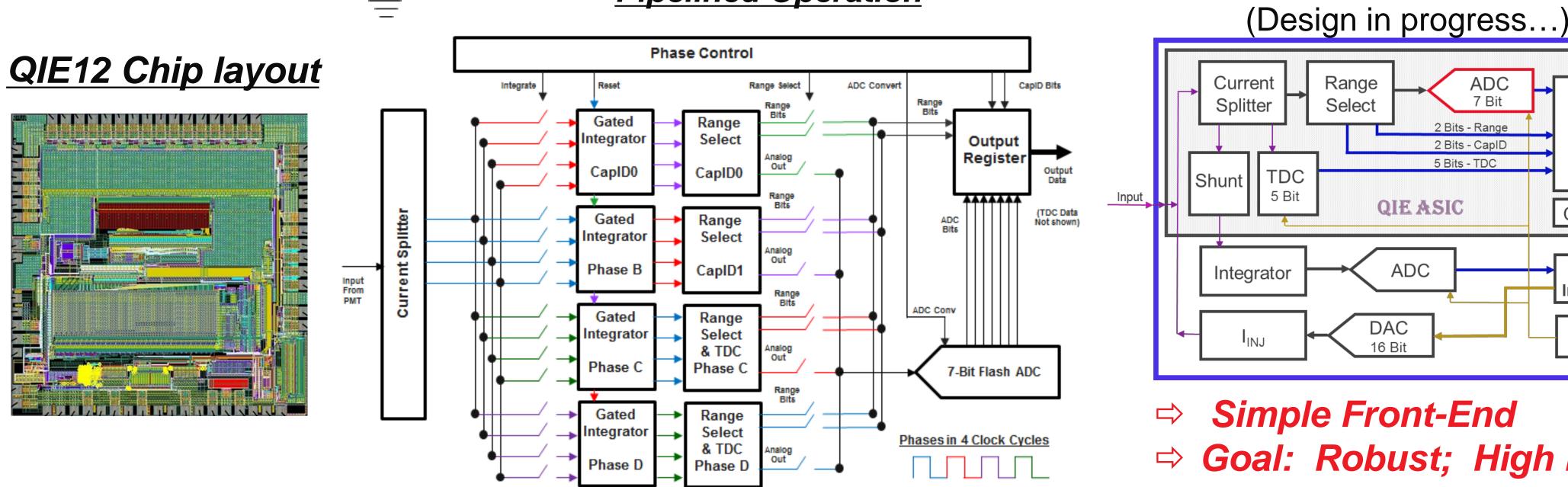

- Pipelined Operation; **Dead-timeless at 40 MHz**

- -18-bits Dynamic Range

- -1.5 3 fC Least Count

- -Internal TDC  $\rightarrow$  1 nS resolution

- -Internal Shunt for External Current Integrator

- -Internal Charge Injection

- -Low Power 360 mW/ch (Chip Only)

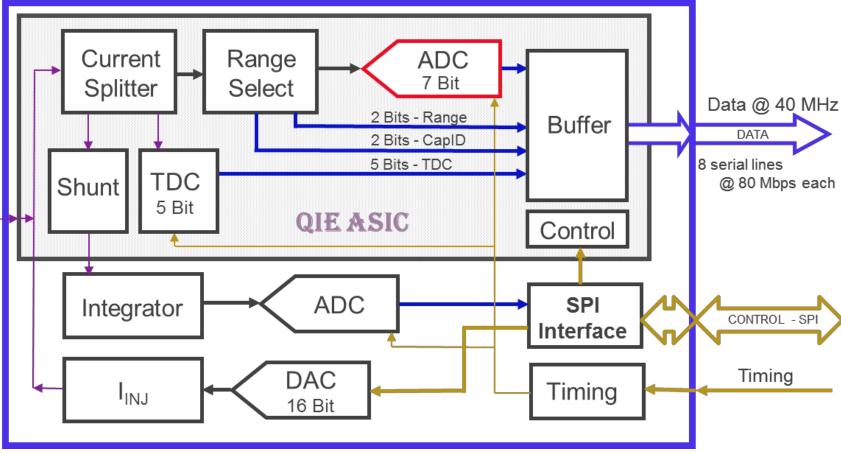

## **Overview of the QIE12**

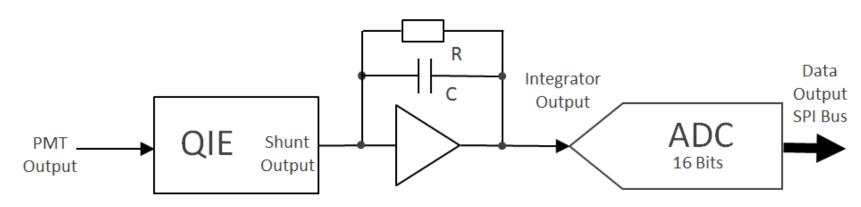

#### <u>Current Integrator Implementation</u>

(External to Chip)

**Pipelined Operation**

Block Diagram of QIE Front-End Board

- -Highly Integrated; Simple Interface & Support Circuitry  $\rightarrow$  High Reliability

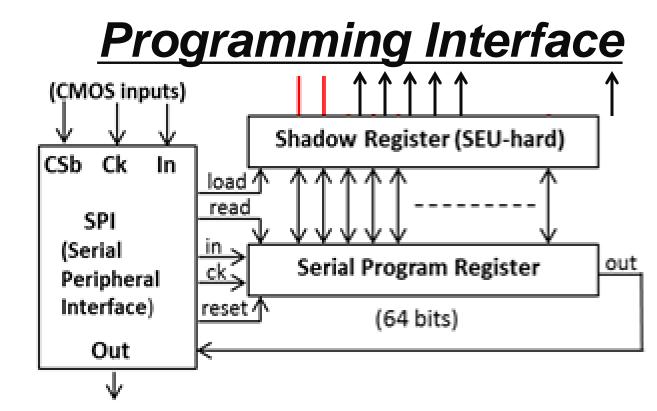

- -Radiation Tolerant (SiGe Process for **TID; SEU-Tolerant Design)**

- -50 Ohm Input, Incorporate SPI for Slow Control

- Allows for one data bus for all slow control functions: Integrator ADC; Q Inj DAC, QIE

### Simple Front-End ⇒ Goal: Robust; High Reliability

Argonne National Laboratory is a U.S. Department of Energy laboratory managed by U Chicago Argonne, LLC.