#### **Pixel/B-layer Developments**

LHCC Upgrade Session CERN, 1 / 7 / 2008

G. Darbo - INFN / Genova

Agenda Page:

http://indico.cern.ch/conferenceDisplay.py?confId=36149

ATLAS Pixel Upgrade

### **B-Layer Replacement**

####

- Detector designed for 300 fb<sup>-1</sup>, could probably withstand to 400fb<sup>-1</sup> or a bit higher with reduced efficiency;

- *integrated dose acceptable even with margin of error until 2013, but not until 2016*

- Details are very dependent on operating conditions (temperature, warm-ups)

- Hard detector failures requires to have a replacement

- - B-layer cannot be replaced in a long shut down (8 months) requires extraction of the pixel package, opening the whole detector (also beam pipe cannot be extracted without opening of pixel package -> special tooling and procedure to make in situ)

- Other options as a simpler 2 hit system with present technology (case of disaster) not realizable (collaboration to make, spares not available)

- Study the insertion of a smaller b-layer and a smaller beam pipe inside the existing detector

#### **B-Layer Replacement - Insertion**

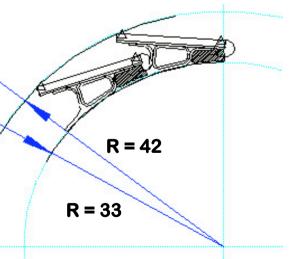

#### Study a smaller radius B-layer to insert in the existing Pixel

- It seems feasible (or not unfeasible) but not demonstrated yet;

- 16-staves (present module "active" footprint gives hermetic coverage in phi) not shingled b-layer. Requires new smaller beam-pipe (long procurement time, dimensions will be known after LHC operation 2009);

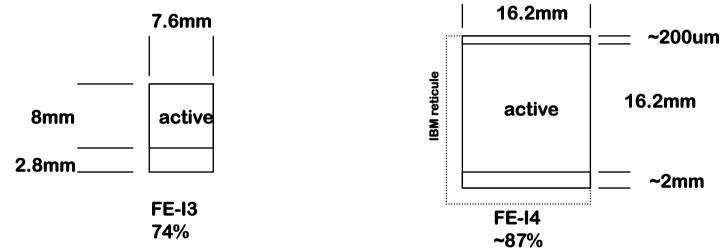

- Module technology: tracking hermetic requires new module design increase live area of the footprint:

- New chip design (FE-I4) live fraction, I/O bandwidth;

- Sensor increase radiation hard (smaller radius and ramping up LHC luminosity).

- *R&D and prototyping in 2009 construction 2010-2012;*

- Services need feasibility studies and solutions.

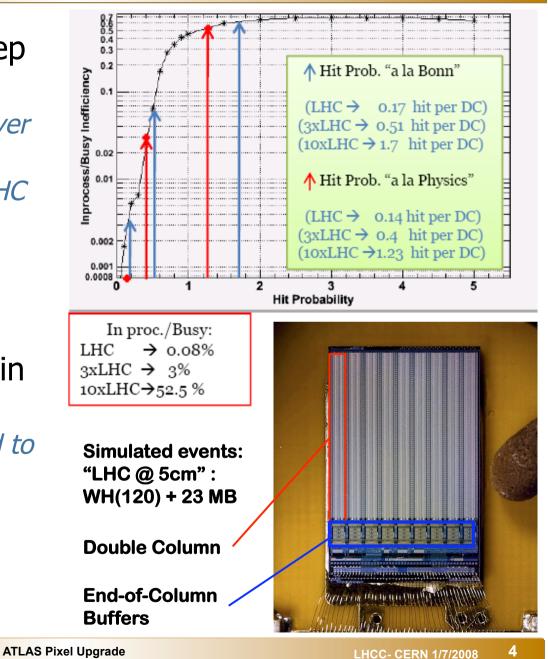

# **Limit of FE-I3 Architecture**

# Inefficiency is a very steep function of hit rate:

- Inefficiency is small for B-layer at nominal luminosity;

- Very much at the limit for LHC "Ultimate Luminosity"

- Unacceptable for B-layer @ 3.6 cm in 2016 and SLHC

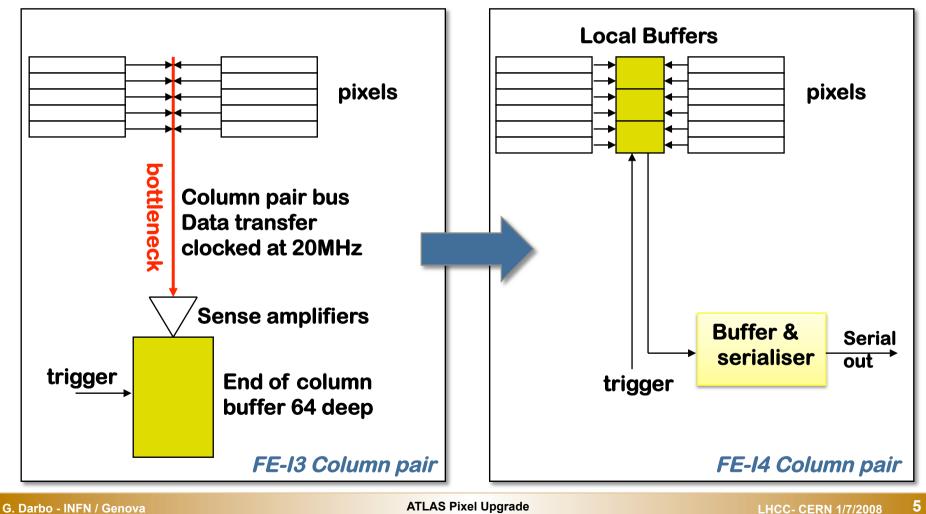

- Bottleneck is congestion in the double columns:

- All hits has to be transferred to the EoC buffers;

- What are the architecture changes...

### **Obvious Solution to Bottleneck**

- >99% or hits will not leave the chip (not triggered)

- So don't move them around inside the chip! (this will also save digital power!)

- - Possible with smaller feature size technology (130nm)

### **FE-I4 Chip Size**

- Larger live fraction of FE-I4 will make possible to meet the tight mechanical constraints of the B-layer replacement

- Larger chip will reduce bump-bonding costs mainly driven by chip placement.

|                                                | FE-I3                                            | FE-I4 goals |                                                                           |

|------------------------------------------------|--------------------------------------------------|-------------|---------------------------------------------------------------------------|

| Analog A/cm <sup>2</sup> (active)              | 130mA                                            | 80mA        | ~same voltage as now                                                      |

| Digital A/cm <sup>2</sup> (active)             | 85mA                                             | 80mA?       | Lower voltage                                                             |

| Total power/cm <sup>2</sup> (active)           | 385mW                                            | 240mW       | Nominal (not worst case)                                                  |

| WORST CASE for<br>MODULE ( <u>footprint</u> !) | 500mW/cm <sup>2</sup><br>(used for mech. design) | ?*          | Take FE-I3 absolute, scale factor, or do " <i>stand alone</i> " estimate? |

# **B-Layer & SLHC Communalities**

- The FE-I4 will not be enough for B-Layer at SLHC.

- FE-I4 hit rate target fits well the SLHC environment in the range R=12÷30cm.

- B-layer @ SLHC will need new front-end design: FE-I5.

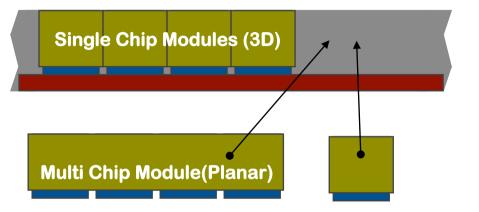

Pre-tested stave structure with integrated bus and cooling, SMD and burned-in power adapters

Robotically placed, fully tested 1-chip or multi-chip modules. Wire bond to stave after placement.

| Radius (cm) | #<br>Events | Hits/FE-I3<br>Module | FE-I3 Module<br>(Mb/s) | FE-I4<br>(Mb/s) |

|-------------|-------------|----------------------|------------------------|-----------------|

| 5.05        | 23          | 18.7                 | 48.6                   | 3.0             |

| 5.05        | 230         | 156.9                | 407.9                  | 25.5            |

| 5.05        | 230         | 156.9                | 407.9                  | 102.0           |

| 5.05        | 400         | 320.0                | 832.0                  | 208.0           |

| 12.25       | 400         | 40.0                 | 104.0                  | 26.0            |

| 3.5         | 230         | 320.2                | 832.5                  | 208.1           |

| 3.5         | 400         | 556.9                | 1447.9                 | 362.0           |

|             |             |                      |                        |                 |

|             | Z           | Х                    |                        |                 |

| Module Size | 60.8        | 16.4                 |                        |                 |

**SLHC**

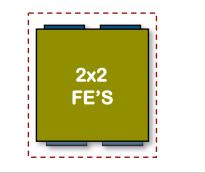

2x2 chip modules for external layers @ SLHC.

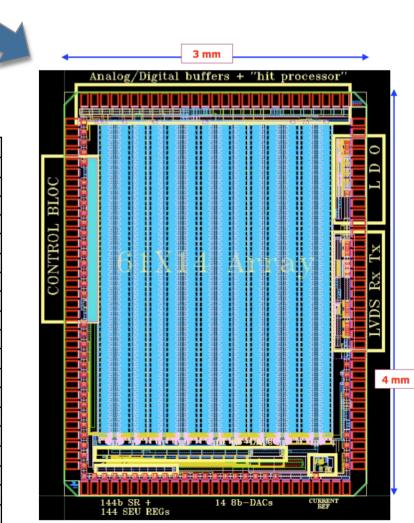

#### **Prototyping - Pixel Collaboration Chips**

- Pixel (FE-I4p) and Opto chips submitted 24/3/08:

- Prototypes for new FE-I4 in 0.13 μm CMOS

- Designing labs: Bonn, Genova, LBNL, Marseille, Nikhef,

| Pixel size                                   | 50 x 250        | $\mu m^2$           |

|----------------------------------------------|-----------------|---------------------|

| DC leakage current tolerance                 | 100             | nA                  |

| Pixel array size                             | $\geq$ 64 x 320 | Col x Row           |

| Normal pixel input capacitance range         | 300-500         | fF                  |

| Long pixel input capacitance range           | 450-700         | fF                  |

| In-time threshold with 20ns gate (400pF)*    | 4000            | e                   |

| Hit-trigger association resolution           | 25              | ns                  |

| Same pixel two-hit discrimination (time)     | 400             | ns                  |

| Single channel ENC sigma (400fF)             | 300             | e                   |

| Tuned threshold dispersion (max)             | 100             | e                   |

| Charge resolution                            | 4               | bits                |

| ADC method                                   | TOT             |                     |

| Operating voltage range                      | 1.2 - 1.5       | V                   |

| Total analog supply current @400fF           | 10              | μA / pixel          |

| Radiation tolerance (specs met at this dose) | 200             | MRad                |

| Average hit rate                             | 200             | MHz/cm <sup>2</sup> |

| Trigger latency (max)                        | 3.2             | μs                  |

| Single chip data output rate                 | 160             | Mb/s                |

| Maximum trigger rate                         | 200             | KHz                 |

| Total digital supply current @ 100KHz        | 10              | μA / pixel          |

### **Pixel Oriented R&Ds**

#### 10 R&Ds where Pixels are involved have been (or will be) submitted

| Doc no.        | Short<br>name           | Title                                                                                                                      | Institutes                                                                                                                                                            | Status at 30/6/2008     |

|----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| ATL-PA-MN-0001 | Opto                    | Radiation Test Programme for the ATLAS<br>Opto-Electronic Readout System for the<br>SLHC for ATLAS upgrades                | Taiwan, Ljubljana, Ohio, Oklahoma,<br>Oxford, SMU                                                                                                                     | Approved EB             |

| ATL-PA-MN-0007 | 3D Sensors              | Development, Testing and<br>Industrialization of Full-3D Active-Edge<br>and Modified-3D Silicon Radiation Pixel<br>Sensors | <i>CNM Barcellona, Bonn, Freiburg, Genova<br/>(Milano), Glasgow, Hawaii, LBNL,<br/>Manchester, Oslo, SINTEF Oslo, Prague,<br/>MBC/Stanford, IRST Trento, Valencia</i> | Approved by EB          |

| ATL-P-MN-0012  | R/O<br>Architectures    | Read-out Electronics for the ATLAS upgraded tracker                                                                        |                                                                                                                                                                       |                         |

| ATL-P-MN-0016  | Gossip                  | R&D proposal to develop the gaseous<br>pixel detector Gossip for the ATLAS<br>Inner Tracker at the Super LHC (SLHC)        | NIKHEF, SACLAY, Twente                                                                                                                                                | EoI Received            |

| ATL-P-MN-0035  | Versatile Link          | The Versatile Link Common Project                                                                                          | CERN, Strasbourg, Oxford, SMU Dallas.                                                                                                                                 | Sent to CB for comments |

| ATU-RD-MN-0008 | Powering                | Research and Development of Power<br>Distribution Schemes for the ATLAS<br>Silicon Tracker Upgrade                         | BNL, Bonn, CERN, Krakow, LBNL, RAL,<br>Wuppertal, Yale                                                                                                                | Approved by EB          |

| ATU-RD-MN-0010 | Thin Pixels             | R&D on thin pixel sensors and a novel<br>interconnection technology for 3D<br>integration of sensors and electronics       | MPI Munich                                                                                                                                                            | Approved by EB          |

| ATU-RD-MN-0012 | Diamond                 | Diamond Pixel Modules for the High<br>Luminosity ATLAS Inner Detector<br>Upgrade                                           | Bonn, Carleton, CERN, Jožef Stefan<br>Institute, Ohio State, Toronto                                                                                                  | Approved by EB          |

| ATU-RD-MN-XXXX | Planar Pixel            | R&D on Planar Pixel Sensor Technology for the ATLAS Inner Detector Upgrade                                                 | <i>Prague, LAL Orsay, Bonn, HU Berlin, TU<br/>Dortmund, MPP Munich, MPI Munich,<br/>Udine, Liverpool, UNM Albuquerque,<br/>UCSC Santa Cruz.</i>                       | EoI to Submit           |

| ATL-RD-MN-XXXX | Pixel Local<br>Supports | Research and Development Local<br>Supports for Pixel Detector Upgrades                                                     |                                                                                                                                                                       | EoI to Submit           |

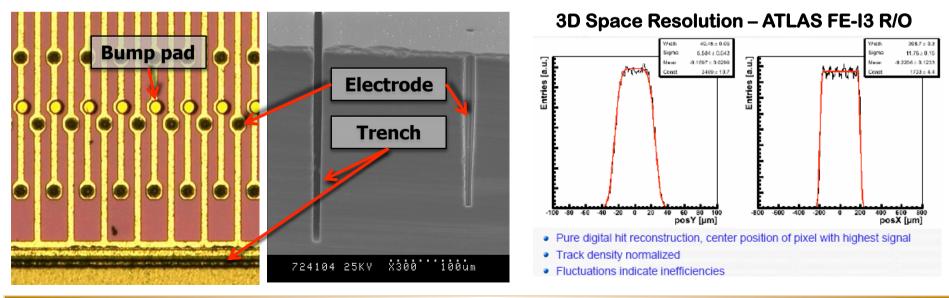

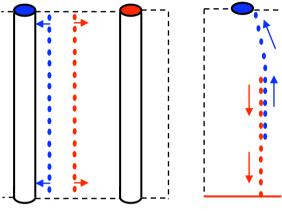

# **3D Sensors Basics**

- Decoupled directions: track traversal versus drift field.

- Shorter traveling distance, more charged collected.

- Active edge: Deep Reactive Ion Etching (DRIE) trench can replace saw dicing.

- Edge itself is an electrode

Planar and 3D Charge Collection Principle

ATLAS Pixel Upgrade

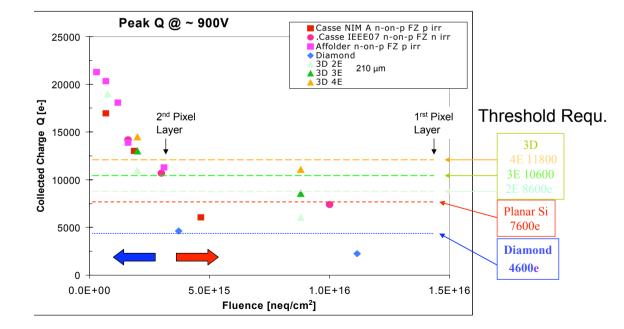

#### **Planar Sensors**

- R&D on planar silicon technologies mainly to reduce cost, increase radiation tolerance and reduce inactive area:

- Bulk material: n-type (n-on-n current pixel sensor) or p-type (single side cost effective)

- Thin sensors (50÷75µm thickness): reduce volume leakage current (noise, power)

- Active edge: no need of shingling or double face stave for hermetic coverage

- *Slim edge: guard rings from 1100µm to ~100µm*

#### Diamonds

- No cooling;

- No leakage current;

- Small capacitance -> small noise;

- High radiation hard -> B-layer

Hartmut F.-W. Sadrozinski, LBL Pixel Upgrade, May 22, 2008