## MFT: WG6 Readout activities LPC Clermont-Ferrand-1<sup>st</sup> april 2015

Cyrille Guérin (IPNL/IN2P3/CNRS) Christophe Flouzat (CEA/IRFU)

ipnl

### Outline

- I. Reminder on the MFT

- II. On-detector studies (Front-end Boards and integration)

- 1. Ladders (FlexPrintedCircuit)

- 2. Disks

- 3. Power supply unit

- 4. Motherboards

- 5. Barrel patch panel

- III. Off-detector studies (Readout Unit)

- 1. Synoptic and numbers

- 2. Readout Unit boards

- IV. WG6 readout tasks

- V. Human ressources and needs

- VI. Discussions

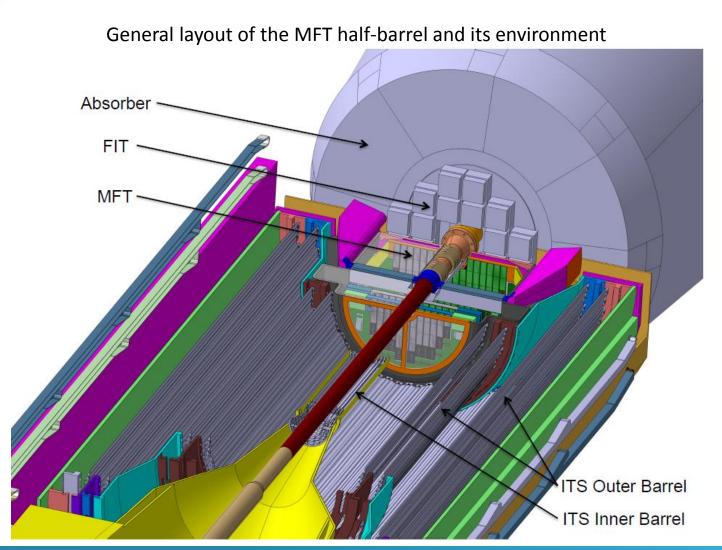

## Reminder on the MFT

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015 c.guerin@ipnl.in2p3.fr

Ι.

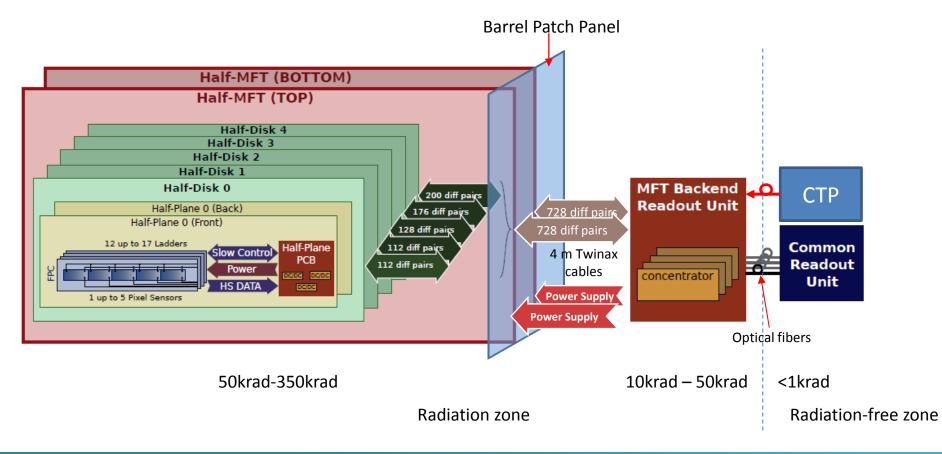

## Reminder on the MFT

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015 c.guerin@ipnl.in2p3.fr

Ι.

## I. Reminder on the MFT

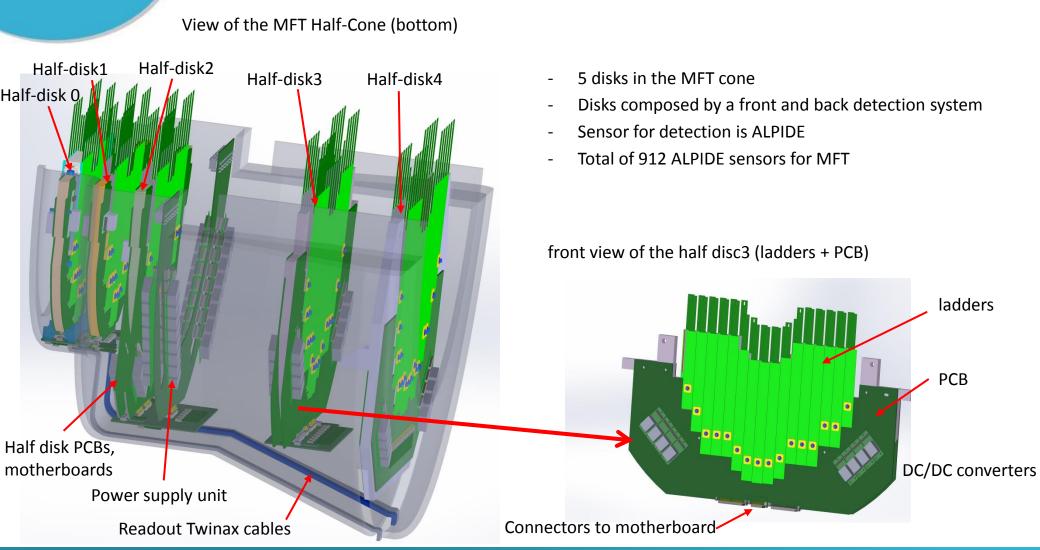

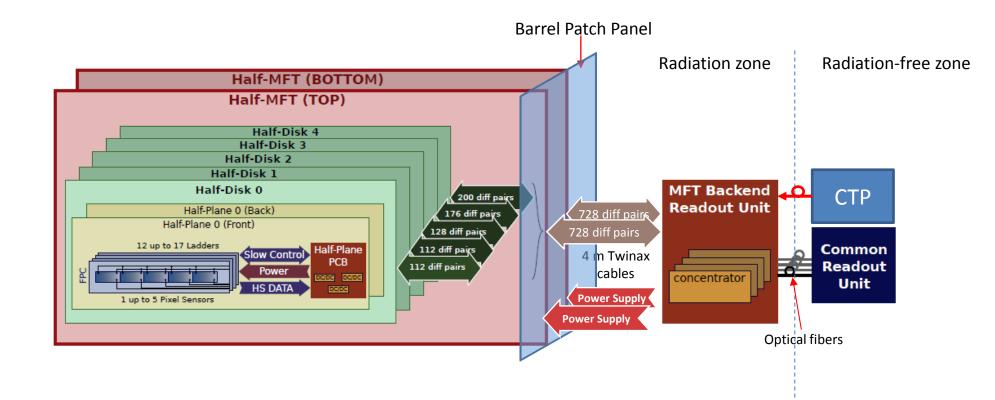

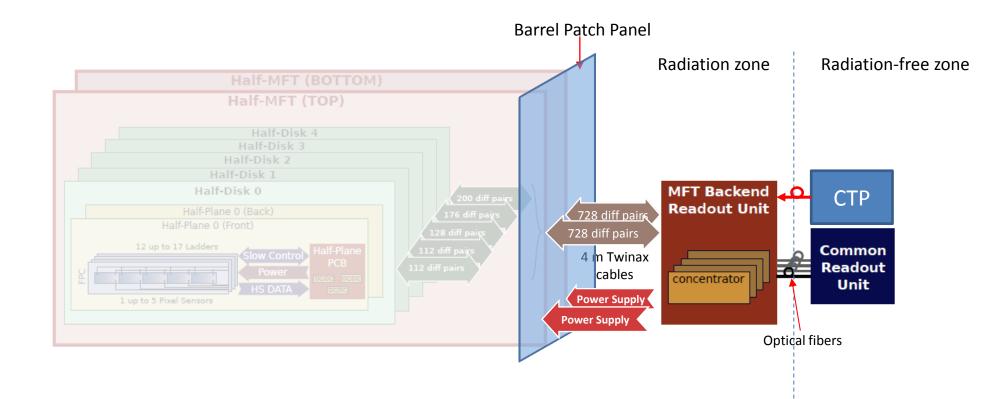

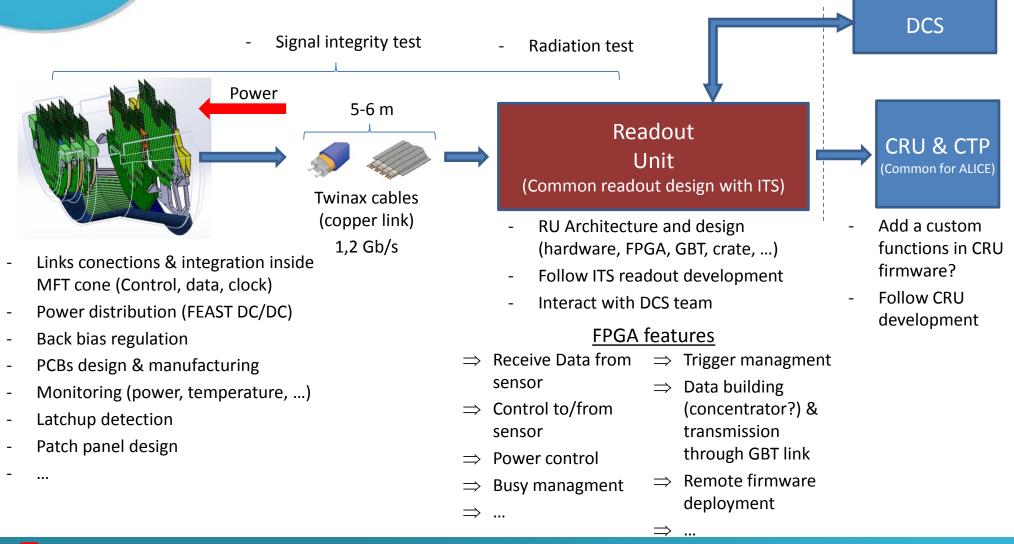

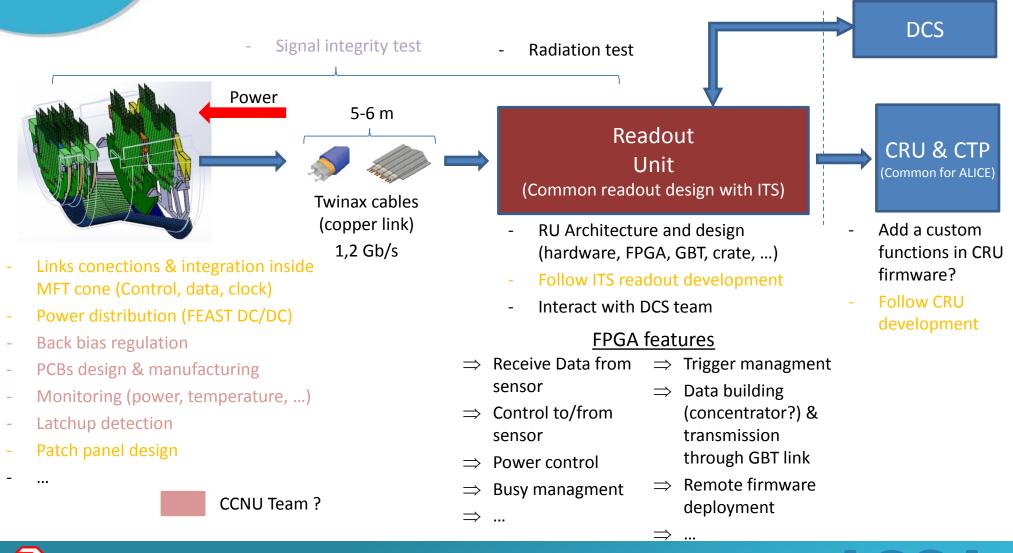

General readout diagram of the MFT Common ITS/MFT readout architecture (Inner Barrel + Twinax)

5

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015

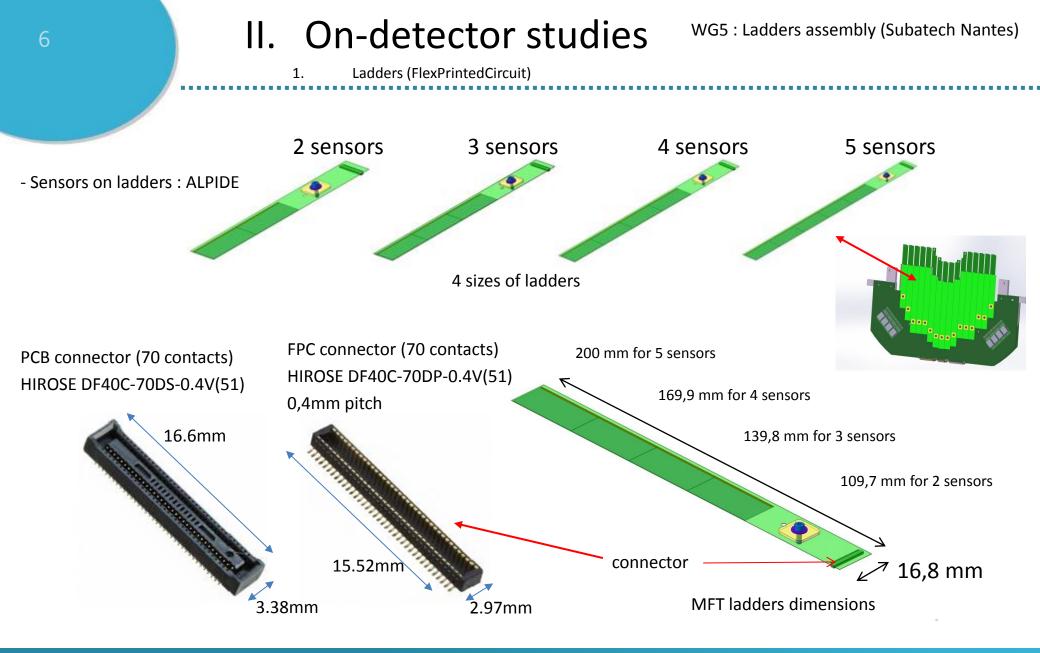

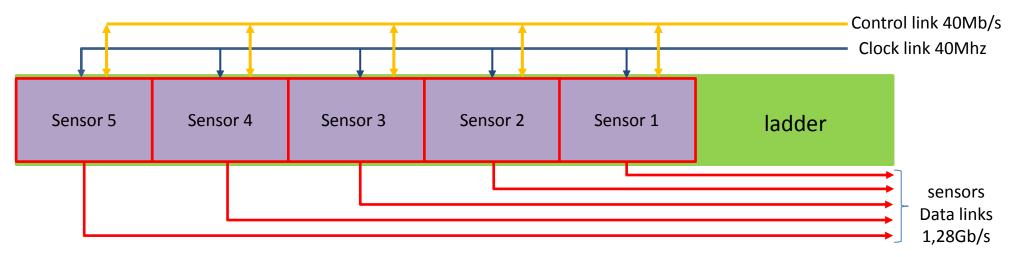

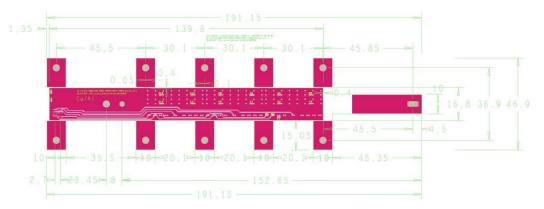

Ladders (FlexPrintedCircuit)

Data/Control connections on ladder

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015 c.guerin@ipnl.in2p3.fr

1.

Ladders (FlexPrintedCircuit)

1.

| Signal names       | Numbers                       | features                                                            |

|--------------------|-------------------------------|---------------------------------------------------------------------|

| HSDATA             | As many as sensors<br>Up to 5 | Point to point link<br>High speed differential link (LVDS) 1.28Gb/s |

| DCLK               | 1 per ladder                  | Multi-drop link<br>40Mhz differential link (MLVDS)                  |

| DCTRL              | 1 per ladder                  | Multi-drop link<br>40Mb/s differential link (LVDS)                  |

| 1.8V analog power  | 1 plan / ladder               | 20mA / sensor => up to 100mA / ladder                               |

| 1.8V digital power | 1 plan / ladder               | 105mA / sensor => up to 525mA /ladder                               |

| GND analog         | 1 plan / ladder               | Connected with GND digital on the half disc?                        |

| GND digital        | 1 plan / ladder               | Connected with GND analog on the half disc ?                        |

| Back-bias (SUB)    | 1 plan / ladder               | 0V to -10V Must be confirmed                                        |

| Back-bias (PWELL)  | 1 plan / ladder               | 0V to -10V Must be confirmed                                        |

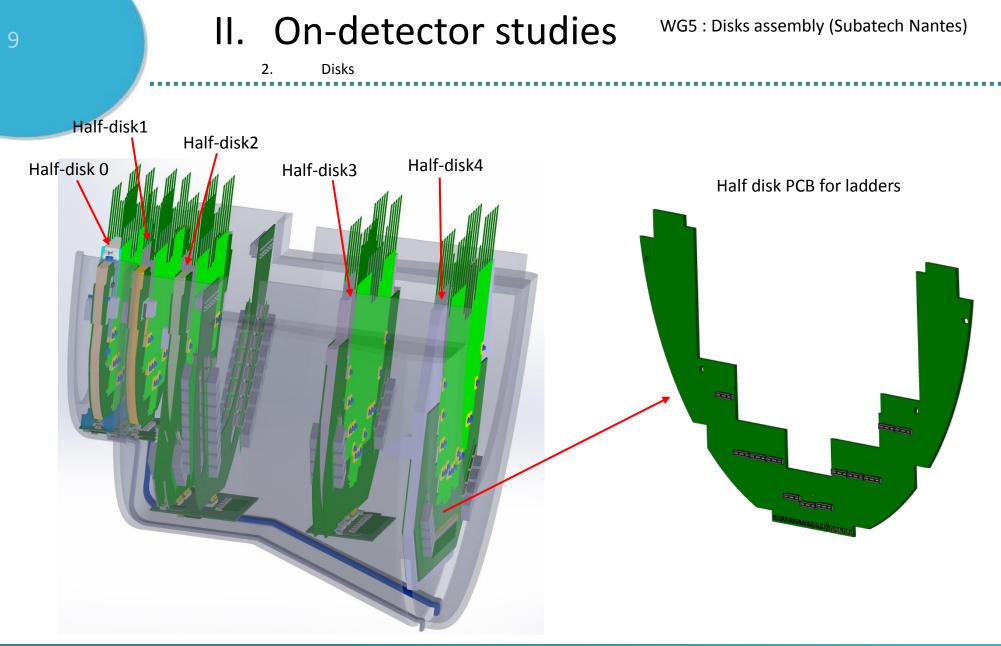

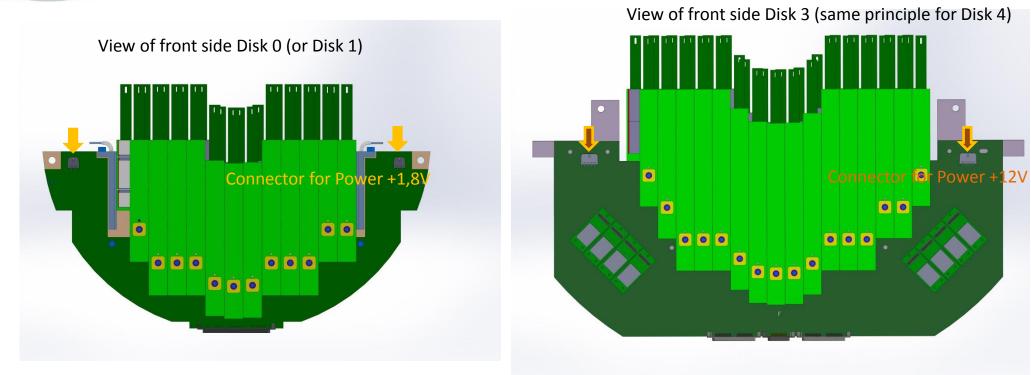

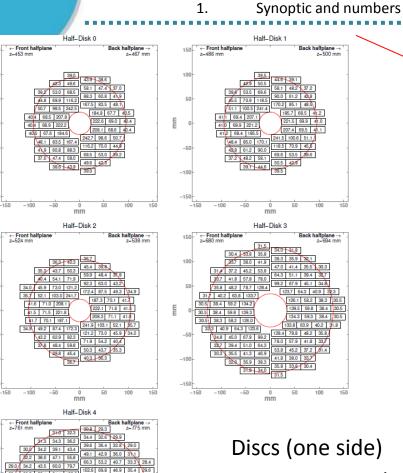

Disks

2.

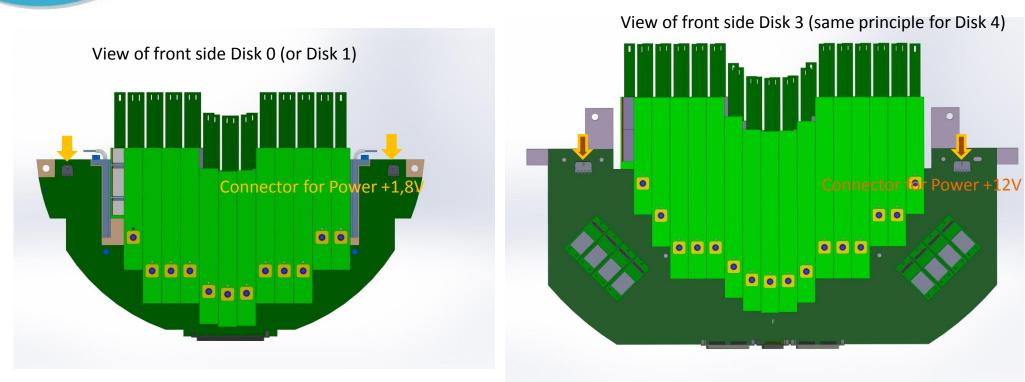

#### **Disk Power supply**

- Disk 1 same as Disk 0 without DC/DC converters

- Disk 2 bigger than Disk 1 but without DC/DC converters

- $\Rightarrow$  Need Power from a Power supply Unit

- Disk 3 bigger than Disk 2 with DC/DC converters

- Disk 4 bigger than Disk 3 with DC/DC converters

- $\Rightarrow$  Power supply directly from +12V

10

#### **Disk Power supply**

- Two DC/DC converters (analog and digital) needed for supply a quarter of a disk side

- $\Rightarrow$  8 DC/DC converters for one side of a disk

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015 c.guerin@ipnl.in2p3.fr

2.

Disks

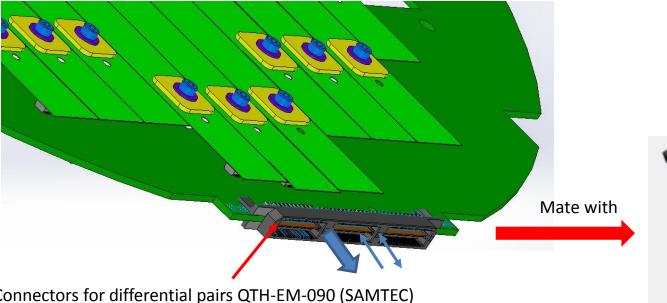

#### **Disk Signals connection**

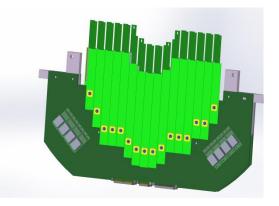

#### **View of Half-disc PCB**

Disks

2.

- DATA, Clock, Control links from/to sensors  $\Rightarrow$

- Temperature measurement links (CTN)  $\Rightarrow$

- ON/OFF signals for DC/DC converters (only for disk3 and 4)  $\Rightarrow$

- $\Rightarrow$  Latchup measurement (on DC/DC converters for disk3 and 4)

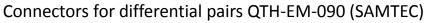

QSH-090 (SAMTEC)

On motherboard

Power supply unit

- $\Rightarrow$  Provides +1,8V (analog and digital) for disk 0, 1 and 2

- $\Rightarrow$  On board latchup measurement

3.

$\Rightarrow$  Connection for +12V input and +1,8V outputs (analog and digital)

Connection for input/output voltage 8 DC/DC converters for one side of a disk Connector for DC/DC converters slow control signals (ON/OFF, temperature and latchup measurement)

View of the first proposal power supply unit (only for disk 0 and 1)

13

Power supply unit

3.

Space for water cooling system between rows o DC/DC converter

Power supply unit

- $\Rightarrow$  New solution under study for power supply unit

- $\Rightarrow$  Like disk assembly (Mechanical spacer between 2 PCBs)

- $\Rightarrow$  Better rigidity

3.

$\Rightarrow$  Water cooling system could be integrated in the mechanical part

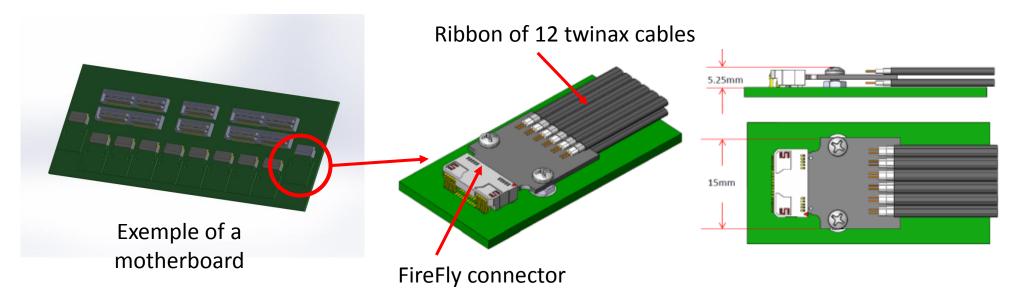

Motherboards

4.

Motherboards to interface disks to Twinax cables Studies of the mechanical structure are made by WG7 (Subatech Nantes)

Disk 0 and Disk 1

Power supply unit + Disk2

Disk3

16

Motherboards

4.

Twinax cables with FireFly connection (SAMTEC)

#### Custom prototype by SAMTEC for ITS

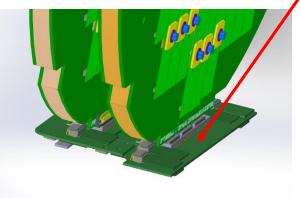

Half MFT view in the barrel

Barrel Patch Panel

5.

Barrel Patch panel used to interconnect twinax cables from the motherboard (inside cone) to the 4m twinax cables from the readout unit

Services repartition area

c.guerin@ipnl.in2p3.fr

Twinax cables are connected to the barrel Patch panel

Patch panel boards fixed on the barrel

18

MFT : WG6 activities - LPC Clermont-Ferrand –  $1^{st}$  april 2015

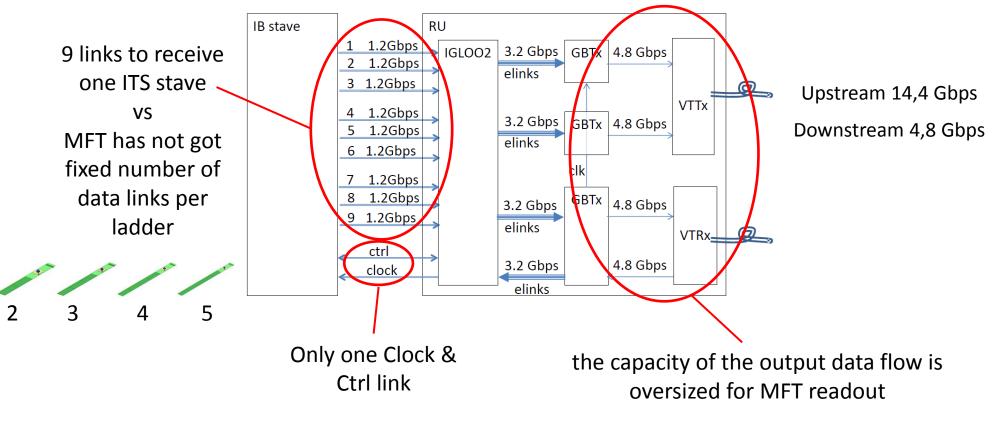

Synoptic and numbers

1.

General readout diagram of the MFT Common ITS/MFT readout architecture (Inner Barrel + Twinax)

c.guerin@ipnl.in2p3.fr

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015

Synoptic and numbers

1.

General readout diagram of the MFT Common ITS/MFT readout architecture (Inner Barrel + Twinax)

c.guerin@ipnl.in2p3.fr

20

MFT : WG6 activities - LPC Clermont-Ferrand –  $1^{st}$  april 2015

One plane

op half-disl

Synoptic and numbers

Numbers of sensors (with power consumption) and numbers of differential links at different level in the MFT

1.

One side of Half disc

|                       |                                                     | Half-disc 0<br>one side | Half-disc 1<br>one side | Half-disc 2<br>one side | Half-disc 3<br>one side | Half-disc 4<br>one side | Plane 0 | Plane 1 | Plane 2 | Plane 3 | Plane 4 | All MFT |

|-----------------------|-----------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|---------|---------|---------|---------|---------|---------|

| sensors               | Nbr ALPIDE                                          | 33                      | 33                      | 39                      | 57                      | 66                      | 132     | 132     | 156     | 228     | 264     | 912     |

| ion                   | 1.8V analog<br>20mA/sensor                          | 660mA                   | 660mA                   | 780mA                   | 1,14A                   | 1,32A                   | 2,64A   | 2,64A   | 3,12A   | 4,56A   | 5,28A   | 18,24A  |

| Power<br>consumpt     | 1.8V digital<br>105mA/sensor                        | 3,47A                   | 3,47A                   | 4,1A                    | 5,99A                   | 6,93A                   | 13,88A  | 13,88A  | 16,4A   | 23,96A  | 27,72A  | 95,84A  |

| Differential<br>links | links HSDATA<br>+<br>DCLK links<br>+<br>DCTRL links | 57                      | 57                      | 65                      | 89                      | 100                     | 228     | 228     | 260     | 356     | 400     | 1472    |

MFT : WG6 activities - LPC Clermont-Ferrand –  $1^{st}$  april 2015

c.guerin@ipnl.in2p3.fr

estimated throughput/sensor

Total throughput for each disk and for whole MFT

(without safty factor)

|           | Throughput (Mb/sec)<br>Front and back side |

|-----------|--------------------------------------------|

| Disk 0    | 10283,8                                    |

| Disk 1    | 10375                                      |

| Disk 2    | 11377,2                                    |

| Disk 3    | 11959,6                                    |

| Disk 4    | 12939                                      |

| Total MFT | 56934,6 Mb/s                               |

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015

c.guerin@ipnl.in2p3.fr

118.9 56.6 37.8 30.4

79.7 60.0 43.5 34.2 29.0

55.8 47.1 38.1 32.2

43.4 39.1 34.2 80.0

36.2 34.3 31

32.3 31.0

04 37.8 56.6 118.7

0.4 37.8 57.0 122.6

31.6 39.8 59.2 109.7 29.0 35.4 46.9 69.8 10

4 33.3 40.7 53.1 66.3

311 36.0 42.9 49.1

29.0 32.8 36.4 39.6

29.9 32.6 34.4

29.3 30.8

Synoptic and numbers

1.

Estimated Data throuput For a quarter of Disk (One PCB)

PCB disk

|                                                       | PCB<br>disk 0 | PCB<br>disk 1 | PCB<br>disk 2 | PCB<br>disk 3 | PCB<br>disk 4 | Total<br>MFT |

|-------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|--------------|

| Nbr Data links (1,2Gb/s)                              | 33            | 33            | 39            | 57            | 66            | 912          |

| Max data rate possible (Gb/s)                         | 39,6          | 39,6          | 46,8          | 68,4          | 79,2          | 1094,4 Gb/s  |

| Estimated Data throuput with safty factor of 2 (Gb/s) | 5,2           | 5,2           | 5,8           | 6             | 6,6           | 115,2 Gb/s   |

| Number of GBT needed (4,8Gb/s)                        | 2             | 2             | 2             | 2             | 2             | 10           |

Nbr of data links Twinax cables

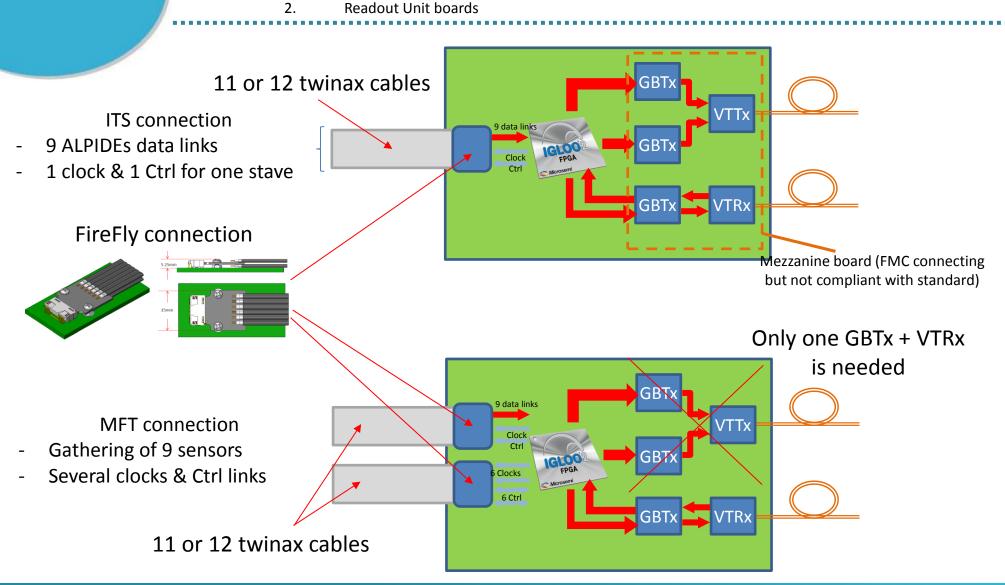

Readout Unit boards

2.

**ITS Inner Barrel Solution**

RU for 1 stave (9 sensors) with 3 GBT links

#### IB RU with 1\* IGLOO2 with 16 SERDES

Readout Unit boards

2.

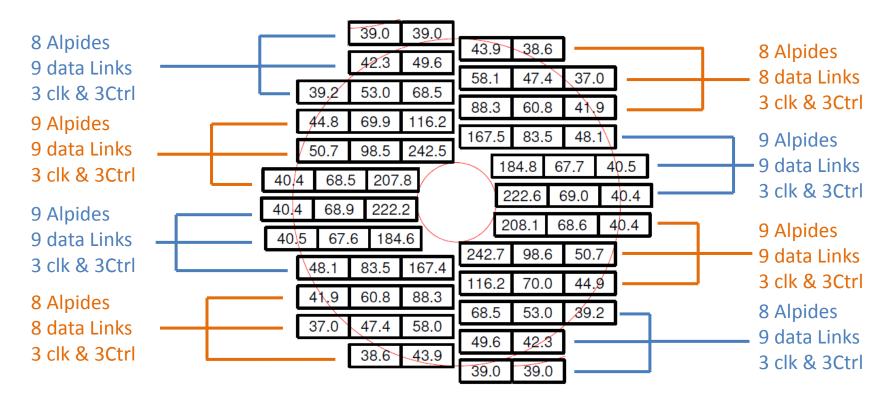

Exemple of gathering for ladders of one side of Disk 0

- 8 RU boards per side of disk 0 => 16 RU boards for Disk 0

## IV. WG6 readout tasks

27

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015 c.guerin@ipnl.in2p3.fr

ippl

## IV. WG6 readout tasks

28

## IV. WG6 readout tasks

MFT : WG6 activities - LPC Clermont-Ferrand – 1<sup>st</sup> april 2015 c.guerin@ipnl.in2p3.fr ipnl

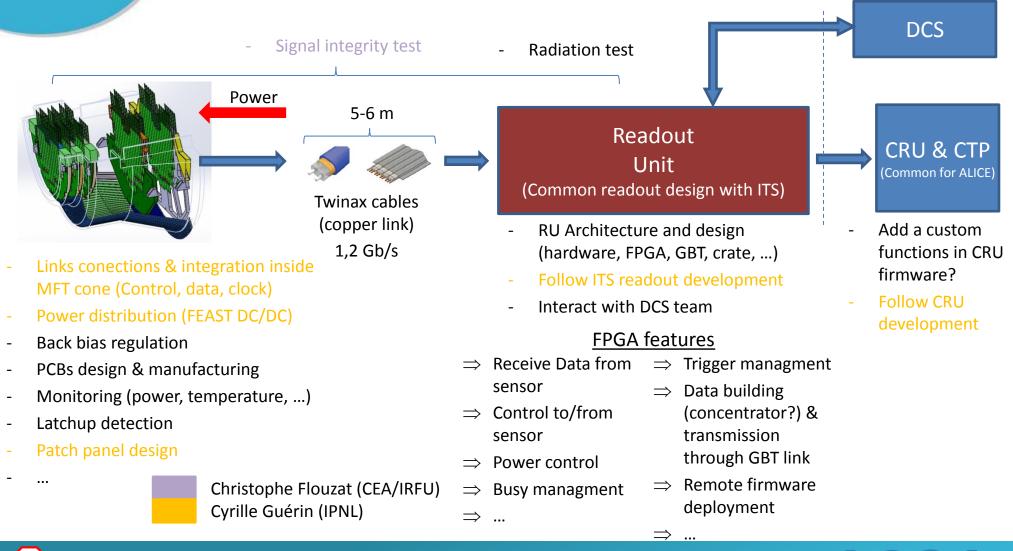

### V. Human resources and needs

Currently:

**Christophe Flouzat** (CEA-Saclay – 0,2 FTE2015 – 0,3FTE2016) Signal integrity tests on twinax link **Cyrille Guérin** (IPNLyon - 0,8 FTE) convener of WG6, works on

- connection studies (inside cone & patchpanel)

- follow ITS readout meetings and just start study of MFT RU architecture to compare with ITS's one

Under discussions for designing ON-detector boards :

- Dr DAICUI Zhou, WANG Dong and their team (CCNU, Wuhan)

Discussions engaged with Indians for 0,6FTE

- Difficulties to identify the task on which they would like to participate

Needs reinforcement on the Readout Unit design (Off-detector):

- 1,5 FTE2015 and 0,75 FTE2016 in case of Indiens participation

- Otherwise 2,1 FTE2015 and 1,35 FTE2016

#### V. Human resources and needs

Reinforcement for

Two parts on the Readout Unit design

#### Hardware (RU board design)

- Continue to follow ITS design of the RU board

- Interfaces (CRU, CTP, PowerUnit ...)

- Hardware (FPGA, GBTX, VTx)

- Propose a dedicated architecture for MFT and discuss with ITS WP10 tem to design this common RU

- Interact with the group which design the firmware

- Interact with DCS team

- Provide a prototype of a RU board

#### Firmware (FPGA architecture and configuration)

- Follow firmware design of ITS

- Identify blocks in FPGA which require modification for MFT

- Involvement in the firmware design of the ALICE CRU

- Provide the firmware of the RU board

In both cases => strong interaction with ITS WP10 team

#### VI. Discussions

# Thank you