## **RE22- PANDA MVD**

#### **Daniela Calvo** INFN – Sezione di Torino on behalf of the PANDA MVD group

Request: test of silicon device prototypes for the Micro Vertex Detector of PANDA (RE22) experiment.

- Available Prototypes

- Setup: reduction of the space request

- Beam time: scheduled too early in July

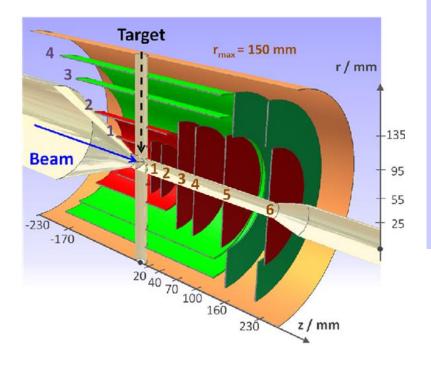

## The Micro Vertex Detector

It must combine good space resolution with accurate time-tagging

Main functions

- Primary vertex reconstruction

- Identification of the secondary vertices ( $c\tau$  of some hundreds of  $\mu$ m)

- Improvement in momentum resolution

- Support PID of low momentum particles by energy loss measurement

- Good spatial resolution (some tens of μm in ρφ, better than 100 μm along z)

- Time resolution < 10 ns</li>

- Continuous readout at ~ 10<sup>7</sup> interactions /s (clock signal @160 MHz)

- Limited material budget X/Xo ≤ 1 % / layer

- Radiation tolerance

< 10<sup>14</sup> n <sub>1 MeV eq</sub> cm<sup>-2</sup>

- Provide at least four hits per track

- Energy loss measurement

- Room temperature operation

- Routing and services only in the backward region

10.3 M (pixel channels) – active area: 0.106  $m^2$ 162 k (strip channels) – active area: 0.494  $m^2$

## Silicon devices

#### Hybrid epitaxial silicon pixel:

- ✓ **Sensor** made of Epitaxial Silicon material

- ρ<sub>epi</sub> ~ kΩ·cm

- ρ<sub>Cz</sub> ~ 20-50 mΩ·cm

- **✓ Pixel cell size**: 100μm x 100μm x 100μm

- ✓ ASIC developed in 130 nm CMOS technology (ToPix)

- Triggerless

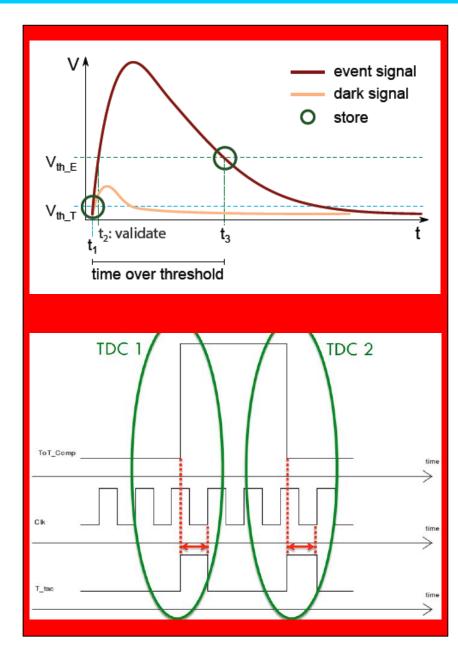

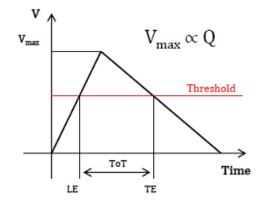

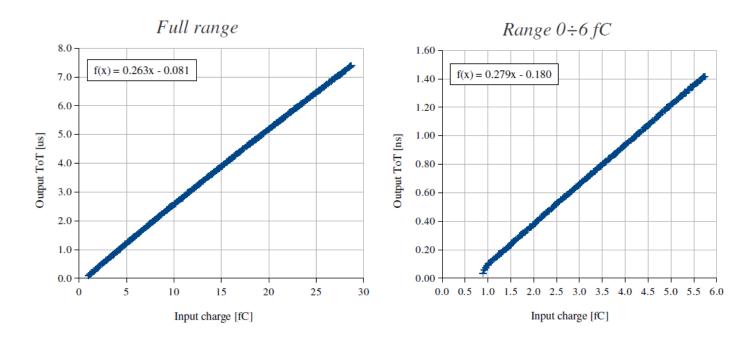

- dE/dx using Time over Threshold technique

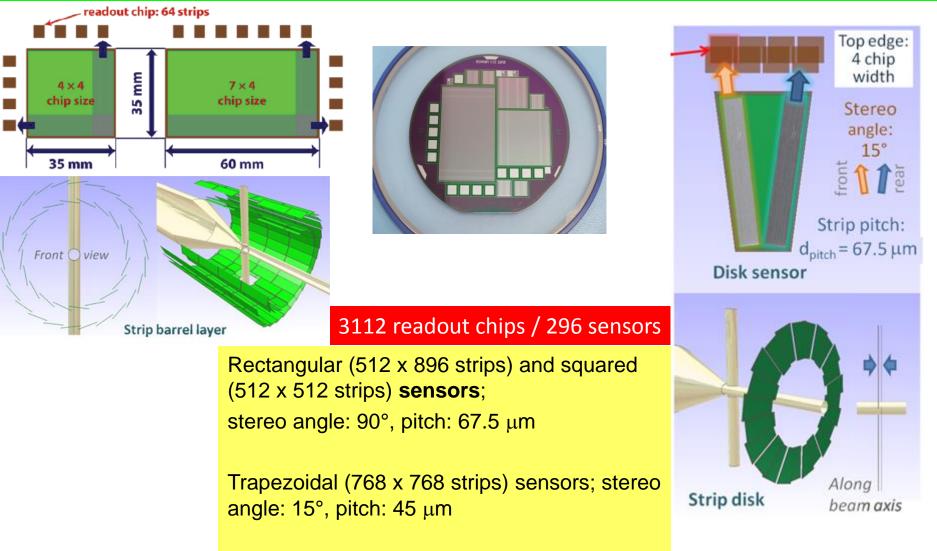

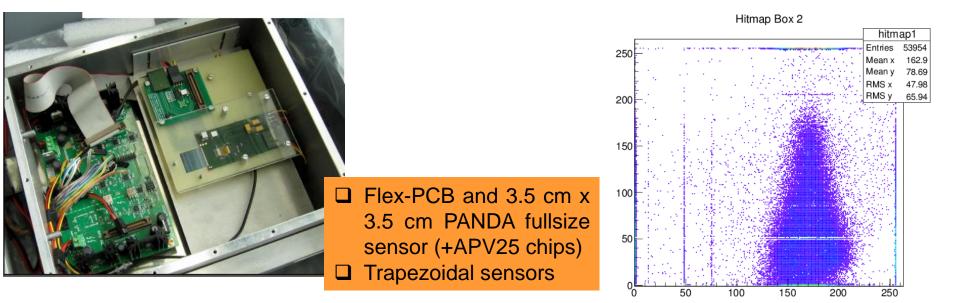

#### Double sided silicon micro strips:

- Rectangular (512 x 896 strips) and squared (512 x 512 strips) sensors; stereo angle: 90°, strip pitch: 67.5 μm, 285 μm thickness

- ✓ ASIC developed in 110 nm CMOS technology (PASTA)

- Triggerless

- ToT technique for dE/dx measurement

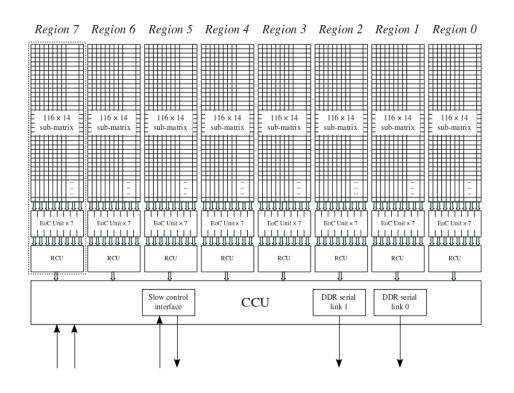

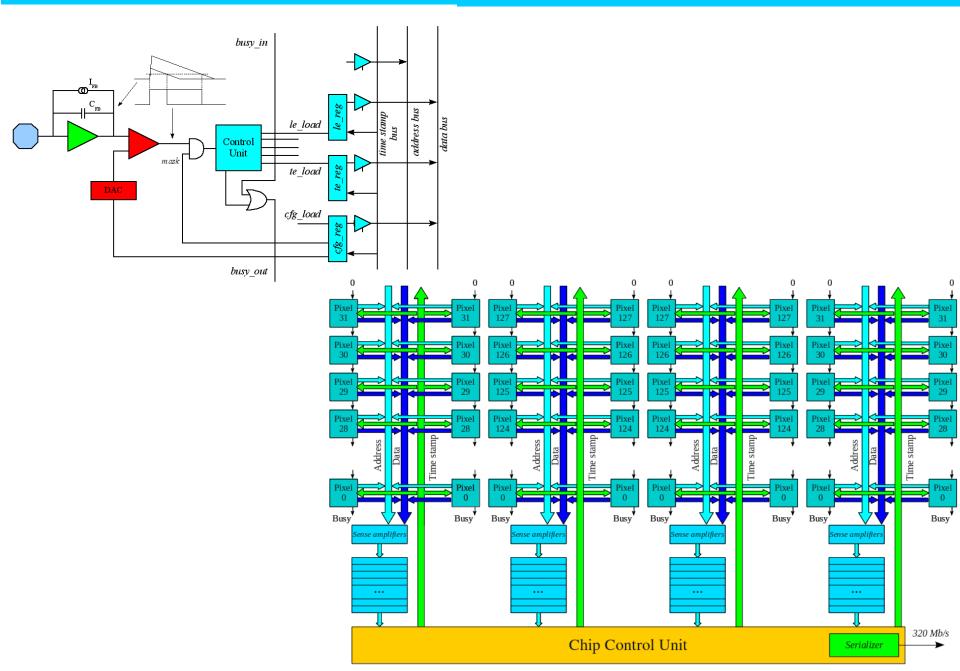

## ToPix

- Columns divided in 8 regions with 7 double columns each

- FIFO in the end of column and region control

- Output bandwidth: 2 x 320 Mb/s

- Supply voltage: 1.2 V

- Pixel matrix: 110 x 116

- Size (to be optimized): 11.2 mm x 14.8 mm

- dE/dx measurement: ToT, 12 bits dynamic range

- Maximum input charge: 50 fC

- Detector type: n and p

- Noise floor: < 200 electrons</li>

- Input clock frequency: 160 MHz

- Time resolution: ~ 6 ns

- Power consumption: ≤ 0.8 W/cm<sup>2</sup>

- Maximum event rate/cm<sup>2</sup>: ~ 6.1 x 10<sup>6</sup>

- Data rate per chip: up to ~ 450 Mb/s

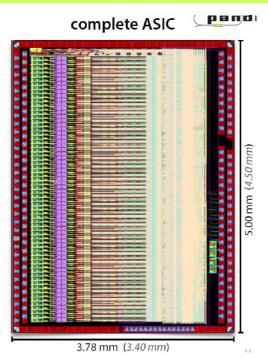

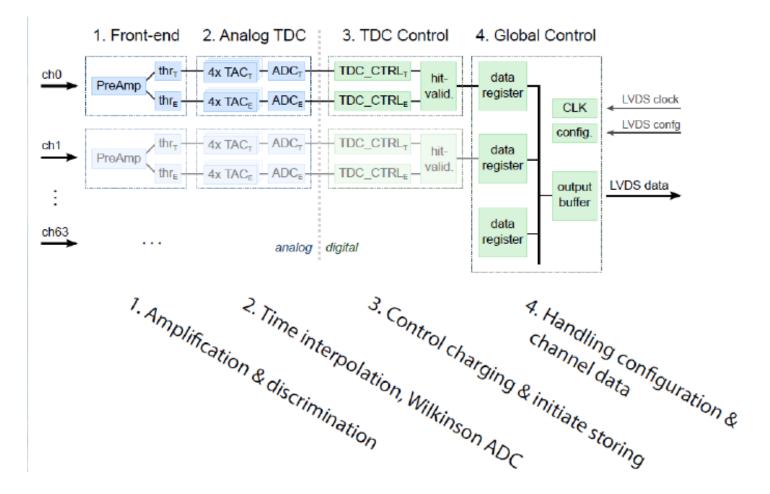

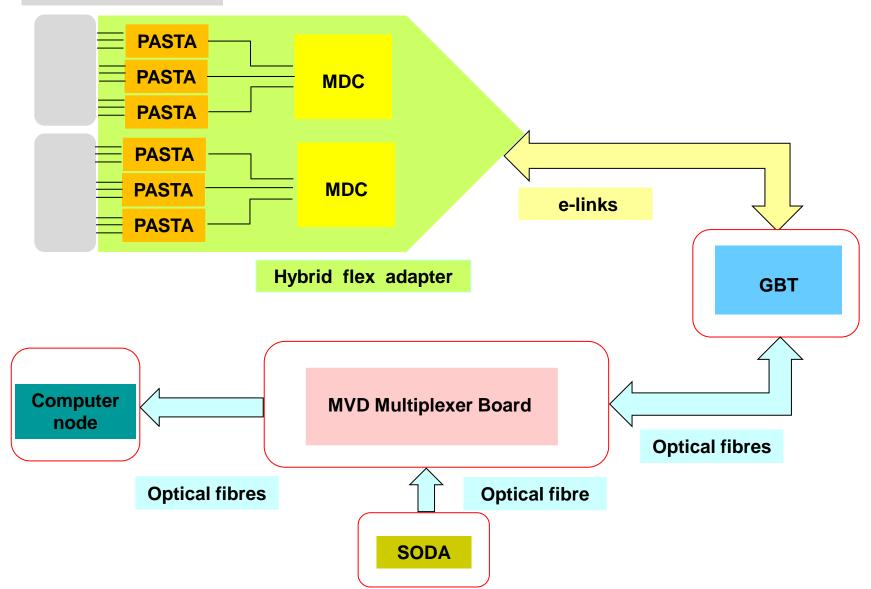

## PASTA

First prototype under submission:

- 64 channel (full size), 3.8 mm x 4.5 mm

- Input capacitance/charge:  $\rightarrow$  25 fF / 40 fC

- Dynamic range: 8 bit

- Power consumption: < 4 mW/ch

- Noise < 1500 e-

- Time bin width ~ 100 ps

- Channel pitch: 60 μm

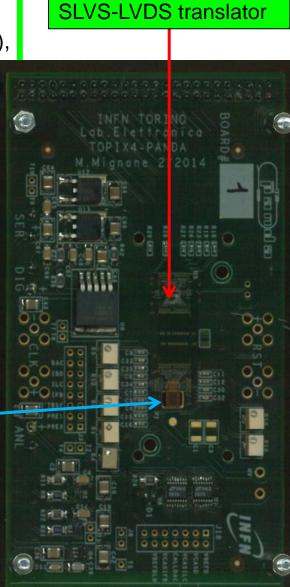

#### **Development of TofPet Project**

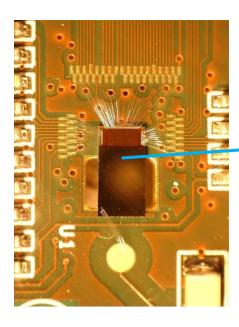

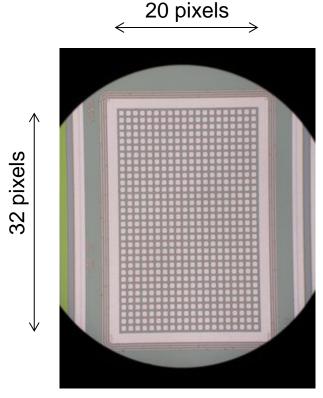

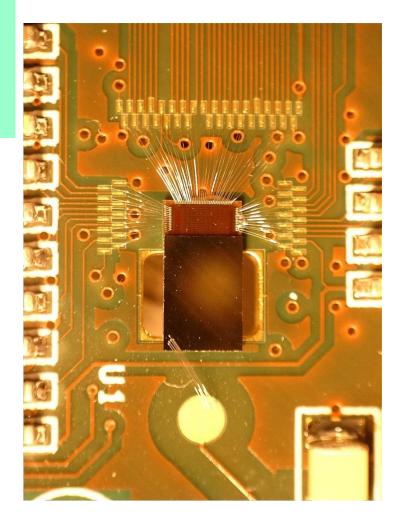

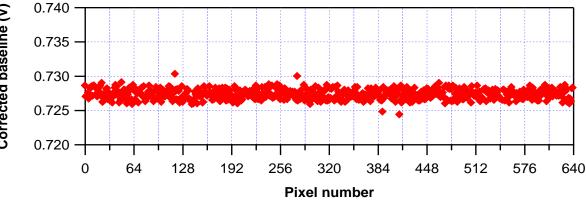

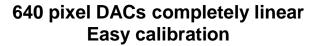

## Single chip assembly based on ToPix\_v4

- ASIC size: 3 mm x 6 mm

- 130 nm CMOS technology

- Input clock frequency: 160 MHz

- Pixel matrix: 640 cells (100μmx100μmx100μm), 2x2x128 and 2x2x32 columns

- Epitaxial silicon sensor (100 μm thick): 3.2 mm x 2 mm

- Hamming encoding and TMR pixel logic protection

- Leading and trailing edge registers with DICE -protected latche

- SEU protected EoC

- Serial data output (SDR and DDR)

- Frame based transmission

- GBT compatible SLVS I/O

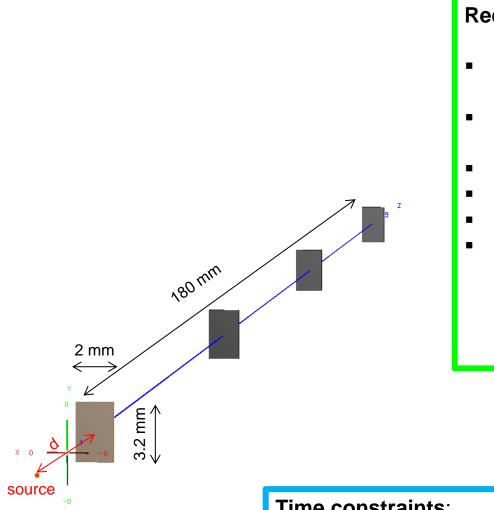

## Setup

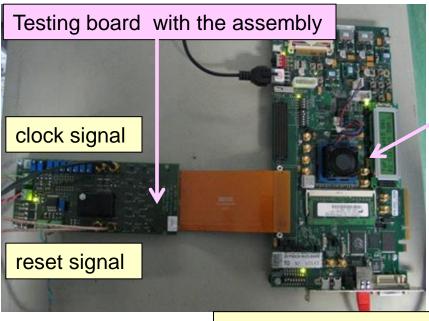

#### Network connection

Xilinx Evaluation Board equipped with a Virtex 6 FPGA

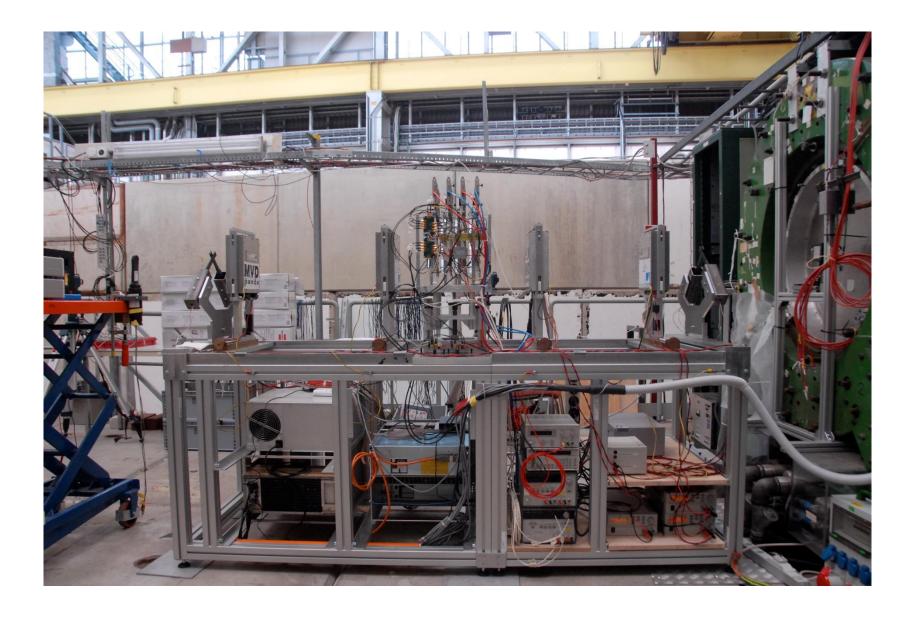

## Long table for pixel and strips

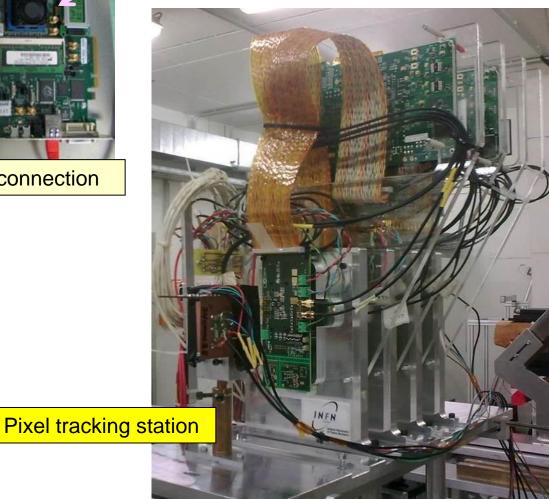

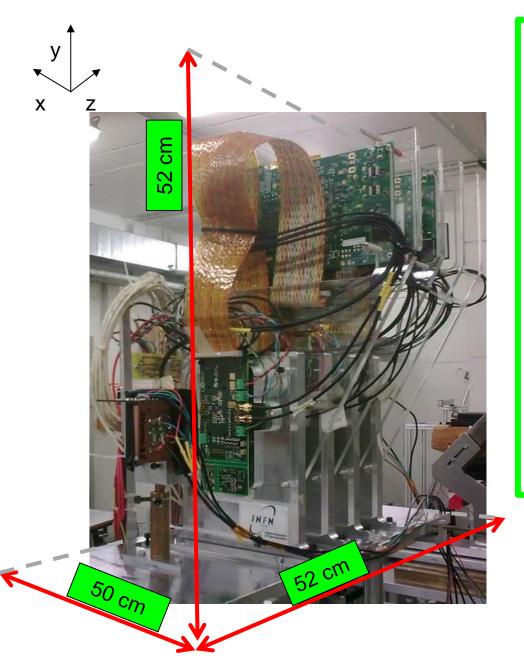

## **Pixel tracking station**

#### **Requests to Cern:**

- x-y table

- alignment support along the beam line

- Equipment to check alignment during the data taking.

- Power requirements: 220 V- 20 A

- Point to point Ethernet cables (min. 2 lines, max. length less than 30 m) between the setup and the counting room

- Space to allocate 4 power supplies and

1 crate NIM close the setup

- in the counting room , 2 workstations for daq and analysis

### **Beam parameter request**

#### **Requests to Cern:**

- Pion beam momenta: 10 GeV/c and 100-150 GeV/c (polarity does not matter)

- (Proton beam momentum: 20 GeV/c and 100 GeV/c)

- Beam size: 3 mm x 3 mm

- @ different intensities:  $10^4$ ,  $10^5$ ,  $10^6$ ,  $10^7$  /spill

- Spill length of  $\sim$  10 s, interspill time of  $\sim$  50 s

- Beam divergence: Point-like source @ d=30 cm: ~ 0.19° @ d=60 cm: ~ 0.12°

@ d=100 cm: ~ 0.08°

#### Time constraints:

- Not before of the last week of July (I mean not before July 27<sup>th</sup>)

- The present schedule foresees beam already Wednesday 22<sup>nd</sup>

# SPARES

## Single chip assembly

- Epitaxial silicon wafer by ITME (Varsaw)  $\rho_{\text{epi}} \sim 1500 \; \Omega \cdot \text{cm}$

- Pixels @ FBK (Trento) 100μm x 100μm

- Cz thinning + Bump bonding @ IZM (Berlin) Sn-Pb bumps

Bump bonding yield of the tested assemblies: ~ 99.5 %

Thin Cz layer is the ohmic contact for the sensor biasing

## **PASTA** architecture

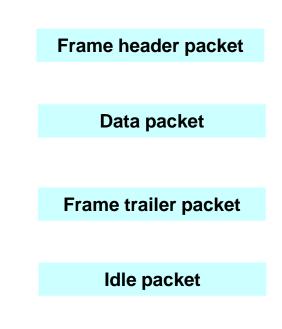

## ToPix4 data format

| 2     | 12                         | 8  | }                 | 12       |                    | 6   |

|-------|----------------------------|----|-------------------|----------|--------------------|-----|

| 01    | Chip address               | F  | С                 | Not used |                    | ECC |

| 2     | 14                         |    | 12                |          | 12                 |     |

| 11    | Pixel address              | Le | Leading edge time |          | Trailing edge time |     |

| 2     | 16                         |    | 16                |          |                    | 6   |

| 10    | # of events                |    | CRC               |          |                    | ECC |

| 2     | 38                         |    |                   |          |                    |     |

| 00    | idle code (Hex 3A55AA55AA) |    |                   |          |                    |     |

| · · · |                            |    |                   |          |                    |     |

| Output frequency             | 160, 320 Mb/s         |  |

|------------------------------|-----------------------|--|

| Time stamp counter frequency | 160, 80 MHz           |  |

| Time stamp mode              | Binary, Gray          |  |

| Idle packet                  | off, on               |  |

| Analog timeout               | off, on               |  |

| Detector type                | n-type, p-type        |  |

| SLVS current control         | 0000 (max), 1111(off) |  |

| Driver pre-emphasis          | off, on               |  |

## **Double-sided silicon strips**

$285 \,\mu\text{m}$  thickness

Readout every second strip with self trigger ASIC and ToT technique for dE/dx

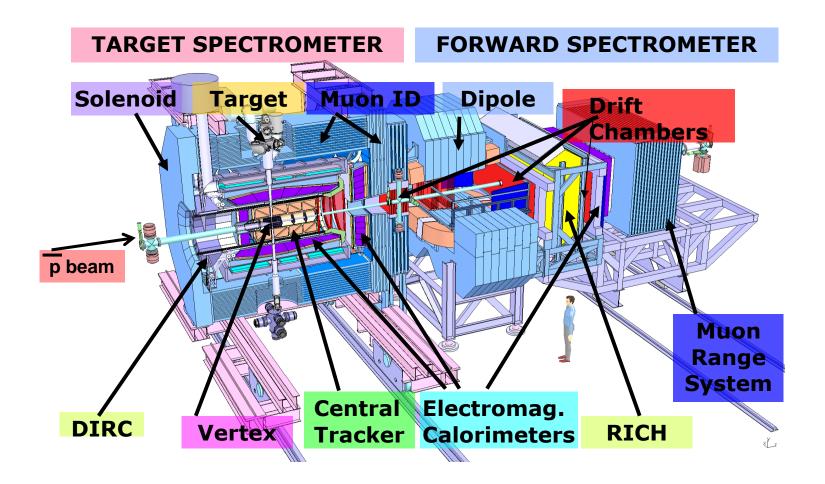

## The PANDA experiment

PANDA is a fixed target experiment with frozen hydrogen pellet and heavier nuclear targets (N, Ne, Ar...)

## ToPix

## ToPix\_v4

Measured perfomance @ 160 MHz clock

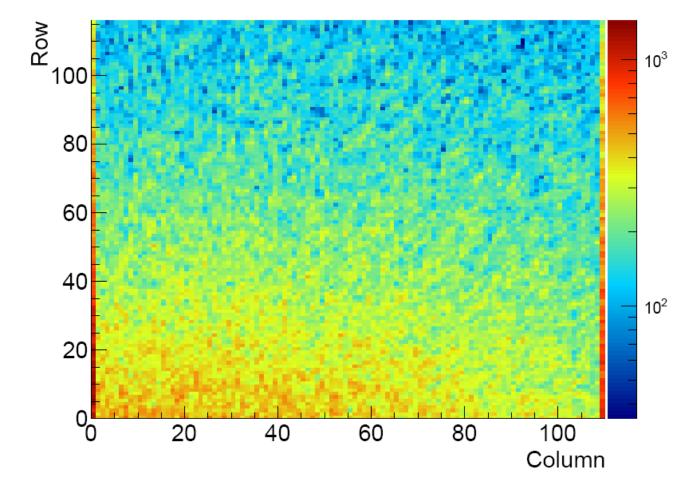

## Hit map from simulation

Hits / s - 116 Rows 110 Columns

## Strip prototypes

ProjectionY of binx=[90,217] slice\_py\_of\_cleloss2 2400 Entries Mean 288.5 138.8 RMS . 2000 900 NUIN N ADC

## Strip readout architecture

Double-sided silicon strip detector

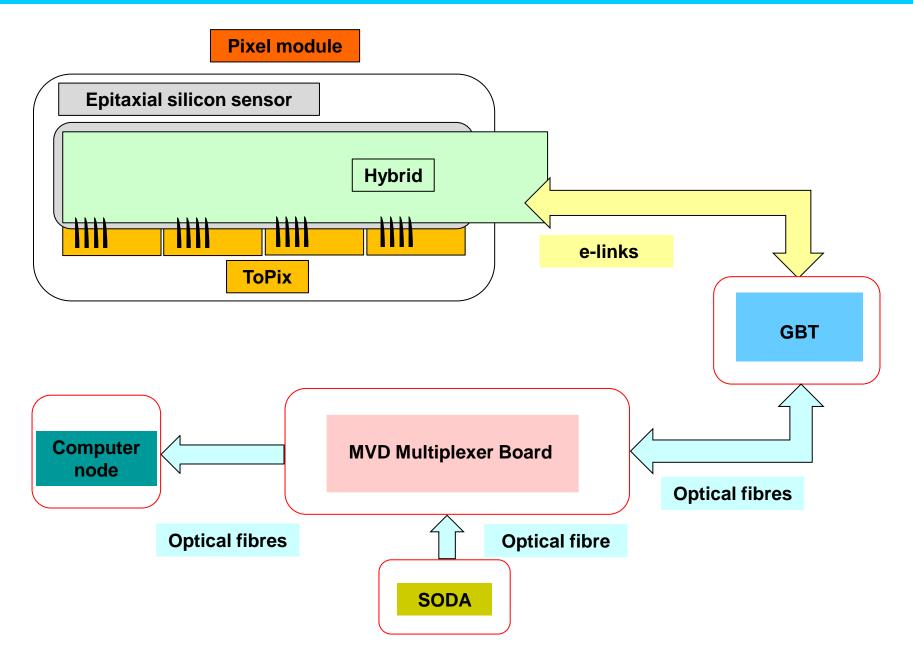

## **Pixel readout architecture**