Tests of High-Resolution Front-End Electronics for Water-Cherenkov Air Shower Detectors equipped with Cyclone® V on the Pierre Auger Test Array Zbigniew Szadkowski<sup>1</sup> IEEE Member

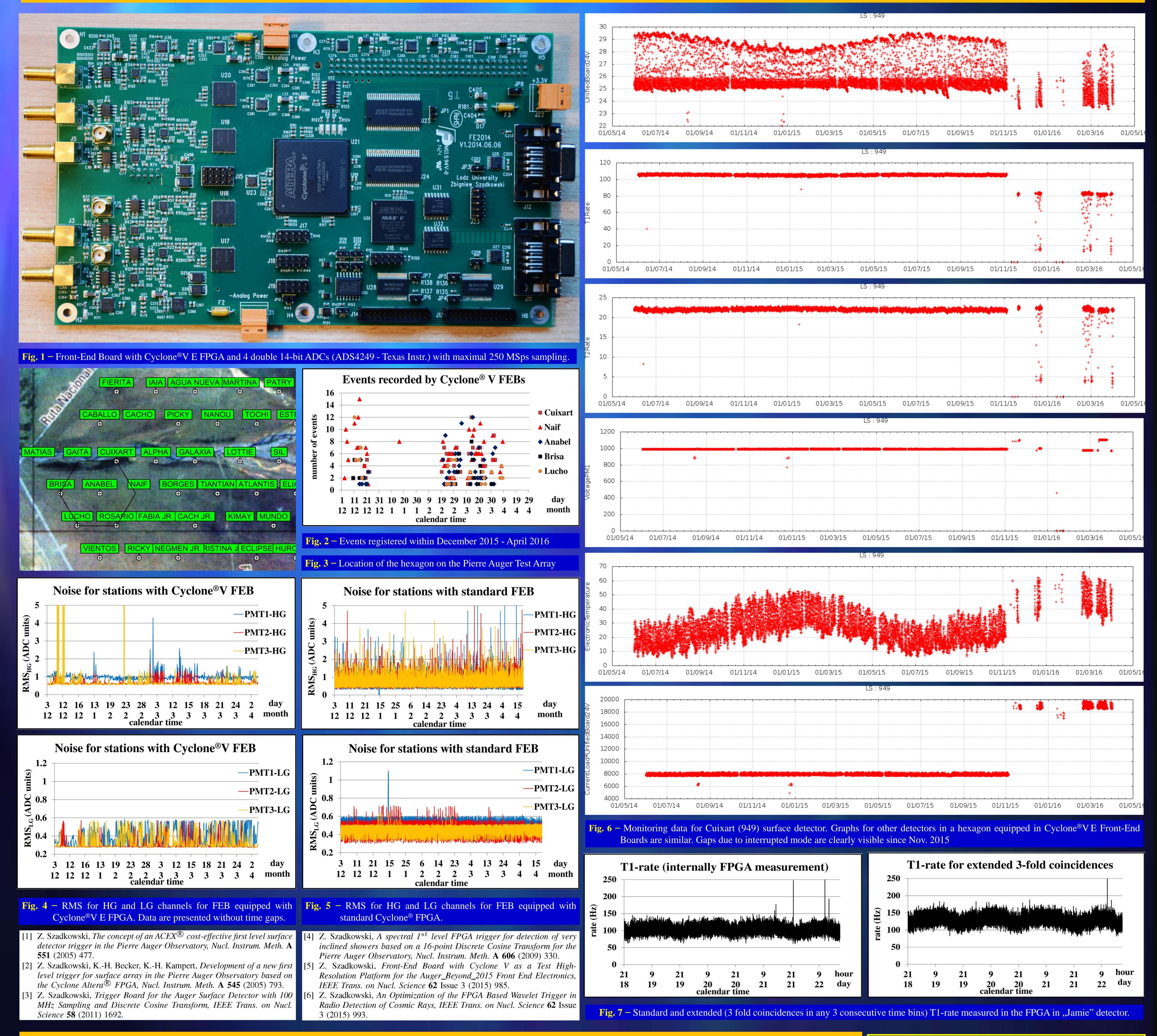

Seven Front-End Boards (FEBs) equipped with the biggest Cyclone<sup>®</sup>V E FPGA 5CEFA9F3117N, supporting 8 channels sampled up to 250 MSps @ 14-bit resolution have been successfully installed in seven surface detectors on the Pierre Auger Test Array. Surface detectors use six channels with a sampling of 120 MHz. Two remaining channels with independent sampling were tested as radio channels with the sampling of 200 MHz. The FEBs have been developed without anti-aliasing filters to keep a maximal flexibility. Communication between surface detectors and the Central Data Acquisition Station (CDAS) has been established via a standard radio link without any modification of a standard protocol. Any tuning of required processes, typically being a task of the Unified Board (UB), has been moved to the FPGA algorithm. The power consumption by the new FEBs is on a level of 18 W, but an average power solar panel output is ~10 W. An external power control circuit with a hysteresis cut off/on supplies the entire surface detector electronics to avoid a total battery discharging and its damage. Such an interrupted operation reduces significantly statistics of registered events. A second (or larger) solar panel would eliminate this inconvenience, however, we gather experiences with a lack of energy in real pampas conditions. We installed seven FEBs in the Pierre Auger Test Array in November 2015. Data acquisition is going smoothly on the T1 trigger only. The ToT (Time over Threshold) trigger has not been implemented due to instabilities.

## CONCLUSIONS

All FEBs delivered to Argentina successfully passed all tests in the field conditions. We tested standard protocols with higher sampling rates (120, 160, 200 and 240 MSps) and 12-bit resolution in a narrower window (6.4, 4.8, 3.84 and 3.2 µs instead of 19.2 µs due to higher sampling rate) and with standard and optimized thresholds. Cloudy days impaired a power budget and selected detectors had to be remotely switched off for the night to ensure that the battery did not discharge to a level menacing of a total damage. We had to add a remote temporary digital power disconnection (supplied from the same power line) to allow independent FPGA reprogramming from the standard configuration chip (a theoretically simultaneous turning on the power for UB and FEB practically generates a race hazard which sometimes leaves the FPGA not programmed). Two surface detectors could not provide a communication with the CDAS (Gaita) or could not provide ADC data (Rosario). Nevertheless, the new Front-End Boards with Cyclone<sup>®</sup>V E FPGA smoothly provided valuable data for 120 MHz sampling and fully confirmed their reliability in the field conditions.

This work was supported by the National Science Centre (Poland) under NCN Grant No. 2013/08/M/ST9/00322