# **FPGA-based Image Analyser for Calibration of Stereo Vision Rigs**

A. Mielczarek, D. Makowski, P. Perek, A. Napieralski, P. Sztoch

## INTRODUCTION

The stereoscopic image recording is relatively new ground of the modern cinematography. Consumer-grade stereoscopic cameras are not suitable for professional productions, hence the video acquisition is usually done by a set-up of two conventional cameras mounted on the camera rig. The aim of the rig is to support the cameras and ensure constant mechanical relationship between them.

Including the lens setting, operator of the stereoscopic rig has to manipulate at least 8 variables to properly align and tune the images from both cameras. Using the legacy equipment the initial rig calibration can easily consume several hours. If the calibration is done wrongly or is lost during shooting, the whole collected material will require costly post-production, or worse, it will have to be captured again.

## USE CASE

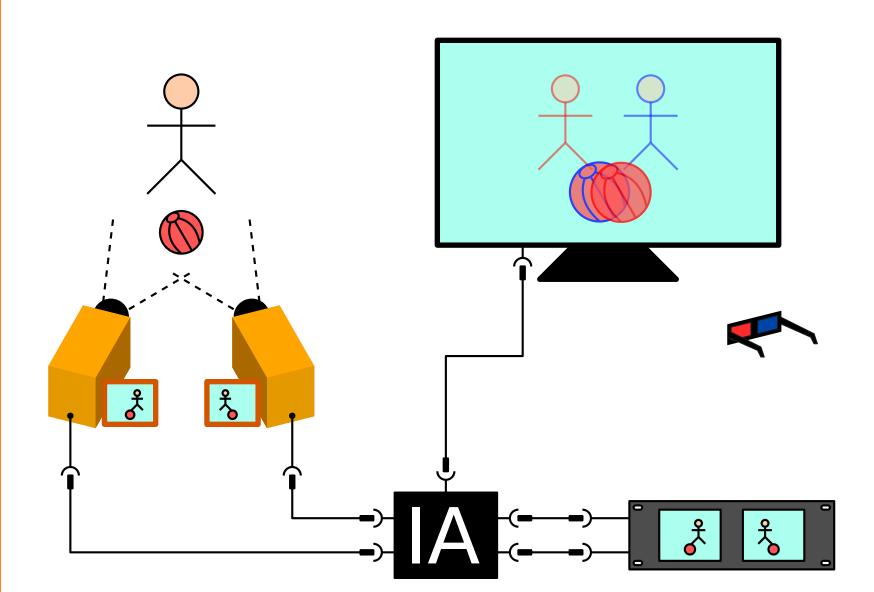

The Image Analyser is an integrated device which compose the images from the cameras, facilitating rig calibration. It connects to camera and provides analysed image as well as pass-through signals.

### FEATURES

#### Implemented analyses:

- **5**0/50

- diference

- monochrome anaglyph

- colour anaglyph

- side-by-side

- over-and-under

- line-by-line

- left/right camera preview

- colour balance equalization between images

#### Additional features:

- local control using keypad and LCD menu

- remote control over the Ethernet

- current setting is presented in the output image

- optional horizontal mirroring of the images

- powered from mains or regular camera battery

- adjustable colour of the LCD display

## PHYSICAL ARCHITECTURE

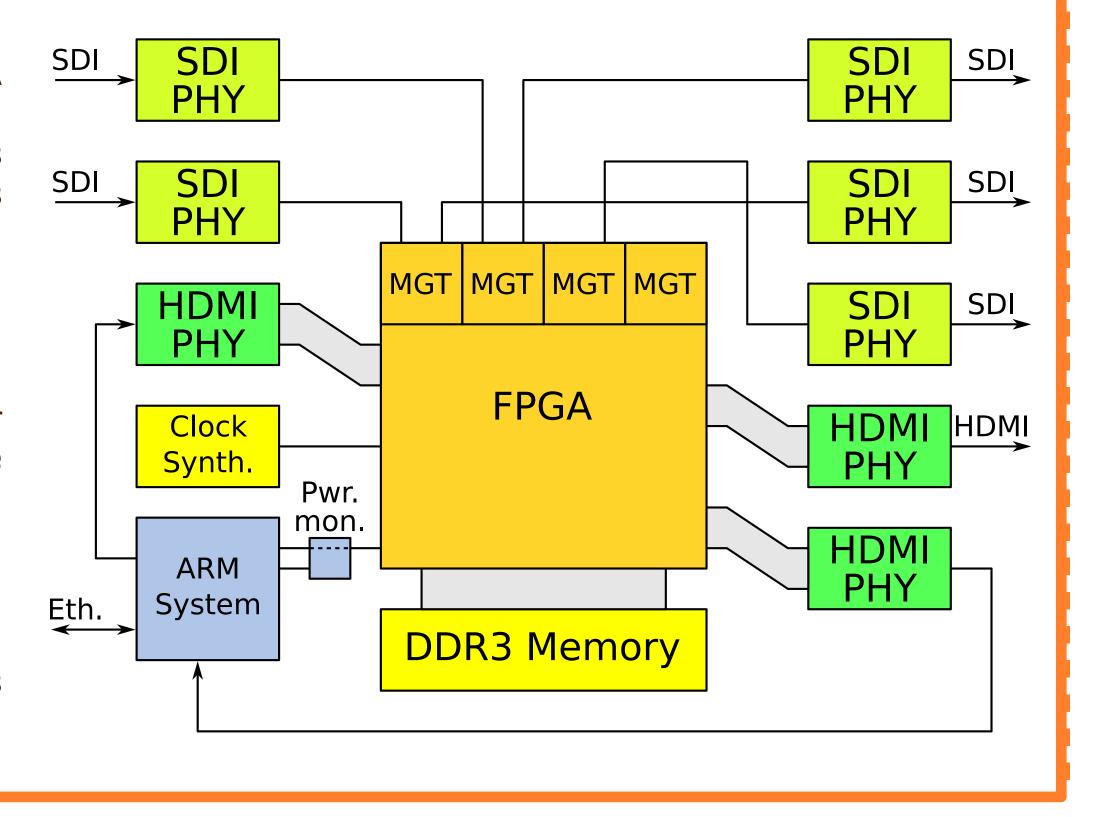

The Image Analyser was designed as a regular 1U 19" rack module. The device consists of FPGA board, I/O modules, ARM-based single board computer and power supply. The selected FPGA is XC7K355T – a modern Xilinx Kintex-7 IC. It is responsible for almost all of the video processing.

The FPGA cooperates with GateWorks Ventana GW5400 computer. The module contains quadcore ARM Cortex-A9 processor running at 1 GHz. It is used for control of the device as well as for streaming the analyser output video through the wired Ethernet.

The unit also contains simple power supervision board based on ARM Cortex-M4 microcontroller. This module monitors the power supplies, switches between them, drives front panel LEDs and controls the LCD back-light.

## EVALUATION

The currently implemented set of features is mainly focused on alignment of the optical tract of the camera rig. The analyser was hence tested on a movie set, being used for rig calibration.

## FIRMWARE DETAILS

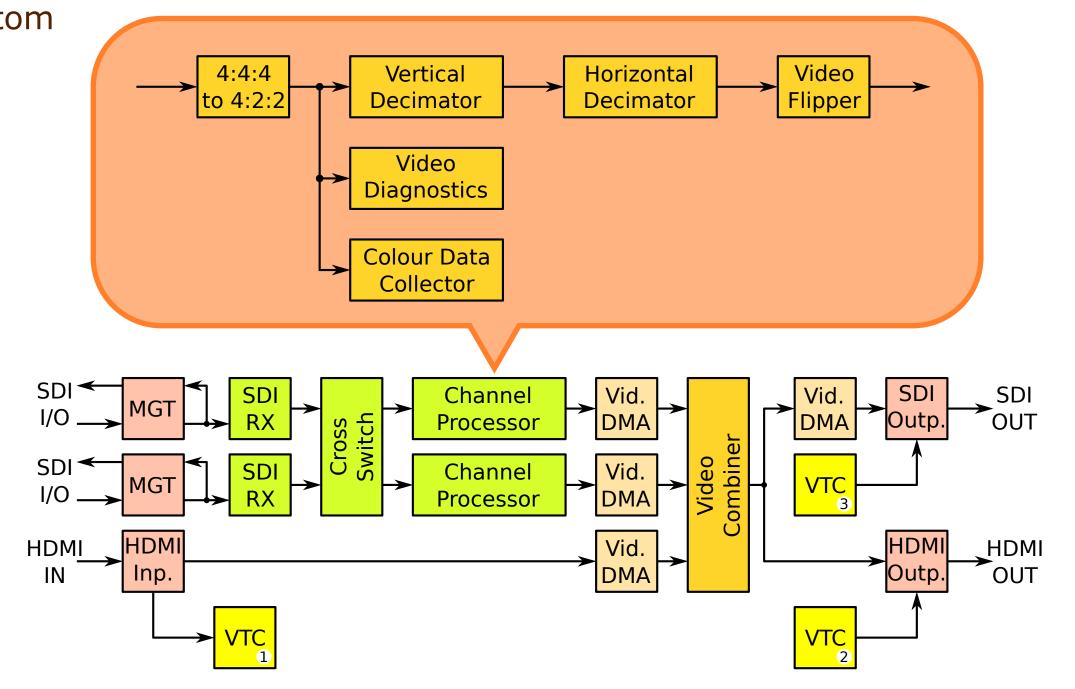

The FPGA firmware of the Image Analyser is composed of two coupled systems: the control system and the video processing path. The control system is governed by a Microblaze processor. It controls over 35 slaves through the AXI bus. The video processing sub-system is custom

128-bit AXI4 Lite switch #2

32-bit AXI4 Lite switch #2

32-bit AXI4 Lite switch #2

32-bit AXI4 Lite switch #3

10 l/O peripherals

tailored to implement the required functionality.

## CONCLUSION

Image Analyser is a stereoscopic rig calibration device realised in the industry standard 19" form factor. It is based on tandem of bleeding-edge Kintex-7 FPGA and ARM single board computer. It helps reduce the righ calibration time using several different image comparison methods. It builds a synchronized 3D video stream for 3D HDMI monitors.

The Image Analyser is still under development. It is planned that in the future the device should perform scene depth analysis. Each functionality is tested with the FINN movie company from Łódź, which ordered the solution. There, the analyser is routinely used for the calibration of the rig.

The Image Analyser was first publicly demonstrated during the MIXDES 2015 international conference held in Toruń, Poland.