## A High Frame Rate Test System for the HEPS-BPIX based on NI-sbRIO Board

Jingzi Gu, Jie Zhang, Zhe Ning, Wei Wei, Zhenjie Li, Xiaoshan Jiang, Lei Fan, Wei Shen, Xiaolu Ji, Allan K. Lan, Yunpeng Lu, Qun Ouyang, Peng Liu, Kejun Zhu, and Zheng Wang The State Key Laboratory of Particle Detection and Electronics, Institute of High Energy Physics, CAS; E-mail: gujz@ihep.ac.cn

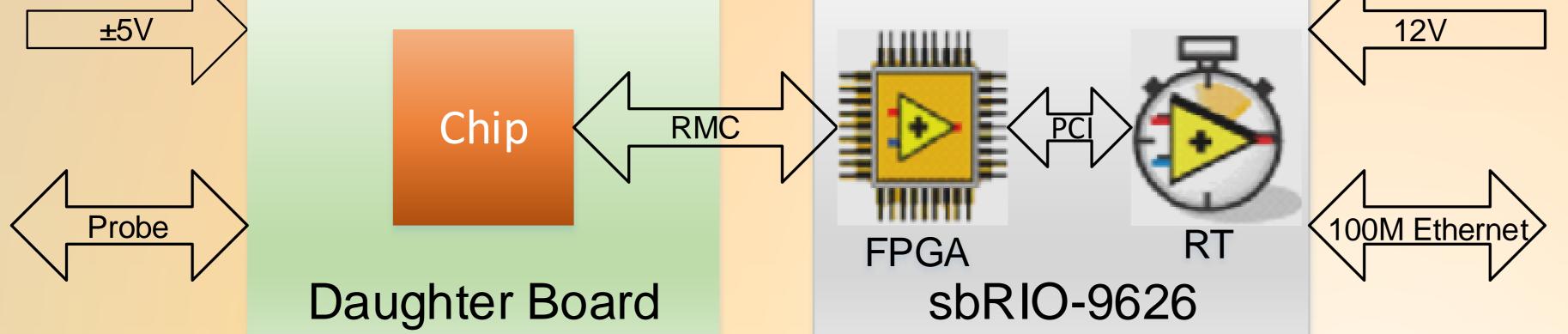

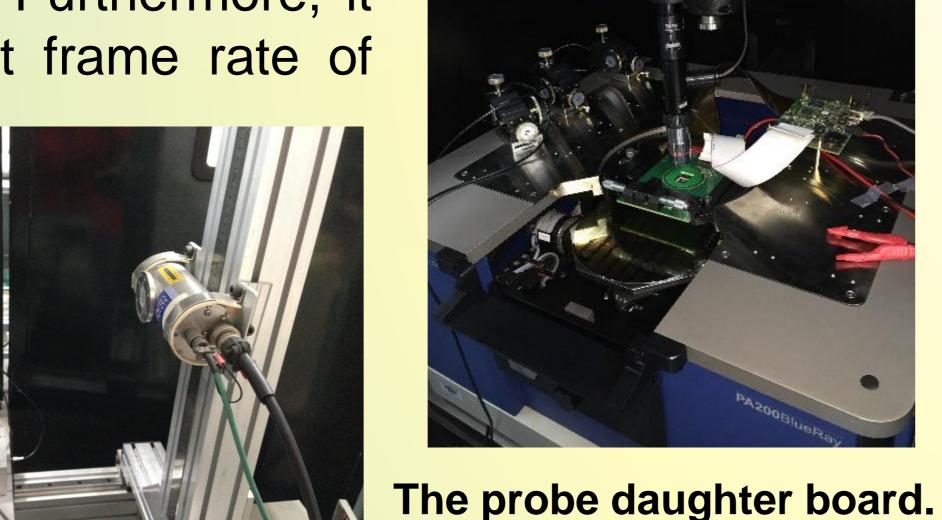

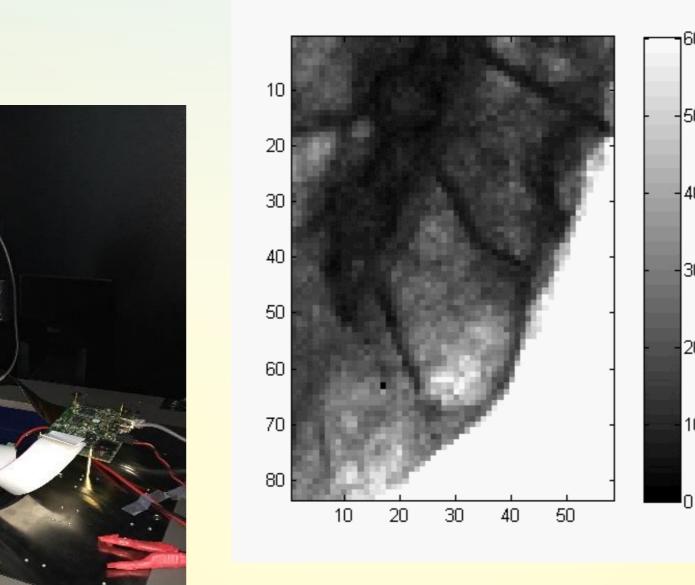

HEPS-BPIX is a hybrid silicon pixel detector designed for the High Energy Photon Source (HEPS). It contains an array of  $104 \times 72$  pixels while each pixel is of  $150\mu m \times 150\mu m$  size. HEPS-BPIX works in the single-photon-counting mode, and every pixel has a counter of 20 bits. The frame rate of the detector can be as high as 1.2 KHz. Aiming to calibrate and test HEPS-BPIX, as well as to make the detector available in the market sooner, we have designed a test system which consists of a pixel detector, a daughter board, an National Instruments (NI) single-board RIO 9626(sbRIO) and a host computer.

Main goal of the test system: 1.2KHz frame rate Advantage: Fast prototype development

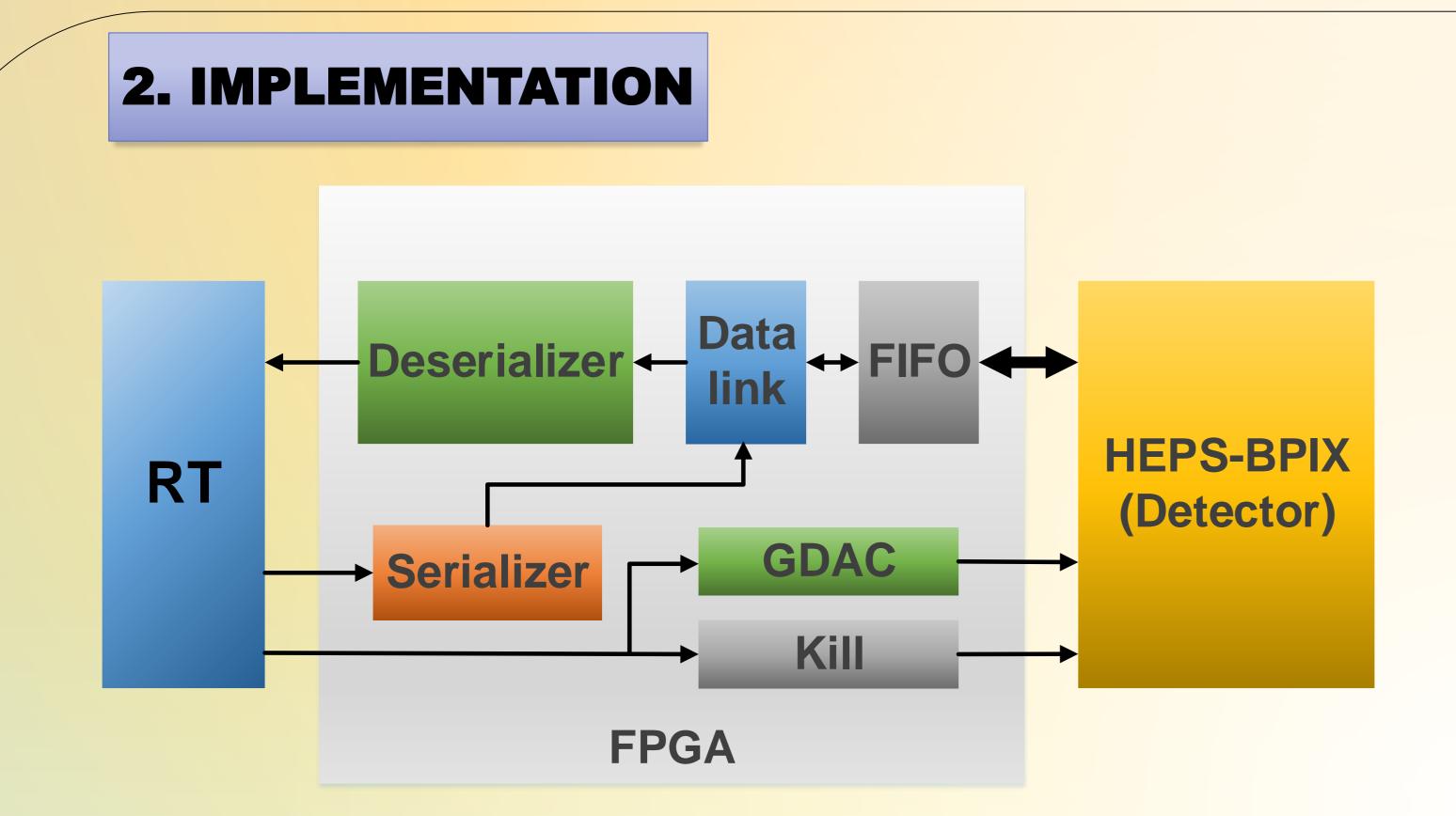

The FPGA deserializes the data from the detector and sends them to the RT processor for further processing. Moreover, the configuration data for the pixel array from the RT processor are serialized by the FPGA. GDAC and Kill are modules dealing with the other configuration data for the detector. The FPGA also provides the clock for HEPS-BPIX. The RT processor utilizes the DRAM on the sbRIO board as data cache as well as transfers the data between the PCI bus and the Ethernet to realize the frame rate of 1.2KHz. The sbRIO board can store more than 12000 frames, which is enough for the practical application.

## Simple block diagram of the FPGA firmware.

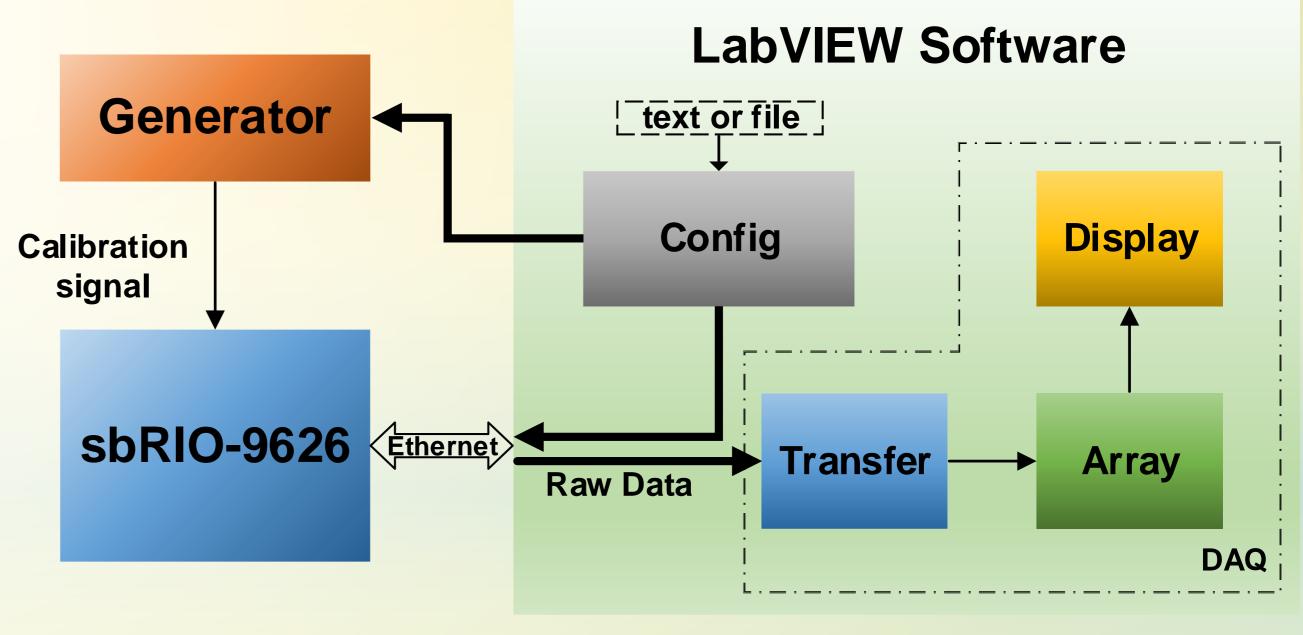

The raw data from the sbRIO board are transformed to single-frame files by the Transfer module. The Array module processes the single-frame file and make it a  $104 \times 72$  array which can be displayed by the Display module to implement the real-time imaging. The Config module can configure the test system as well as control the signal generator for S-curves collection.

## The structure of the upper-computer software.

The test system can implement the debugging and calibration of the detector. Also, it has the functions of data acquisition and real-time imaging. Furthermore, it reaches the target frame rate of 1.2KHz.

Test environment.

A fishtail: image taken by a Fe55 X-ray source. A rolling fan with four blades was placed before the test system to stop the beam light. The rotation frequency of the fan is 50Hz and the period of every blade is 6 frames, which proves the frame rate of the system to be 1.2kHz. Phase 1, 3 and 5 of the 6 frames in a period are shown in the figure.