### Level-1 Track Trigger for CMS in HL-LHC

Sergo Jindariani (Fermilab)

Mark Pesaresi (Imperial College) on behalf of the CMS collaboration

Vienna Conference on Instrumentation, February 2016

## Outline

- Why Level-1 (L1) tracking trigger?

- Challenges of implementing L1 track trigger at LHC

- Overview of current R&D efforts.

- Roadmap

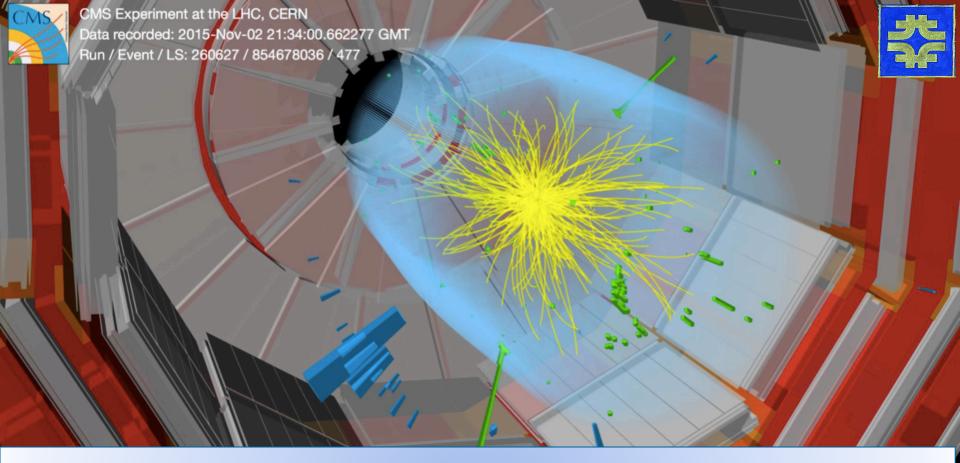

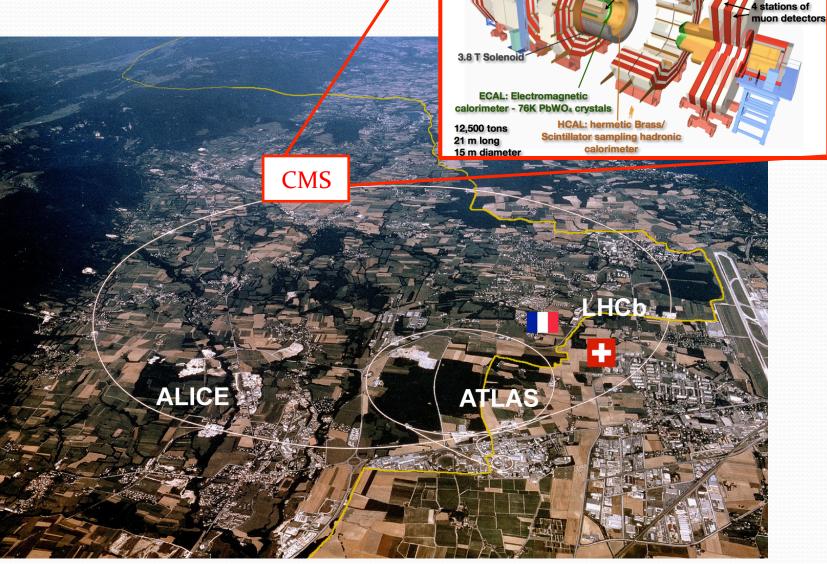

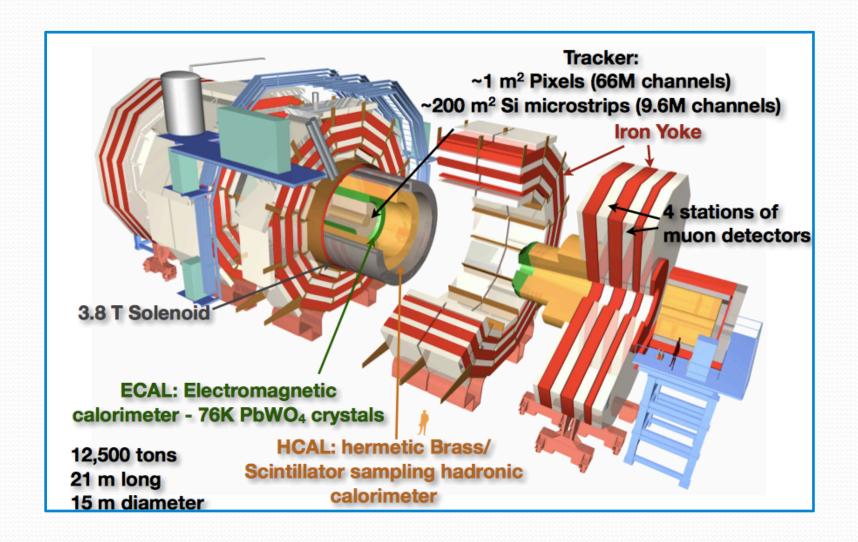

# LHC and CMS

Tracker:

~1 m² Pixels (66M channels)

-200 m² Si microstrips (9.6M channels)

Iron Yoke

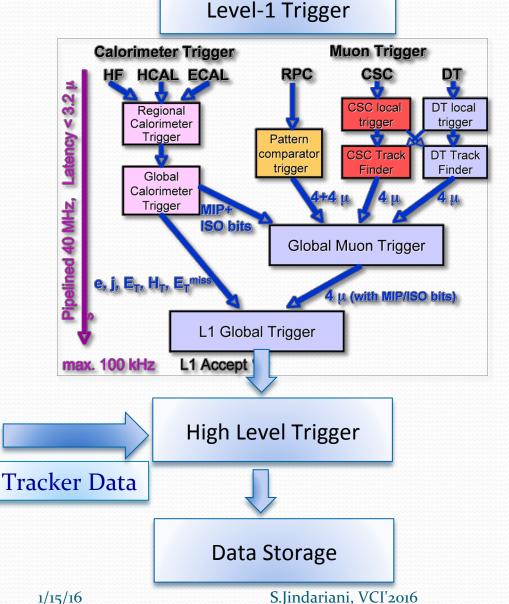

## Current CMS trigger

40 MHZ

100 kHZ

~1 kHZ

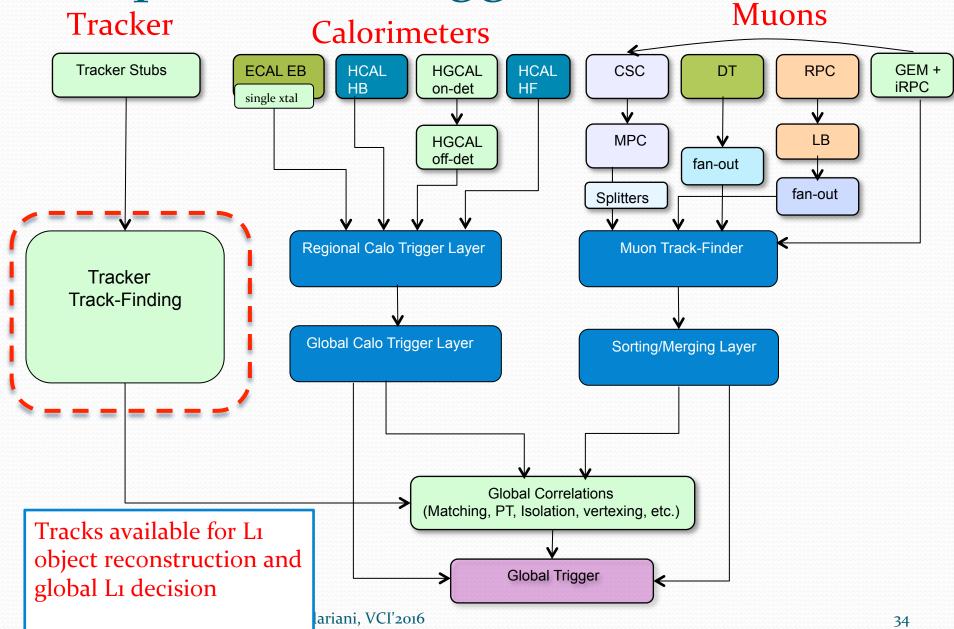

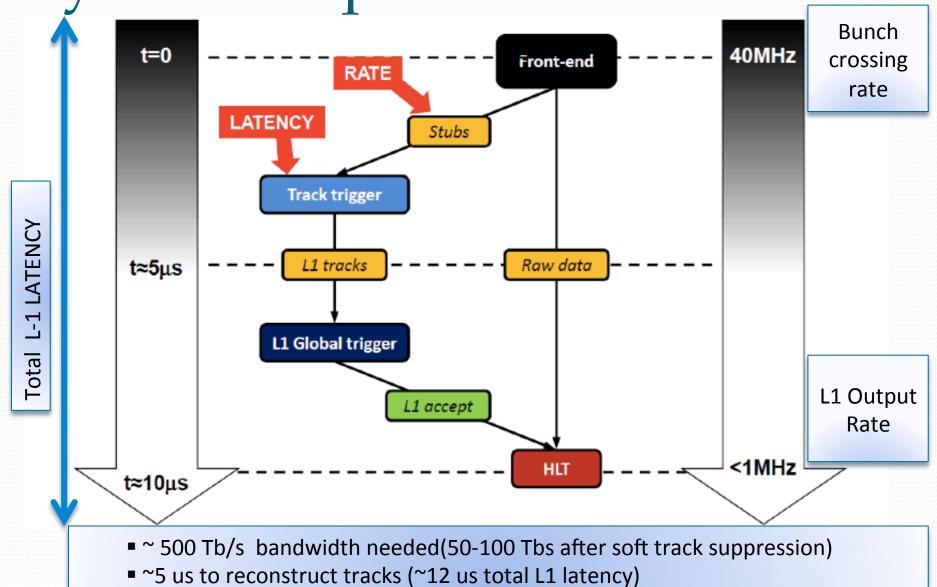

- L1 trigger system reduces event rate from 40 MHz down to 100 kHz

- Until HL-LHC, Level-1 decision is based solely on calorimeter and muon system information

- Tracker data available at the HLT level only

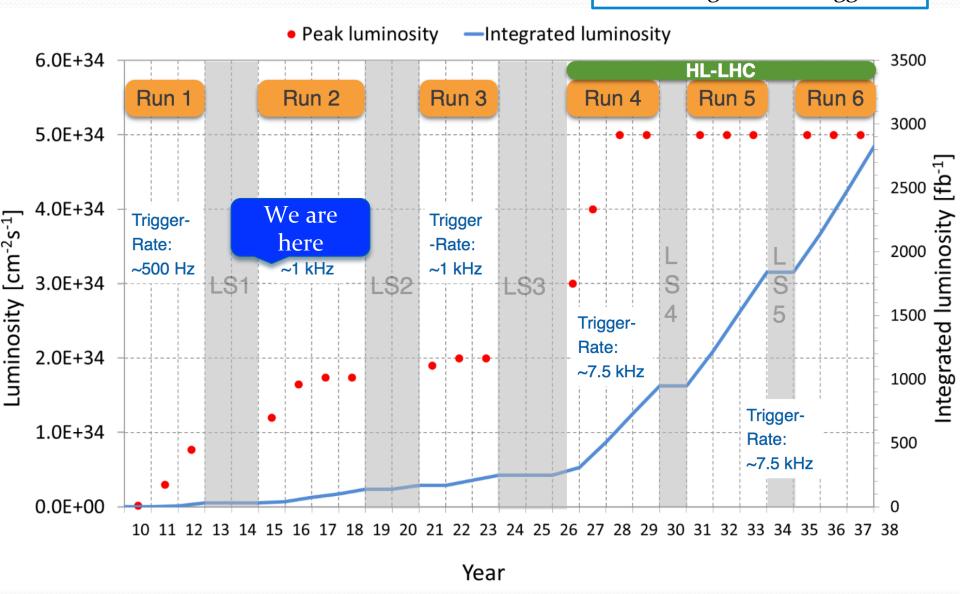

## LHC timeline

Trigger rates are shown for the High-Level Trigger

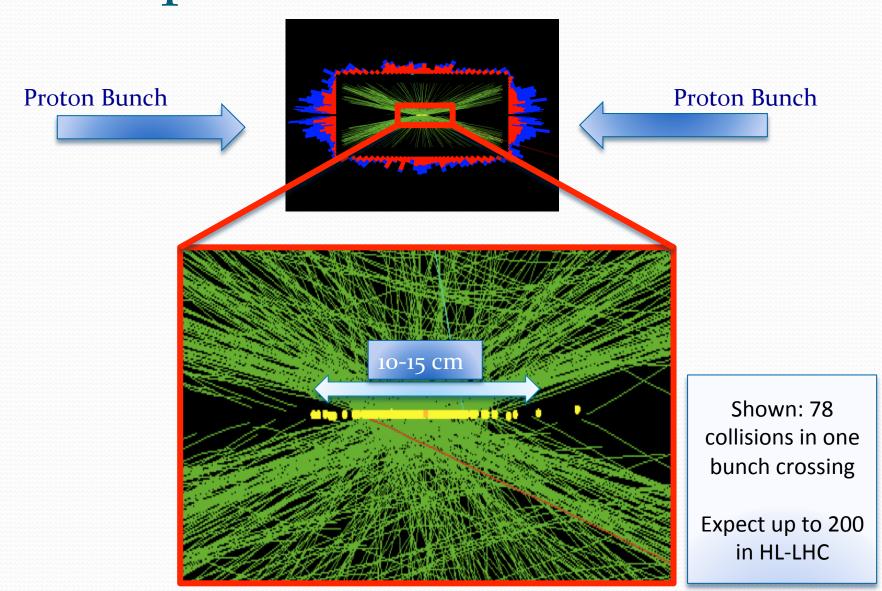

# Pile-up

# Tracking in L1 trigger:

#### Tracking is highly effective for pileup mitigation

- Electron/Photons

- Extra measurement Rate Reduction

- Isolation

- Muons

- Excellent Pt Resolution

- Isolation

- Tau TriggersMultiprong

- Separation of Interactions

- Hadronic/Multi-object Triggers

- Track-based Missing Energy

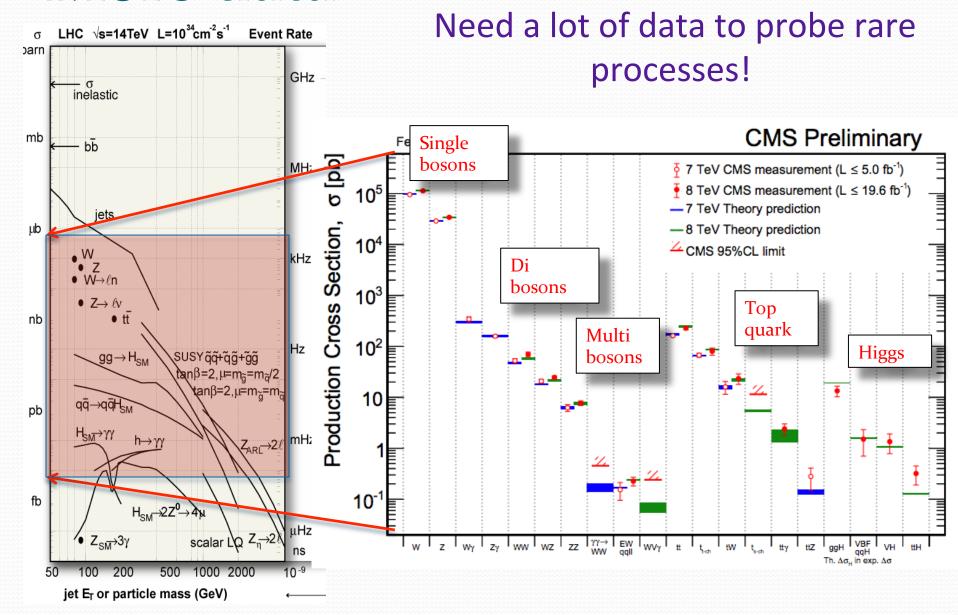

# Scale of the problem

#### Sheer amount of data in collisions:

- Bunch Spacing = 25 ns i.e. 40 million bunch crossings per second

- Up to 200 interactions per bunch crossings

- Several particles per interaction

- = > Reconstruct billions of particles per second

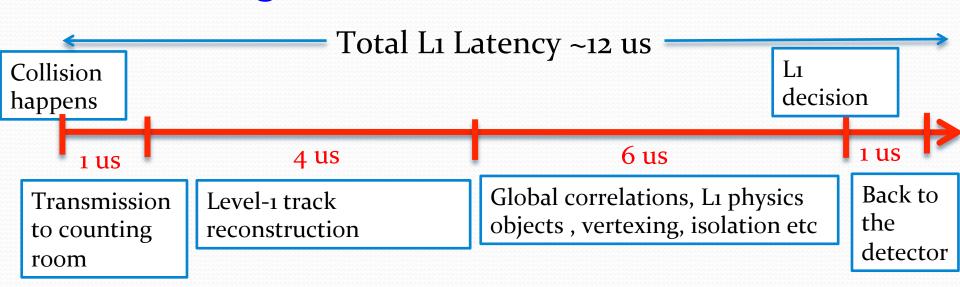

## Challenge 1:

Up to 1 Pb/s bandwidth needed (50-100 Tbs after soft track suppression)

# Scale of the problem

## Challenge 2:

Tracks have to be reconstructed in < 5 us

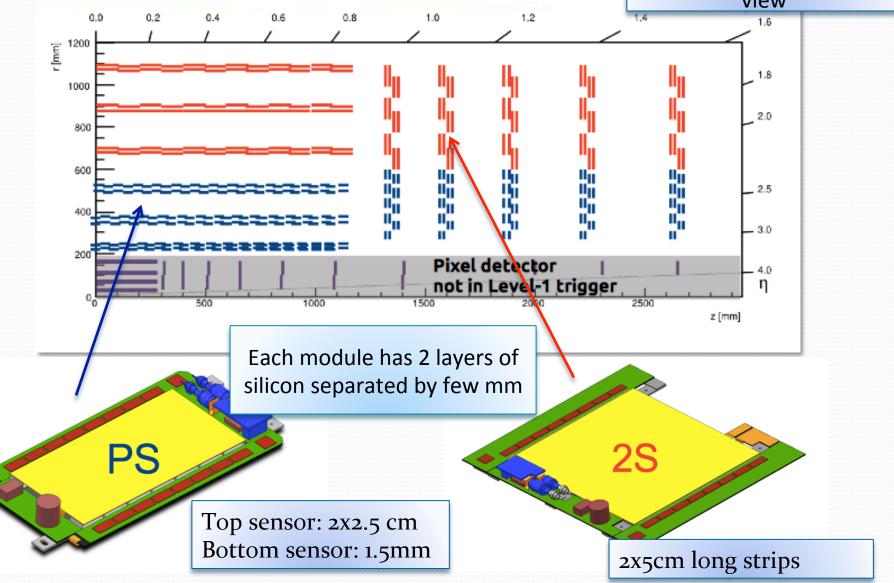

## New CMS Tracker

More on the tracker in the talks by Giacomo SGUAZZONI and Axel KONIG (Wednesday)

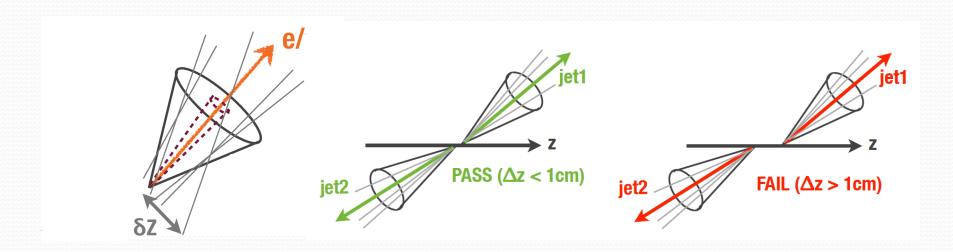

#### Tracker design is from the ground up done for triggering

- Stub = pair of clusters in the 2 sensors of a module within a predefined strips window (enabling pT cut at the module level).

- Pass/Fail window is programmable (2 GeV default cut)

- Stubs drastically reduce (by a factor 10-20) the amount of data to extract from the tracker @40MHz

- Stubs allow L1 tracking possibility

- ~15000 modules transmitting

- p<sub>T</sub>-stubs to L1 trigger @ 40 MHz

- Full tracker readout @ 750 kHz

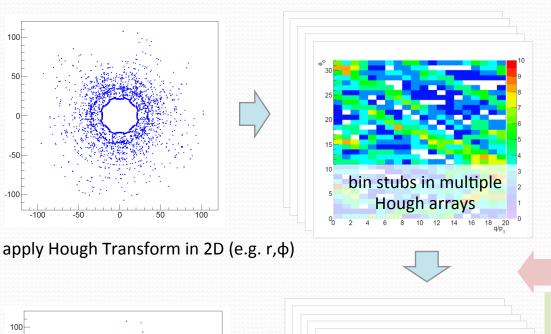

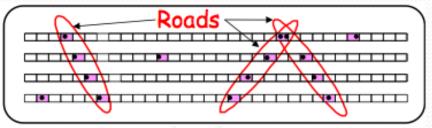

#### General Strategy Partition detector into trigger towers Data transfer Associative Memory (AM) **Hough Transformation** Tracklet-based Data Fit filtered hits in FPGA to formatting determine track $\Delta t_1$ parameters Pattern Recognition $\Delta t_2$ Total **Track** Fitting and processing $\Delta t_3$ duplicate Latency $\Delta t$ ? removal Tracks out

# Approaches

Need to handle the high occupancy and combinatorics that result from there (faster than linear scaling). Done using:

- data partitioning (tracklets)

- Hough transform (TMT)

- Associative Memory (AM+FPGA)

#### Hardware:

<u>FPGA-only</u> (Tracklets and TMT): perform both pattern recognition and track fitting in FPGA:

- Can be done using conventional hardware (FPGA)

- challenging to fit within FPGA resources and the latency budget

<u>Associative Memory (AM) based:</u> Use AM for pattern recognition followed by track fit performed in an FPGA.

Proven: CDF SVT and ATLAS FTK (in progress), but not at L1 Requires custom ASIC

1/15/16 S.Jindariani, VCI'2016

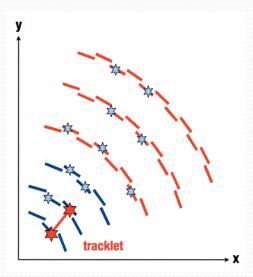

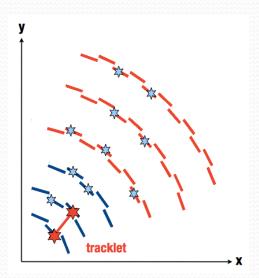

# Tracklet Based Approach

# Tracklet based approach

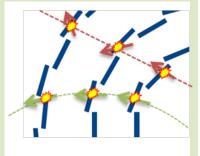

#### Seeding:

- Form tracklets from pairs of stub in adjacent layers

- Use beamspot constraints

- Tracklet must be consistent with Pt and z0 requirements

# Tracklet based approach

#### Seeding:

- Form tracklets from pairs of stub in adjacent layers

- Use beamspot constraints

- Tracklet must be consistent with Pt and z0 requirements

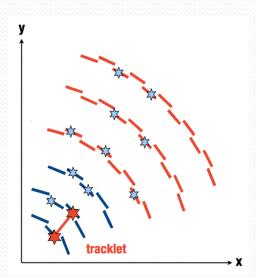

#### **Projecting:**

- Project to other layers and disks

- search window derived from residuals b/w projected tracks and stubs

- In-out & Out-in

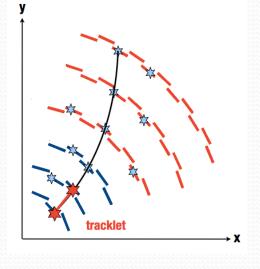

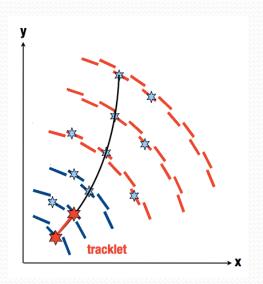

# Tracklet based approach

#### Seeding:

- Form tracklets from pairs of stub in adjacent layers

- Use beamspot constraints

- Tracklet must be consistent with Pt and z0 requirements

#### **Projecting:**

- Project to other layers and disks

- search window derived from residuals b/w projected tracks and stubs

- In-out & Out-in

#### **Fitting**

linearized track fit

#### **Duplicate Removal:**

Based on number of shared stubs

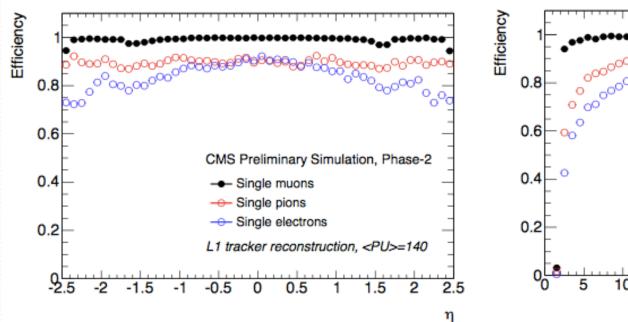

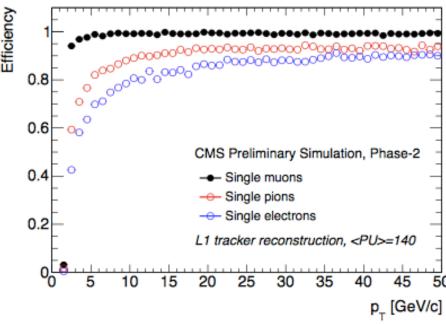

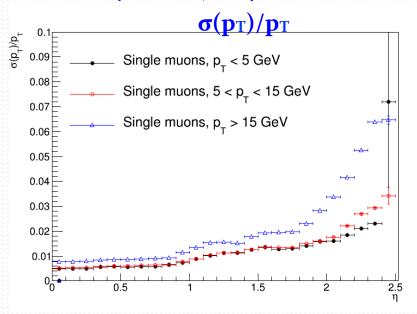

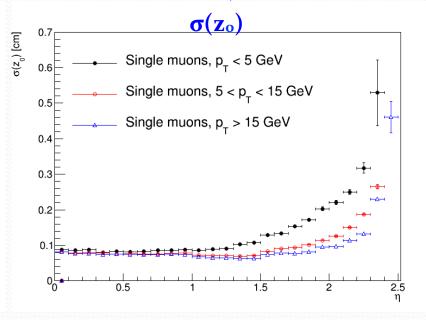

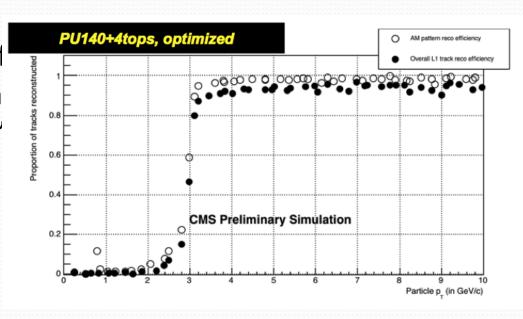

## Performance in Simulation

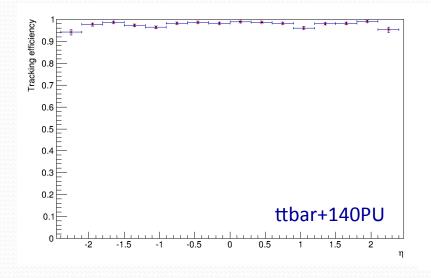

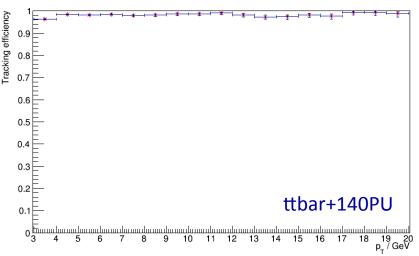

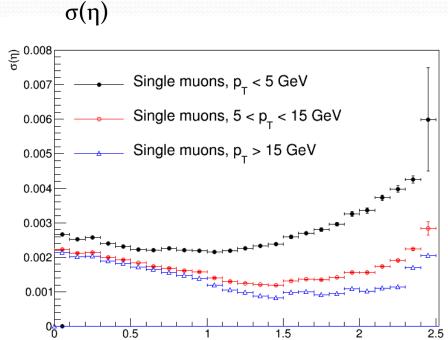

- Muons: Sharp turn-on at 2 GeV & high efficiency across all η. Eff ~99%

- Pions: Somewhat lower efficiency due to higher interaction rate. Eff~90%

- Electrons: Slower turn-on curve, efficiency reduced from bremsstrahlung. Eff~90%.

Similar performance is expected in other approaches

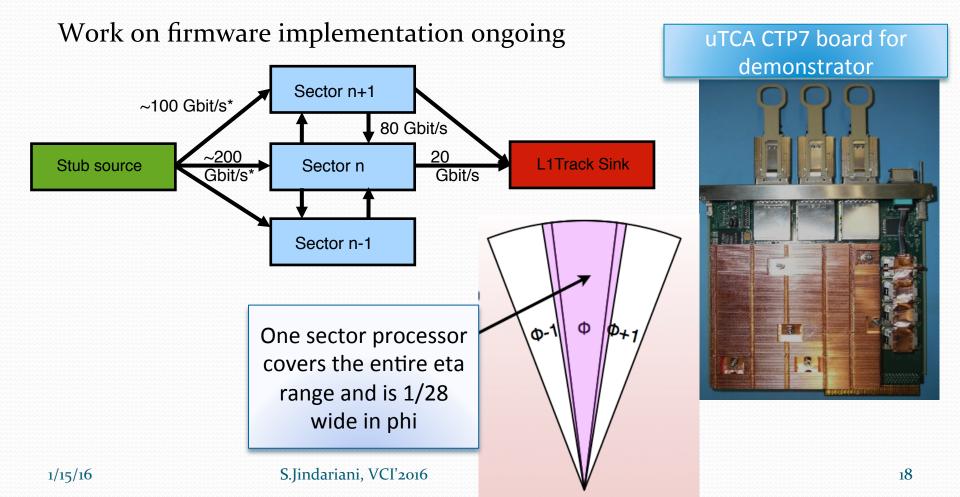

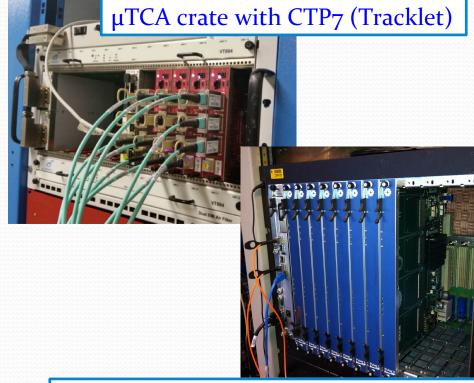

## Tracklets in Hardware

Demonstration in hardware is needed to show that the approach can work within latency budget

Xilinx Virtex-7 based board CTP7 is being used for demonstration

# Fully Time Multiplexed Based Approach

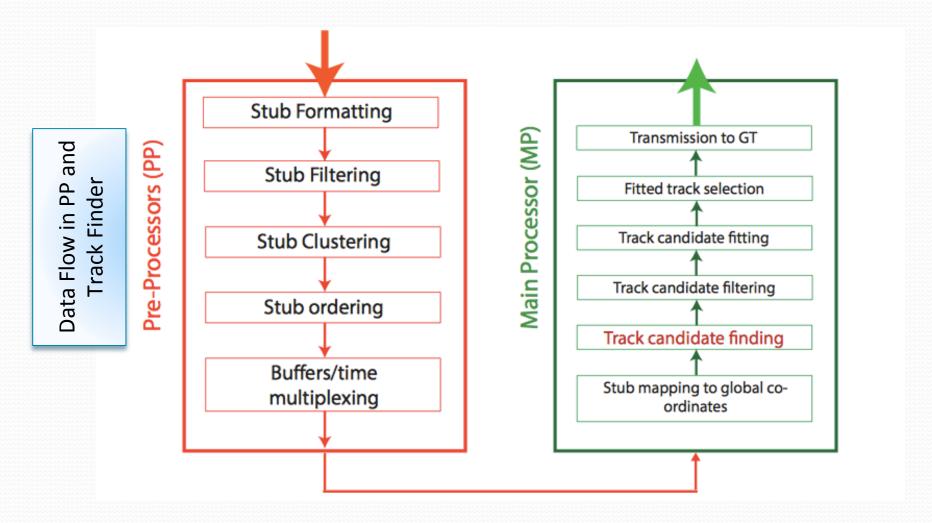

regional readout boards

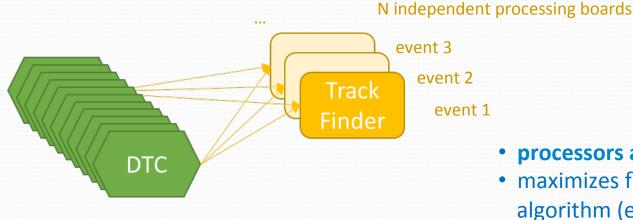

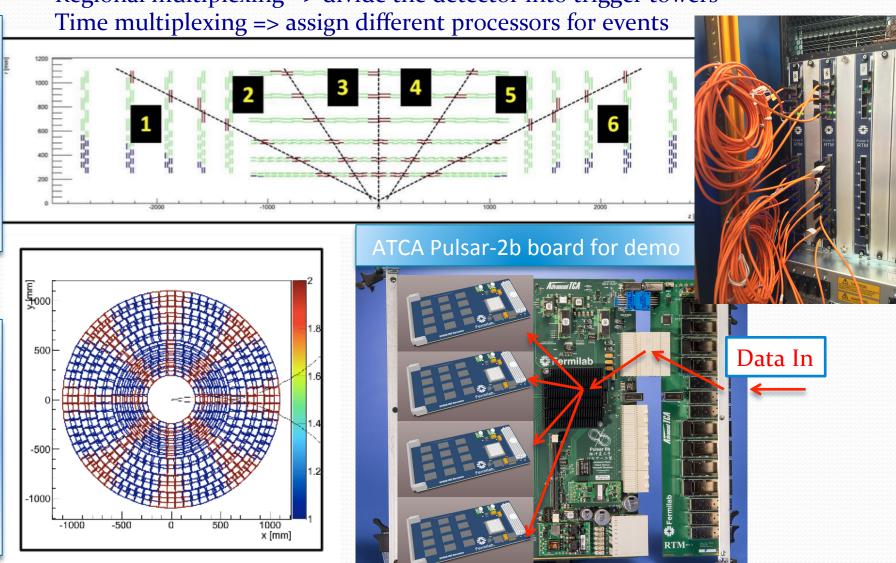

#### Time multiplexed architecture

- HLT-like architecture event data flows to a single processing node

- now implemented in CMS Level 1 Calorimeter Trigger

- allows for a simple, scalable slice demonstration system

- processors are independent in time

- maximizes flexibility to make changes to algorithm (even during operation!)

- efficient use of FPGA resources

- minimizes hardware regions

- regional data sharing avoided

1/15/16 S.Jindariani, VCI'2016 20

- µTCA card built for CMS upgrade

L1 calorimeter trigger

- Contains a Virtex-7 XC7VX690T

- 72 input/ 72 output optical links that operate up to 12.5 Gbps

- Total bandwidth > 0.9 Tbps

- maximum number of links into the L1 Track Finder (72) imposes limit on DTCs connected

- need to divide tracker into at least five regions, e.g. in  $\eta$  ( $\Delta \eta \sim 1.0$ )

- flexibility to choose 24-36x time multiplexing

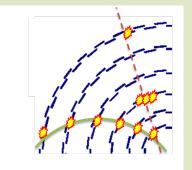

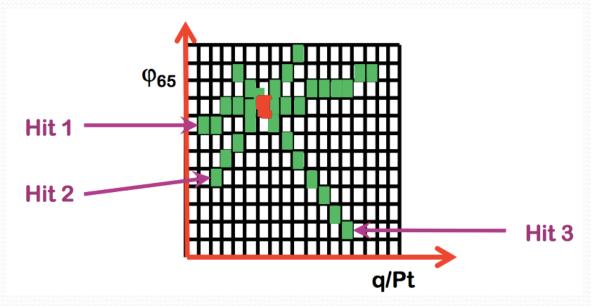

two step track finding approach based on coarse 2D Hough Transforms

- orders stubs into valid track candidates

- · binning of stubs according to projections

~20x20 typical array size required

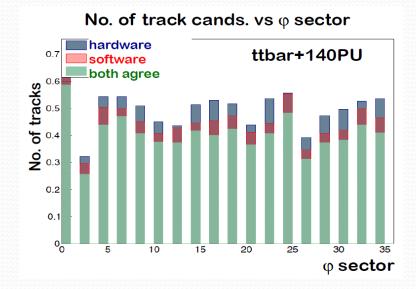

36 φ segments, each an independent HT

#### apply track criteria to accept

bins with stubs that have compatible local bend

stubs from selected bins form track candidates for further processing

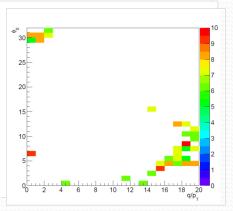

- injecting stubs from "ttbar+140PU" into hardware & comparing kinematic distributions of tracks found with those predicted by software

- fairly good agreement so far with remaining discrepancies to be debugged

- simulated performance indicates high efficiency for track finding above 3 GeV/c

1/15/16 S.Jindariani, VCI'2016

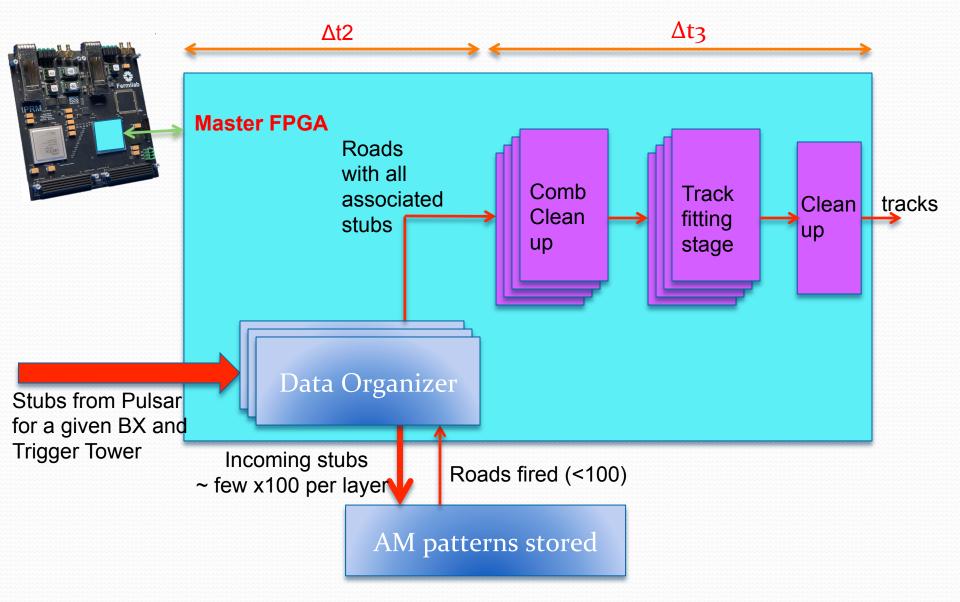

# AM+FPGA Based Approach

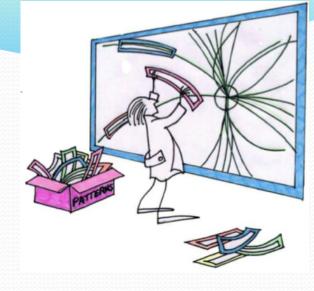

# Associative Memory

Pattern Recognition Associative Memory = content addressable memory (CAM) cells + majority logic (ML)

#### Massive parallel processing to tackle the intrinsically complex combinatorics

- o Avoid the typical power law dependence of execution time on occupancy

- Solving the pattern recognition in times roughly proportional to the number of hits

CMS L1 track trigger applications require high pattern density and high operational frequency while managing power needs

# Sectors and processors

S.Jindariani, VCI'2016

Regional multiplexing => divide the detector into trigger towers

26

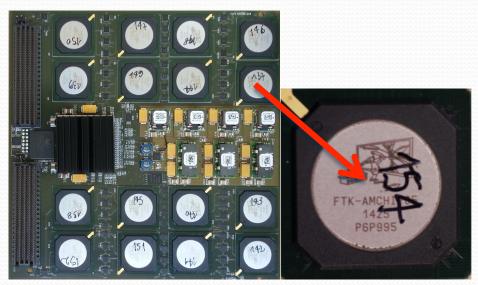

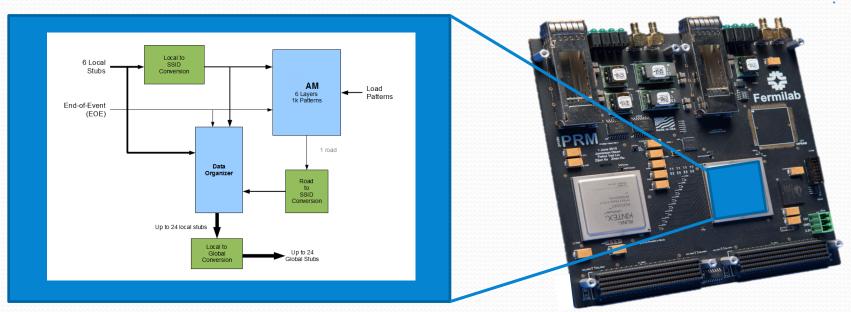

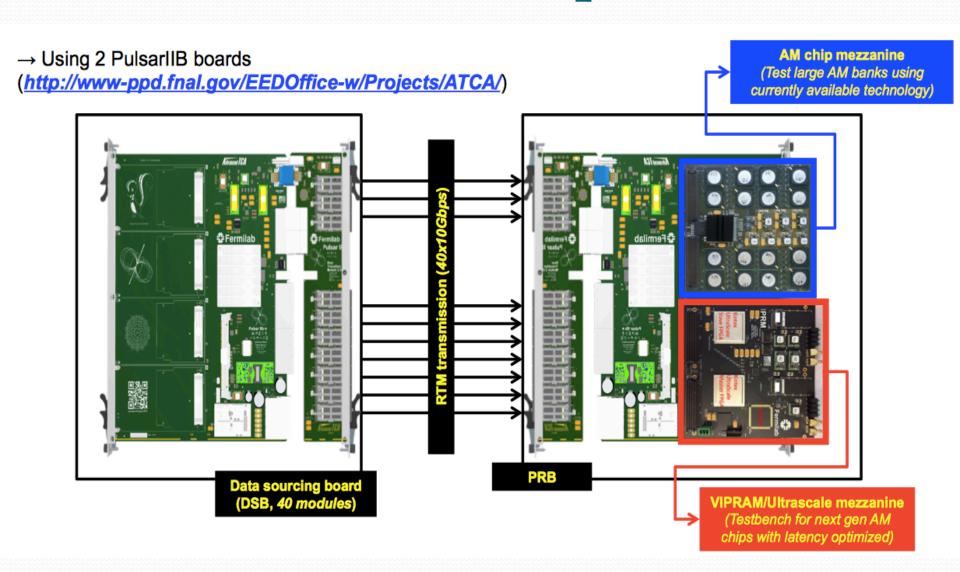

## Tale of two mezzanines

#### Kintex-7 FPGA + AMchipo5/06

- Designed based on ATLAS FTK chip

- High pattern density (AM05/6, 2k/128k)

- AM05 version in hand and working

- Goal: to prove that the 2M patterns can be implemented with today's technology

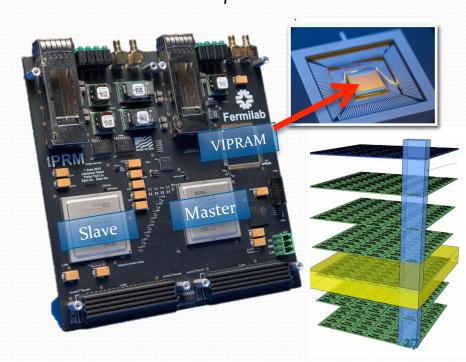

#### UltraScale FPGA + VIPRAM

- Designed for L1 applications

- Low latency

- Low pattern density (4-16k)

- UltraScale FPGAs, more capability

- Goal: to optimize for latency and performance, develop the spec for the final chip

S.Jindariani, VCI'2016

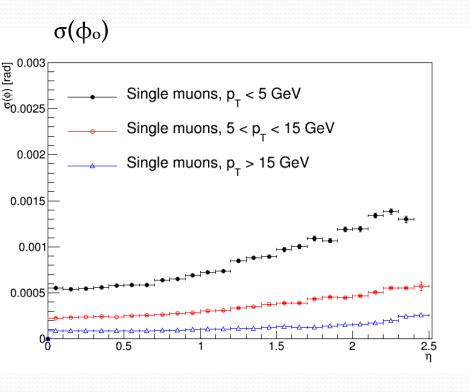

# Linearized track fitting

Given a set of stubs estimate:

- compatibility with a track:  $\chi^2$ /ndof

- track parameters: charge/p<sub>T,</sub>  $\phi_{0,}$  z<sub>0,</sub> cot( $\theta$ ) and d<sub>0</sub>

Method: Linearized Track Fit  $\phi_0 = \sum_i A_i \Delta \phi_i + \bar{\phi}_0$  where  $\Delta \phi_i = \phi_i - \bar{\phi}_i$

New Idea: To minimize number of constants transform the tracker into a smooth cylinder (only 20k constants for the entire tracker)

# Gearing up for demonstration

Need to demonstrate feasibility to finalize design of the tracker

At least one approach has to be proven to work

- Equation with many variables:

- Latency

- Efficiency & Fake Rate

- Anticipated size and cost of the system

- Robustness (against material, alignment, beam shifts, etc)`

- Target end of this year

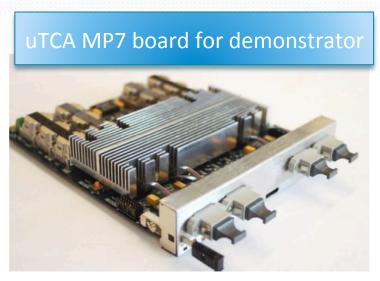

μTCA crate with MP7 (TMT)

## Conclusions

- Having L<sub>1</sub> track trigger is crucial for success of CMS physics goals in HL-LHC

- Highly challenging as track triggering at this scale and speed has never been implemented before

- Aggressive R&D efforts to address the challenge -> both FPGA-only and AM+FPGA approaches

- Plan to demonstrate by the end of 2016 (with Tracker Technical Design Report planned in 2017)

1/15/16 S.Jindariani, VCI'2016 30

# Backup

## **CMS** Detector

## More data

# Proposed L1 Trigger Architecture

## Pattern Recognition Engine Flow

1/15/16

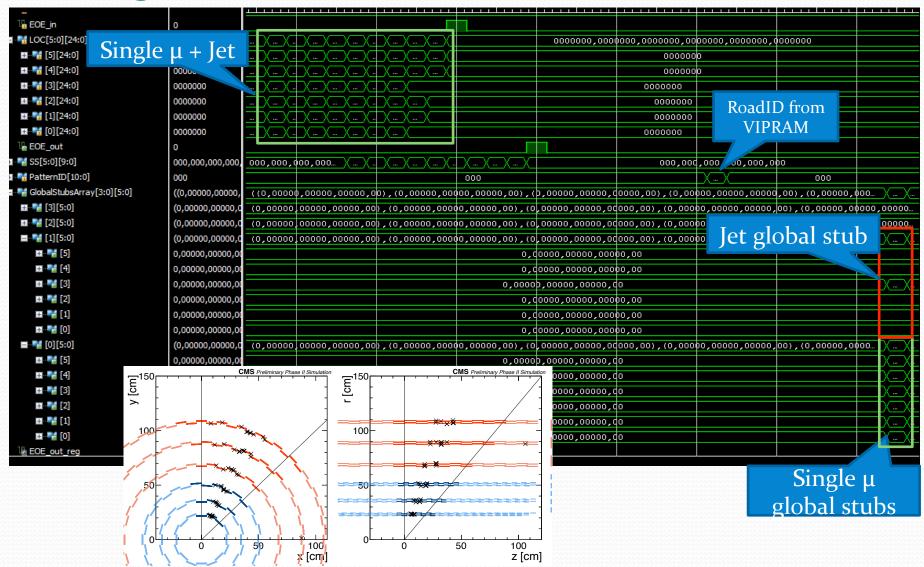

# Single Muon + Jet

1/15/16 S.Jindariani, VCI'2016 36

### Running Firmware in PRM Board

- First time running everything in PRM board

- ✓ All the function blocks are implemented in the Master FPGA of proPRM for simplification

- ✓ Event MEM and Init MEM are BlockRAM with Initial Values (ROM)

System Requirements

S.Jindariani, VCI'2016

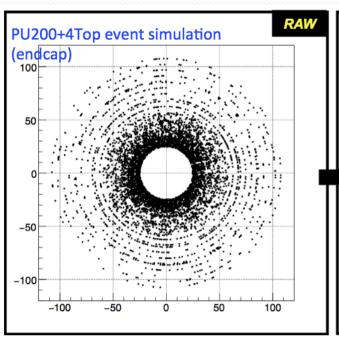

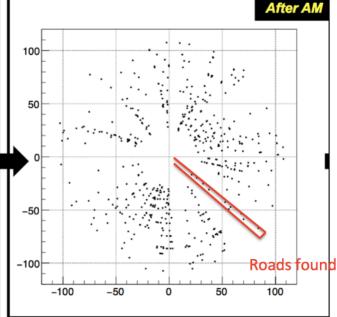

#### **AM Simulation**

Stubs input per trigger tower:

- ~ few x 100

- With patterns per trigger

tower: ~ 4 M

Roads fired per trigger tower:

<50 unique patterns fired

Stubs left for track fitting at AM stage filtering: ~ 20% (th is a set of "stubs of interests" Fountain-like Sstrips, w/o z-segmentation, seem to achieve smaller pattern bank sizes with less fit combinations

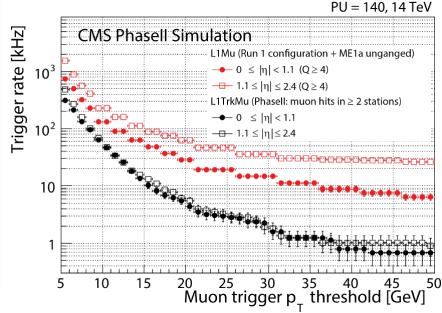

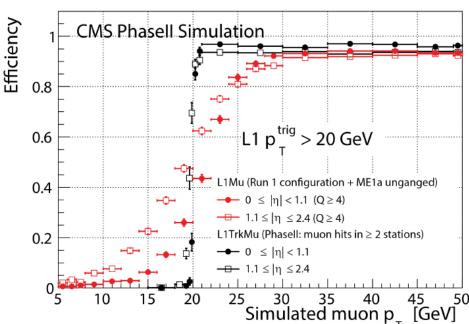

## Impact of tracking at L1:

- Immense trigger challenge facing CMS

- EXAMPLE: At upgraded luminosity trigger curve flattens out for L1 muons

- Most important handle (pt) no longer works with just the information from the muon system

- Need additional information from the tracker to control trigger rates

# Impact of tracking at L1:

#### Current Level-1 Trigger

- No central tracking information

- Electrons/Gammas (EG), Taus, Jets based solely on calorimeter deposits.

- Muons reconstructed from tracks in muon chambers.

- Maximum Bandwidth: 100 kHz

#### HL-LHC:

- Current Trigger System:

- EG rate @25 GeV > 100 kHz

- Muon rate plateaus

- Overall Trigger Rate > 1000 kHz (unsustainable) to reach physics goals

- Upgraded System

- Must increase total bandwidth

- Must increase trigger capabilities

- <u>Level-1 Tracking is a completely</u> NEW handle.

| $L = 5.6 \times 10^{34}  \text{cm}^{-2} \text{s}^{-1}$ | Level-1 Trigger     |              |

|--------------------------------------------------------|---------------------|--------------|

| $\langle PU \rangle = 140$                             | with Level-1 Tracks |              |

|                                                        |                     | Offline      |

| Trigger                                                | Rate                | Threshold(s) |

| Algorithm                                              | [kHz]               | [GeV]        |

| Single Mu (tk)                                         | 14                  | 18           |

| Double Mu (tk)                                         | 1.1                 | 14 10        |

| ele (iso tk) + Mu (tk)                                 | 0.7                 | 19 10.5      |

| Single Ele (tk)                                        | 16                  | 31           |

| Single iso Ele (tk)                                    | 13                  | 27           |

| Single $\gamma$ (tk-iso)                               | 31                  | 31           |

| ele (iso tk) + $e/\gamma$                              | 11                  | 22 16        |

| Double γ (tk-iso)                                      | 17                  | 22 16        |

| Single Tau (tk)                                        | 13                  | 88           |

| Tau (tk) + Tau                                         | 32                  | 56 56        |

| ele (iso tk) + Tau                                     | 7.4                 | 19 50        |

| Tau (tk) + Mu (tk)                                     | 5.4                 | 45 14        |

| Single Jet                                             | 42                  | 173          |

| Double Jet (tk)                                        | 26                  | 2@136        |

| Quad Jet (tk)                                          | 12                  | 4@72         |

| Single ele (tk) + Jet                                  | 15                  | 23 66        |

| Single Mu (tk) + Jet                                   | 8.8                 | 16 66        |

| Single ele (tk) + $H_{\rm T}^{\rm miss}$ (tk)          | 10                  | 23 95        |

| Single Mu (tk) + $H_T^{miss}$ (tk)                     | 2.7                 | 16 95        |

| H <sub>T</sub> (tk)                                    | 13                  | 350          |

| Rate for above Triggers                                | 180                 |              |

| Est. Total Level-1 Menu Rate                           | 260                 |              |

1/15/16 S.Jindariani, VCI'2016

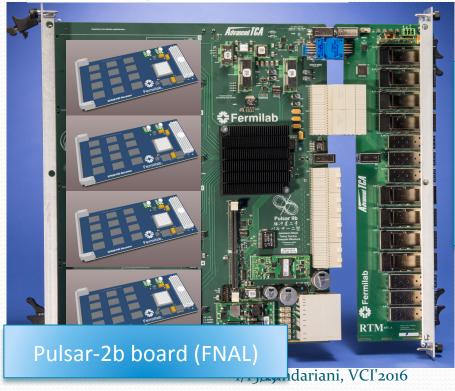

## Board level development

#### AM Architecture

Architecture is flexible and scalable

■Ten Processors send target Processor Blade in a round robin scheme.

## Linearized track fitting

Given a set of stubs estimate:

- compatibility with a track:  $\chi^2$ /ndof

- track parameters: charge/p<sub>T</sub>,  $\phi_0$ ,  $z_0$ , cot( $\theta$ ) and  $d_0$

Method: Linearized Track Fit

$$\phi_0 = \sum_i A_i \Delta \phi_i + \bar{\phi}_0$$

where  $\Delta \phi_i = \phi_i - \bar{\phi}_i$

$$\Delta \phi_i = \phi_i - \bar{\phi}_i$$

To minimize number of constants transform the tracker into a smooth cylinder

Layers/Disk Combinations (6/6) Before Projections

Layers/Disk Combinations (6/6) After Projections

1/15/16 S.Jindariani, VCI'2016

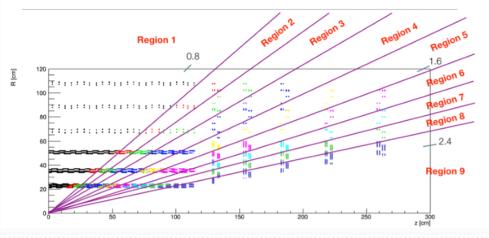

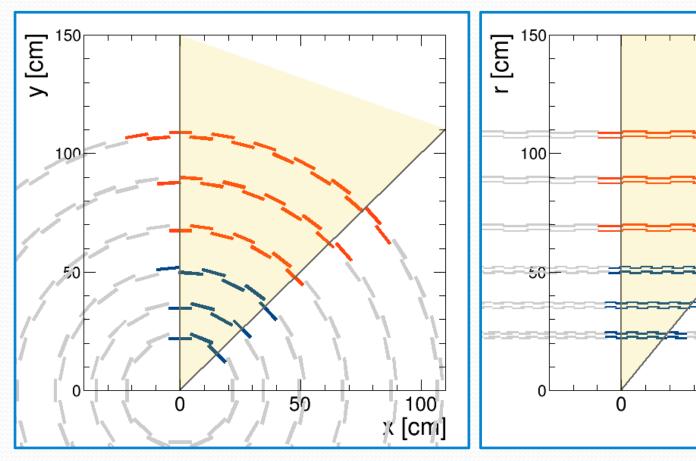

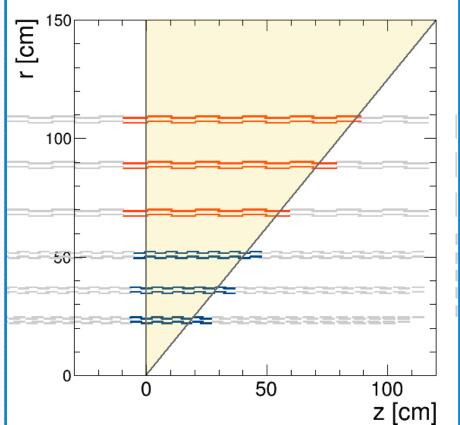

# Example: Barrel Trigger Tower

1/15/16 S.Jindariani, VCI'2016 45

# Linearized track fitting

1/15/16

## Linearized track fitting

- Including 5/6

- 42 (6x6) unique matrices for 6/6 and 252 (5x5) unique matrices for 5/6

- Total number of constants: 19800

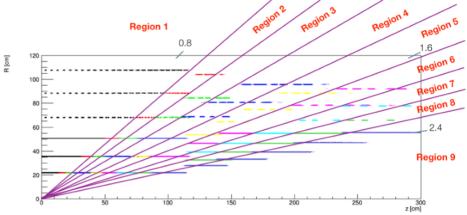

|   | Barrel<br>0 < η < 0.8 | Hybrid<br>0.8 < η < 1.6 | Endcaps $\eta > 1.6$ |

|---|-----------------------|-------------------------|----------------------|

|   | transverse            | transverse              | transverse           |

|   | 2 6x6                 | 18 6x6                  | 16 6x6               |

|   | 12 5x5                | 108 5x5                 | 96 5x5               |

|   | R-z                   | R-z                     | R-z                  |

|   | 1 6x6                 | 9 6x6                   | 8 6x6                |

|   | 6 5x5                 | 54 5x5                  | 48 5x5               |

| _ | 1100 constants        | 9900 constants          | 8800 constants       |

6 S.Jindariani, VCI'2016

#### FM-TMT

- Track finding done using Hough Transformation (HT)

- 36 or 64 (2 implementations)  $\phi$  sectors. Processed processed by independent HT

- Currently, each MP7 processes all (or many)  $\phi$  sectors within a single  $\eta$  sector.

- First tracks showing up in hardware. ~ agree with simulation

1/15/16 S.Jindariani, VCI'2016 48

#### FM-TMT

1/15/16 S.Jindariani, VCI'2016 49

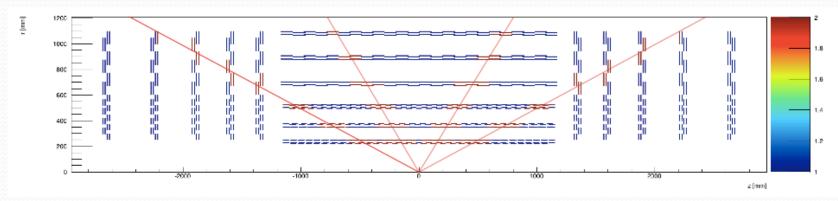

## CMS Tracker Upgrade

One quadrant of the r-z view