# How can Moore's Law help making better detectors?

Larger and cheaper detectors need smaller and more powerful chips.

A. Marchioro CERN/PH-ESE

## Topics

- How is microelectronics benefitting/changing other "instrumentation" fields

- Scaling and trends

- Scaling revisited

- Advanced CMOS technologies

- Technologies around the corner

- Finfet

- Steep sub-threshold devices

- Where to use transistors in instruments and detectors

- Conclusions

## Topics

- How is microelectronics benefitting/changing other "instrumentation" fields

- Scaling and trends

- Scaling revisited

- Advanced CMOS technologies

- Technologies around the corner

- Finfet

- Steep sub-threshold devices

- Where to use transistors in instruments and detectors

- Conclusions

### Simplest Instrument of all

Measurement accuracy: ± 1/16" (from Bosch online catalog). TDC resolution < 10ps. Very likely SPAD based optical receiver. **Much** greater convenience for certain measurements.

A. Marchioro / VCI 2016

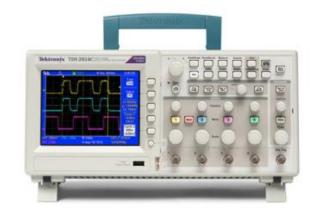

### Instrumentation

| 1960 Price | 1960 Adj Price              | 2015 Price       |

|------------|-----------------------------|------------------|

| 2,600\$    |                             |                  |

| 400\$      |                             |                  |

| 3,400\$    | 21,620\$                    |                  |

|            |                             |                  |

|            |                             | ~1,000\$         |

|            |                             |                  |

|            | 2,600\$<br>400\$<br>3,400\$ | 2,600\$<br>400\$ |

### **Electronics in cars**

- 1965 Car

- Ignition (really electronics...?)

- ?

- 2015 Car

- Engine

- Fuel Injection

- Emission control

- Hybrid engine control

- ...

- ABS

- Safety

- Air bags

- Emergency brake

- Transmission

- Driver Assistance

- Navigation

- Cellular Phone

- Entertainment

- Audio

Target for 2030 is the full ADAS (Advanced Driver Assistance System), i.e. fully autonomous (co)pilot.

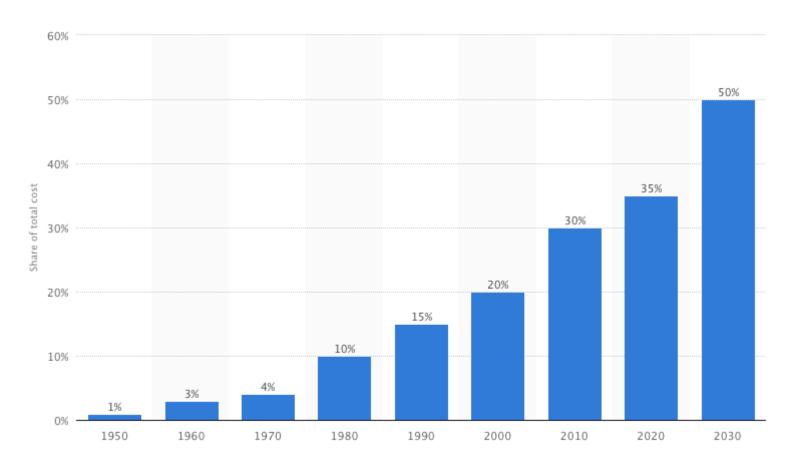

### Value of Electronics in Cars

© Statista 2016

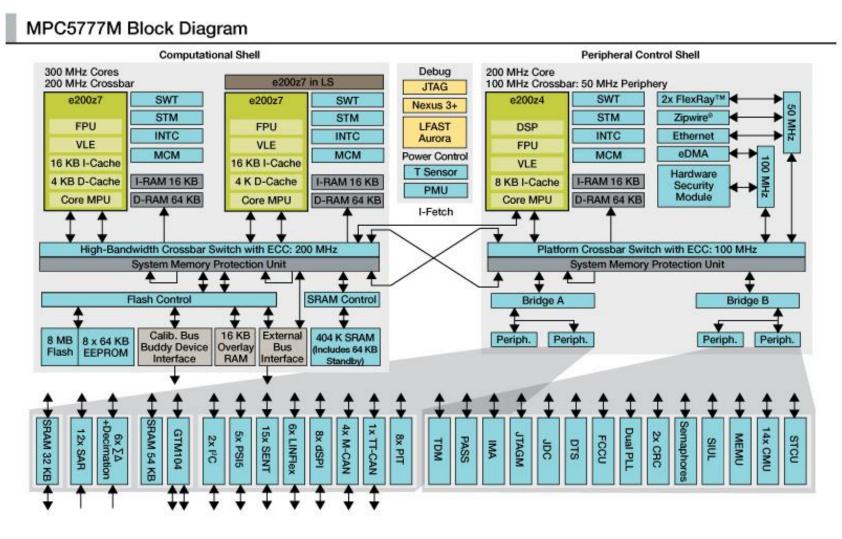

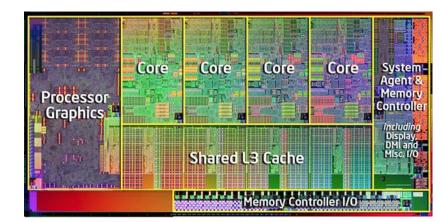

### State-of-the-art processor for ADAS

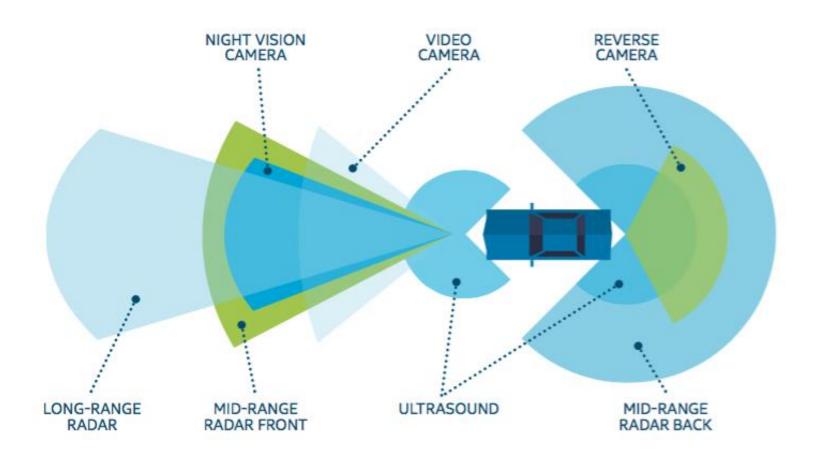

### Sensors in ADAS System

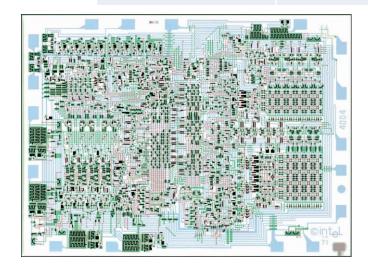

### **Evolution of FE electronics**

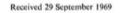

#### AN AMPLIFIER, TRIGGER AND MEMORY FOR SIGNALS FROM PROPORTIONAL WIRE CHAMBERS

J. C. TARLÉ and H. VERWEIJ

CERN, Geneva, Switzerland

Fig. 2. Complete circuit diagram of amplifier, trigger, gates and memory.

Basically the electronic problem is simple: a current pulse of  $\approx 500$  nA (or  $\approx 1$  mV across 2 k $\Omega$ ,  $t_r \approx 20$ nsec,  $t_f \approx 200$  nsec) has to be amplified to a level of  $\approx 1.0$  V, so that it can be conveniently processed. If the

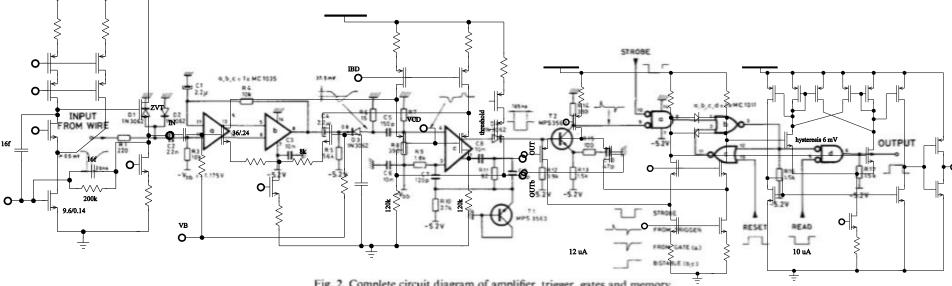

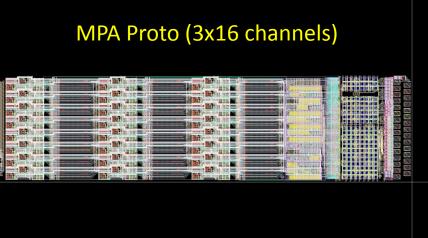

Courtesy of J. Kaplon (CERN) : Front-end for 2015 MPA chip for CMS

### **Complex Data Processing in DosePix**

# Topics

- How is microelectronics benefitting/changing other "instrumentation" fields

- Scaling and trends

- Scaling revisited

- Advanced CMOS technologies

- Technologies around the corner

- Finfet

- Steep sub-threshold devices

- Where to use transistors in instruments and detectors

- Conclusions

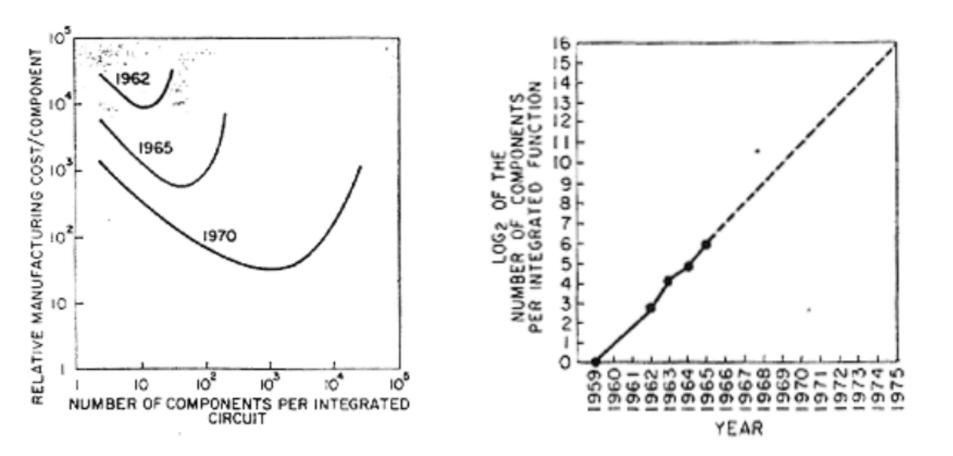

### 50<sup>th</sup> anniversary of G. Moore's paper

# Cramming more components onto integrated circuits

With unit cost falling as the number of components per circuit rises, by 1975 economics may dictate squeezing as many as 65,000 components on a single silicon chip

#### By Gordon E. Moore

Director, Research and Development Laboratories, Fairchild Semiconductor division of Fairchild Camera and Instrument Corp.

The future of integrated electronics is the future of electronics itself. The advantages of integration will bring about a proliferation of electronics, pushing this science into many new areas.

Integrated circuits will lead to such wonders as home computers—or at least terminals connected to a central computer—automatic controls for automobiles, and personal portable communications equipment. The electronic wristwatch needs only a display to be feasible today. machine instead of being concentrated in a ce addition, the improved reliability made possible circuits will allow the construction of larger pro Machines similar to those in existence today v

lower costs and with faster turn-around.

#### Present and future

By integrated electronics, I mean all the nologies which are referred to as microelectro well as any additional ones that result in elec-

### 50<sup>th</sup> anniversary of G. Moore's paper

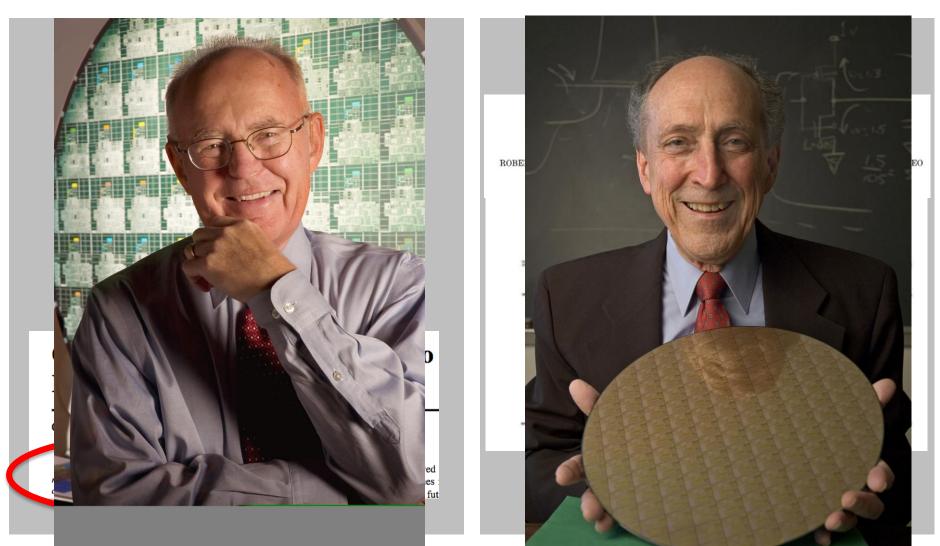

### Who's scaling

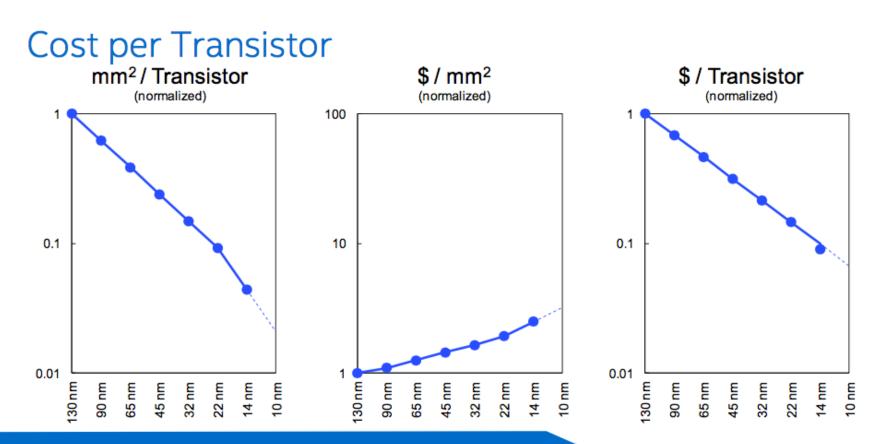

### 1965 statement still true in 2014

Intel 14 nm Continues to Deliver Lower Cost per Transistor

(intel) 3

## What scaling?

| Feature                | <b>1970</b> <sup>[1]</sup>                        | <b>2015</b> <sup>[2]</sup>                        | Ratio       |

|------------------------|---------------------------------------------------|---------------------------------------------------|-------------|

| Wafer Area             | φ=4"                                              | φ=12"                                             | 9 x         |

| Lithography            | 10 um                                             | 14 nm                                             | 700 x       |

| Performance            | 92 KHz                                            | 3 GHz                                             | 32,000 x    |

| Price/Transistor       |                                                   |                                                   | 1/60,000 x  |

| Energy/Comput<br>ation | (1/2 C <sub>1</sub> V <sub>1</sub> <sup>2</sup> ) | (1/2 C <sub>2</sub> V <sub>2</sub> <sup>2</sup> ) | ~1/50,000 x |

|                        |                                                   |                                                   |             |

[1] 1970 numbers are based on Intel 4004 processor[2] 2015 numbers are based on Intel 14 nm technology

A. Marchioro / VCI 2016

A. Marchioro / VCI 2016

### Scaling revisited

The fundamental objective that the microelectronics industry has pursued in the past 50 years may not have been:

"How to make transistors smaller and smaller at each new generation"

but rather:

"How to make transistors (i.e. functionality) cheaper and cheaper at each new generation"

# Topics

- How is microelectronics benefitting/changing other "instrumentation" fields

- Scaling and trends

- Scaling revisited

- Advanced CMOS technologies

- Technologies around the corner

- Finfet

- Steep sub-threshold devices

- Where to use transistors in instruments and detectors

- Conclusions

# Why do we need advanced technologies?

Power used in (digital) integrated circuit:

$$P = P_{dyn} + P_{static}$$

=  $\partial \times N \times f \times C \times V_{dd}^2 + I_{leak} \times V_{dd}$

with:

- a : activity factor

- N : number of transistors switching

- *f* : operating frequency

- C : wire+transistor capacitance

- $V_{dd}$  : operating voltage

- $I_{leak}$  : leakage current (i.e. current when device is off)

### What do we want from a transistor anyway? (sorry engineers...)

- A transistor (a digital transistor) is a device that has to have the following characteristics:

- to work as a switch (on or off)

- make a transition between the two states in a time as short as possible

- has no leakage current when off

- has to deliver high current when on (to drive strongly the next stage).

- Unfortunately this it is not uncorrelated from the previous requirement

- make a transition between the two states with a voltage drive (Vg) as small as possible

- control terminal should not be influenced by input/output terminal(s)

- be physically small (otherwise other "parasitics" ruin the party)

- Must have complementary type (i.e. a second type which is turned on when the first is turned off using the same "control").

- Good "analog" characteristics are desirable but by far not necessary or even important for the the majority of applications.

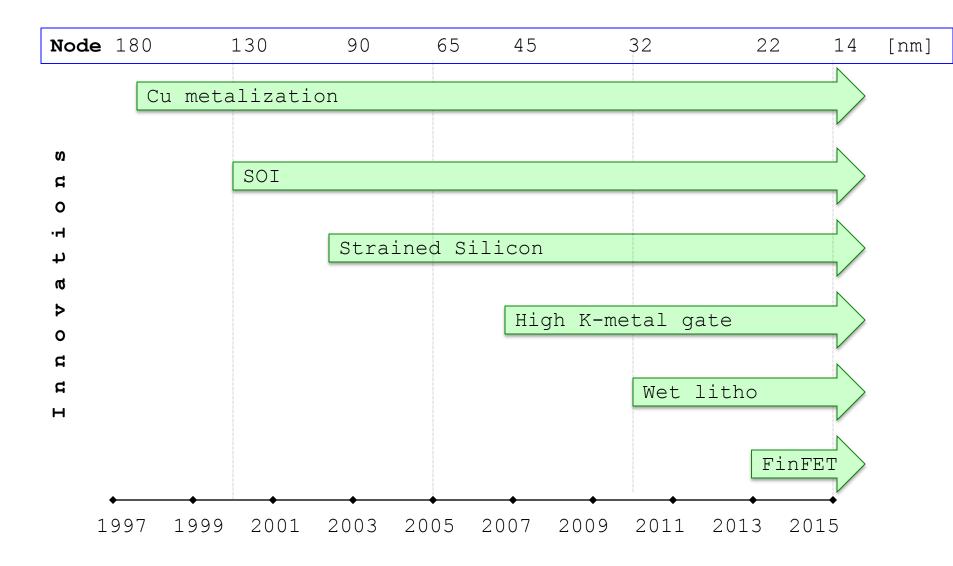

### Timeline of significant innovations

## Technologies around the corner

- FinFet

- FDSOI

- TSVs

- Wafer-to-wafer stacking

- Truly 3D monolithic CMOS

- New materials (III-IV, Ge, GaN, SiC, etc.)

- New phenomena: non kT/q controlled thresholds slopes

## Technologies around the corner

### • FinFet

- FDSOI

- TSVs

- Wafer-to-wafer stacking

- Truly 3D monolithic CMOS

- New materials (III-IV, Ge, GaN, SiC, etc.)

- New phenomena: non kT/q controlled thresholds slopes

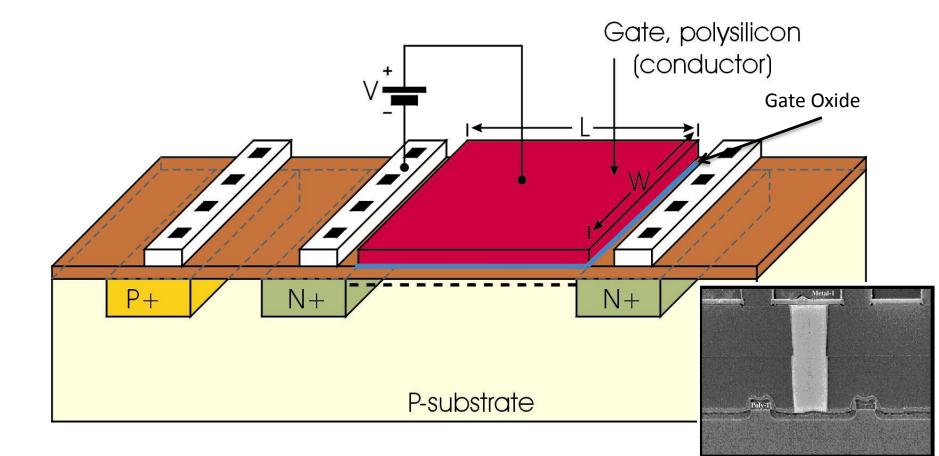

### Refresher: the classical planar transistor

### FinFET: a new device with a long incubation

Solid-State Electronics Vol. 27, Nos. 8/9, pp. 827-828, 1984 Printed in Great Britain 0038-1101/84 \$3.00 + .00 1984 Pergamon Press Ltd. NEW EFFECTS OF TRENCH ISOLATED TRANSISTOR USING SIDE-WALL GATES CALCULATED THRESHOLD-VOLTAGE CHARACTERISTICS OF AN K. Hieda, F. Horiguchi, H. Watanabe, K. Sunouchi, I. Inoue and T. Hamamoto XMOS TRANSISTOR HAVING AN ADDITIONAL BOTTOM GATE VLSI Research Center, Toshiba Corporation Komukai, Saiwai-ku, Kawasaki, 210 Japan (Received 30 May 1983; in revised form 24 August 1983) TOP GATE dato paky SI Source Gate lifewall GATE OXIDE ransistor Drain Sidewall gate region A SOURCE CHANNEL REGION DRAIN Tsi Trench isolation Isolation (Poly Si) Tox SUBSTRATE BOTTOM GATE Fig. 1. Schematic cross-sectional structure of an XMOS transistor having an additional bottom gate which is symmetrically placed to a top gate with a channel region (b) between them. "X" originates from Greek capital letter of xi as this structure resembles its shape. Fig. 1. (a) Schematic cross section of trench isolated transistor using side-wall gates (TIS). (b) SEM micrograph of the cross section along the direction of gate width. Hitachi(?)- 1984 Toshiba-1987 Electronic Device Division T. SEKIGAWA and Electrotechnical Laboratory Y. HAYASHI 32.2 Sakura-mura Iburaki, 305 IEDM 87-737 Japan Monte Carlo Simulation of a 30 nm Dual-Gate MOSFET: IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 38, NO. 6, JUNE 1991 How Short Can Si Go? Impact of the Vertical SOI "DELTA" Structure on Planar Device Technology D. J. Frank, S. E. Laux and M. V. Fischetti Digh Hisamoto, Member, IEEE, Toru Kaga, Member, IEEE, and Eiji Takeda, Senior Member, IEEE IBM Research Division, T. J. Watson Research Center P.O. Box 218, Yorktown Heights, NY 10598 Abstract-A fully depleted lean channel transistor (DELTA) is required. Moreover, it is evident that these st Abitraci—A fully depleted lean channel transistor (DELTA) with its gate incorporated into a new vertical ultra-thin SOI structure is presented. In the deep-submicrometer region, se-lective oxidation produces and isolates an ultra-thin SOI MOS-FET that has high crystalline quality, as good as that of con-ventional pluk single-crystal devices. Experiments and threeare difficult to contact to the substrate, and thus suf Conclusions a substrate floating effect. The second concept makes the device thickness In summary, it appears that high performance Si SOURCE DRAIN than the depletion-layer width to intentionally dep MOSFETs can be scaled down to gate lengths of order dimensional simulations have shown that this new gate struc-ture has effective channel control, and that the vertical ultrachannel. This can be done with thin-film SOI tech such as SIMOX and recrystallization [7], [8]. T 30 nm. Such devices are still suitable for digital circuitry, thin SOI structure provides superior device characteristics: recept is ideal because the structure has the same n and may have transconductances as high as 2300 mS/mm duction in short-channel effects, minimized subthreshold swing, and high transconductance. conventional MOSFET's, however, it requires and ring oscillator speeds near 1 ps. The technology n++ Si ultra-thin SOI substrates, a difficult task. Still, a n<sup>++</sup> Si needed to do this includes thickness control of very thin layers, dual gate alignment, very abrupt doping profiles GATE 2 and gate work function control. A high thermal conductivity method of removing heat from such devices SiÓ2 would also need to be found. Fig. 1. Dual-gate MOSFET cross-section. Our simulations all use References  $d_{ex} = 3$  nm,  $d_{SG} = d_{GD} = 0.3 \times l_G$ , and  $10^{20}$  cm<sup>-3</sup> n-type source and drain doping 21.1 Hitachi – 1991 IBM - 1992 556-IEDM 92 Fig. 1. (a)-(c) Process flow of selective oxic section of DELTA.

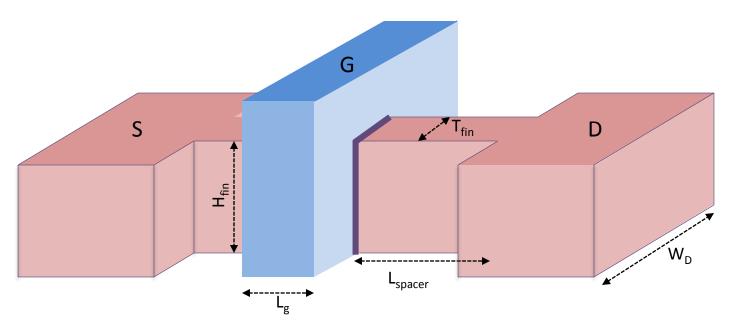

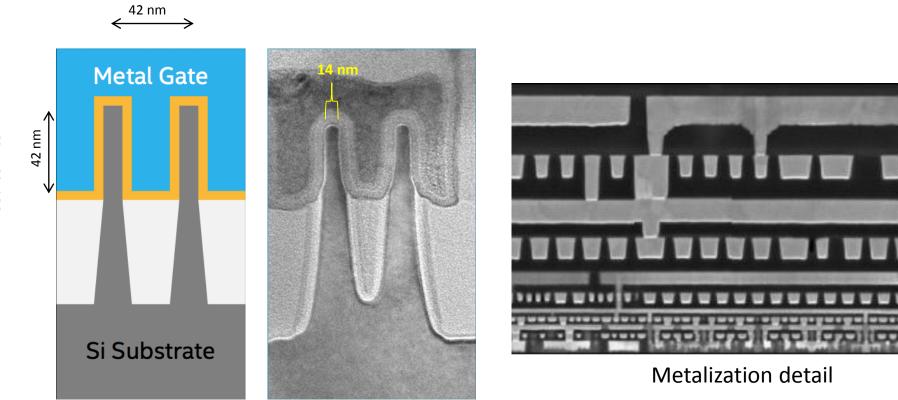

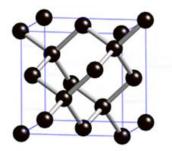

### FinFET Detail

- L<sub>g</sub> same for all devices

- $H_{fin} >> T_{fin}$

- Top Ox same as Lateral Ox -> Tri-Gate,

- if >> Lateral Oxide -> FinFET

- $W_{fin} = 2 * L_{fin} (+T_{fin})$

- W <sub>S,D</sub> >> T<sub>fin</sub>

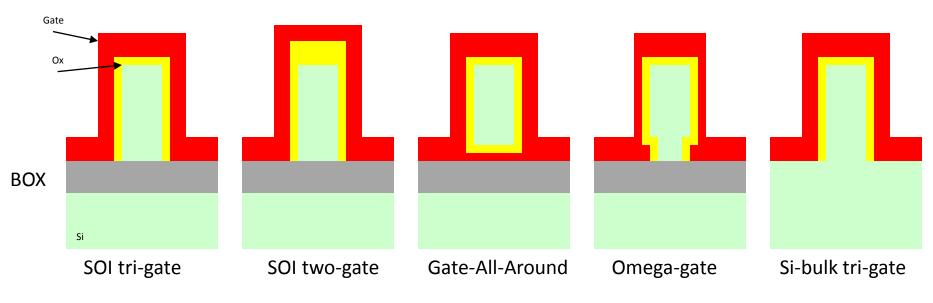

### **Multi-Gate variations**

### Intel TRI-Gate

## **Typical FinFET dimensions**

### From the ITRS 2011 report

| Year of Production          | 2013 | 2015 | 2017 | 2019 | 2021 | 2023 | 2025 | 2028 |

|-----------------------------|------|------|------|------|------|------|------|------|

| FinFET Fin Width (new) (nm) | 7.6  | 7.2  | 6.8  | 6.4  | 6.1  | 5.7  | 5.4  | 5.0  |

## Technologies around the corner

- FinFet

- FDSOI

- TSVs

- Wafer-to-wafer stacking

- Truly 3D monolithic CMOS

- New materials (III-IV, Ge, GaN, SiC, etc.)

- New phenomena: non kT/q controlled thresholds slopes

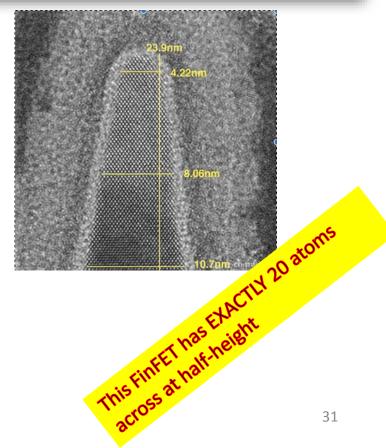

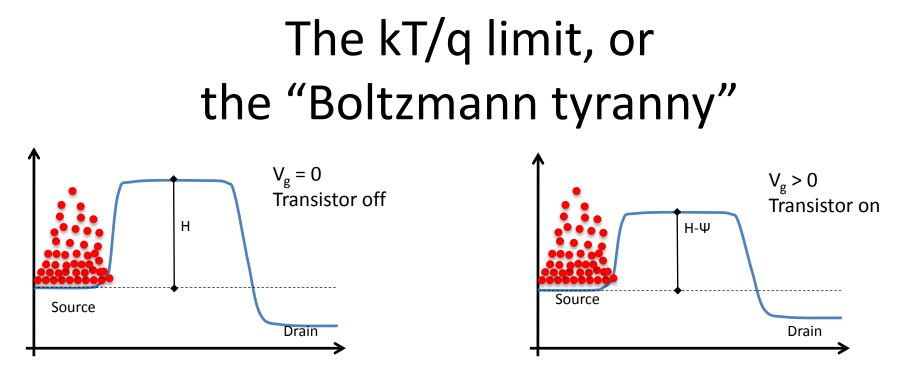

### Intro: about switching transistors

To change the current in a MOS transistor by one order of magnitude, it turns out that the gate voltage has to be changed by:

$$SS = \ln(10)\frac{kT}{q}$$

If the static leakage in a multi-million transistor chip has to be  $\frac{I_{off}}{I_{on}} < 10^{-6}$  then

the transistion region between off and on will have to span at least:

$$V_{TRAN} = 6 \times \ln(10) \frac{kT}{q} \gg 360 mV$$

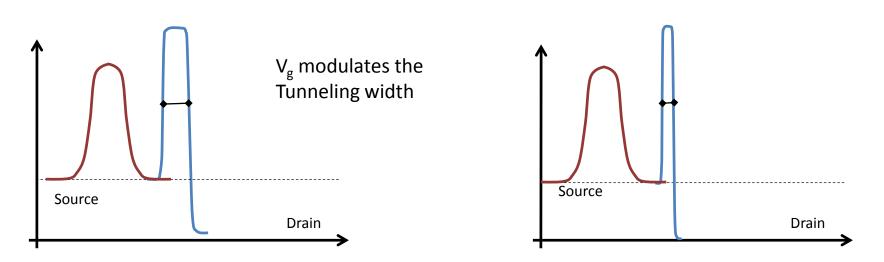

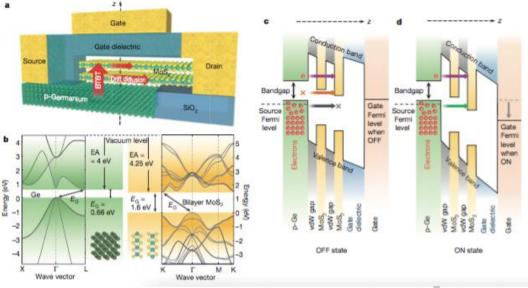

### Quantum tunneling devices

It turns out that certain devices can actually be built with atomic dimensions where band-to-band tunneling can be achieved with SS < 60 mV/decade.

### Sub 60mV/decade FETs

### LETTER

doi:10.1038/nature15387

### A subthermionic tunnel field-effect transistor with an atomically thin channel

Deblina Sarkar<sup>1</sup>, Xuejun Xie<sup>1</sup>, Wei Liu<sup>1</sup>, Wei Cao<sup>1</sup>, Jiahao Kang<sup>1</sup>, Yongji Gong<sup>2</sup>, Stephan Kraemer<sup>3</sup>, Pulickel M. Ajayan<sup>2</sup> & Kaustav Ban

threshold swing, such as band-to-band tunnelling<sup>10-16</sup>. Here we demonstrate band-to-band tunnel field-effect transistors (tunnel-FETs), based on a two-dimensional semiconductor, that exhibit steep turn-on; subthreshold swing is a minimum of 3.9 millivolts per decade and an average of 31.1 millivolts per decade for four decades of drain current at room temperature. By using highly

## Scaling summary: Is scaling really finished in industry?

If one calls "scaling" only the (2D) miniaturization of transistors, then definitively Dennard's scaling is closer to saturation than Moore's.

If instead one calls scaling the reduction in cost (somehow) of the \$/transistor on a chip, then several more generations are ahead of us.

# Topics

- How is microelectronics benefitting/changing other "instrumentation" fields

- Scaling and trends

- Scaling revisited

- Advanced CMOS technologies

- Technologies around the corner

- Finfet

- Steep sub-threshold devices

- Where to use transistors in instruments and detectors

- Conclusions

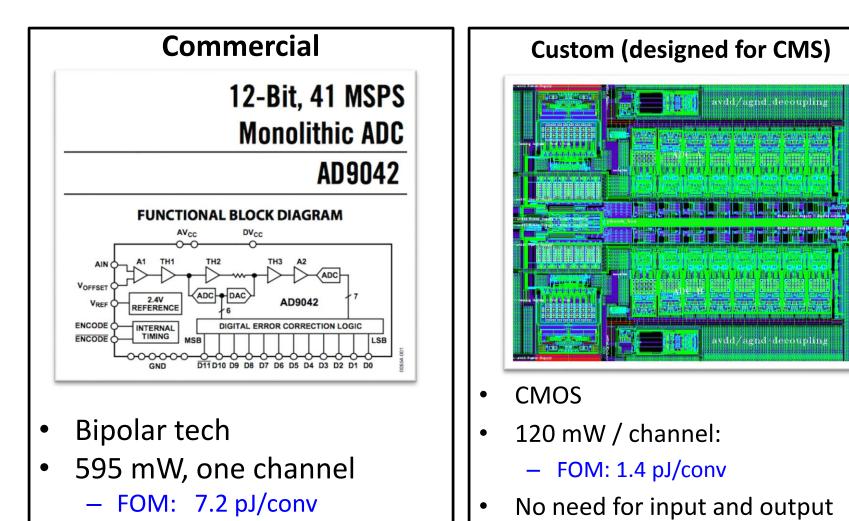

### RH ADCs, circa 2002

2015 State-of-the-art published ADC FOM: ~ 0.01 pJ/conv

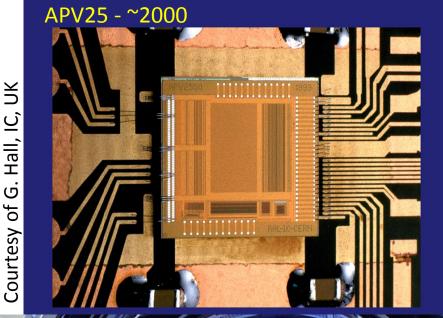

### Tracker FE chips: APV

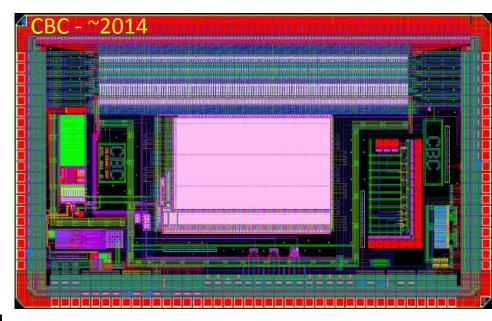

### **CBC** key features

- 130 nm CMOS

- 256 channels

- 300 uW/ch on ~ 5 pF sensor

- previous generation > 675 uW/ch (normalized on 5pF)

- noise ~ 850 e<sup>-</sup>

- Built-in Logic to form trigger primitives

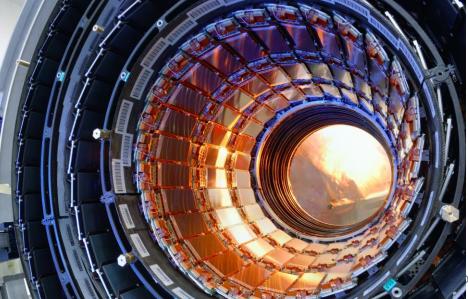

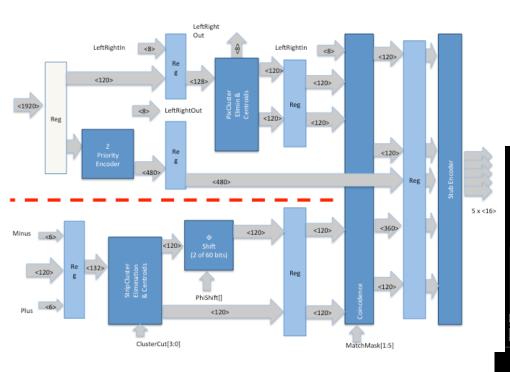

## High complexity FE for trackers: the MPA

### Functionality

two layers sensor to find promptly "stiff" tracks through prompt combinations of hits in FE chips

- One macro pixel (1500x100 um) contains:

- normal analog FE for amp/shaping/discriminating

- clustering logic

- re-alignment logic

- pixel-strip trigger logic

- storage for L1 2,000 logic gates + 512 bit SRAM/pixel

- periphery with 3,000 gates common logic/pixel

# High Speed Links: The GOL {\$}

### A 1.25Gbit/s Serializer for LHC Data and Trigger Optical Links

<u>P. Moreira<sup>1</sup></u>, J. Christiansen, A. Marchioro, E. van der Bij, K. Kloukinas, M. Campbell and G. Cervelli

CERN-EP/MIC, Geneva Switzerland

High density, low power CMOS allowed not only to implement a high speed serializer in a chip, but actually three to combat SEU effects

Serializer FOM: ~ 200 pJ/bit

A. Marchioro / VCI 201

{\$} Paper presented at LEB 1999

### 2016 Links

IEEE SOLID-STATE CIRCUITS SOCIETY

#### SESSION 3

#### Monday February 1st, 1:30 PM

#### Ultra-High-Speed Transceivers

Session Chair: Hyeon-Min Bae, KAIST, Daejeon, Korea Associate Chair: Aiith Amerasekera, Texas Instruments, Dallas, TX

#### 1:30 PM

#### 3.1 A 25Gb/s ADC-Based Serial Line Receiver in 32nm CMOS SOI S. Rylov', T. Beukerna', Z. Toprak-Deniz', T. Toiff', Y. Liu3, A. Agrawal',

P. Buchmann<sup>o</sup>, A. Rylyakov<sup>4</sup>, M. Beakes<sup>1</sup>, B. Parker<sup>4</sup>, M. Meghelli<sup>1</sup> 1BM T. J. Watson Reseach Center, Yorktown Heights, NY <sup>2</sup>IBM Zurich Research Laboratory, Rüschlikon, Switzerland <sup>3</sup>now with Shanghai Jiao Tong University, Shanghai, China <sup>4</sup>now with Coriant Advanced Technology Group, New York, NY

2:00 PM

2:30 PM

3.2 A 320mW 32Gb/s 8b ADC-Based PAM-4 Analog Front-End with Programmable Gain Control and Analog Peaking in 28nm CMOS D. Cui', H. Zhang', N. Huang', A. Nazemi', B. Catli', H. G. Rhew', B. Zhang', A. Momtaz', J. Cao' Broadcom, Irvine, CA: 2now with Apple, Cupertino, CA

3.3 A 25Gb/s Multistandard Serial Link Transceiver for 50dB-Loss DST Copper Cable in 28nm CMOS T. Norimatsu', T. Kawamoto', K. Kogo', N. Kohmu', F. Yuki', N. Nakajipa', T. Muto', J. Nasu<sup>2</sup>, T. Komori<sup>2</sup>, H. Koba<sup>2</sup>, T. Usugi<sup>2</sup>, T. Hokari<sup>2</sup>, T. Kawamata<sup>2</sup> S. UmaF. 2.5 pl/bit M. Tsuge", T. Yamashita", M. Hasegawa", K. Higeta <sup>1</sup>Hitachi, Tokyo, Japan; <sup>2</sup>Hitachi, Kanagawa, Japan Break 3:00 PM 3:15 PM 3.4 A 40/50/100Gb/s PAM-4 Ethernet Tr Serializer FON. K. Gopalakrishnan', A. Ren', A. Tan', A vur', B. Helal', C-F. Loi?, C. Jiang<sup>†</sup>, H. Cirit<sup>†</sup>, I. Quek<sup>a</sup>, J. Rian M. Le<sup>a</sup>, M. Ranjbar<sup>†</sup>, P-S. Wonp<sup>4</sup> Wu', J. Pernillo', L. Tse', R. Naravanan', R. Mohanavelu', S. Herlekar', S. Bhoja', V. St Inphi, Santa Clara, CA: Singapore; <sup>3</sup>Inphi, Irvine, CA

3.5 A 56Gb/s NP /mW/lane Serial Link Transceiver DS1 in 28nm T. Shibasa Ogata', Y. Sakai', H. Miyaoka<sup>2</sup>, F. Terasawa<sup>2</sup>, M. Kudo<sup>2</sup>, Н. Кало?, , S. Kawai<sup>2</sup>, T. Araf<sup>2</sup>, H. Higashi<sup>2</sup>, N. Naka<sup>2</sup>, H. Yamaguchi<sup>1</sup>, T. Mori', Y. Ko, nagi', H. Tamura'

<sup>1</sup>Fujitsu Laboratories, Kawasaki, Japan; <sup>2</sup>Socionext, Yokohama, Japan

#### 4:15 PM

3.6 A 45Gb/s PAM-4 Transmitter Delivering 1.3V<sub>and</sub> Output Swing with 1V Supply in 28nm CMOS FDSOI

M. Bassi<sup>1</sup>, F. Radice<sup>2</sup>, M. Bruccoleri<sup>2</sup>, S. Erba<sup>3</sup>, A. Mazzanti<sup>1</sup> <sup>1</sup>University of Pavia, Pavia, Italy; <sup>2</sup>STMicroelectronics, Cornaredo, Italy 3STMicroelectronics, Pavia, Italy

#### 4:45 PM

3.7 A 40-to-64Gb/s NRZ Transmitter with Supply-Regulated Front-End in DS1 16nm FinFET Y. Frans, S. McLeod, H. Hedavati, M. Elzeftawi, J. Namkoong, W. Lin, J. Im,

P. Upadhyaya, K. Chang Xilinx, San Jose, CA

Conclusion 5:15 PM

15

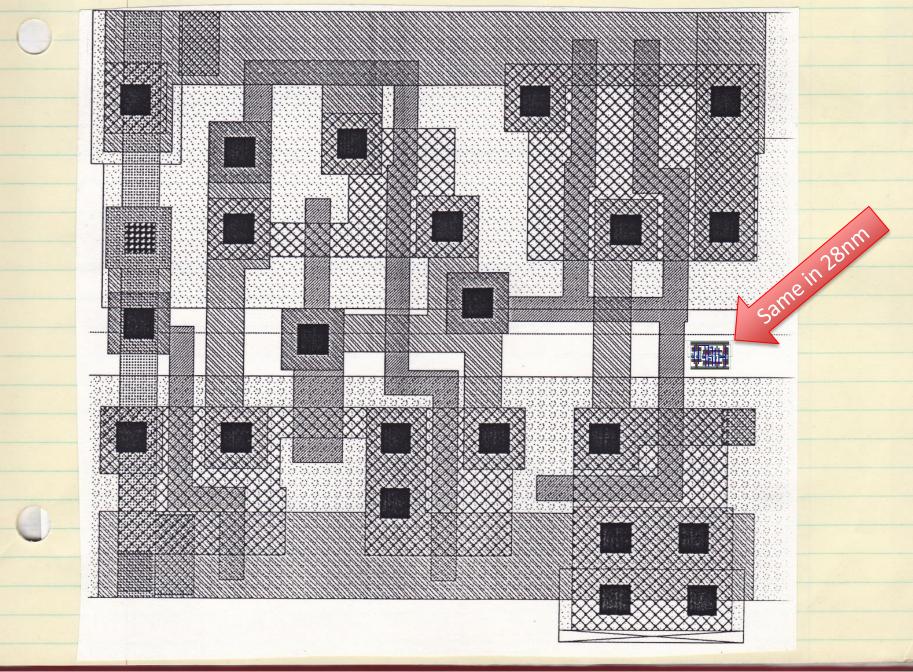

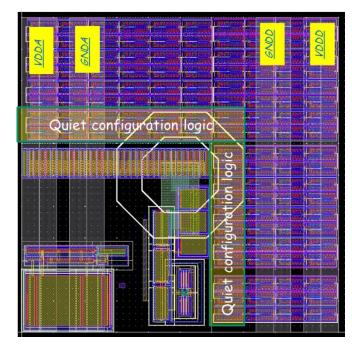

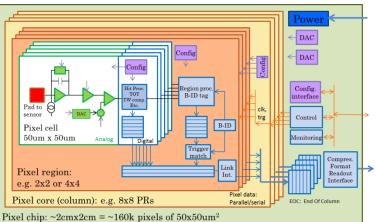

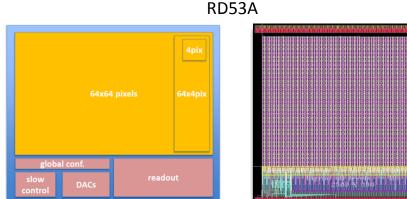

### High density pixel design: RD53 pixel

- Architecture and floor-plan for large pixel chip

- Memory size:

- 2x2 macro-pixel -> 8 hits buffer

- 4x4 macro-pixel -> 16 hits buffer

- Memory size is the critical issue for a 50x50 um pixel

- Benefits from higher density technology in:

- Power

- Buffer sizes

- Logic implementation, triplication

A. Marchioro / VCI 2016

### from J. Christiansen, RD53 Collaboration

### SRAM Density Comparison

| Node          | SRAM Cell Area<br>[um2] {\$} | KBits/mm2 | Relative Density<br>Gain |

|---------------|------------------------------|-----------|--------------------------|

| 130nm         | 1.2                          | 814       | 1.0                      |

| 65nm          | 0.55                         | 1776      | 2.2                      |

| 28nm [bulk]   | .1                           | ~10K      | 12                       |

| 14nm [Finfet] | 0.05                         | ~20K      | 25                       |

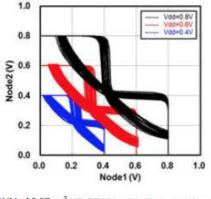

## FE memory with FinFET

TSMC Finfet Based SRAM @ IEDM 2014

Fig.9 SNM of 0.07um<sup>2</sup> HD SRAM cell is illustrated down to 0.4V.

### Cell size: 0.07 um2 Min Operating Voltage: 0.45V Access time @1V is 0.6ns

from Shien-Yang Wu et al: An Enhanced 16nm CMOS Technology Featuring 2nd Generation FinFET Transistors and Advanced Cu/low-k Interconnect for Low Power and High Performance Applications, IEDM 2014

**Application example:**

If trigger latency @HL-LHC taken to 25 us, the tracker F-E would need a 1K memory per channel, i.e. a 128Kbit buffer: 128 10<sup>3</sup> \* 0.07 um<sup>2</sup> = 8.9 10<sup>3</sup> um<sup>2</sup> => 94x94 um only ! (~ 100 x 100 um<sup>2</sup> is the area of a bonding pad!) Operation @ 0.5V => ¼ of the power

# Topics

- How is microelectronics benefitting/changing other "instrumentation" fields

- Scaling and trends

- Scaling revisited

- Advanced CMOS technologies

- Technologies around the corner

- Finfet

- Steep sub-threshold devices

- Where to use transistors in instruments and detectors

- Conclusions

### Conclusions

- Innovation in building new scientific instruments is not limited by the availability of electronic technologies!

- Advanced technologies are nevertheless complex and require strong engineering teams, i.e. more collaboration and coordination in our small community.

- Only workable model:

- Ride carefully well established commercial mainstream technologies

- Stay with a single supplier: partnership is mandatory

- Join forces: foster support of libraries of high level, well constructed, truly portable IPs

- Be professional: demand strictly controlled and documented design flows

- Production cost is NOT dominated by the ICs themselves but by other elements, often our "boutique-like" assembly procedures

- Making more "disposable" detectors?

- Already done in some detectors: can we extend the idea?

### THANK YOU