# Neuromorphic silicon chips

#### Who we are

iniLabs is a spin-off company which commercialises technology from the Institute of Neuroinformatics (INI) at the University of Zurich and ETH Zurich

INI has researched Neuromorphic Engineering since 1990s

Prof. Giacomo Indiveri could not be here today

#### Neuromorphic engineering

Designing electronic circuits which behave similarly to elements of biological nervous systems

- May help us understand how the nervous system works

- May help us to build better computers

I'll present a brief overview, highlighting design choices

# Neuromorphic engineering Antecedents

iniLabs

Mechanical automata (18<sup>th</sup>-19<sup>th</sup> century) e.g. Vaucanson's digesting duck:

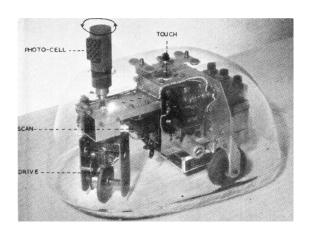

Cybernetic robots (1950s) e.g. Grey Walter's Turtle:

# Neuromorphic engineering Antecedents

iniLabs

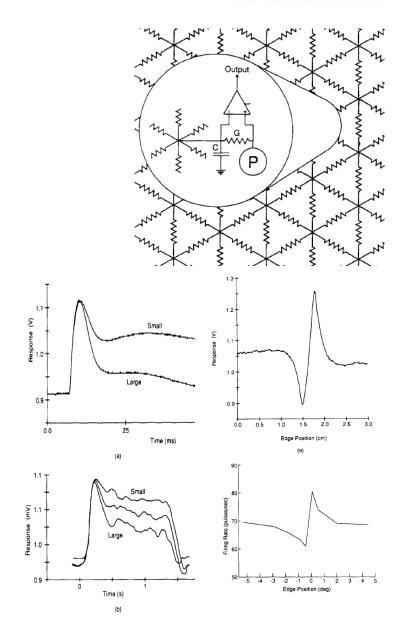

Neural electrical circuits (1960s-1970s)

e.g. Fukushima and Kuffler 1970:

An Electronic model of the retina

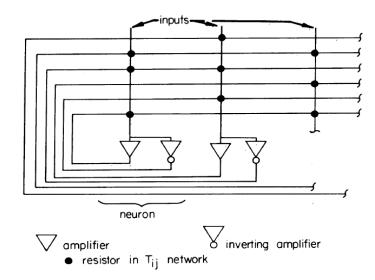

Hopfield 1984:

An electronic model of neural associative memory

neuron

resistor in Tii network

## Silicon integrated circuits

Mead and Mahowald 1988

"A silicon model of early visual processing"

#### Models have been made of:

- Retinae

- Cochleae

- Cognition in central nervous system

#### Parallelism

Many simple imperfect elements acting simultaneously

Many connections between units

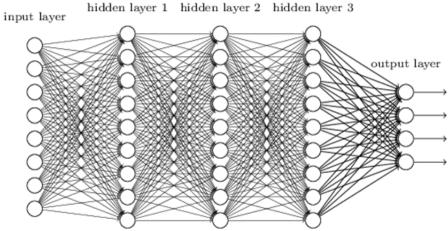

#### Deep neural network

www.rsipvision.com/wp-content/uploads/2015/04/Slide5.png

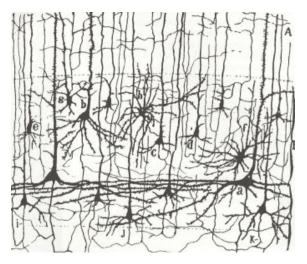

Image by S. Ramon y Cajal

#### Spikes

iniLabs

Artificial neural networks – synchronous layered approach

Hopfield network – continuous operation

Real neurons communicate with pulses (spikes)

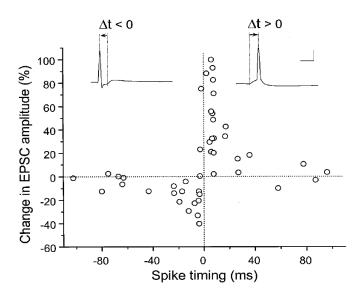

Relevance of spike timing

Bi and Poo 1998: "Synaptic Modifications in Cultured Hippocampal Neurons: Dependence on Spike Timing, Synaptic Strength, and Postsynaptic Cell Type"

#### Spikes

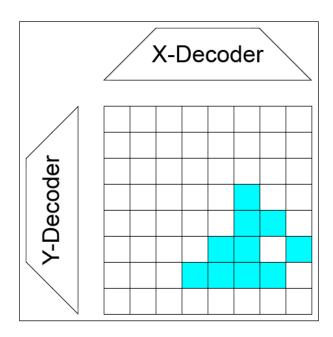

Asynchronous pulse-based communication

Address-Event Representation

Multiplexing uses speed difference between electronic and ionic transmission

Image by S. Ramon y Cajal

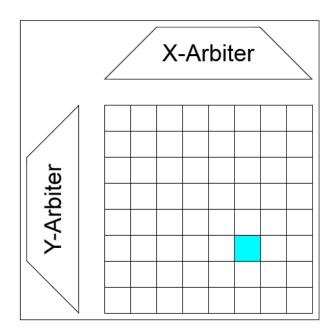

## Many to many connectivity

Fan in and fan out (order 10<sup>5</sup> synapses converge on cells in the cerebellum)

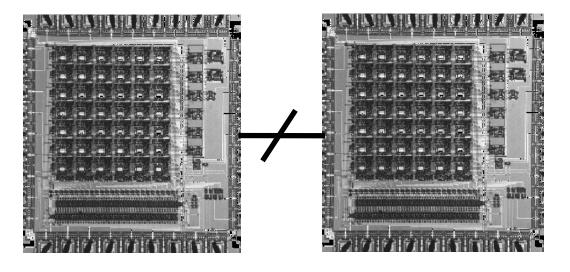

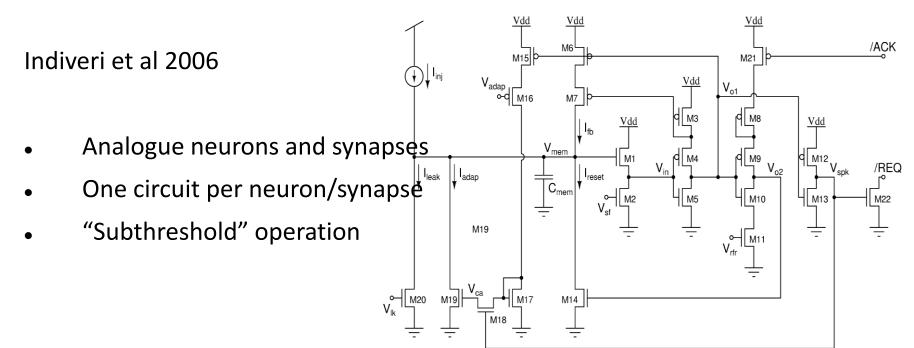

#### Analogue vs digital neurons

c.f.:

IFAT (Cauwenberghs, UCSD)

True North (Modha, IBM)

Spinnaker (Furber, Manchester)

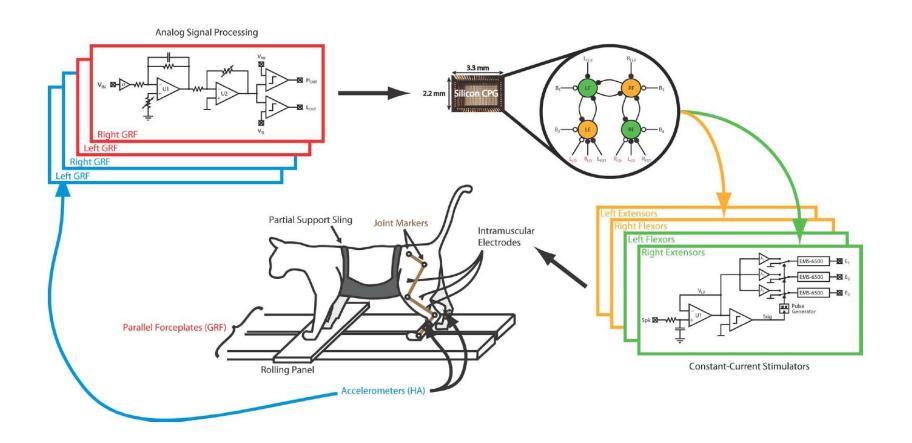

## Neural prosthesis

Vogelstein et al 2008 "A Silicon Central Pattern Generator Controls Locomotion in Vivo"

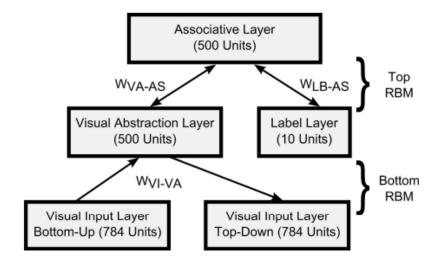

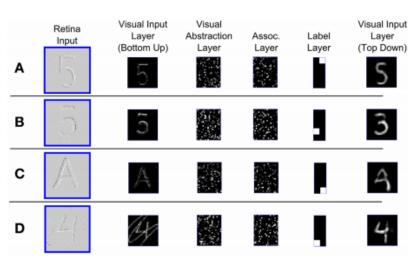

#### Spike-based deep nets

O'Connor et al. 2013 "Real-time classification and sensor fusion with a spiking deep belief network."

## Learning in silicon

#### iniLabs

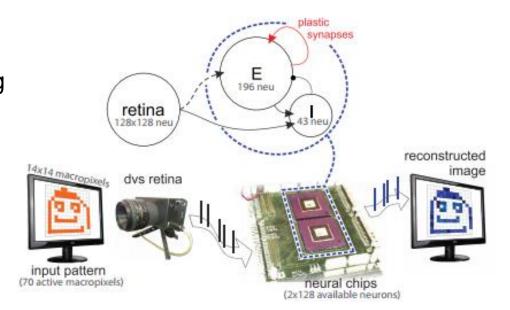

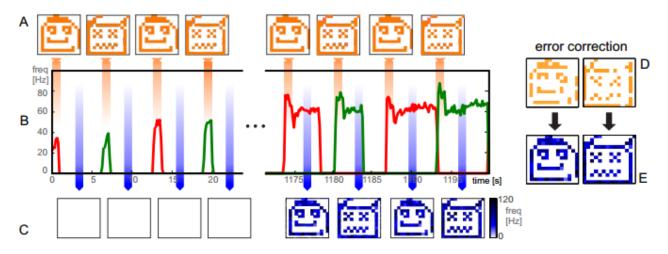

Giulioni et al. 2015

"Real time unsupervised learning of visual stimuli in neuromorphic VLSI systems"

#### The promise

- Attempting to model the nervous system in hardware helps us to understand the nervous system gives us insights into how to solve (computational) problems

- Low-power, real-time, real-world computation

#### Applicability?

- CERN experiments are not continuous but pulsed

- Multiplexing of connections exploits difference between electronic and ionic speeds; when attempting to react much faster than biological reactions this ceases to be an advantage

- No serious power constraints

Could CERN benefit from any of the following?

- Dedicated computational hardware implementing massive parallelism?

- Pulse-timing based transmission of (sensor) values?

- Recurrency in classification?

- Continuous learning (supervised/unsupervised)?

## Neuromorphic engineering

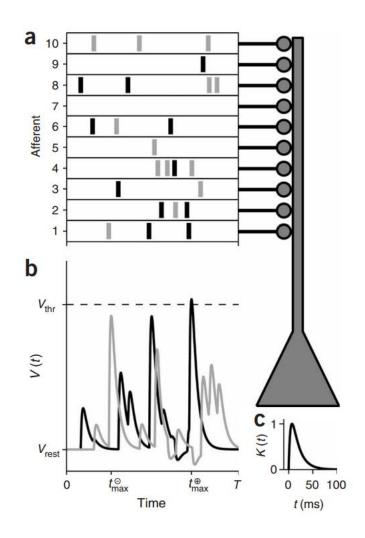

Gutig and Sompolinsky 2006

"The Tempotron: a neuron that learns spike-timing based decisions"

# Dynamic Vision Sensor (DVS)