# Upgrade of the ALICE ITS

#### Markus Keil (CERN)

Markus Keil (CERN)

#### 1 The ALICE ITS Upgrade

#### 2 The Upgraded ALICE ITS

Pixel Chip Barrels and Staves Flex Printed Circuit Cooling

### 1 The ALICE ITS Upgrade

# 2 The Upgraded ALICE ITS

Barrels and Staves Flex Printed Circuit Cooling

# **3** Summary

Markus Keil (CERN)

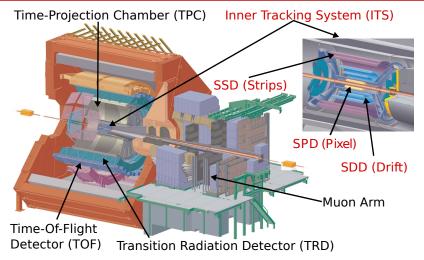

# ALICE and the Current ITS

ALICE is the heavy-ion focussed experiment at the LHC with the main goal to study strongly interacting matter

ALICE

Markus Keil (CERN)

ALICE ITS Upgrade

- Motivation: Focus on high-precision measurements of rare probes at low p<sub>T</sub>

- Cannot be selected by hardware trigger

- Need to record large sample of events

- Goal: Pb-Pb recorded luminosity ≥ 10 nb<sup>-1</sup> (Plus: pp and p-Pb data)

- Gain of factor 100 in statistics for minimum bias

- Strategy: Read out all Pb-Pb interactions up to the maximum LHC collision rate of 50 kHz

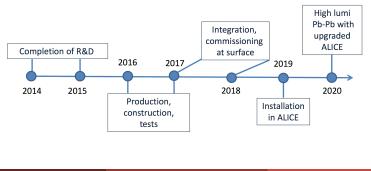

- ▶ When: 2nd long LHC shutdown LS2 (2018/19)

#### Upgrade of the Silicon Trackers

- New high-resolution, low-material inner tracking system (ITS), covering mid-rapidity

- New muon forward tracker (MFT) covering forward rapidity (silicon pixel telescope in front of the hadron absorber, in the acceptance of the muon spectrometer)

- Further Upgrade Items

- New, smaller beam pipe

- TPC: replacing of readout planes and electronics

- Upgrade of forward trigger detectors (FIT) and ZDC

- Upgrade of readout electronics of: TRD, TOF, PHOS and Muon Spectrometer

- Upgrade of Online and Offline Systems

# ITS upgrade

- Main goal: replacement of ALICE Inner Tracking System (ITS) during LHC long shutdown II in 2018–2019

- Design objectives:

- Increased spatial resolution:

- $\blacktriangleright \lesssim 5\,\mu m$  in longitudinal and transverse directions

- Closer to interaction point:

- move to r = 23 mm

- Reduced material:

- $\blacktriangleright\,$  aiming at  $\lesssim 0.3\,\%\,\,X_0$  for innermost layers

- additional benefit from thinner beam pipe

- Increased readout speed:

- Record 50 kHz Pb–Pb collisions (minimum bias)

fully approved

# ITS upgrade

- Main goal: replacement of ALICE Inner Tracking System (ITS) during LHC long shutdown II in 2018–2019

- Design objectives:

- Increased spatial resolution:

- $\blacktriangleright \lesssim 5\,\mu m$  in longitudinal and transverse directions

- Closer to interaction point:

- move to r = 23 mm

- Reduced material:

- $\blacktriangleright\,$  aiming at  $\lesssim 0.3\,\%\,\,X_0$  for innermost layers

- additional benefit from thinner beam pipe

- Increased readout speed:

- Record 50 kHz Pb–Pb collisions (minimum bias)

|    | 15311 0554 31893                                                                                                                                                              |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Journal of Physics G<br>Nuclear and Particle Physics                                                                                                                          |

|    | Volume 41 Number 8 August 2014                                                                                                                                                |

|    | Special Issue<br>Uppraéo of the ALICE Experiment: Letter of Intent<br>Trechical Design Repet for the Upgrade of the ALICE<br>Inner Tracking System<br>The ALICE Collaboration |

|    |                                                                                                                                                                               |

|    | lopscience org/jphysg                                                                                                                                                         |

| J. | Phys. G <b>41</b> 087002                                                                                                                                                      |

#### The ALICE ITS Upgrade

### 2 The Upgraded ALICE ITS

Pixel Chip Barrels and Staves Flex Printed Circuit Cooling

## **3** Summary

Markus Keil (CERN)

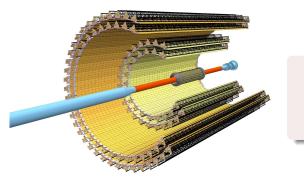

### Layout of the Upgraded ITS

- 7 layers from r=22 mm to r=400 mm

- $\blacktriangleright$   $\sim$  10  ${

m m}^2$  of silicon

- 12.5 GPixels

- Moderate radiation hardness required (at 30°C), expected radiation levels (innermost layer, safety factor of 10):

- $\blacktriangleright$  2700 krad (TID) and 1.7  $\times$   $10^{13}\,1\,{\rm MeV}\,{\rm n}_{\rm eq}{\rm cm}^{-2}$

- ▶  $\eta$  coverage:  $|\eta| \leq 1.22$ , for tracks from 90% most luminous region

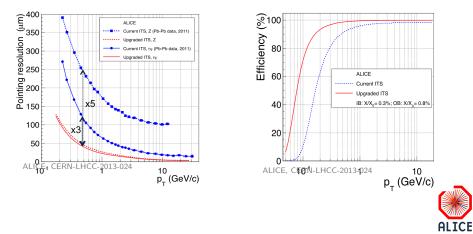

### Expected Performance

Expected improvement of impact parameter resolution (left) and tracking efficiency (right).

#### The ALICE ITS Upgrade

### 2 The Upgraded ALICE ITS Pixel Chip

Barrels and Staves Flex Printed Circuit Cooling

## **3** Summary

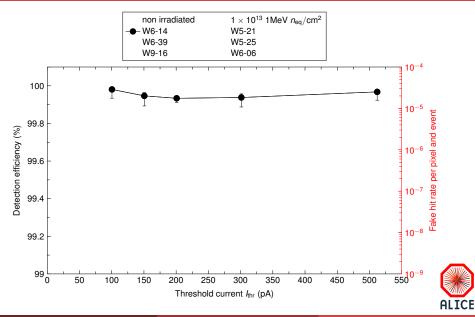

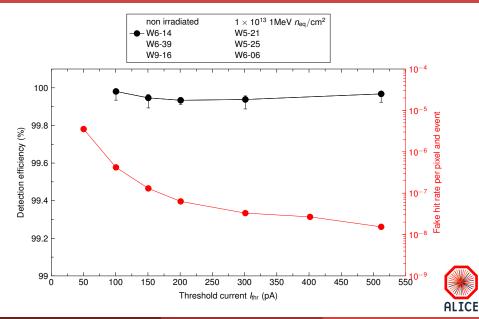

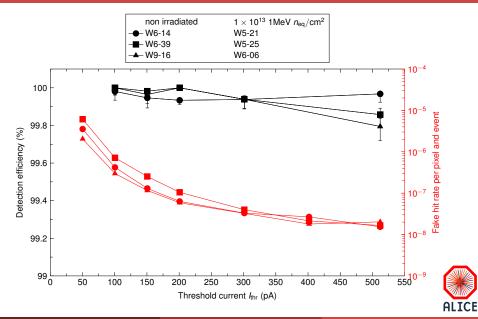

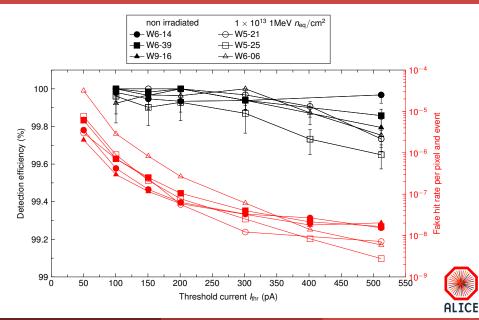

#### Requirements (TDR):

| Parameter            | Inner barrel                             | Outer barrel                                        |  |

|----------------------|------------------------------------------|-----------------------------------------------------|--|

| Silicon thickness    | 50μm                                     |                                                     |  |

| Spatial resolution   | 5µm                                      | 10µm                                                |  |

| Power density        | $< 300 \text{ mW/cm}^2$                  | $< 100 \mathrm{~mW/cm^2}$                           |  |

| Event resolution     | < 30µs                                   |                                                     |  |

| Detection efficiency | > 99%                                    |                                                     |  |

| Fake hit rate        | $< 10^{-5}$ per event per pixel          |                                                     |  |

| TID radiation *      | 2700 krad                                | 100 krad                                            |  |

| NIEL radiation *     | $1.7 \times 10^{13}$ 1 MeV $n_{eq}/cm^2$ | $10^{12} \ 1 \ \mathrm{MeV} \ \mathrm{n_{eq}/cm^2}$ |  |

\* Including a safety factor of 10, revised numbers w.r.t. TDR

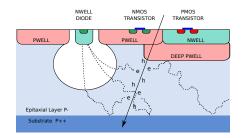

# Pixel Chip Technology

Monolithic active pixel sensors in TowerJazz  $0.18\,\mu\text{m}$  CMOS imaging process

- High-resistivity epitaxial layer on p-substrate

- Quadruple well process: deep pwell shields PMOS transistors, allowing for full CMOS circuitry within active area

- Application of (moderate) bias voltage to substrate can be used to increase depletion zone around NWELL collection diode

13 / 36

Markus Keil (CERN)

ALICE ITS Upgrade

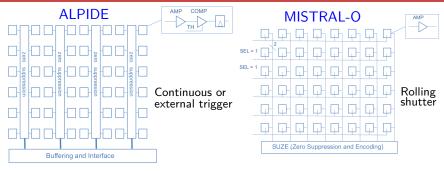

# Chip architectures

- Readout: Data driven sparse readout

- Pixel pitch: 28μm × 28μm

- Event time resolution:  $\leq 2\mu s$

- Power consumption: ~ 40 mW/cm<sup>2</sup>

- Dead area: 1.1 mm × 30 mm

- Baseline solution is the ALPIDE

- Rolling shutter

- 36μm x 65μm

- ► ~ 20µs

- ▶ 80 90 mW/cm<sup>2</sup>

- 1.5 mm x 30 mm

Both chips have the same dimensions, identical physical and electrical interfaces

Markus Keil (CERN)

ALICE ITS Upgrade

# The ALPIDE Development Program

| 2012<br>2013  | Explorer-0<br>Explorer-1                 | Explorer and Investigator:<br>Analog chip to study pixel<br>geometry, starting material and<br>sensitivity to radiation |

|---------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|               | pALPIDEss-0                              |                                                                                                                         |

|               |                                          | <ul> <li>pALPIDEss:<br/>Small scale digital chip to study the</li> </ul>                                                |

| 2014 May      | pALPIDE-1<br>pALPIDEss-1<br>Investigator | priority encoder and the front-end<br>electronics                                                                       |

| 2015 April    | pALPIDE-2                                | <ul> <li>pALPIDE-1:<br/>Full scale chip to study system<br/>effects</li> </ul>                                          |

| 2015 August   | pALPIDE-3                                | pALPIDE-2:<br>Full scale chip which supports                                                                            |

| 2016 February | ALPIDE                                   | integration into module protot<br>Supports local bus of Outer B<br>modules ALICE                                        |

Markus Keil (CERN)

2

**ALPIDE** Prototype Generations:

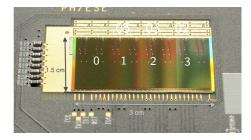

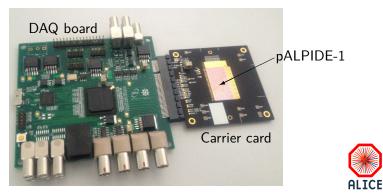

# pALPIDE-1

- First prototype with final size  $(15 \text{ mm} \times 30 \text{ mm})$

- ▶ 512 x 1024 pixels

- Pixel size 28µm x 28µm

- Digital readout with priority encoder

- Four sectors with different pixel layouts

| Sector | Nwell<br>diameter | Spacing | Pwell<br>opening | Reset |

|--------|-------------------|---------|------------------|-------|

| 0      | 2μm               | 1μm     | 4µm              | PMOS  |

| 1      | 2μm               | 2μm     | бµт              | PMOS  |

| 2      | 2μm               | 2μm     | бµт              | Diode |

| 3      | 2µm               | 4µm     | 10µm             | PMOS  |

Markus Keil (CERN)

ALICE ITS Upgrade

ATLAS HV-MAPS Workshop

#### Characterization methods - laboratory

- USB based test system. Performed comprehensive lab measurement program

- Noise and threshold scans

- Pulse shape / pulse length

- Noise occupancy measurements

- Source measurements

- For different back bias voltages

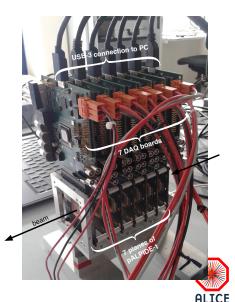

- Test beams are carried out using a telescope made entirely of pALPIDE-1

- Extensive campaign with beams at PS, SPS, PAL (Korea), BTF (Italy), DESY (Germany)

- In the following: results with 6 GeV/c π<sup>-</sup> from CERN PS

- Tests before and after neutron irradiation

Markus Keil (CERN)

Markus Keil (CERN)

ALICE ITS Upgrade

Markus Keil (CERN)

Markus Keil (CERN)

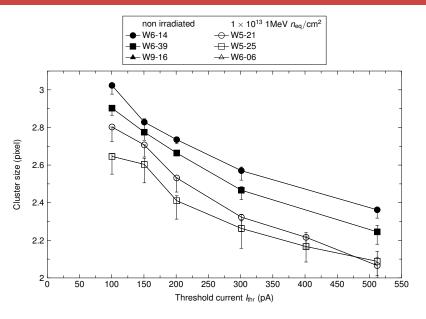

#### Cluster sizes

**ALICE** 20 / 36

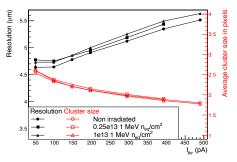

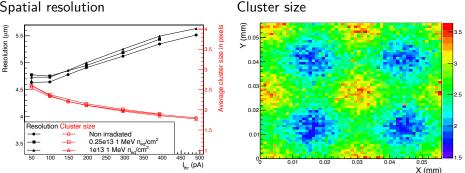

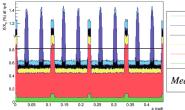

# Spatial resolution

#### Spatial resolution

- Average cluster sizes of 1.5–3 pixels

- Spatial resolution of around 4.5 μm to 5.5 μm

# Spatial resolution

#### Spatial resolution

- Average cluster sizes of 1.5-3 pixels

- Spatial resolution of around  $4.5 \,\mu\text{m}$  to  $5.5 \,\mu\text{m}$

- → Can use telescope tracking to study properties differential in track impinging point

- Cluster size varies nicely leading to good intrinsic resolution

# MISTRAL development

#### MISTRAL FSBB

- First Full Scale Building Block (FSBB)

- Sensitive area: 13.7 × 9.2mm<sup>2</sup> (~ third of the final chip size)

- Staggered pixels of 22 × 33µm<sup>2</sup>

- In-pixel pre-amplification and clamping with 6 metal layers

- 416 × 416 of Columns x Row of pixels ended by discriminator (8-cols with analogue output)

- Double-row readout at 160 MHz clock frequency resulting in 40µs integration time

MISTRAL-O

- Being optimized for the outer layers

- $\blacktriangleright$  Target requirements on the spatial resolution:  $\sim 10 \mu m$

- Target requirements on power consumption: < 100mW/cm<sup>2</sup>

ALICE ITS Upgrade

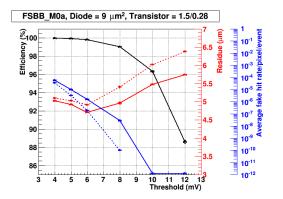

# Performance of the MISTRAL FSBB

- $\blacktriangleright$  Large operational margin: 5.0 mV  $\leq$  Thr  $\leq$  8.0 mV

- Fake hit rate averaged over 11 sensors

- ▶ Fake hit rate drops by O(10) by masking the 20 noisiest pixel

- $\blacktriangleright$  Tracking resolution is (4.7  $\pm$  0.1)µm (U) and (4.9  $\pm$  0.1)µm (V) Thr= 6 mV

23 / 36

Markus Keil (CERN)

#### The ALICE ITS Upgrade

```

2 The Upgraded ALICE ITS

Pixel Chip

Barrels and Staves

Flex Printed Circuit

Cooling

```

Markus Keil (CERN)

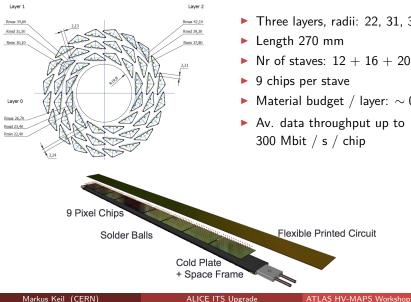

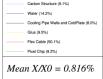

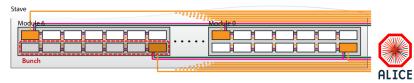

# ALICE ITS Inner Barrel

- Three layers, radii: 22, 31, 39 mm

- Length 270 mm

- Nr of staves: 12 + 16 + 20

- 9 chips per stave

- Material budget / layer:  $\sim 0.3\% X_0$

ALICE

25 / 36

Av. data throughput up to 300 Mbit / s / chip

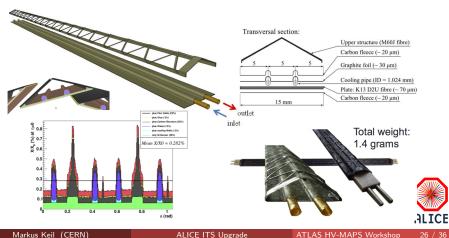

#### Inner Barrel Stave **Design and Prototypes**

- Lightweight carbon structure with polyimide cooling pipes (wall thickness  $25 \,\mu m$ )

- Average material budget  $< 0.3\% X_0$

#### Inner Barrel Prototype

- 4 layers, radii: 194, 247, 353, 405 mm

- Length: 843 (ML), 1475 mm (OL)

- Nr of staves: 22, 28, 40, 46

- Nr of modules/stave: 4 (ML), 7 (OL)

- Nr of chips/module: 14

- $\blacktriangleright\,$  Material budget / layer:  $\sim 0.8\%\,X_0$

- Data throughput < 12 Mbit / sec / cm<sup>2</sup>

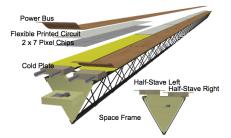

# Outer Barrel Stave

- Outer barrel stave consists of two staggered half-staves

- Each half-stave further segmented into modules

- Average material budget per layer ~ 0.8% X<sub>0</sub>

# Stave Readout Topology

- From the innermost to the outermost layer

- The expected hit densities decrease by a factor of 100.

- The number of chips per (half-) stave increases from 9 to 98.

- Different readout topologies for inner and outer barrel

- Inner Barrel: each chip drives point-to-point data line to off-detector electronics.

Outer Barrel: chips grouped into modules with two master chips; point-to-point link from masters to off-detector electronics.

#### The ALICE ITS Upgrade

#### 2 The Upgraded ALICE ITS

Pixel Chip Barrels and Staves Flex Printed Circuit Cooling

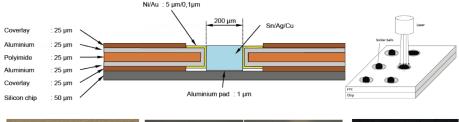

# Flex Printed Circuit (FPC)

- Flexible printed circuit of low-CTE polyimide and aluminium

- Power planes for digital and analogue voltage

- 11 differential pairs (clock, configuration, 9 data lines)

Outer Barrel: Decided to use Cu instead of Al (  $\sim$  +0.1% X<sub>0</sub>), physics impact low enough ALICE

Markus Keil (CERN)

ALICE ITS Upgrade

# Chip-to-FPC Connection

Chip and FPC will be connected by laser soldering

- Connection to dedicated pads distributed over the full chip area

- Successfully tested with daisy-chain and real chips

- Thermal cycling tests currently ongoing

Markus Keil (CERN)

ALICE ITS Upgrade

#### The ALICE ITS Upgrade

#### 2 The Upgraded ALICE ITS

Pixel Chip Barrels and Staves Flex Printed Circuit Cooling

## **3** Summary

Markus Keil (CERN)

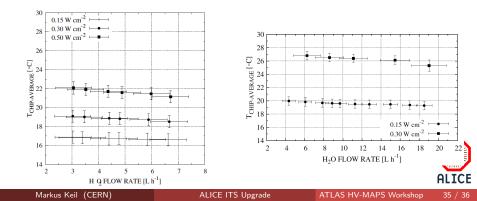

# Cooling

- Goal: Chip temperature below 30°C

- Baseline: leakless (< 1 bar) water cooling</p>

- Thermal characterisation of stave prototypes with heaters for different flow rates:

- Chip (heater) temperature well below 30°C

- Pressure drop < 0.3 bar</p>

## Summary

- ALICE will replace its entire Inner Tracking System by a MAPS based pixel-only tracker during LS2

- All R&D items of the project are close to finalised

- Two working pixel chip prototypes

- Currently completing R&D and preparing for start of production / construction in 2016

ALICE