# Status of digital integration electronics

#### J. Kral, D. Belohrad, D. Esperante

#### Overview

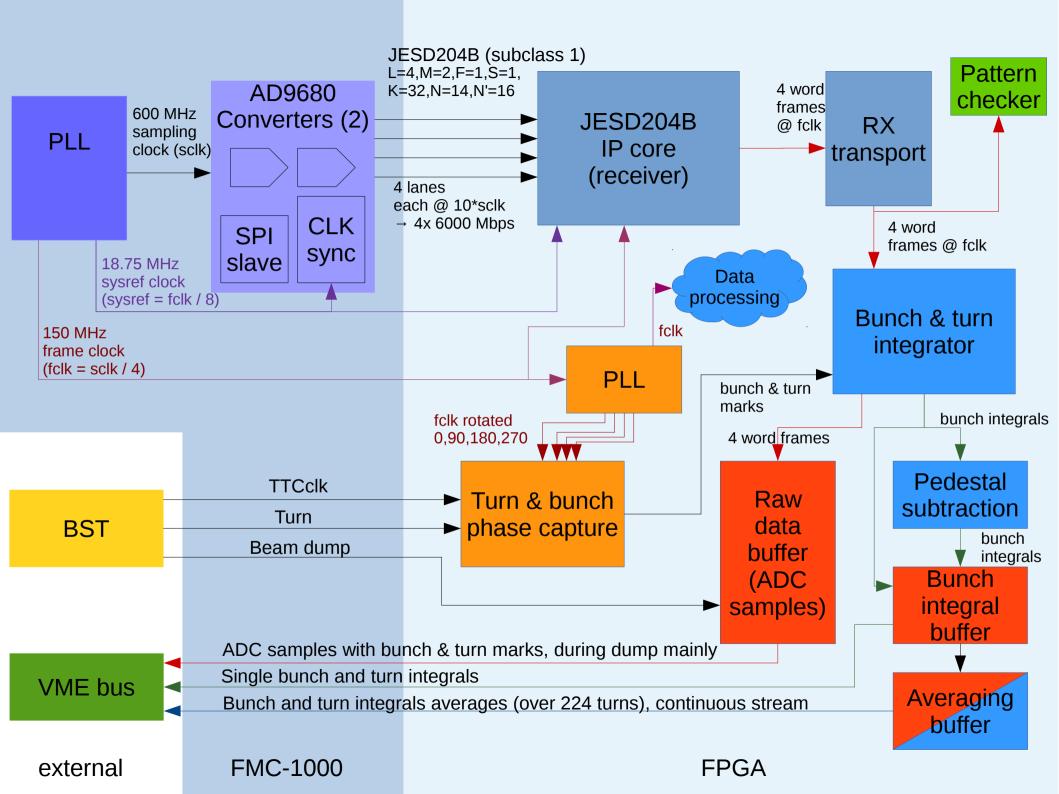

- Up to 1 GSPS digital sampling to replace used analog integrators

- 600 MSPS currently due to VFC FPGA transceiver limitation

- Expecting production of VFC with Arria V GT (10 GSPS limit)

- Current status

- Received FMC-1000 hardware from Innovative (May 21st)

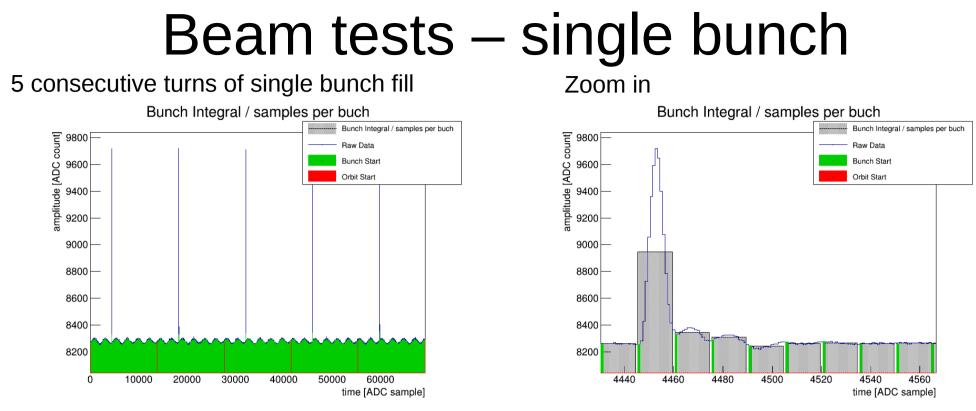

- First beam tests at SPS (since July 8<sup>th</sup>)

- Demonstration project for JESD204B link available

#### **Basic idea**

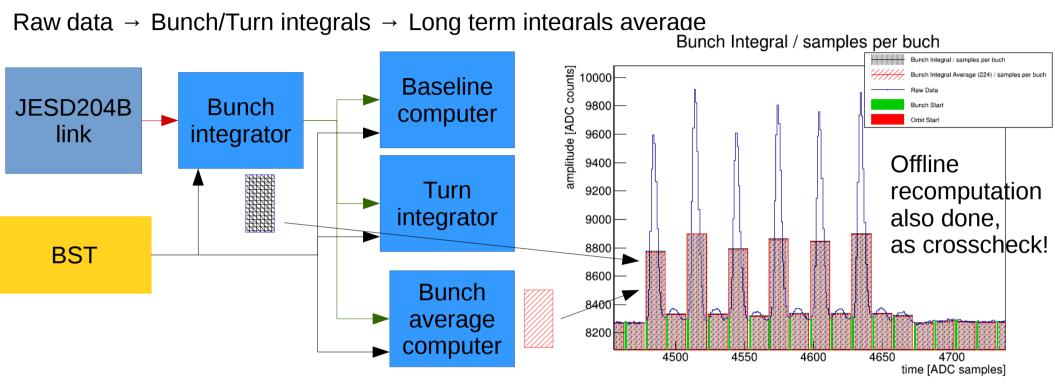

# Data processing in FPGA

- Bunch margins identified by sampling the bunch/turn clock, identical # of ADC samples per bunch  $\rightarrow$  unused samples

- Baseline acquired each turn during abort gap

- Baseline subtraction ON/OFF possibility

- Automatic machine (LHC/SPS) ID based on BST

### Available measurements

- Continuous

- Per bunch integral long term average with selectable averaging period (# of turns)

- Turn integral long term average, same period

- Start of averaging time stamped

- Triggered (dumps)

- Raw ADC data

- Bunch integrals

- Baseline

- Turn integral

- Dump start time stamped

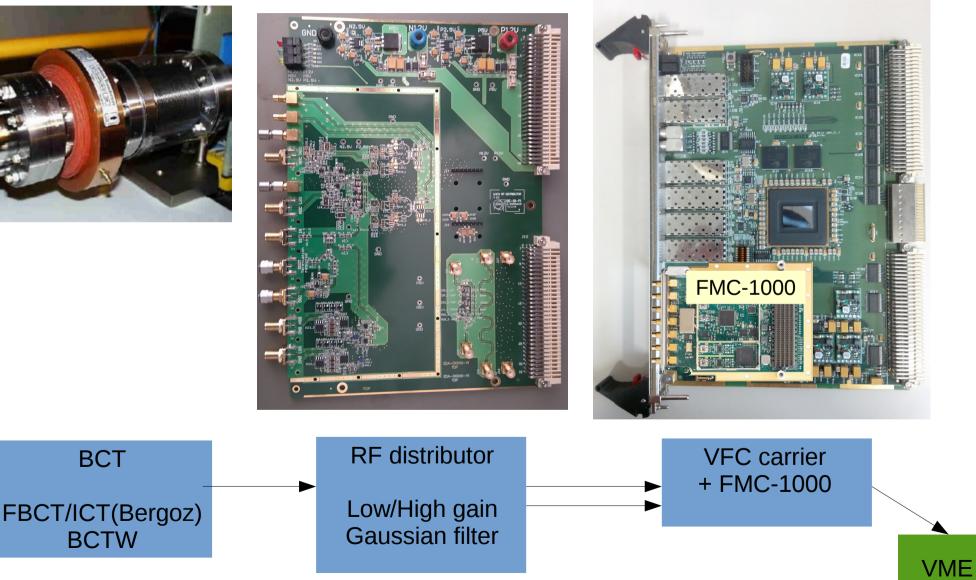

- Installation at SPS, BA3

- FBCT  $\rightarrow$  amplifier  $\rightarrow$  RF distributor  $\rightarrow$  FMC-1000

- Re-using existing setup

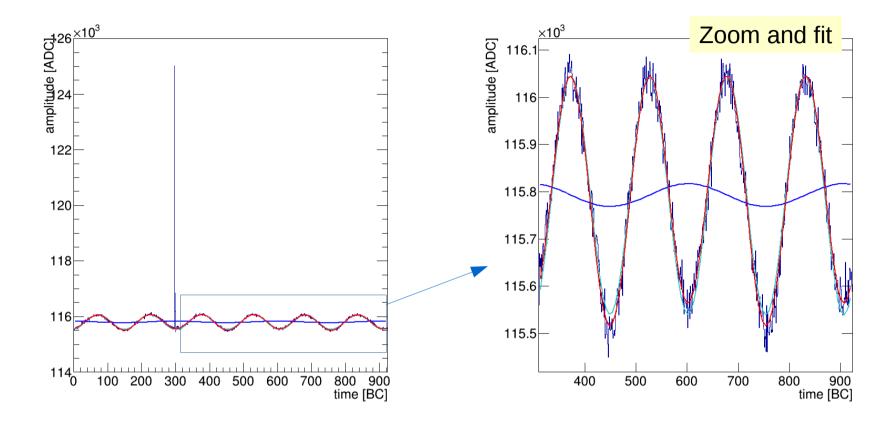

- Oscillating baseline observed

- Visible on scope at amplifier output as well, not visible on amplifier input

- Single bunch signal ringing & droop observed

- Observed in front of amplifier as well, with scope  $\rightarrow$  needs to be quantified

#### **Baseline** subtraction

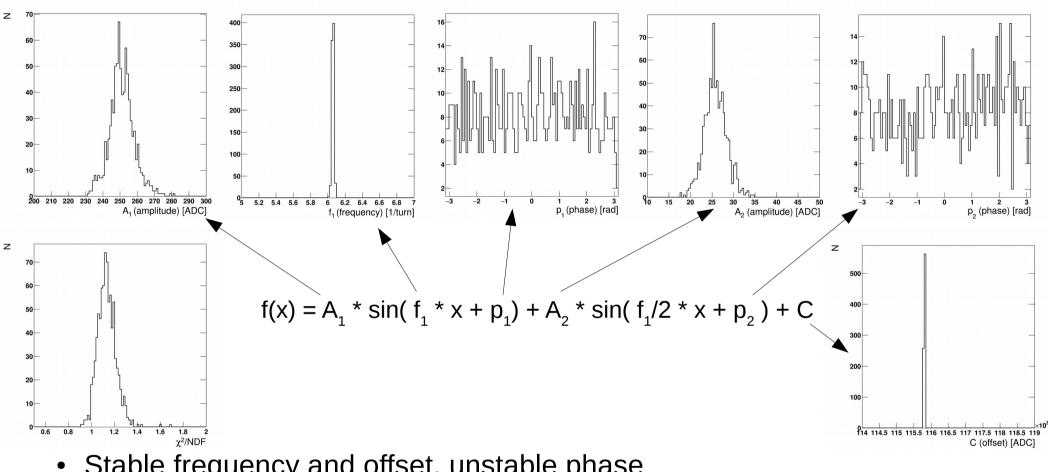

- · Working with bunch integrals from now on

- Double sin fit of two consecutive harmonics

$- f(x) = A_1 * sin(f_1 * x + p_1) + A_2 * sin(f_1/2 * x + p_2) + C$

# **Background fit results**

- Stable frequency and offset, unstable phase

- In respect to turn start

- $f_1 = 6.06 \text{ turn}^{-1}$

- Fit can be used to extrapolate baseline below signal on per dump bases

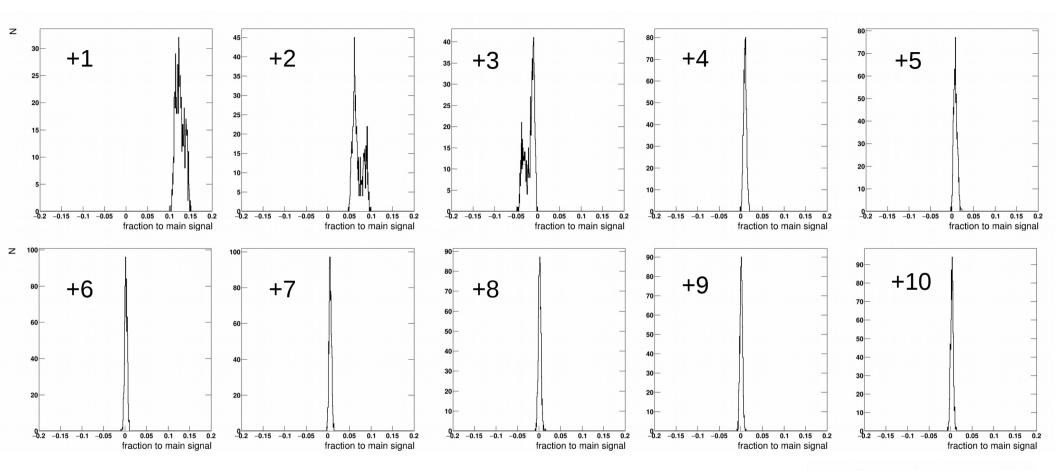

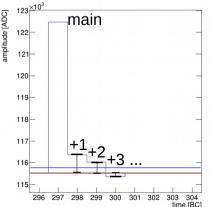

# **Deconvolution of ringing**

- Signal to baseline extrapolation difference

- For bunches following the main signal

- Plotted as a fraction of the main signal

- Sampling phase effects observed

Jiri Kral for BI/TB on VFC

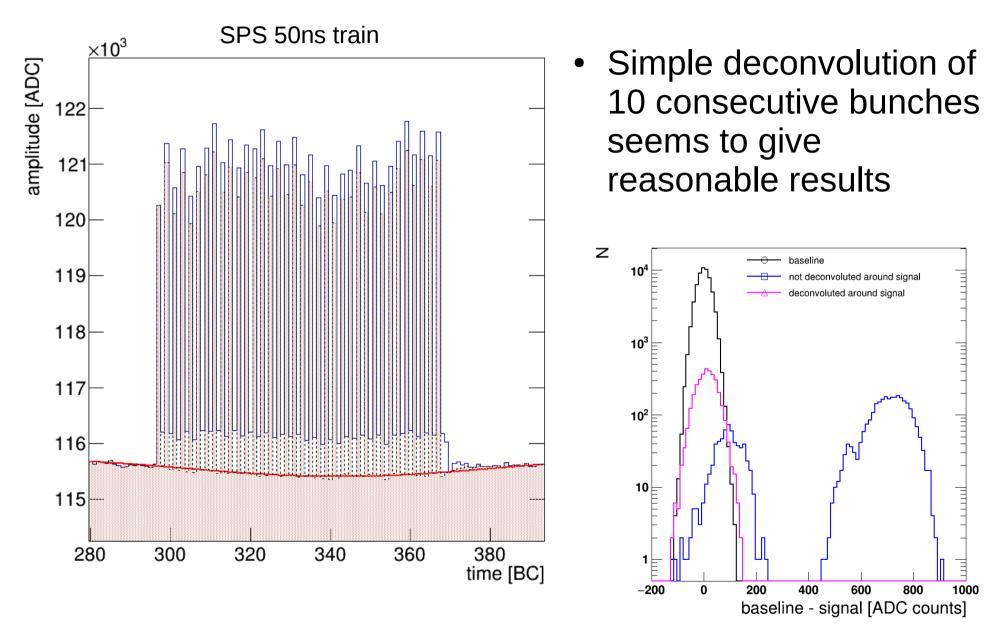

## **Deconvolution application**

### Near future

- Try to understand the oscillating baseline

- Not hurrying to implement subtraction in FPGA, since the effect might be specific to the temporarily used setup

- Adapt FPGA code for 2 parallel ADC channels

- Running single channel code so far

- Prepare FPGA code for frequency increase to 1 GSPS

- Requires parallelization, since the FPGA fabric can not work with 250 MHz frame clock

- Write documentation

- Calibration setup preparation

# Already existing outputs

- Arria V GX example project with AD9680 dev board showing JESD204B core implementation

- Development versions of Arria V GX project with AD9680 dev board or FMC-1000 implementing the whole functionality

- Preliminary register/memory map

- Basic python scripts to configure/pull data