# P-spray implant optimization for p-type microstrip detectors -Status of the RD50 calibration run-

#### <u>C. Fleta</u>, M. Lozano, G. Pellegrini, K. Vatter, F. Campabadal, J. M. Rafí and M. Ullán

Instituto de Microelectrónica de Barcelona IMB-CNM (CSIC) Spain

3th June 2005

## Background

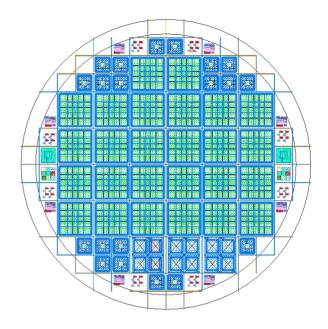

- IMB-CNM to process wafers for the Collaboration

- P-in-N and N-in-P

- Mask set designed by RD50

- Insulation between strips provided only by p-spray (no p-stops)

- Optimize the p-spray parameters before processing the RD50 wafers

- Complete simulation process (ISE-TCAD)

Test run to check simulation results

Wafer 1: 25 keV,  $10^{12}$  cm<sup>-2</sup>Wafer 4: 30 keV,  $10^{12}$  cm<sup>-2</sup>Wafer 2: 25 keV,  $1.4x10^{12}$  cm<sup>-2</sup>Wafer 5: 35 keV,  $10^{12}$  cm<sup>-2</sup>Wafer 3: 25 keV,  $2x10^{12}$  cm<sup>-2</sup>Wafer 6: 45 keV,  $10^{12}$  cm<sup>-2</sup>

P-spray implant oxide thickness = 150 nm

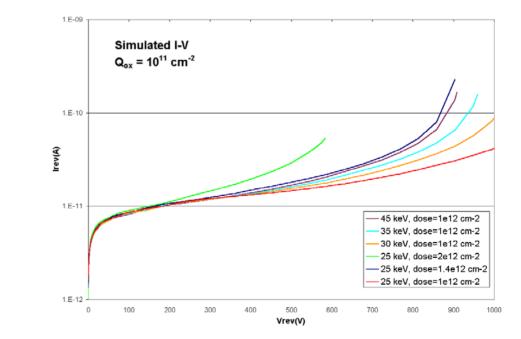

## Simulations: I-V

|         | P-spray                                       | B peak (cm <sup>-3</sup> ) | B total (cm <sup>-2</sup> ) | V <sub>BD</sub> (V) |

|---------|-----------------------------------------------|----------------------------|-----------------------------|---------------------|

| Wafer 1 | 25 kev, 10 <sup>12</sup> cm <sup>-2</sup>     | 3.80×10 <sup>15</sup>      | 3.01×10 <sup>11</sup>       | > 1000              |

| Wafer 2 | 25 kev, 1.4×10 <sup>12</sup> cm <sup>-2</sup> | 5.32×10 <sup>15</sup>      | 4.22×10 <sup>11</sup>       | 900                 |

| Wafer 3 | 25 kev, 2×10 <sup>12</sup> cm <sup>-2</sup>   | 7.59×10 <sup>15</sup>      | 6.02×10 <sup>11</sup>       | 580                 |

| Wafer 4 | 30 kev, 10 <sup>12</sup> cm <sup>-2</sup>     | 4.13×10 <sup>15</sup>      | 3.56×10 <sup>11</sup>       | > 1000              |

| Wafer 5 | 35 kev, 10 <sup>12</sup> cm <sup>-2</sup>     | 4.30×10 <sup>15</sup>      | 3.85×10 <sup>11</sup>       | 960                 |

| Wafer 6 | 45 kev, 10 <sup>12</sup> cm <sup>-2</sup>     | 4.44×10 <sup>15</sup>      | 4.09×10 <sup>11</sup>       | 910                 |

V<sub>BD</sub> decreases as implanted dose increases

Simulations: strip insulation

Inversion layer at full depletion?

- Higher p-spray doses to avoid surface inversion on heavily irradiated devices, but V<sub>BD</sub> decreases

- Compromise solution

- Strip insulation is not the major concern in irradiated detectors

- More complete simulations needed

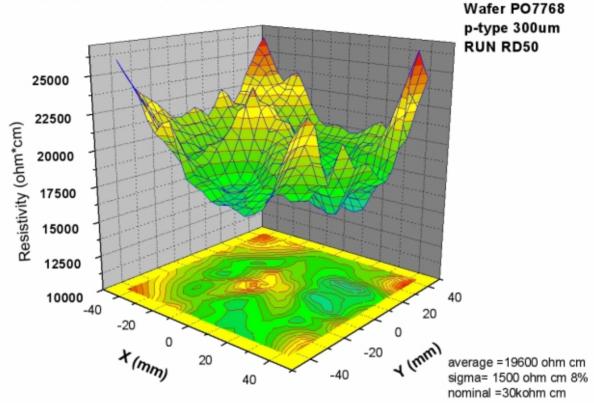

#### Wafer characteristics

- New wafers from Siltronic

- <100>, p-type, 300 ± 15 μm

- **D**  $\rho$  (nominal) = 30 kΩ.cm,  $\rho$  (measured) = 20 kΩ.cm

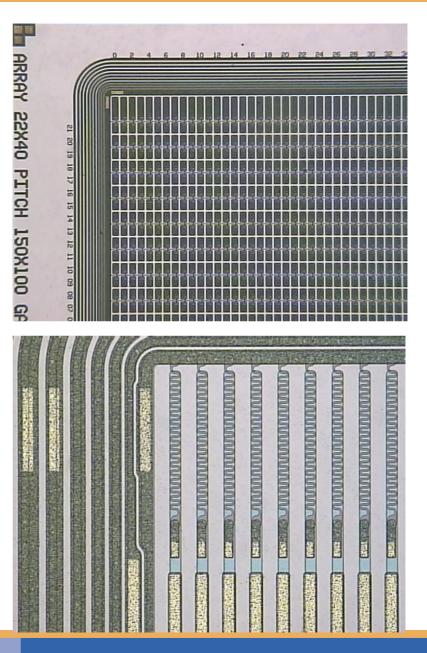

## Fabricated devices

#### **Electrical characterization**

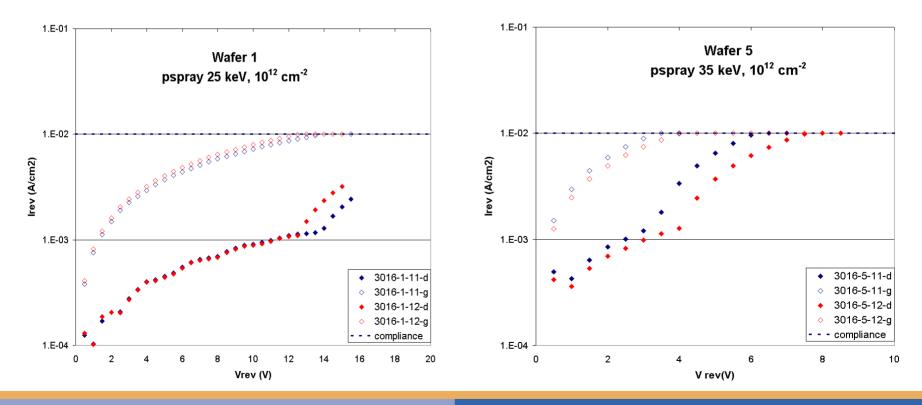

- Microstrips of wafers 1 to 5:

- Very high leakage currents (mA/cm<sup>2</sup> @ 10 V)

- Do not fulfill the requirements for radiation detectors

## **Electrical characterization**

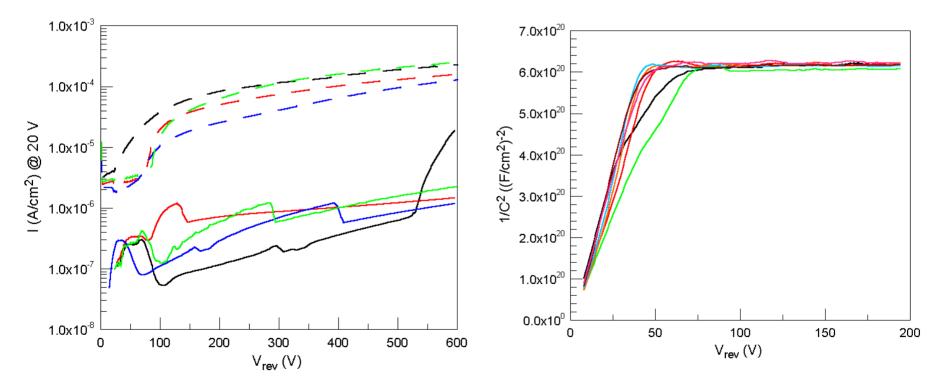

- Wafer 6

- Leakage current ~ μA/cm<sup>2</sup>

- V<sub>BD</sub> > 600 V

- $V_{FD} = 46 \pm 5 \text{ V} \rightarrow \rho = 17 \pm 2 \text{ k}\Omega.cm$

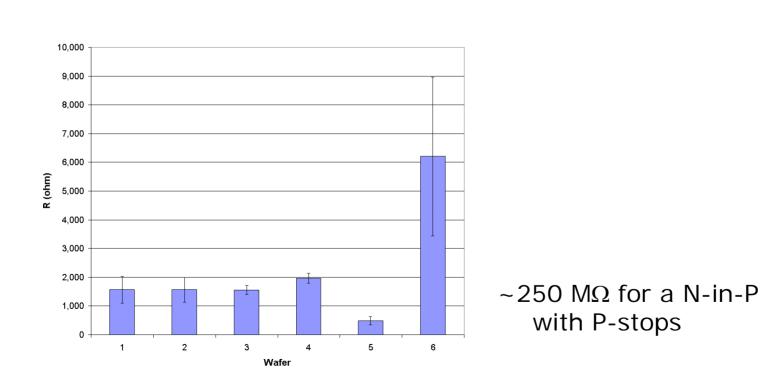

### **Electrical characterization**

- Verify strip insulation

- Measurement of the resistance between two consecutive microstrips

Surface is clearly inverted

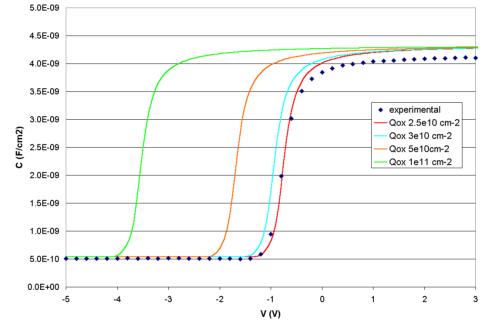

#### Oxide charge measurement

Simulated devices:  $Q_{ox} = 10^{11} \text{ cm}^{-2}$ . Overestimated oxide quality?

- C-V measured in test structure (MOS capacitor)

- Agreement with the simulated curve for Q<sub>ox</sub> = 2.5x10<sup>10</sup> cm<sup>-2</sup>

- Another reason for the bad electrical performance

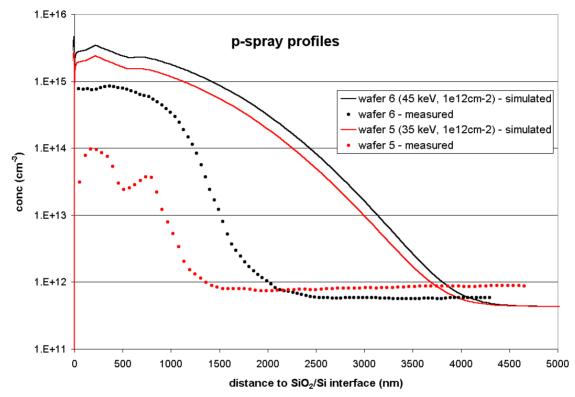

## Spreading resistance measurements

Total implanted dose lower than the predicted by simulations

- Wafer 6: 70% of the expected dose

- Wafer 5: 9%

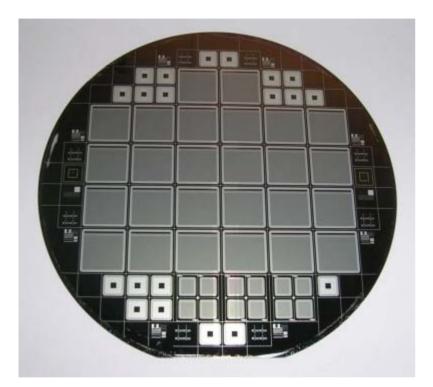

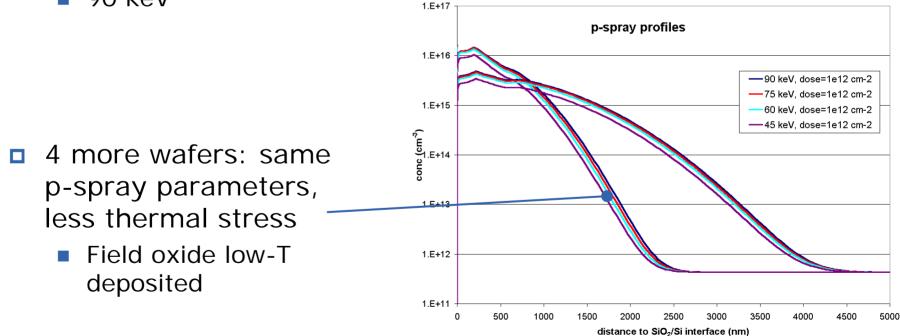

### Second calibration run

Higher implant energies with the lowest dose (10<sup>12</sup> cm<sup>-2</sup>)

- 45 keV (= wafer 6)

- 60 keV

- 75 keV

- 90 keV

## Second calibration run

- Defective wafers from Siltronic

- P-spray implant oxide thicker in some areas (irregular wafer surface)

- Will affect the implant profile

- Could this be the reason for the bad results of the previous run?

- Wafers from the same provider but a different batch

- Did not detect anything unusual during the first process

### Conclusions

- Calibration runs to optimize the p-spray implant parameters in N-in-P detectors

- First run: p-spray profiles lower than expected

- Implantation doses near the technical limit of the ion implanter. Calibration error?

- Wrong predictions by process simulator?

- Defective wafers?

- **□** ...?

- Second run:

- Oxide thickness not uniform due to irregular wafer surface

- Still not finished

- What we have learnt so far...

- Not sure of the suitability of the p-spray for heavily irradiated devices

- Compromise between reasonable V<sub>BD</sub> and good strip insulation

- More complete studies needed

- P-spray seems to be very sensitive to fabrication details

- Alternative technologies?