# **(On-line) Data Processing for the EU-DET, MAPS based Beam Telescope Demonstrator**

W. Dulinski IReS, 23 rue du Loess BP 28, 67037, Strasbourg Cedex 02, France

### Outline

• The goal for the DAQ in 2006 (my personal point of view)

- Minimum data processing during acquisition

- DAQ example based on existing acquisition cards

- Conclusions

# DAQ Requirements for the Beam Telescope Demonstrator: to be discussed and agreed on

- Continuous data taking: no dead time

- Real-time (in-flight) zero suppression

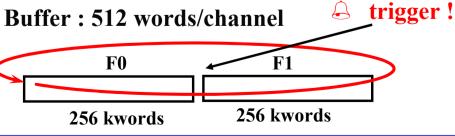

- Acquisition cards: ADC + FPGA + two-frames data memory + buffer (hit) memory

- Common interface for the PC

- Sensitive area selection based on internal data?

- On-line track reconstruction?

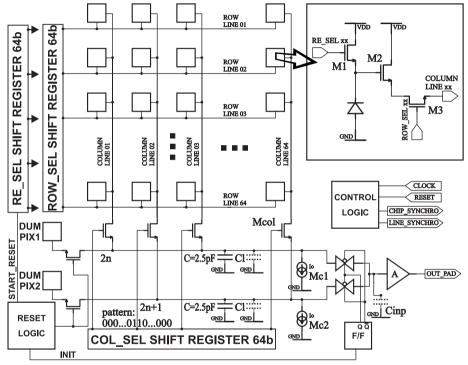

## The simplest readout electronics (Mimosa5): diode + 3 transistors/pixel

Fast ADC 12 bits

- 1. Reset in order to inverse bias

- 2. Continuous serial addressing and readout (digitisation) of all pixels

- 3. Keeping two successive frames in external circular buffer

- 4. Following reset when needed (removing integrated dark current)

- 5. After trigger (or in a real time)), simple data processing in order to recognise hits

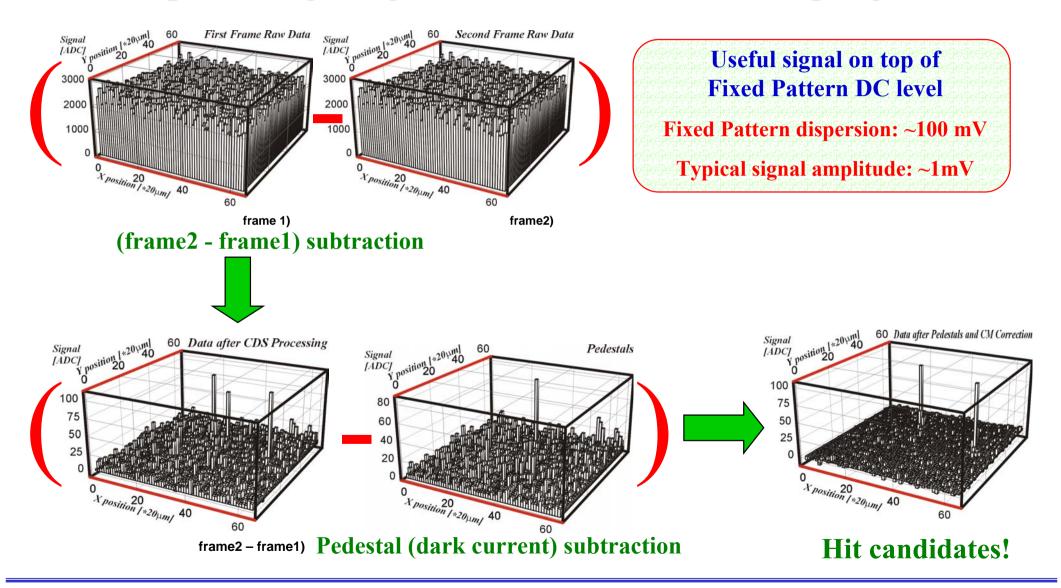

## **Data processing: (Digital) Correlated Double Sampling (CDS)**

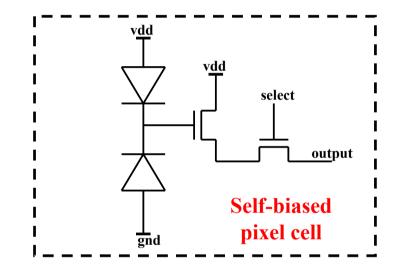

## **MimoSTAR case: self-biasing**

- NO Reset (only synchronisation pulse at the beginning)

- NO pedestal (dark current) correction

- NO Common Mode correction???

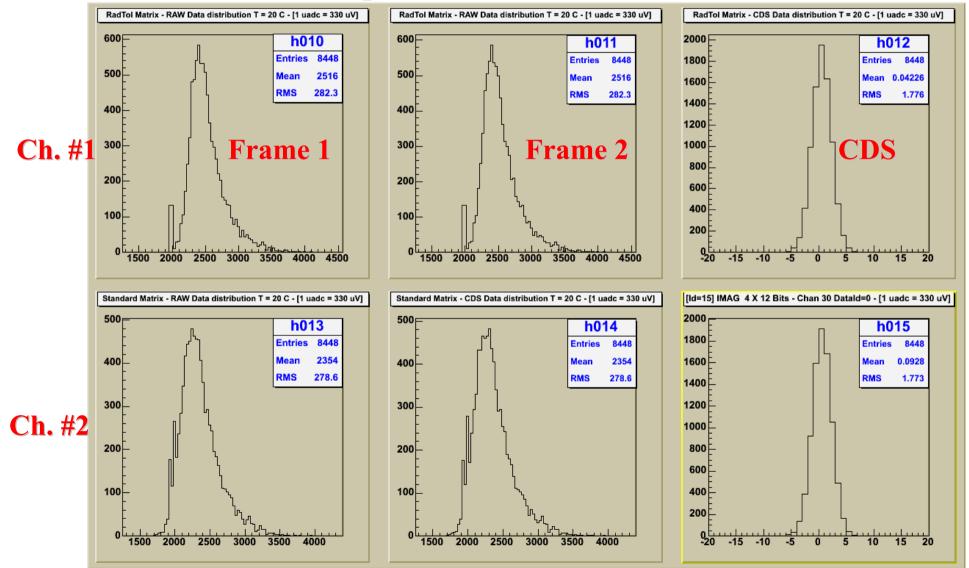

## **Raw data examples from MimoSTAR 2 (ADC counts)**

7

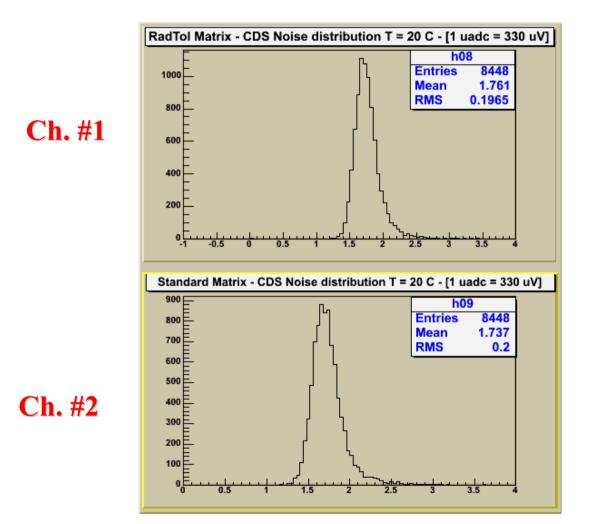

## **Raw noise distribution**

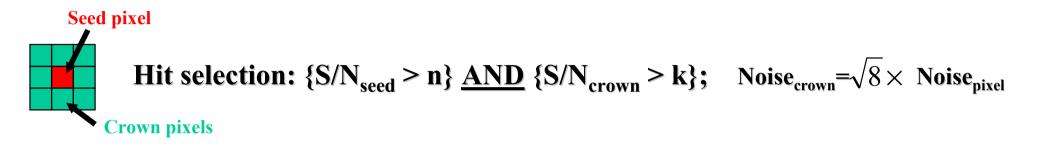

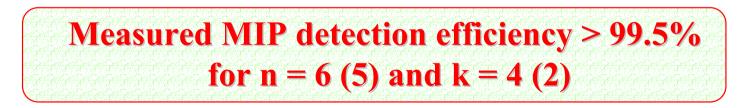

## Mimosa9 beam tests: efficiency, noise hit rejection

## For n = 4 and $k = 2 \rightarrow$ noise hit rejection should be $> 10^6$ that's about what we measure...

Noise safety factor of 2 ÷ 2.5, before efficiency drops...

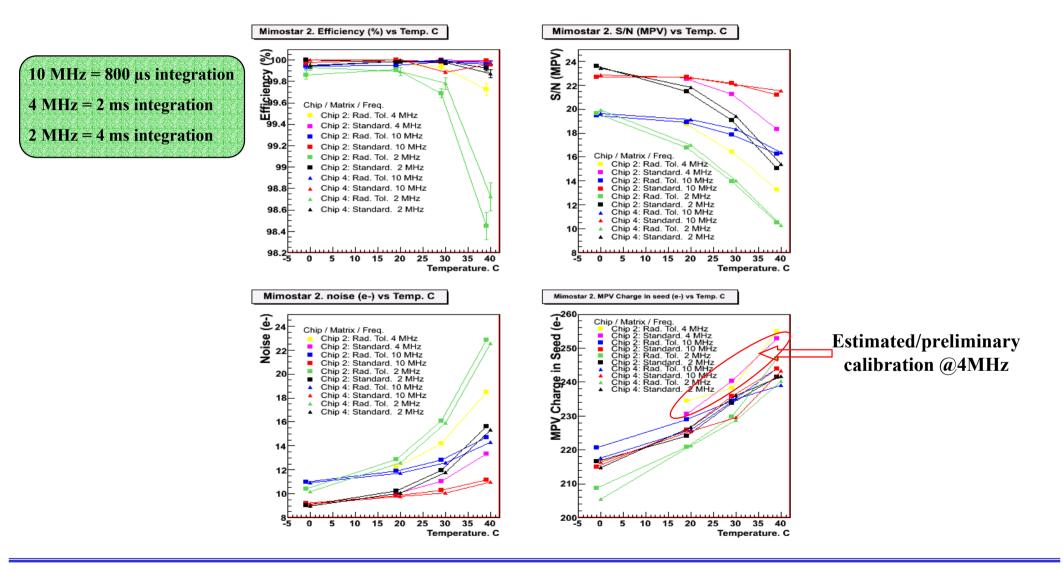

### **MimoSTAR2 beam tests summery**

## Minimum on-line data processing: data flow estimation

No data reduction:

10<sup>5</sup> pixels × 4 ref. planes × 2 bytes × 1 kframes/s = 0.8 Gbytes/s Quite a lot!!!

Zero suppression:

4 clusters × 10 pixels × 4 ref. planes × 4 bytes (address and CDS) × 1 kframes/s = 640 kbytes/s Much better! (three orders of magnitude less)

Sparsification: 4 clusters × 4 ref. planes × 8 bytes (x and y position, amplitude ) × 1 kframes/s = 128 kbytes/s Factor five less

Full track reconstruction:2 tracks × 12 bytes (x, y,  $\theta$ ,  $\phi$ ,  $\chi^2$ ) × 1 kframes/s = 24 kbytes/sAnother factor five less

## Minimum amount of calculation for zero-suppression in FPGA, supposing pipelining (one operation per 50 ns clock cycle)

- 1. Read from ADC (frame n)

- 2. Read from memory (frame n-1), write to memory (frame 2)

- 3. CDS: frame (n) frame (n-1)

- 4. CDS threshold

- 5. Decision

- 6. Neighbors selection

- 7. Address and amplitude coding

- 8. Transmission to the buffer memory (FIFO?)

What with the common mode correction? Really needed? Possible on the basis of data from one row?

**Expert needed in order to estimate the minimum FPGA resources!**

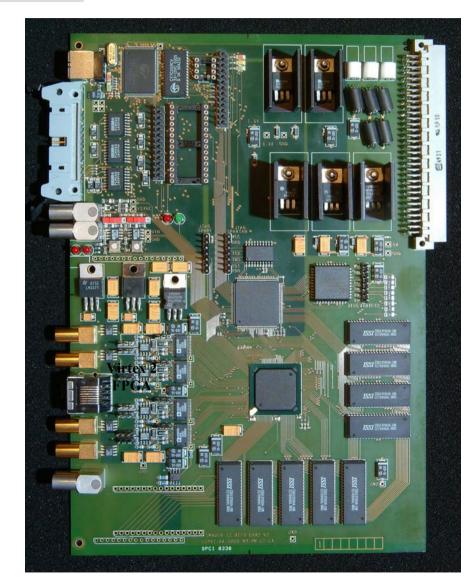

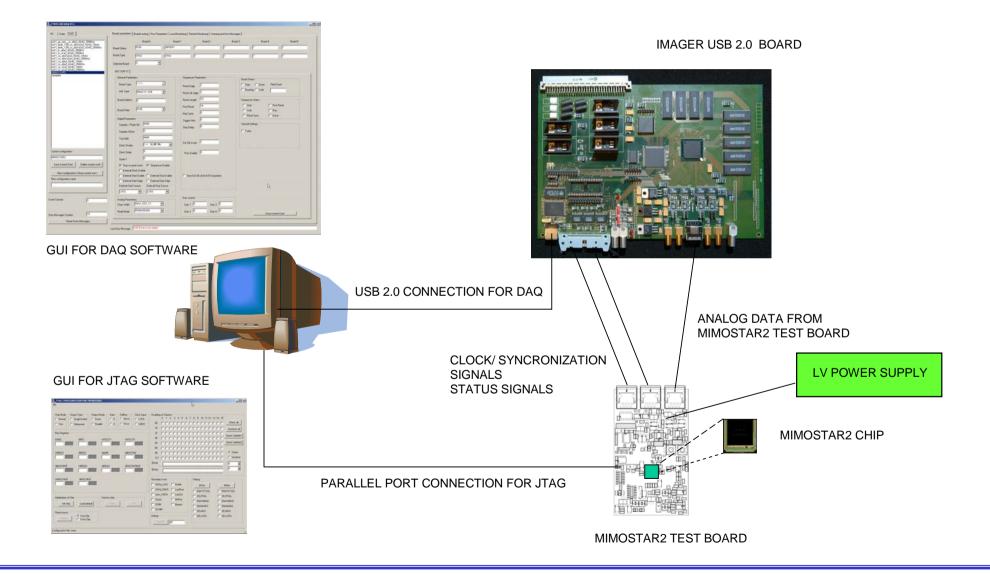

## The DAQ system: examples from existing (@IReS) device

• Present system based on VME boards: 4-channel, 12 bit, 40 MHz ADC, FPGA XC4000, 4Mby RAM for digital conversion, zero- suppression implemented and tested @10 MHz several years ago (by Pawel Jaloha) but never used in practice

• Soon replaced by USB boards: 4-channel, 12 bit, 50 MHz ADC, FPGA Virtex2, 4Mby RAM for digital conversion AND sparsification (to be implemented)

### DAQ workshop, Geneva, December 2005

#### DAQ USB 2.0

### Analog

- · 4 ADC 12 bits 40 Mhz

- · 10<sup>6</sup> pixels **shared** 1-4 Inputs

### Digital

- · Pattern generator & Trigger

- 12 Digital I/O: 8 LVDS and 4 NIM (2 In, 2 Out)

### Daq

· Transfer 15 MB/ s USB 2.0

### Firmware ( To Be Done )

- · CDS Calculation ( Done )

- · Pedestal subtraction

- · Data sparsification

## Minimum set-up to run MimoSTAR sensor

# **Conclusions and prospects**

If the DAQ specification agreed on, the development may start soon!

Should it be based on existing boards? If not, what will be effect on the schedule?

We must also soon discuss and agree on the Sensor/DAQ Interface (mechanics, electric standards, protocol)

The final DAQ for digitally readout sensors should be the logical evolution of the Demonstrator DAQ!