# Silicon Pixel R&D for CLIC

38<sup>th</sup> International Conference on High Energy Physics (ICHEP 2016)

August 3-10, 2016 Chicago

Dominik Dannheim (CERN)

on behalf of the

CLIC detector and physics (CLICdp) collaboration

### **Outline**

- CLIC vertex- and tracking detector requirements

- Hybrid pixel-detector assemblies with:

- thin planar sensors

- small-pitch planar sensors

- small-pitch active sensors

- Integrated CMOS pixel sensors

- Summary / Conclusions

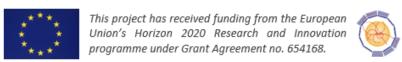

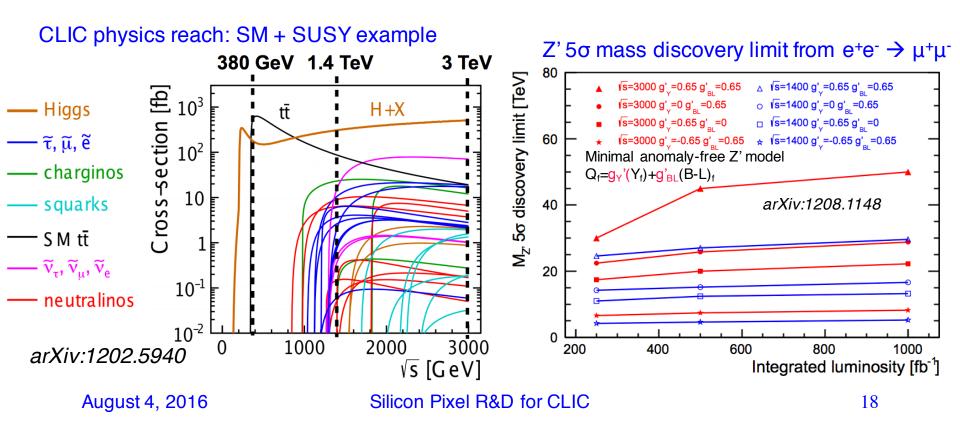

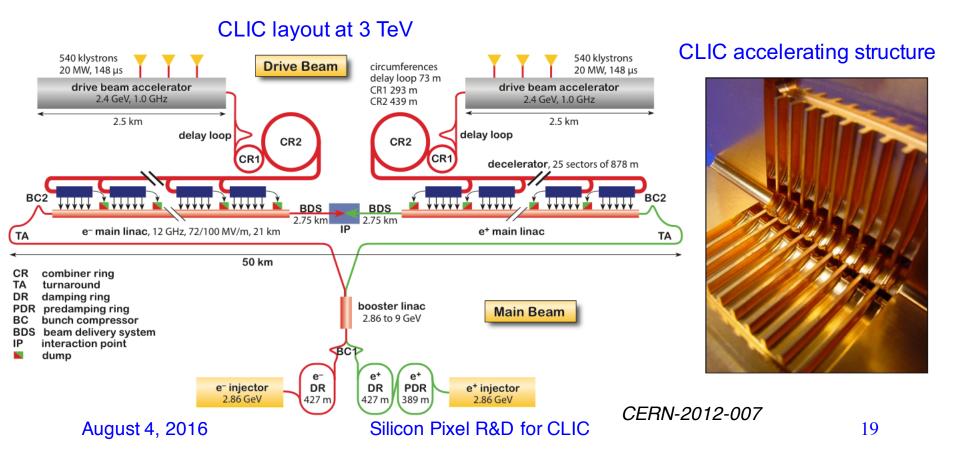

#### CLIC

- •CLIC (Compact Linear Collider): linear e+e- collider concept for post HL-LHC phase

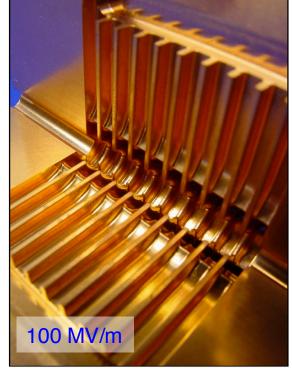

- •√s from few hundred GeV up to 3 TeV (two-beam acceleration with ~100 MV/m)

- •Physics goals:

- Precision measurements of SM processes (Higgs, top)

- Precision measurements of new physics potentially discovered at 14 TeV LHC

- •Search for new physics: unique sensitivity to particles with electroweak charge

#### Possible staged CLIC implementation near CERN

CLIC accelerating structure

August 4, 2016

Silicon Pixel R&D for CLIC

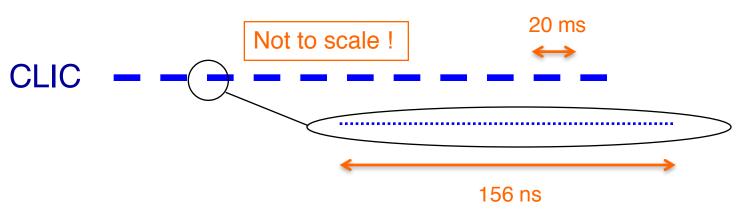

### CLIC vertex-detector and tracker requirements

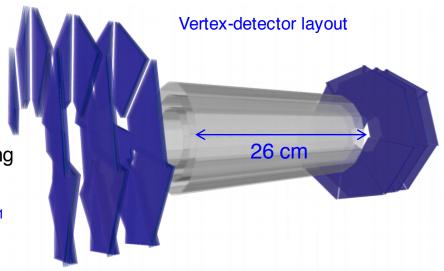

#### Vertex detector:

- efficient tagging of heavy quarks through precise determination of displaced vertices:

- $\rightarrow$  good single point resolution:  $\sigma_{SP}\sim3 \mu m$

- → small pixels <~25x25 µm², analog readout

- → low material budget:  $X \lesssim 0.2\% X_0$  / layer

- → low-power ASICs (~50 mW/cm²) + gas-flow cooling

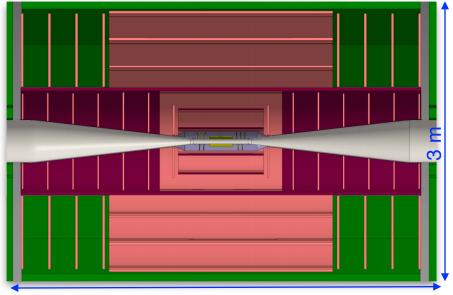

#### Tracker:

- Good momentum resolution: σ(p<sub>T</sub>) / p<sub>T</sub><sup>2</sup> ~ 2 x 10<sup>-5</sup> GeV<sup>-1</sup>

- → 7 μm single-point resolution (≲50 μm pitch)

- → many layers, large outer radius (~90 m² surface)

- → ~1-2% X0 per layer

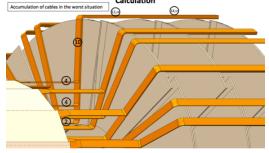

- → low-mass supports + services

#### Both:

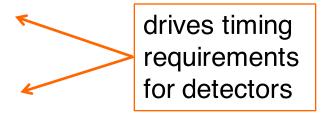

- 20 ms gaps between bunch trains

- → trigger-less readout, pulsed powering

- <u>few % maximum occupancy from beam backgrounds</u>

- → sets inner radius and limits cell sizes

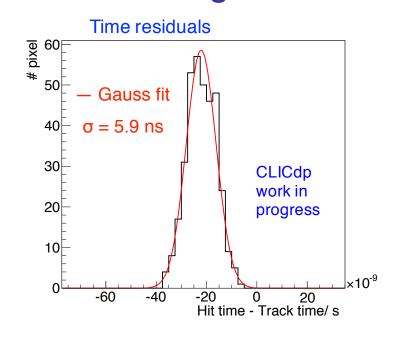

- → time stamping with ~10 ns accuracy

- → depleted sensors (high resistivity / high voltage)

- moderate radiation exposure (~10<sup>4</sup> below LHC!):

- NIEL:  $< 10^{11} \text{ n}_{eq}/\text{cm}^2/\text{y}$

- TID: < 1 kGy / year</li>

Tracker layout

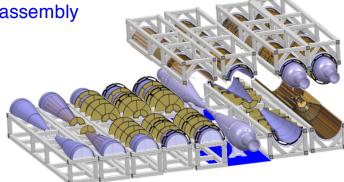

### Vertex and tracker technology R&D

#### Sensors

#### Interconnects

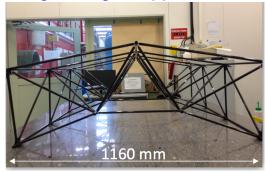

#### Light-weight supports

#### Readout ASICs

#### **Powering**

#### Simulations

#### Cooling

- Integrated R&D effort, simultaneously addressing CLIC vertex+tracking detector challenges

- Examples of recent developments on the following slides (focus on sensors & readout)

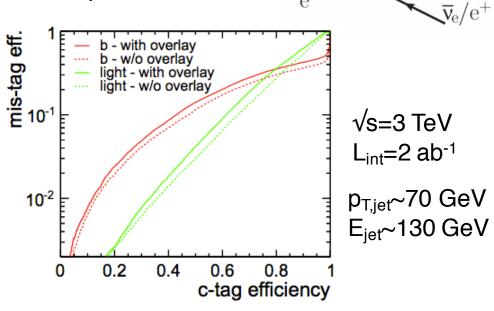

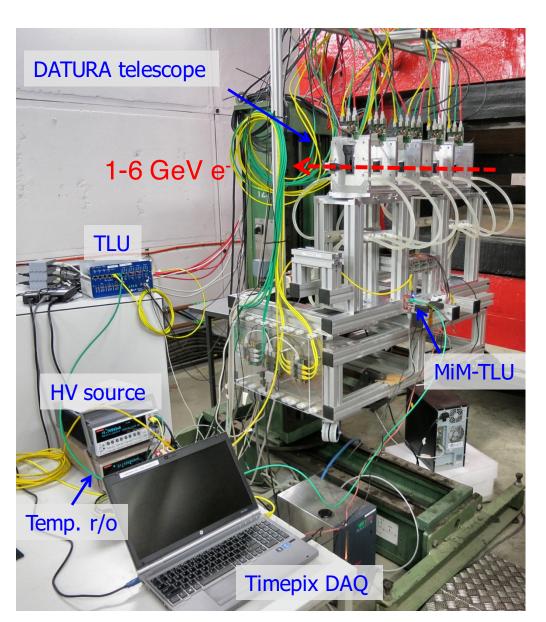

#### Test-beam data taking

#### **EUDET/AIDA telescopes**:

- Used for initial test-beam studies at DESY II, CERN PS and CERN SPS

- Rolling-shutter r/o over ~230 μs

→ limited rate and timing capabilities

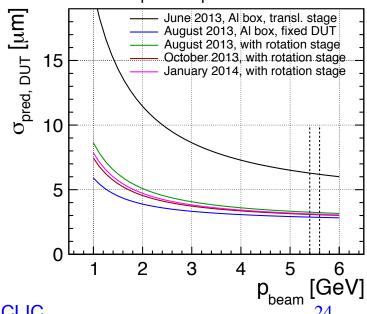

- Pointing resolution at DUT ~1.6-3 μm

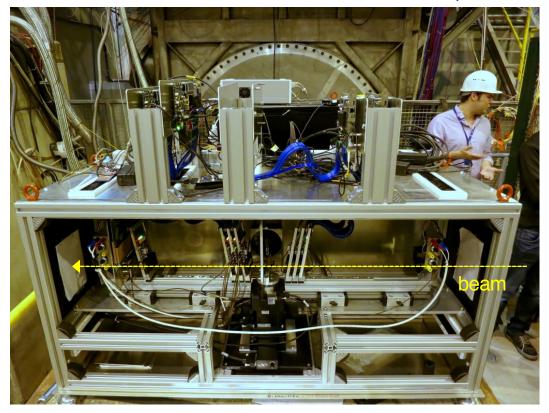

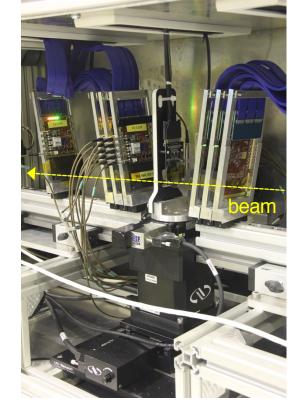

#### CERN-LCD Timepix3 telescope:

- Permanent installation at CERN SPS H6B

- Movement and rotation stages for automatic scans

- High rate: up to 10M particles / s

- Track timing with <2 ns accuracy</li>

- Track pointing resolution at DUT ~2 μm

#### CERN-LCD Timepix3 telescope in SPS H6B

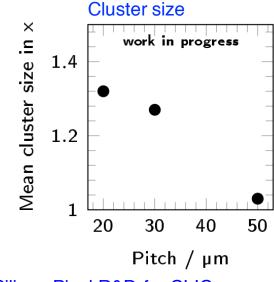

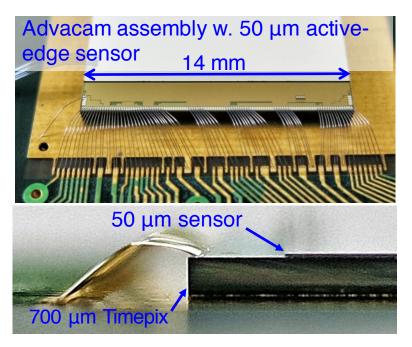

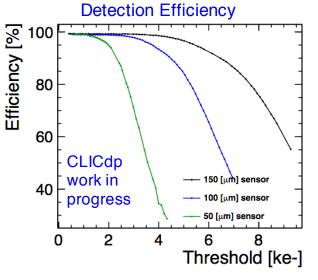

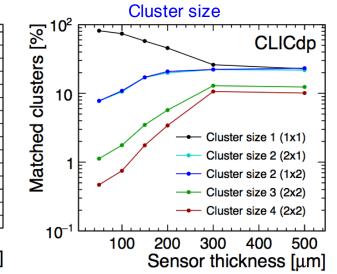

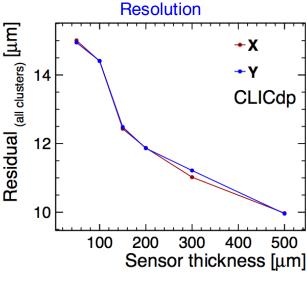

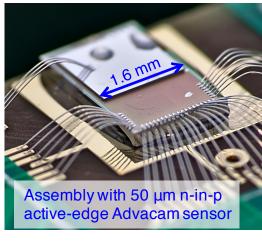

#### Thin sensor test-beam results

- Test-beam measurements of Timepix/Timepix3

assemblies (Micron, Advacam) with different

sensor thicknesses, 55 μm pixel pitch

- Goal: test feasibility of ultra-thin sensors with minimized inactive regions

- High detection efficiency (>99%) under normal operating conditions, even for 50 µm sensors

- Resolution limited by single-pixel clusters

- → worse resolution for thinner sensors

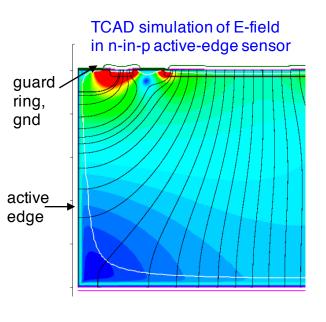

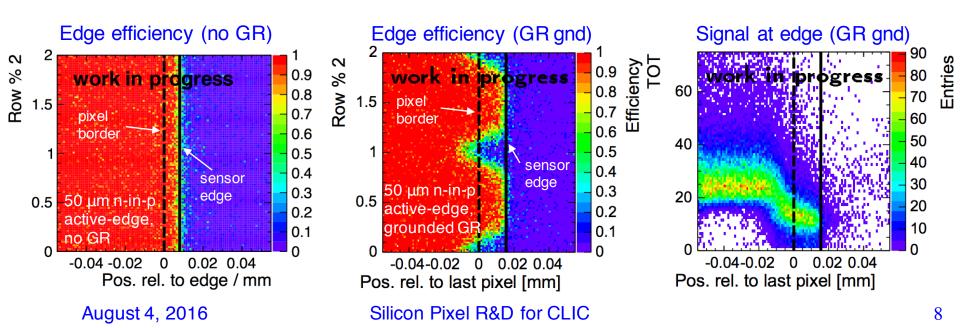

### Active edge sensors

- Deep Reactive Ion Etching (DRIE) process:

- Implantation on the sensor sidewalls: extension of the backside electrode to the edge

- Efficiency extends to the physical edge

→ allows for seamless tiling of sensors

- Comparing different edge layouts:

w/o guard ring (GR), floating GR and grounded GR

→ signal loss to GR for very thin sensors,

in agreement with TCAD simulations

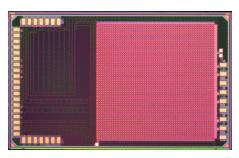

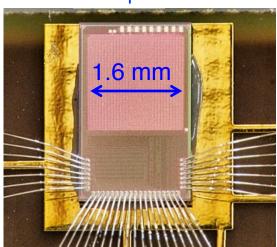

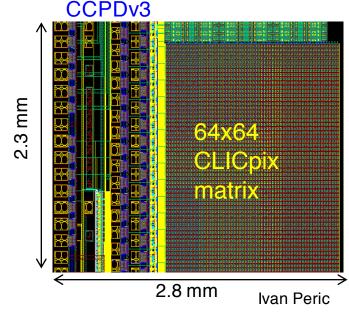

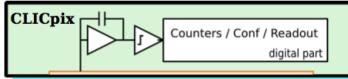

#### Hybrid r/o technology: CLICpix

crc

- 65 nm CMOS hybrid r/o chip, targeted to CLIC vertex detectors

- based on Timepix/Medipix chip family,

- demonstrator chip: 64 x 64 pixel matrix

- 25 µm pixel pitch

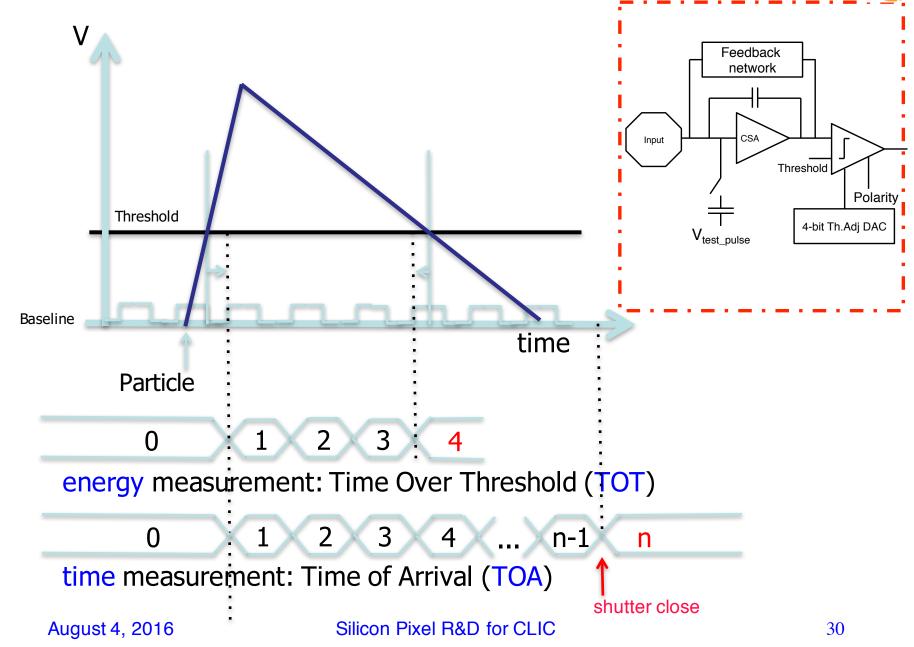

- simultaneous 4-bit time (ToA) and energy (ToT) measurement per pixel

- → front-end time slicing < 10 ns

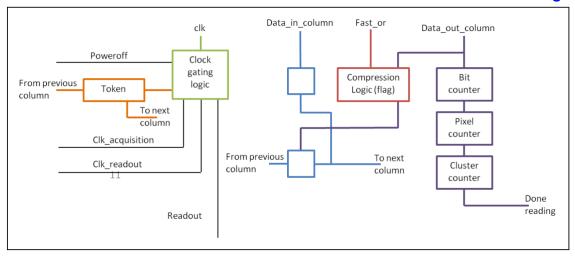

- selectable compression logic: pixel, cluster + column-based

- full chip r/o in less than 800 μs (at 10% occup., 320 MHz r/o clock)

- power pulsing scheme

- $\rightarrow$  P<sub>avg</sub>< 50 mW/cm<sup>2</sup>

- lab measurements

- → performance in agreement with simulations

- test assemblies with planar and active HV-CMOS sensors

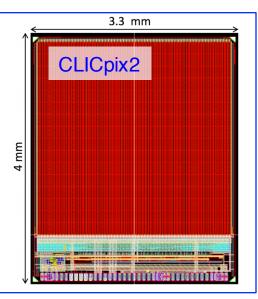

#### New version CLICpix2:

- 128x128 pixels

- 5 bit ToT, 8 bit ToA

- Improved I/O

- design currently under validation (UVM)

- to be submitted in coming weeks

LCD-Note-2012-018

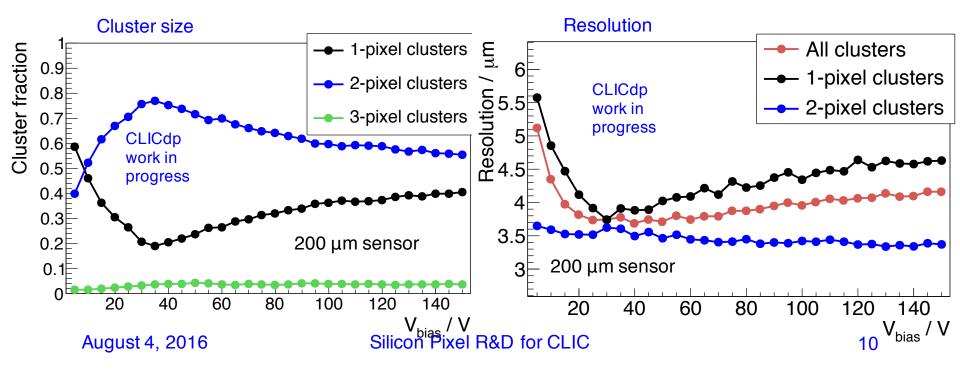

#### CLICpix planar sensor assemblies

- Single-chip bump-bonding process for 25 μm pitch developed at SLAC (C. Kenney, A. Tomada)

- Results for 3 test assemblies with 200  $\mu m$  Micron sensors :

- 0.2-3% unconnected channels

- 1-2% shorted channels

- Test-beam measurements:

- Operation threshold ~1000 e<sup>-</sup>, V<sub>dep</sub>~35 V

- High detection efficiency (>99.5%)

- ~20% single-pixel clusters at V<sub>dep</sub>

- ~4 μm single-point resolution

- Validation of assembly with 50 μm Advacam active-edge sensor ongoing

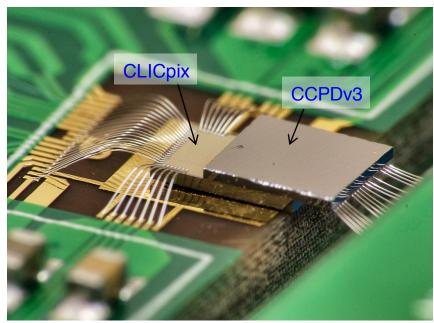

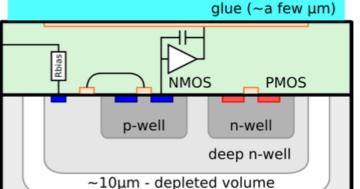

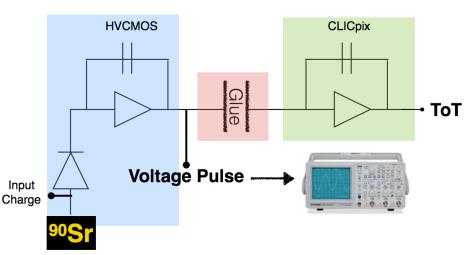

### HV-CMOS active sensor with capacitive coupling

#### **Capacitive Coupled Pixel Detector (CCPD)**

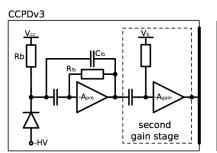

- Prototype for ATLAS (FEI4) and CLIC: CCPDv3

- Commercial 180 nm High-Voltage-CMOS process

- V<sub>bias</sub>~30-90 V → depletion layer ~10-20 μm

- 2-stage amplifier, capacitive coupling to readout ASIC through thin glue layer (few μm)

- Includes 64x64 matrix (25 μm pitch)

- glue assemblies with CLICpix readout chips

- → lab and test-beam results (next slide)

- new improved chip version C3PD matching CLICpix2

- → chip functional, lab tests ongoing

Nucl. Instrum. Meth. A731 (2013) 131

Nucl. Instrum. Meth. A823 (2016) 1

CCPDv3

p-substrate

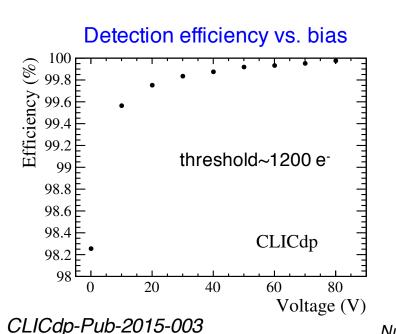

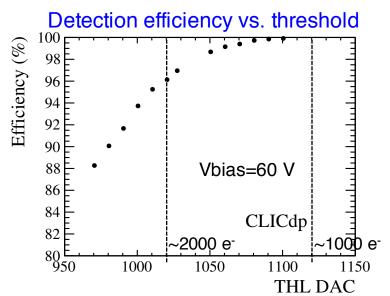

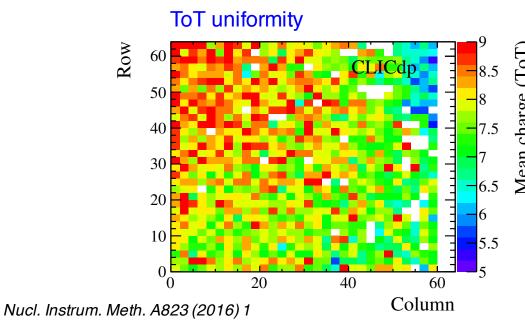

### CLICpix+CCPDv3 test-beam results

#### CERN SPS test beam with AIDA telescope:

- High detection efficiency, even without bias (diffusion)

- Measured mean charge (ToT)

varies across matrix

→ non-uniformity of glue thickness,

observed in early assemblies

produced without control of planarity

- ~6 μm single-point resolution

Silicon Pixel R&D for CLIC

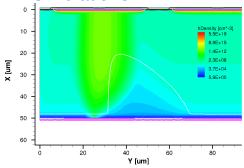

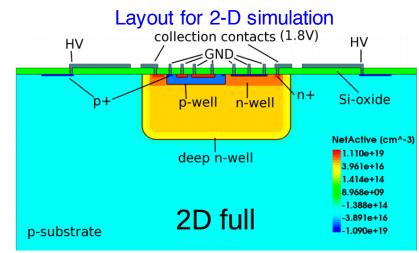

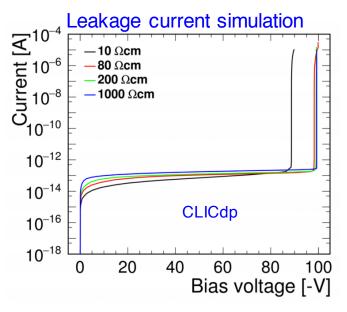

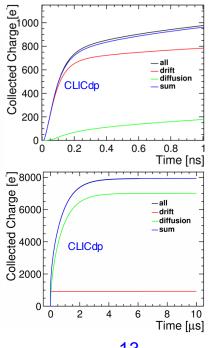

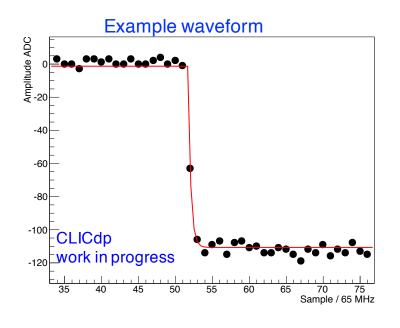

#### **HV-CMOS TCAD simulation**

- Implemented CCPDv3 pixel layout in TCAD

- 2-D and 3-D transient simulation for MIPs at different positions within pixel → input for ASIC simulation

- Measured leakage current breakdown of ~90 V well reproduced

- Fast rise of collected charge within ~ns (drift in depleted volume)

- Increasing pulse height over hundreds of ns (diffusion in bulk)

CLICdp-Note-2016-004

0.08

Time [µs]

MIP response in CCPDv3

**CLICdp**

0.04

0.06

Silicon Pixel R&D for CLIC

0.02

all

drift

sum

diffusion

<u>\$2500</u>

2000

1500

1000

500

0

Charge

Collected

August 4, 2016

### Integrated CMOS technologies for tracker

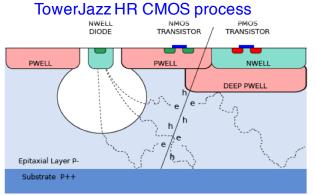

#### TowerJazz 180 nm High-Resistivity CMOS:

- Quadruple well process with full CMOS: n-wells shielded by deep p-wells

- 15-40 µm / 1-8 kΩcm epitaxial layer, not fully depleted (Vbias ≤ 6 V)

- ALICE Investigator analog test chip

- Pixel sizes: 20x20 to 50x50 μm²

- Optimization of collection-diode geometry to minimize capacitance (~2 fF)

- Readout with external sampling ADCs

- Integration in CLIC test-beam setup

→ good time resolution obtained (few ns)

W. Snoeys et al. NIM A 765 (2014) 177

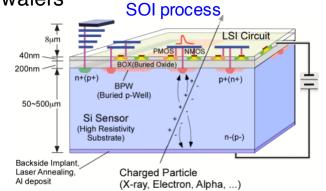

#### Lapis 200 nm SOI:

- CMOS sensor on Silicon On Insulator (SOI) wafers

- Electronics on low resistivity wafer, separated by buried oxide from fully depleted high-resistivity sensing layer

- Test-chip from AGH Cracow:

- Different pixel sizes (≥ 30 x 30 μm²)

- Targeted towards CLIC requirements (position, amplitude and few ns timing)

- Integration in CLIC test-beam setup

- → chip functional, data taking and analysis ongoing

arXiv:1507.00864

### **Summary and Conclusions**

- CLIC accelerator provides:

- unique potential for discovery and precision physics at the TeV scale

- challenging requirements for vertex and tracking detectors

- Ongoing integrated R&D program on CLIC vertex + tracking detectors:

- Sensor and readout technologies for precision measurements:

- Hybrid readout ASICs with planar sensors

- Hybrid readout ASICs with active HV-CMOS sensors

- Integrated CMOS sensors

- Not shown today: powering, cooling and mechanical integration studies incorporating realistic constraints

Thanks to everyone who provided material for this talk!

### Additional material

# CLIC detector & physics collaboration

- •The CLICdp collaboration is addressing detector and physics issues for the future Compact Linear Collider (CLIC) <a href="http://clicdp.web.cern.ch/">http://clicdp.web.cern.ch/</a>

- •CERN acts as host laboratory

- •Currently 27 institutes from 17 countries

- •The CLIC accelerator R&D is being conducted in collaboration with  $\sim\!48$  institutes

### **CLIC** physics program

- •CLIC (Compact Linear Collider): linear e+e- collider concept for post HL-LHC phase

- •Staged construction: √s from few hundred GeV up to 3 TeV

- •Physics goals:

- Precision measurements of SM processes (Higgs, top)

- Precision measurements of new physics potentially discovered at 14 TeV LHC

- Search for new physics: unique sensitivity to particles with electroweak charge

#### **CLIC** accelerator

- Linear e<sup>+</sup>e<sup>-</sup> collider

- 2-beam acceleration scheme, operated at room temperature

- Gradient: 100 MV/m

- √s up to 3 TeV

- Luminosity: 6 x 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> (at 3 TeV)

- Physics + Detector studies for 350 GeV 3 TeV

# Machine parameters

|                                       | LHC at<br>14 TeV   | CLIC at<br>3 TeV   |

|---------------------------------------|--------------------|--------------------|

| L (cm <sup>-2</sup> s <sup>-1</sup> ) | 1x10 <sup>34</sup> | 6×10 <sup>34</sup> |

| BX separation                         | 25 ns              | 0.5 ns             |

| #BX / train                           | N/A                | 312                |

| Train duration                        | N/A                | 156 ns             |

| Train repetition                      | N/A                | 50 Hz              |

| Duty cycle                            | ~1                 | 0.00078%           |

| $\sigma_x$ / $\sigma_y$ [nm]          | 15000 / 15000      | ≈ 45 / 1           |

| $\sigma_z$ [ $\mu$ m]                 | ~50000             | 44                 |

very small beam sizes at interaction point

•low-mass vertex detector with ~25x25 μm² pixels

silicon tracker

•fine-grained **PFA**calorimetry,

1+7.5 Λ<sub>i</sub>

W-ECAL + Fe-HCAL

•4 T solenoid

•return yoke with muon ID

•Complex instrumented forward region

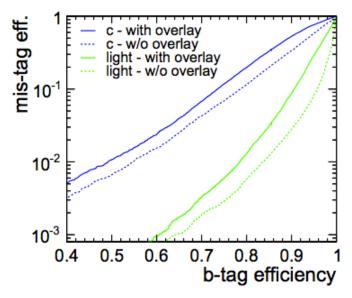

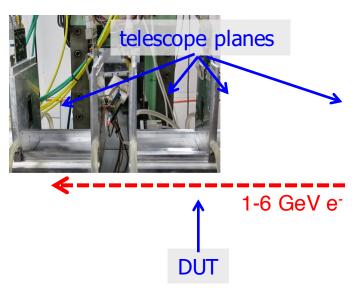

### Flavor tagging: impact on physics performance

- e<sup>+</sup>e<sup>-</sup> → Hvv: dominating Higgs production process at √s=3 TeV

- $\sigma \times BR$  measurement for the decays to bb and cc

- flavor tagging crucial for achievable precision

| channel       |       | change for +/-20% fake r. |

|---------------|-------|---------------------------|

| H <b>→</b> bb | 0.23% | 0.24% / 0.21%             |

| Н→сс          | 3.1%  | 3.6% / 2.6%               |

LCD-Note-2011-036, CLICdp Note-2014-002

- consider ±20% change in fake rates

- sizeable effect, in particular for H→cc:

30% more integ. luminosity required for same precision when increasing fake rate by 20% (>1 year of additional running!)

### Medipix/Timepix hybrid r/o chip family

| Chip                  | Year          | CMOS<br>Process | Pitch<br>[µm²] | Pixel operation modes           | r/o<br>mode              | Main applications                      |

|-----------------------|---------------|-----------------|----------------|---------------------------------|--------------------------|----------------------------------------|

| Timepix               | 2006          | 250 nm          | 55x55          | ∫ToT or ToA or<br>γ counting    | Sequential (full frame)  | HEP, Medical                           |

| Medipix3RX            | 2012          | 130 nm          | 55x55          | γ counting                      | Sequential (full frame)  | Medical                                |

| Timepix3              | 2013          | 130 nm          | 55x55          | ToT + ToA,<br>γ counting + ∫TOT | Data driven              | HEP, Medical                           |

| CLICpix/<br>CLICpix2  | 2013/<br>2016 | 65 nm           | 25x25          | ToT + ToA                       | Sequential (data compr.) | Test chips targeting CLIC requirements |

| Velopix               | 2016          | 130 nm          | 55x55          | ToT + ToA,<br>γ counting + ∫TOT | Data driven              | LHCb (10x<br>Timepix3 rate)            |

| Medipix4/<br>Timepix4 | tbd           | 65 nm           | ~35x35         | ToT + ToA,<br>γ counting + ∫TOT | Data driven              | HEP, Medical<br>4-side buttable        |

ToT: Time-over-Threshold

→ Energy

ToA: Time-of-Arrival

→ Time

- Taking advantage of smaller feature sizes:

- Increased functionality and/or

- Reduced pixel size

- Improved noise performance

# Test beam setup at DESY

#### DATURA telescope DUT prediction resolution

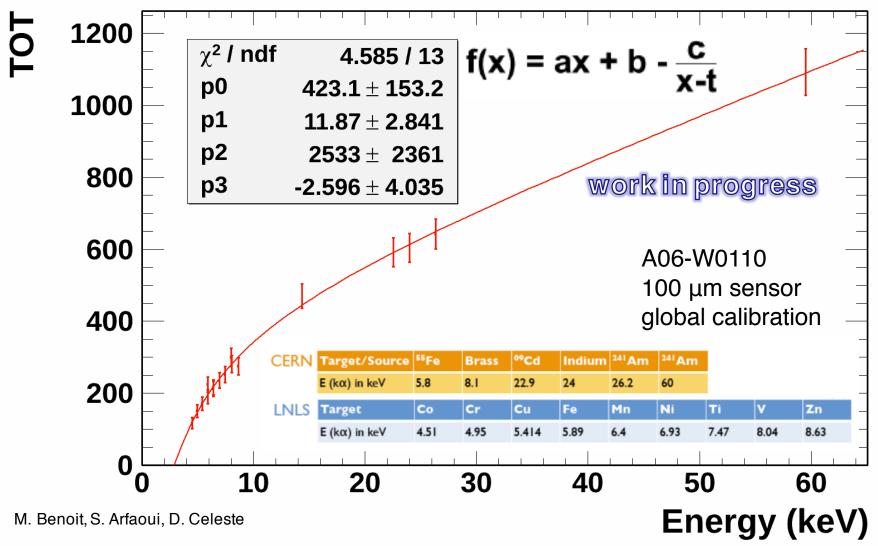

#### Timepix calibration

- Calibration of non-linear Timepix energy response with radioactive sources + fluorescence

- Parameterization with 4 parameters; global and per-pixel

- → Improves accuracy of position determination with charge-weighting methods

### Characteristics of Medipix chips

|                                          | Medipix2                 | Timepix                                      | Medipix3                                                              | Timepix3                                              | Medipix4                  | Timepix4     |

|------------------------------------------|--------------------------|----------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|---------------------------|--------------|

| Pixel side (μm)                          | 55                       | 55                                           | 55/110                                                                | 55                                                    | x/2x/3x                   | У            |

| Technology (nm)                          | 250                      | 250                                          | 130                                                                   | 130                                                   | 65                        | 65           |

| # pixels in x and y                      | 256                      | 256                                          | 256/128                                                               | 256                                                   | 512/256/128               | 512          |

| Readout                                  | Frame based              | Frame based                                  | Frame based                                                           | Data driven/                                          | Frame based               | Data driven/ |

| architecture                             | Sequential RW            | Sequential RW                                | Continuous RW                                                         | frame based                                           | Continuous RW             | frame based  |

| Charge summing and allocation mode (CSM) | No                       | No                                           | Yes                                                                   | No                                                    | Yes                       | No           |

| # thresholds                             | 2 (window discriminator) | 1                                            | 2/4/8 Seq RW<br>1/4 Cont RW                                           | 1                                                     | ?                         | 1            |

| ТоТ/ТоА                                  | No                       | ToT (14 bit) OR ToA (14 bit, 10ns precision) | No                                                                    | ToT (10 bit) AND<br>ToA (14 bit, 1.56ns<br>precision) | No                        | ToT AND ToA  |

| Front end noise<br>(e rms)               | 110                      | 100                                          | 80(SPM)<br>174(CSM)                                                   | 62                                                    | ≤ 80 (SPM)<br>≤ 174 (CSM) | ≤ 62         |

| Peaking time (ns)                        | 150                      | 100                                          | 120                                                                   | 30                                                    | ≪120                      | ≪30          |

| Max count rate<br>(Mc/mm²/s)*            | 826                      | -                                            | 826 (SPM 55μm)<br>164 (CSM 55μm)<br>376 (SPM 110μm)<br>28 (CSM 110μm) | 0.43 (data driven)                                    | x5 Medipix3               | x10 Timepix3 |

| Number of sides available for tiling     | 3                        | 3                                            | 3                                                                     | 3                                                     | 4                         | 4            |

<sup>\*</sup>Depends strongly on exact conditions of threshold, sensor material and energy of illumination Brown indicates parameters which are still be to defined

M. Campbell October 15, 2015

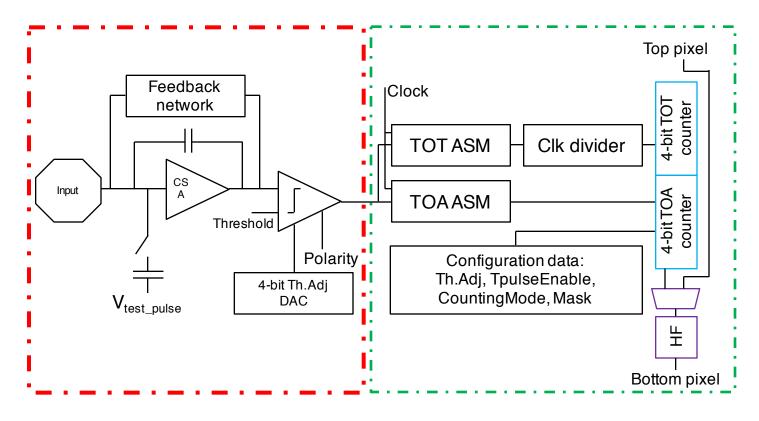

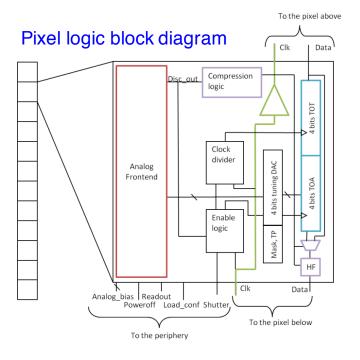

#### CLICpix: pixel architecture

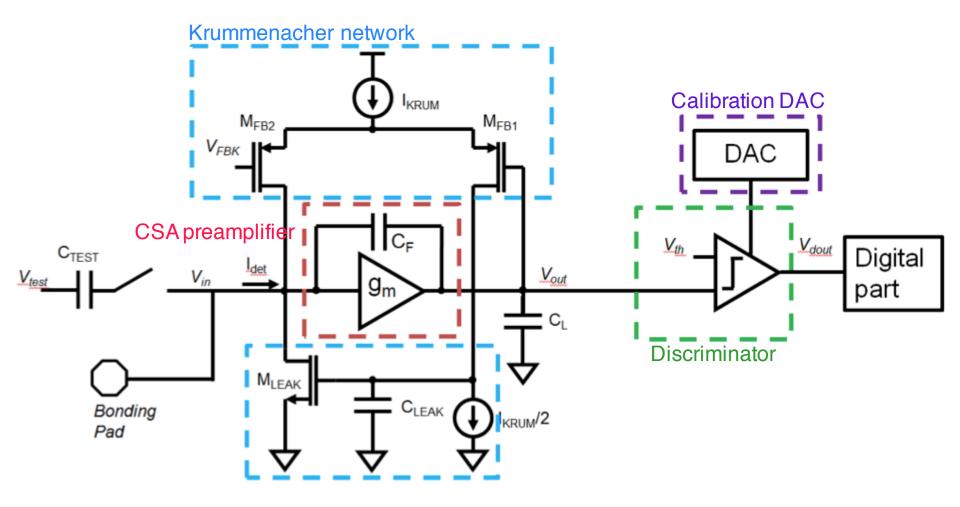

- The analog front-end shapes photocurrent pulses and compares them to a fixed (configurable) threshold

- Selectable polarity (positive / negative signals)

- Digital circuits simultaneously measure Time-over-Threshold and Time-of-Arrival of events and allow for zero-compressed readout

### **CLICpix** analog frontend

# CLICpix digital architecture

#### End of column block diagram

### CLICpix: time and energy measurement

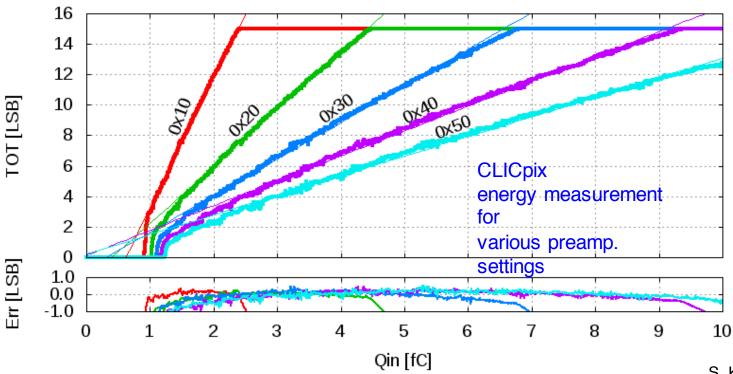

# CLICpix: energy measurement

- Measure charge released in each pixel

→ Improve position resolution through interpolation

- Time-Over-Threshold (TOT) measurement (4-bit precision)

- Calibration measurement using external test pulser:

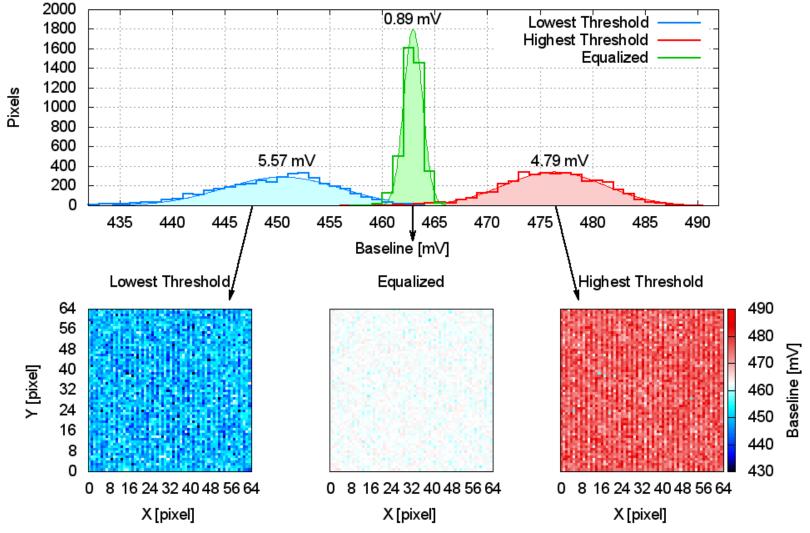

### CLICpix: baseline equalization

Calibrated spread across the whole matrix is 0.89 mV RMS (~22 e<sup>-</sup>) For comparison: MIP signal in 50 µm silicon ~3700 e<sup>-</sup>

S. Kulis, P. Valerio

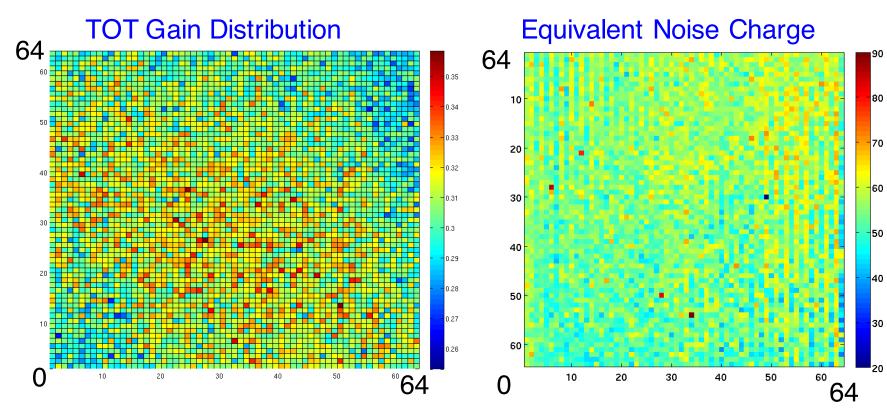

### CLICpix: uniformity of gain and noise

- Uniform gain across the matrix

- Gain variation ~4.2% r.m.s.

(for nominal feedback current)

- Uniform ENC across the matrix

- Mean ENC: 55 e<sup>-</sup>, SD: 5.7 e<sup>-</sup> (without sensor)

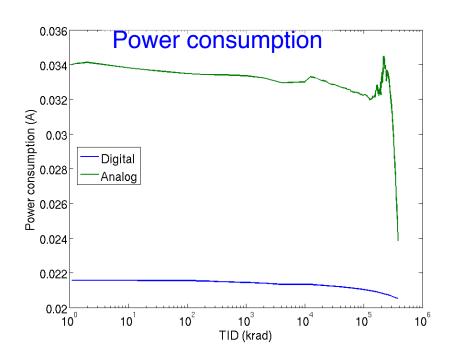

#### **CLICpix:** radiation qualification

- Moderate radiation-tolerance requirements at CLIC: <100 kRad TID</li>

- However: building blocks can be re-used for RD53 (~1 GRad required)

- Results of radiation testing useful for gaining deeper understanding of the chip

- → performed radiation test up to 1 GRad (up to 150 kRad/minute) in calibrated X-ray setup

- No significant changes observed in sub-MRad range relevant for CLIC

- For >250 MRad: PMOS switches in current mirror fail

- → Break-down of analog power (note: band gap foreseen for final chip, instead of current mirror)

- digital components kept working normally

### **CLICpix:** summary

| Parameter                  | Unit               | Simulation        | Measurement      |

|----------------------------|--------------------|-------------------|------------------|

| Rise time                  | [ns]               | 50                | -                |

| TOA accuracy               | [ns]               | <10               | <10              |

| Gain                       | [mV/ke-]           | 44                | 40 *             |

| Dynamic range              | [ke <sup>-</sup> ] | 44 (configurable) | 40 * (configur.) |

| Integr. nonlinearity (TOT) | [LSB]              | <0.5              | <0.5             |

| ENC (w/o sensor)           | [e <sup>-</sup> ]  | ~60               | ~55 *            |

| DC spread σ (uncalibrated) | [e <sup>-</sup> ]  | 160               | 128 *            |

| DC spread σ (calibrated)   | [e <sup>-</sup> ]  | 24                | 22 *             |

| Power consumption          | [µW/pixel]         | 6.5               | 7                |

<sup>\*</sup> results obtained with electrical test pulses

S. Kulis, P. Valerio

- good agreement between simulations and measurements

- power pulsing works according to specifications (~100x reduction of average power)

- programmable power on/off times, front-end wake up within ~15 μs

- Radiation test: chip functional up to ~250 MRad

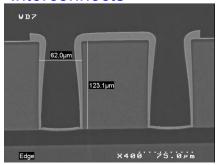

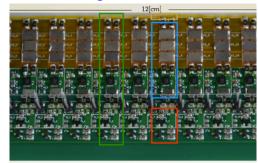

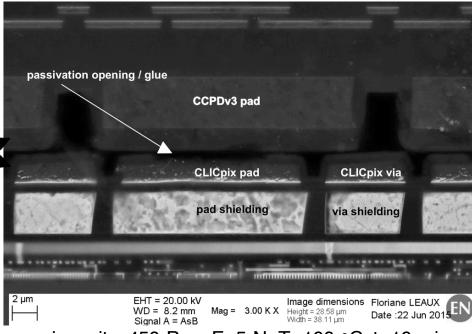

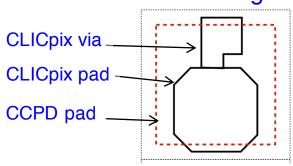

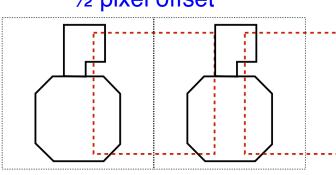

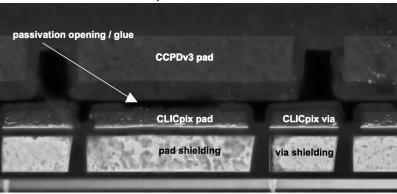

# CLICpix+HV-CMOS glue assemblies

polyimide

passivation

- Study of glue parameters:

- Viscosity

- Bonding force

- Alignment

- Glue-layer uniformity

- Cross sections of glue assemblies

- → alignment precision ~1 µm

- glue-layer thickness ~0.5 μm

(+2 μm polyimide passivation)

- Laboratory and test-beam measurements

- correlate performance with glue parameters (coupling strength, uniformity)

SEM picture CCPDv3-CLICpix assembly

viscosity: 450 Pas, F=5 N, T=100 °C, t=10 min

#### centered alignment

½ pixel offset

pad alignment

August 4, 2016 Silicon Pixel R&D for CLIC

36

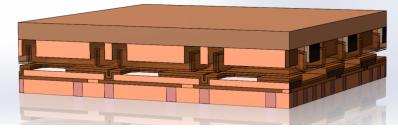

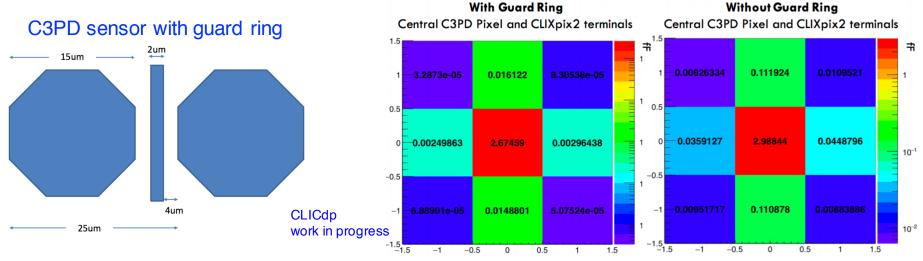

### Simulation of capacitive coupling

crc

- COMSOL multi-physics simulation of capacitance between sensor and r/o ASIC

- Detailed model of the major metal and passivation layers and the glue in 3x3 matrix

- Obtain coupling capacitance (~3 fF) and cross capacitances

- Significant cross coupling (~4%) to neighboring pads for current CCPDv3 version

- Cross coupling largely reduced for newly designed C3PD active sensor with guard ring

CCPDv3+CLICpix cross section

#### COMSOL simulation model

August 4, 2016

Silicon Pixel R&D for CLIC

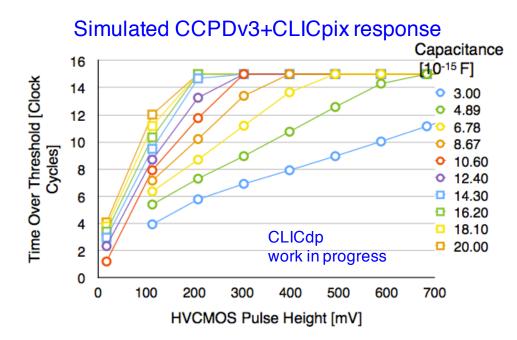

### CLICpix+HV-CMOS calibration

crc

- Dedicated test pixels: direct access to CCPDv3 output signal

- Used to calibrate CLICpix ToT response

- Simulation of CLICpix ToT response for different values of coupling capacitance

- → estimate coupling capacitance by comparison of measured and simulated response: ~10 fF

#

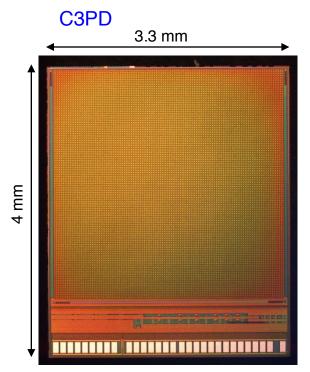

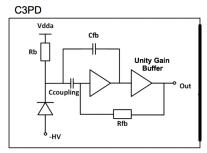

#### New HV-CMOS active sensor

- New HV-CMOS chip C3PD produced in same process:

- Increased matrix size to 128 × 128 pixels

- Major redesign of the full chip:

- On-pixel amplification scheme significantly changed

- → reduced peaking time to some ~10 ns

- Guard ring around coupling pads

- → reduced cross capacitance

- Power pulsing circuitry introduced

- Testpulsing of the matrix

- 10 Ω cm substrate

- possible future submissions with substrate resistivities of 100, 200, 1k  $\Omega$  cm

- Lab measurements for first chips ongoing

39

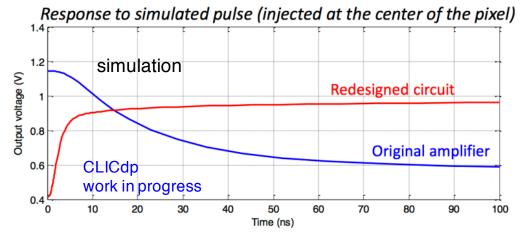

### First results from ALICE Investigator

- First test-beam performance results:

- Good time resolution ~5 ns

- Cluster size distributions and spatial resolution in agreement with expectations

- · Caveats:

- Results based on full waveform analysis of signals from external sampling ADC

- Unknown absolute efficiency (r/o deadtime not recorded)