# The upgrade of the CMS Tracker for HL-LHC

Duccio Abbaneo PH-CMX

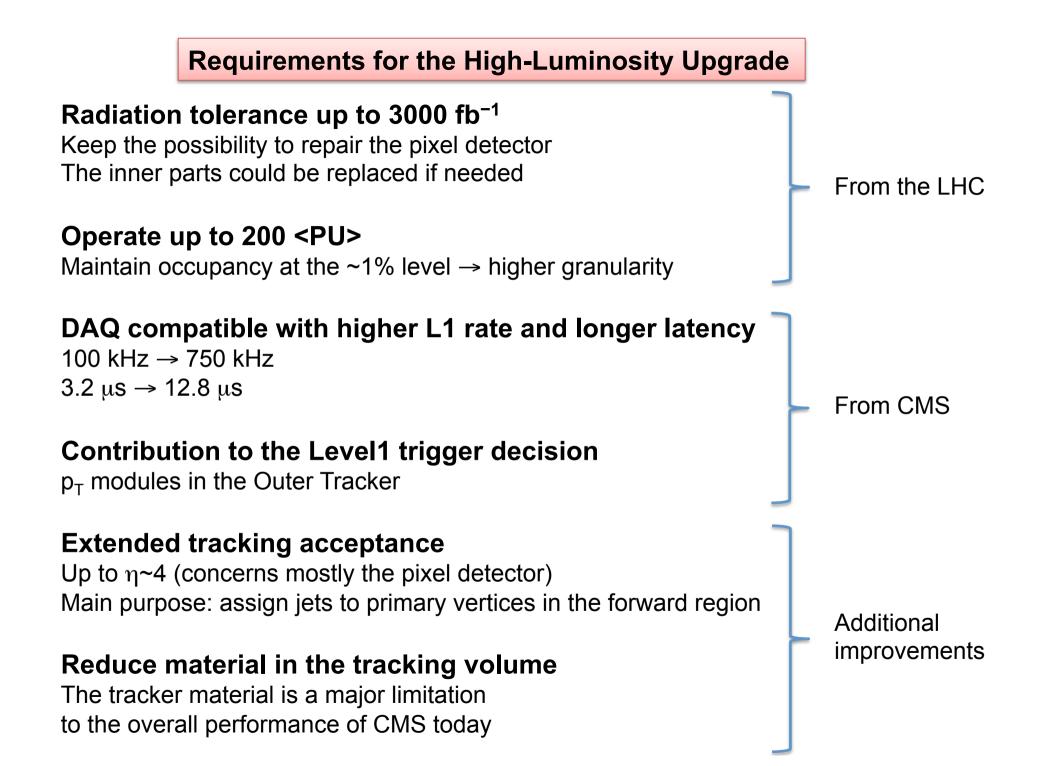

## **Requirements for the High-Luminosity Upgrade**

## **The Pixel detector**

- Main challenges

- Sensors

- Readout chip

- Electronics system and detector optimization

# The Outer Tracker

- Main challenges and new requirements

- Sensors

- ▷ p<sub>T</sub> modules

- Electronics system

- Optimization of the detector layout

- Mechanical structures and cooling

- Tracking @ Level-1

- Some performance plots

## **Requirements for the High-Luminosity Upgrade**

## **The Pixel detector**

- Main challenges

- Sensors

- Readout chip

- Electronics system and detector optimization

## **The Outer Tracker**

- Main challenges and new requirements

- Sensors

- ▷ p<sub>T</sub> modules

- Electronics system

- Optimization of the detector layout

- Mechanical structures and cooling

- Tracking @ Level-1

- Some performance plots

## And to conclude... the bill!

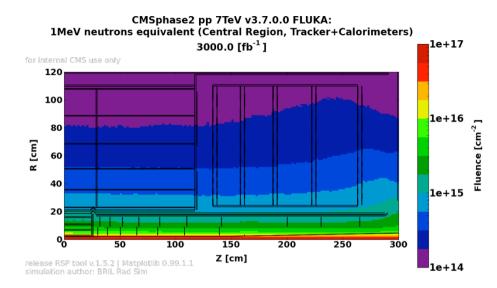

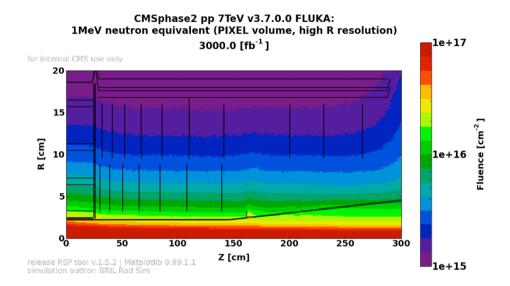

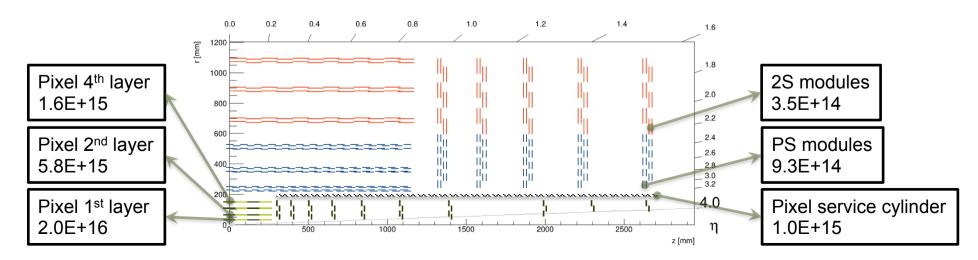

### Radiation levels depend essentially on R, not on z

- ♦ The target is 10× present tracker

- ♦ Challenging for silicon sensors and electronics (notably in the pixel region)

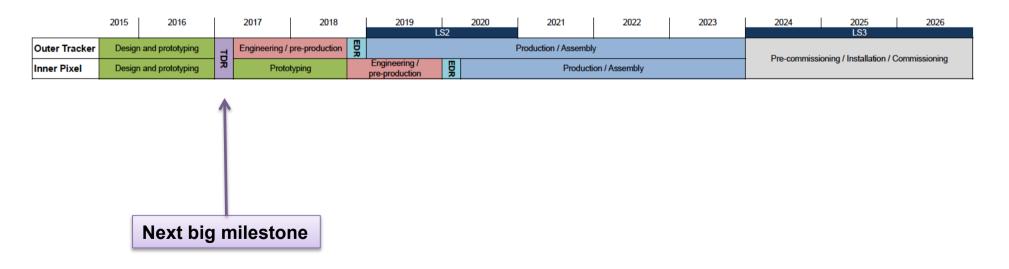

# Timeline

### The new Tracking System is due for installation in LS3

## The official timeline has still ample margin

Production time can be shorter *Notably for Inner Pixel* Installation will be towards the end of LS3

# The phase-2 pixel upgrade

#### Radiation tolerance is a major worry, not only for sensors but also electronics!

Huge ongoing effort in RD53 to qualify TSMC 65 nm technology R&D on thin n-in-p planar sensors, 3D sensors, (n-in-n thin sensors)

#### **Rapidity extension**

Main requirement is to match jets to vertices in the forward region (Anything else is a bonus)

### Operate at 200 PU x 750 kHz

#### Maintain/improve single hit resolution and two-track separation

Rad tolerance requirements implies thinner sensors, less charge (100  $\div$  150  $\mu$ m active thickness). Achieve hit resolution with less charge sharing and smaller pixels. Rectangular pixels give lower occupancy and mitigate requirement on pixel chip threshold (around 1000 e-, under study)

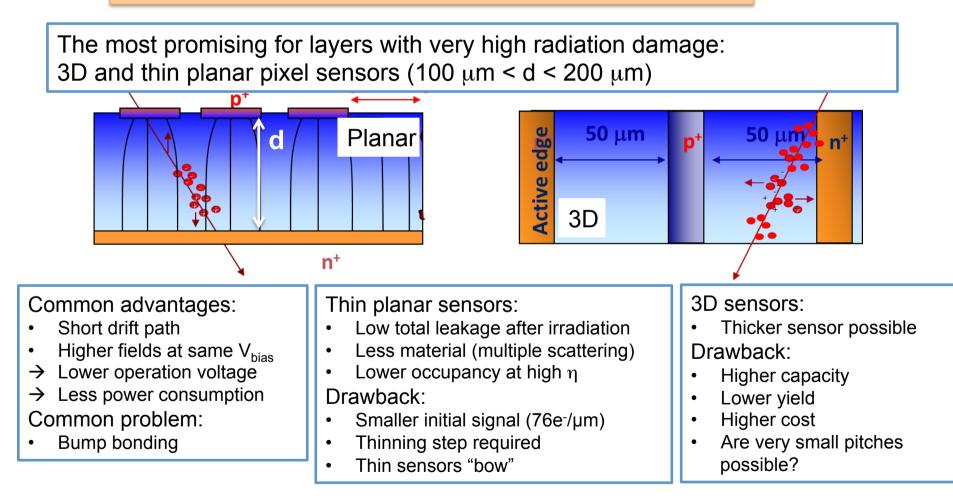

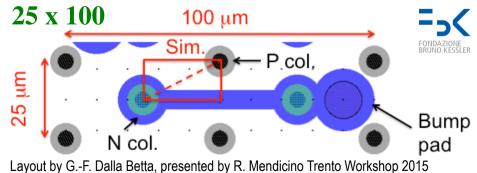

# Pixel sensors: thin planar (n-in-p) and 3D

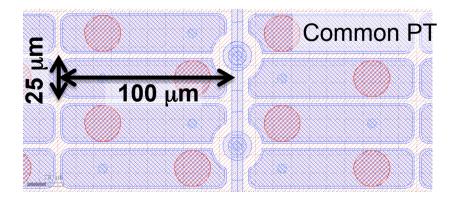

Developing small-area pixels 25 x 100  $\mu$ m<sup>2</sup> or 50 x 50  $\mu$ m<sup>2</sup>

N.B. Planar n-in-n remains as a valid back-up (more expensive than n-in-p!) Thinning being investigated

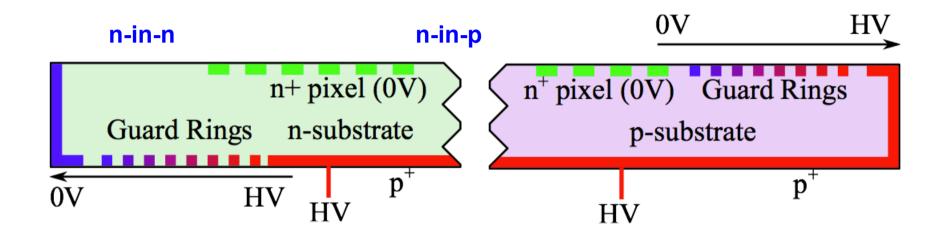

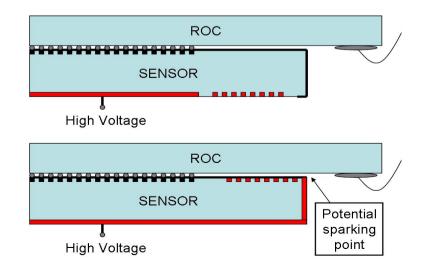

# n-in-n vs n-in-p

Compare radiation hardness Address spark protection problem Consider production issues

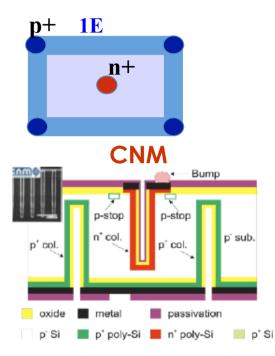

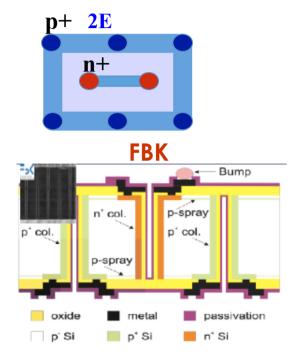

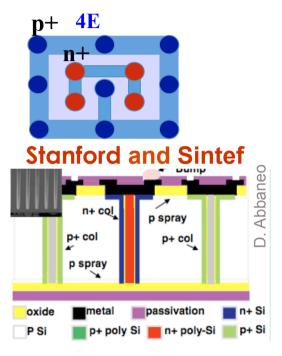

# **3D sensors**

Different techniques to realize the electrodes, and different possible geometrical configurations

Often linked to different vendors....!

**Double side**, not passing through columns but slim edges (200  $\mu$  m)

Double side, full 3D with slim edges (200  $\mu$  m)

Single side, full 3D with 10 active edges (it requires a support wafer which is removed later)

#### **Specific issues:**

- Inefficiency around electrodes

- Advantages progressively reduced for thinner sensors

- Fabrication difficult for small pixels

- COST...

# **Pixel sensors submissions**

# **Pixel ROC**

## **Developed in RD53**

## Radiation qualification studies converging

Large effort involving many Institutes Testing to unprecedented levels (1 Grad) Finding effects never observed before! Coherent picture emerging

### **Outlook:**

Wrap up findings, derive design rules for optimal radiation tolerance Likely achievable goal: chip that functions up to at least 500 Mrad 1 Grad is not (yet) excluded

### Design of chip structures continuing Small demonstrator about to be submitted

Next steps: Finalize ROC specifications ~ mid 2016 Full-size ROC demonstrator ~ end 2017

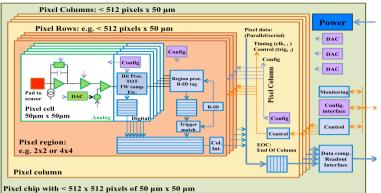

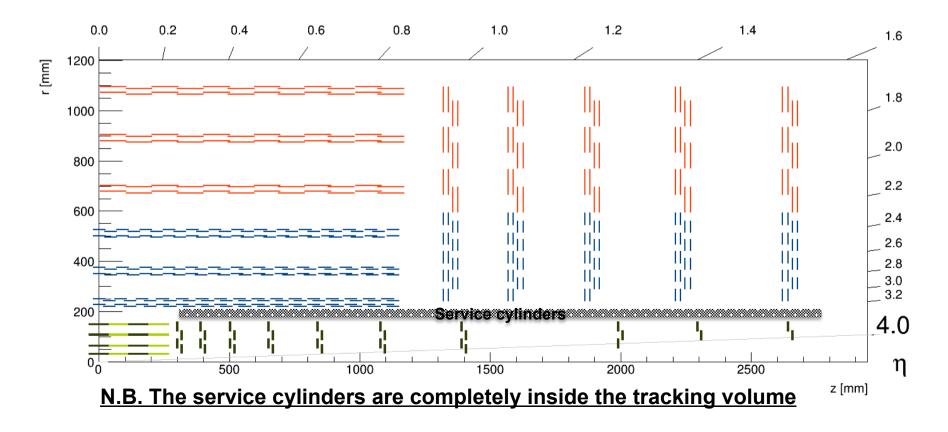

# **Electronics architecture - concept**

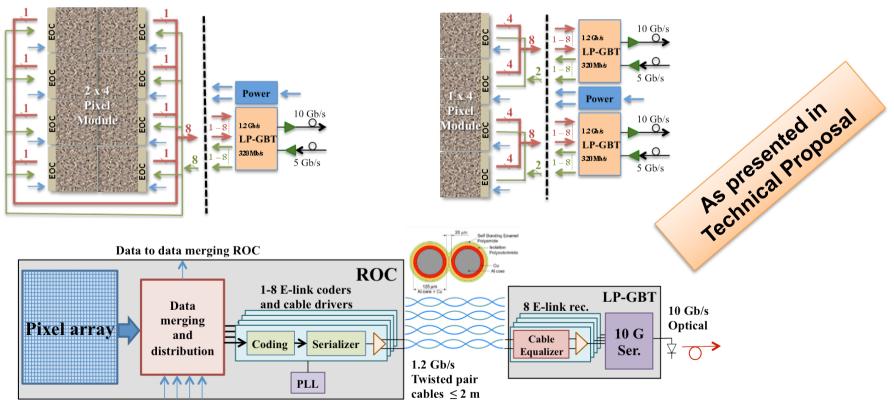

Envisage modules with 1×4 and 2×4 chips in the barrel, possibly ½ length in the forward (1×2 and 2×2) 1.2 Gbps e-links up to 2m length (or possibly 2.4 Gbps) from FE chips to LP-GBT (on the service cylinders) The chip implements data merging functionality

2 or 4 links / chip in the innermost regions (chip can support up to 8); multiple chips into one link in the outer layers The chip can work with  $\frac{1}{2}$  or  $\frac{1}{4}$  of the channels operational

Fine-tune channel density and the link density in the different layers to reduce power and mass Very flexible architecture!

Data from 1-4 neighbour ROCs

## **Electronics system challenges - I**

### 200 PU x 750 kHz $\rightarrow$ x 30 increased bandwidth wrt to phase-1!

Huge increase of the cross section of electrical links Optical converters can be integrated on the service cylinders – but not on-module Need very efficient lightweight e-links!

Implement Feed Forward Equalization

R&D ongoing – simulations and lab tests: early results very encouraging

## **Electronics system challenges - II**

### Higher power, with lower operating voltage $\rightarrow$ large conductors

#### DC-DC conversion not very appealing in this case

Inductor-based converters are too bulky for a pixel module, and in any case would not survive If implemented far away from the load (service cylinder) they do not help much On-chip converters maybe possible with x2 conversion factor – not good enough for material budget

### Conclusion: resume R&D on serial powering!

Work just started - collaborate with ATLAS

# **Phase-2 data links**

Discussion on specs for phase-2 data link is converging Highly optimized link for use in high radiation Asymmetric up/down link rate with different forward error correction in the two directions High bandwidth required in the downstream (data) link High robustness required in the upstream (control) link

#### "Low-speed " version

Downstream bandwidth 12 /14 links @ 320 Mb/s (3.84 or 4.48 Gb/s) (depending on error correction scheme) Or else 6 /7 links @ 640 Mb/s Upstream link reduced to 4 links @ 320 Mb/s With increased SEU robustness

#### "High-speed " version

As above with x2 bandwidth in the links

Some (moderate) penalty in power

E.g. maximum 7 links @ 1.28 Gb/s  $\rightarrow$  Total 8.96 Gb/s

Implementation in a small-size package: huge leap compared to the 400 Mb/s DOH used for phase-1 Suitable development to cope with the x 30 increase in bandwidth requirement (Suitable also for Outer Tracker) Limit at 7 links / GBT does not ideally fit our initial Pixel electronics system concept ... some more thinking required... !!

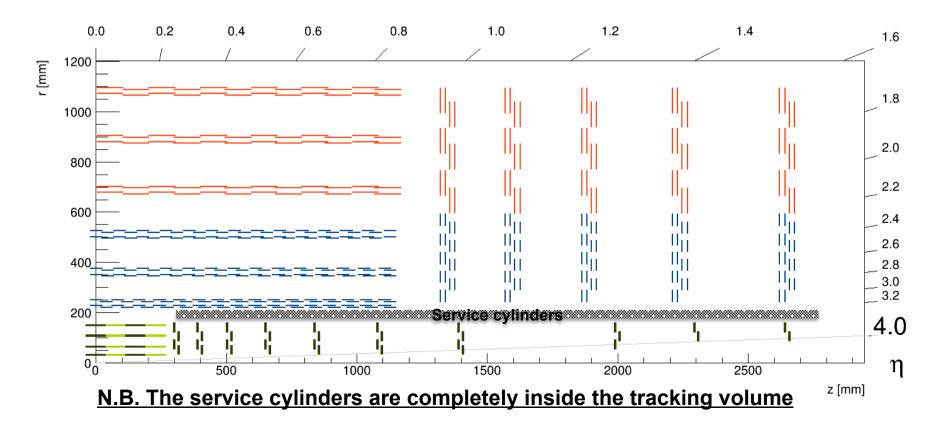

# **Detector optimization**

#### Geometry used for TP studies: straightforward extension of the phase-1 geometry

#### Detector optimization ongoing:

- Detailed analysis of achievable hit resolution for different pixel sizes and aspect ratios in the different part of the detector

- Effect on track parameter resolution

- Optimization of geometry to improve rapidity coverage

#### Medium-term goal: coherent baseline concept for TDR, with well understood performance

# The phase-2 Outer Tracker upgrade

### Increased granularity and radiation tolerance

~ one order of magnitude wrt to present tracker

## Participate to Phase-1 Trigger decision

## " $p_T$ modules" with online data reduction

Allows tracking of charged particles with  $p_T > 2GeV$  at every bunch crossing Novel concept of silicon detector modules Drives design of modules and overall detector concept

# **Sensors for Outer Tracker**

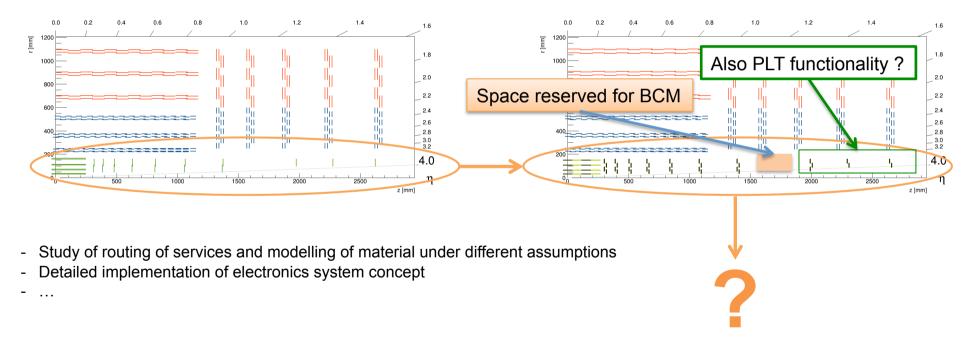

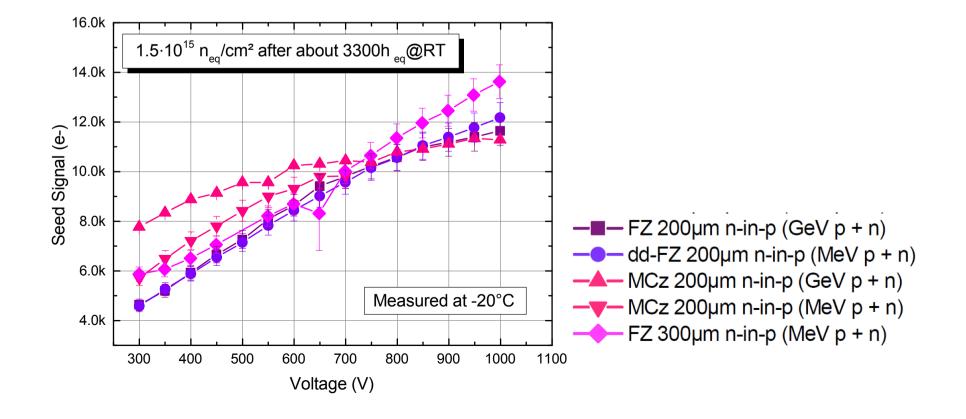

- After heavy irradiation (~10<sup>15</sup>) charge from 320 µm thick sensors drops down to the same level as 200 µm

- More trapping

- ⊙ In 200 µm the leakage current is smaller, and can be operated at smaller V<sub>bias</sub>: mitigate requirement on cooling!

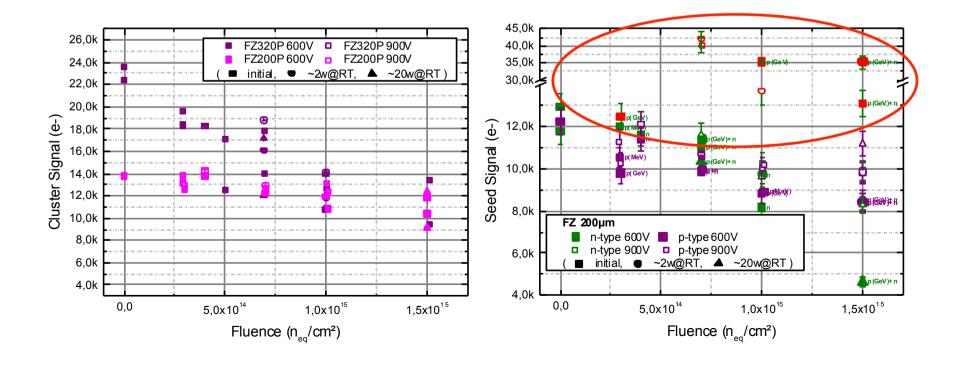

- In p-in-n sensors observed spurious signals (random non-gaussian noise, a.k.a. Random Ghost Hits)

# **Understanding RGH**

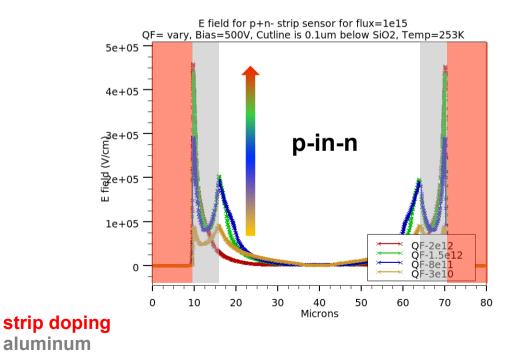

- T-CAD simulations show higher electric fields at the strip edges for irradiated p-in-n sensors than for p-type sensors with same geometry

- ⊙ Suggests the occurrence of "micro-discharges" in p-in-n

- Increasing oxide charge...

- ⊙ increases max. electric fields in p-in-n, reduces max. electric fields in n-in-p

- Observation: rate of RGHs are smaller for neutron than for proton irradiation

★ less ionization, less surface damage

# Annealing

- All thin p-type samples work well and show seed signals >8ke- at 600V until about 20w@RT

- Can be used to reduce the leakage current by keeping the detector at RT for 2 weeks each year, e.g. during YETS

- MCz material shows significantly better behaviour after long annealing time

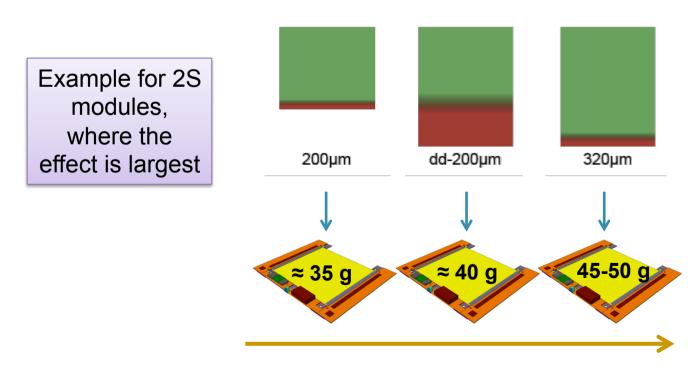

# **Sensor thickness**

- 200 µm active thickness provides sufficient charge

Due to smaller charge loss after irradiation

- > Adding (inactive) silicon thickness increases the mass

- With larger active thickness the leakage current is larger

... and most likely V<sub>bias</sub> would have to be larger, eventually

- $\rightarrow$  additional material for thermal management

# **Outer Tracker sensors summary**

### Basic R&D essentially finished: the main properties of the sensors are defined

- Polarity

- n-in-p is the selected option, as it offers robust performance (i.e. graceful degradation) after heavy irradiation

### > Material

- MCz is the preferred option (but FZ is OK)

- ★ Allows for long annealing times with no adverse effects

- ★ Could be (eventually) operated at lower V<sub>bias</sub>, mitigating the requirements on the cooling

## Thickness

- ⊙ 200 µm active and physical thickness is the preferred option

- ★ Sufficient charge, good annealing behaviour, lower  $I_{dark}$  and  $V_{bias}$

- 200 µm active 320 µm physical is a good backup

- \* Adds 60 kg of inactive material uniformly distributed in the tracking volume

- ★ Active thickness can also be fine-tuned...

# **Outer Tracker sensors outlook**

Ongoing: qualification of vendors and production options, fine-tuning of sensor design parameters, preparation of Market Survey (with ATLAS)

HPK: well-established reliable vendor, consistently delivering excellent quality; dd-320 μm FZ 6" material available at good price, thinning expensive

Infineon: development ongoing for several years; produced 300  $\mu$ m p-in-n sensors with adequate quality; now moving to n-in-p, exploring thinning and production on 8"; dd-FZ material also available

Work with other possible vendors (Novati, CiS...)

Procurement of sensors to support module prototyping

**Preparation for sensor QA in several labs**

**Evaluation of new irradiation sources**

# **Tracker input to Level-1 trigger**

● µ, e and jet rates would substantially increase at high luminosity

★ Even considering other trigger upgrades

### ⊙ Increasing thresholds would affect physics performance

- ★ Performance of algorithms degrades with increasing pile-up

- Muons: increased background rates from accidental coincidences

- $\circ$   $\:$  Electrons/photons: reduced QCD rejection at fixed efficiency from isolation

- ⊙ Even HLT without tracking seems marginal

⊙ Add tracking information at Level-1

★ Move part of HLT reconstruction into Level-1

- Goal for "track trigger":

- ⊙ Reconstruct tracks above 2 GeV

- Identify the origin along the beam axis with 1÷2 mm precision

- ★ Enables vertex discrimination

# **General concept**

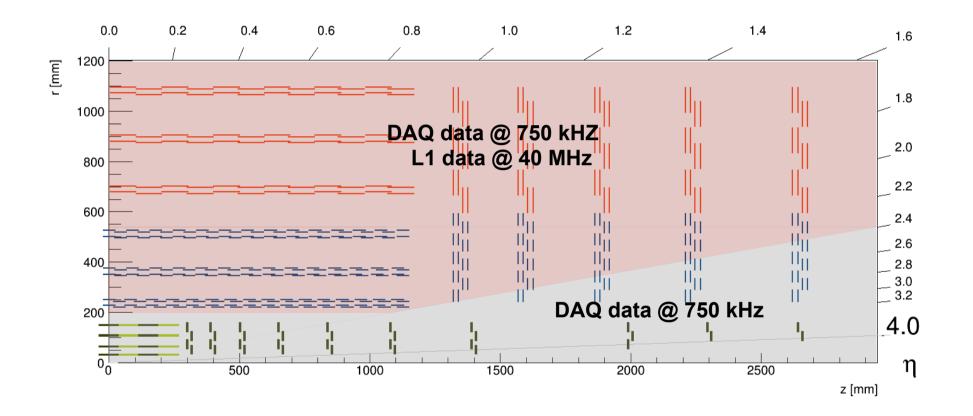

Silicon modules provide at the same time "Level-1 data" (@ 40 MHZ), and "DAQ data" (upon Level-1 trigger)

The whole tracker sends out data at each BX

▶ Level-1 data require local rejection of low-p<sub>T</sub> tracks

⊙ To reduce the data volume, and simplify track finding @ Level-1

⊙ Threshold of ~ 2 GeV ⇒ data reduction of ~ one order of magnitude

> Design modules with  $p_T$  discrimination (" $p_T$  modules")

⊙ Correlate signals in two closely-spaced sensors

- $\odot$  Exploit the strong magnetic field of CMS

- ➤ Level-1 "stubs" are processed in the back-end

⊙ Form Level-1 tracks, p<sub>T</sub> above ~2 GeV

- ⊙ To be used to improve different trigger channels

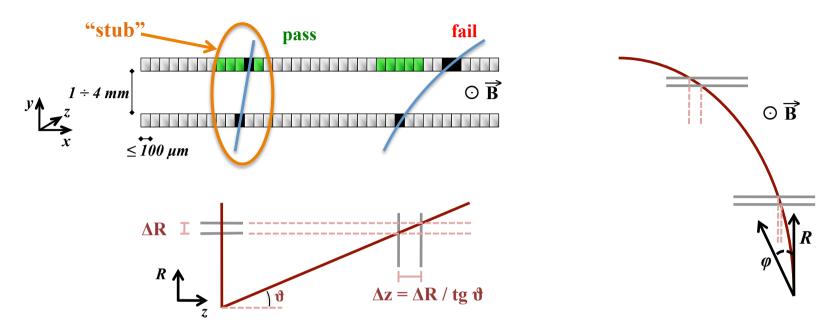

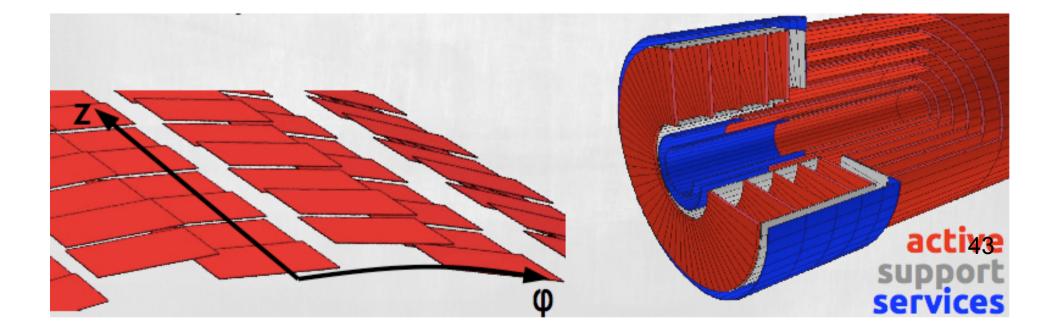

# Working principle of $p_T$ modules

- Sensitivity to  $p_T$  from measurement of  $\Delta(R\phi)$  over a given  $\Delta R$

- For a given  $p_T$ ,  $\Delta(R\phi)$  increases with R

- $\odot$  In the barrel,  $\Delta R$  is given directly by the sensors spacing

- $\odot$  In the end-cap, it depends on the location of the detector (tg $\vartheta$ )

- $\star$  End-cap configuration typically requires wider spacing, and yields worse discrimination

- Optimize selection window and/or sensors spacing

- $\odot$  To obtain, as much as possible, consistent  $p_T$  selection through the tracking volume

- The concept works down to a certain radius

- $\odot$  20÷25 cm with the CMS magnetic field and a realistic 100  $\mu m$  pitch

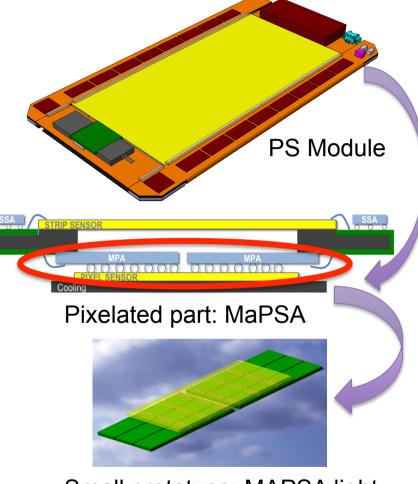

p<sub>T</sub> modules

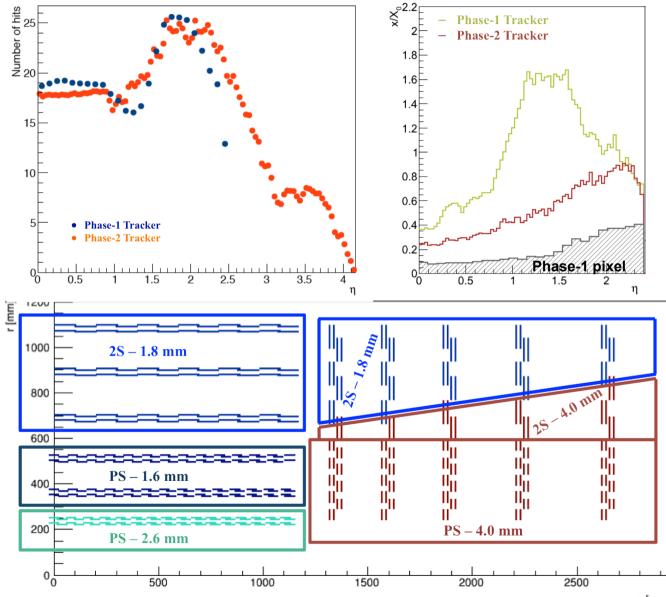

2 Strip sensors 2×1016 Strips: 5 cm × 90  $\mu$ m 2×1016 Strips: 5 cm × 90  $\mu$ m P ~ 5 W ~ 90 cm<sup>2</sup> active area For R > 60 cm Spacing 1.8 mm and 4.0 mm

Pixel + Strip sensors  $2 \times 960$  Strips: 2.5 cm × 100 µm  $32 \times 960$  Pixels: 1.5 mm × 100 µm  $P \sim 7$  W  $\sim 45$  cm<sup>2</sup> active area For r > 20 cm Spacing 1.6 mm, 2.6 mm and 4.0 mm

Operate sensors at about -20°C with cooling set point at -30°C

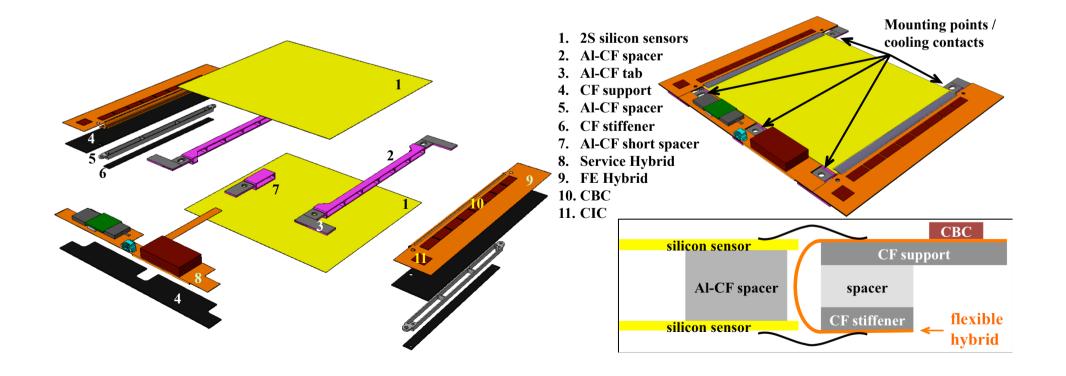

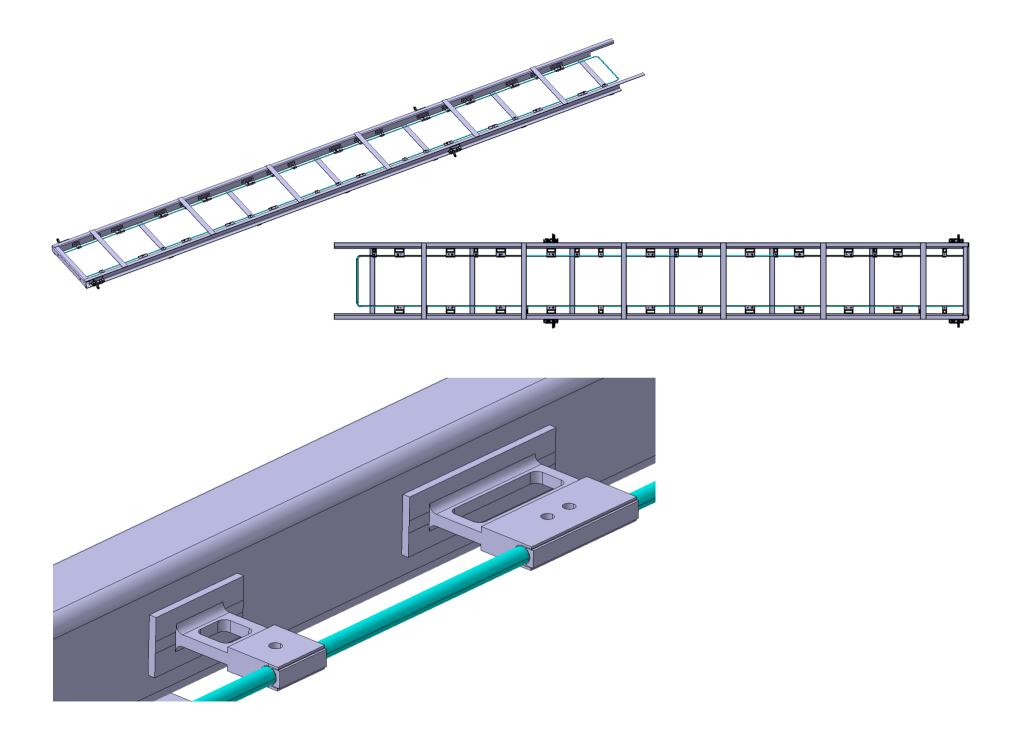

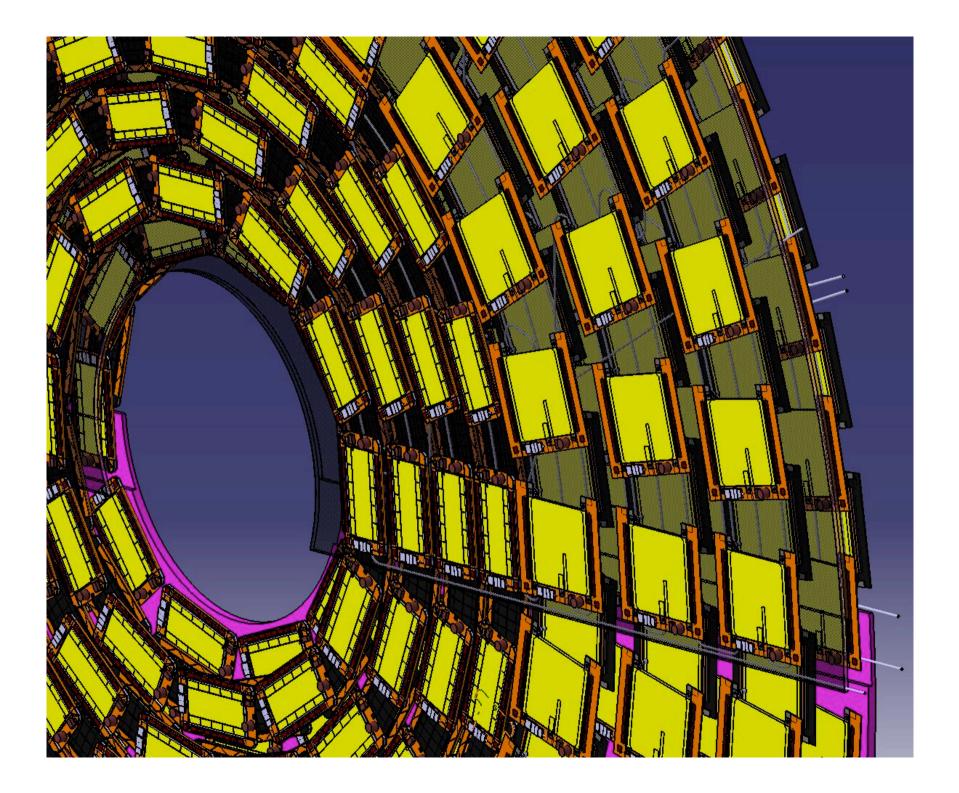

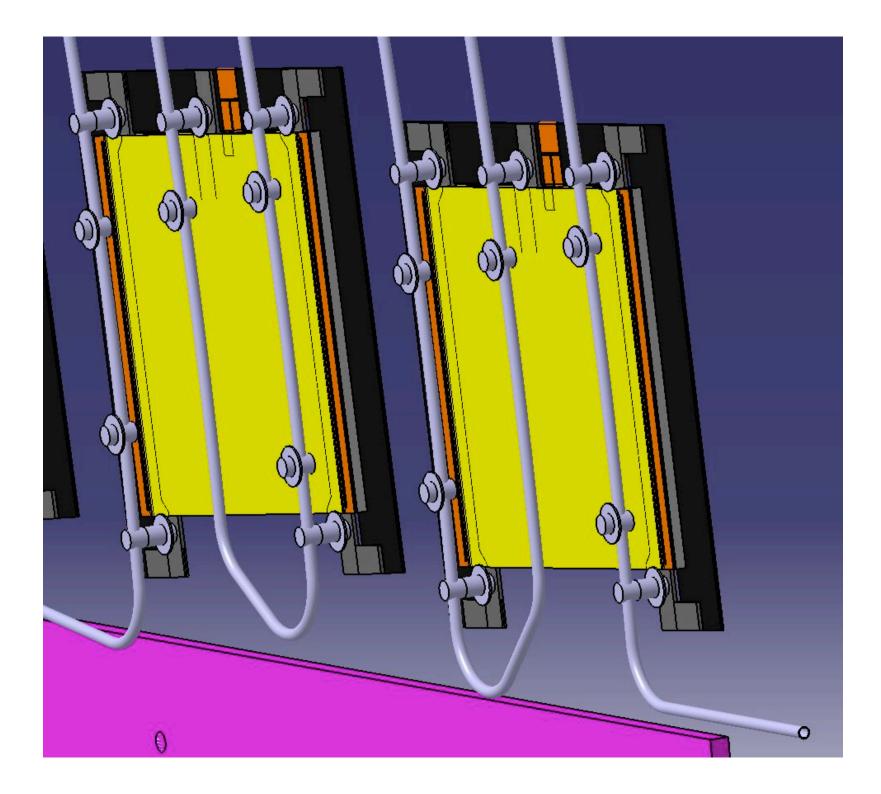

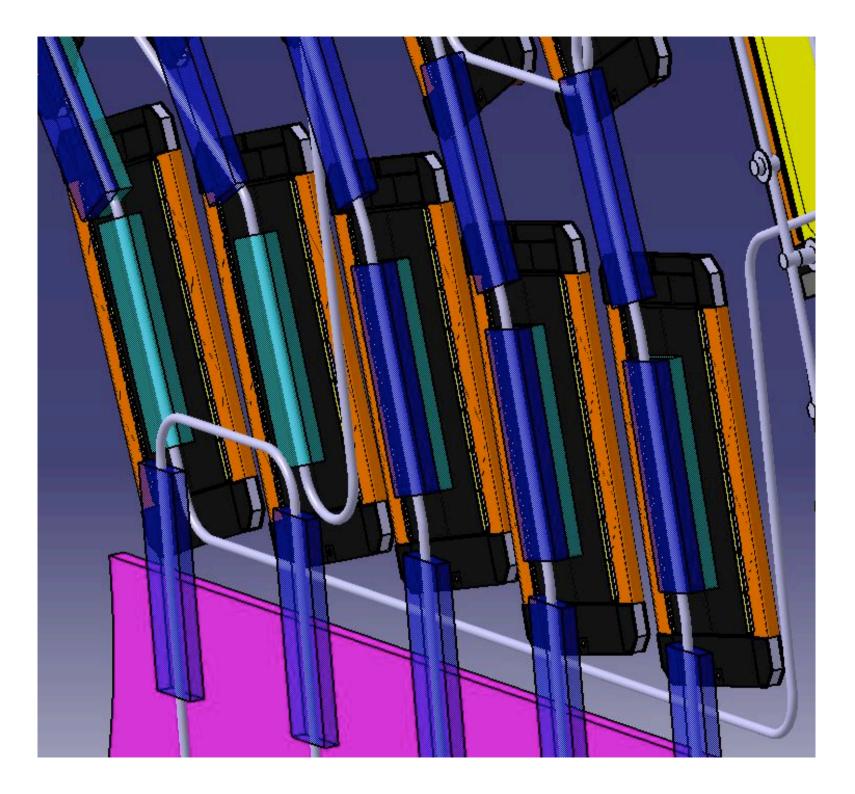

# **2S module**

- Five mounting/cooling points peripheral cooling

Ocncept similar to modules of the present tracker

- AI-CF spacers provide good thermal conduction, and enable simple, high-precision assembly with ~ no CTE mismatch

- Hybrids are laminated on the CF supports by the company

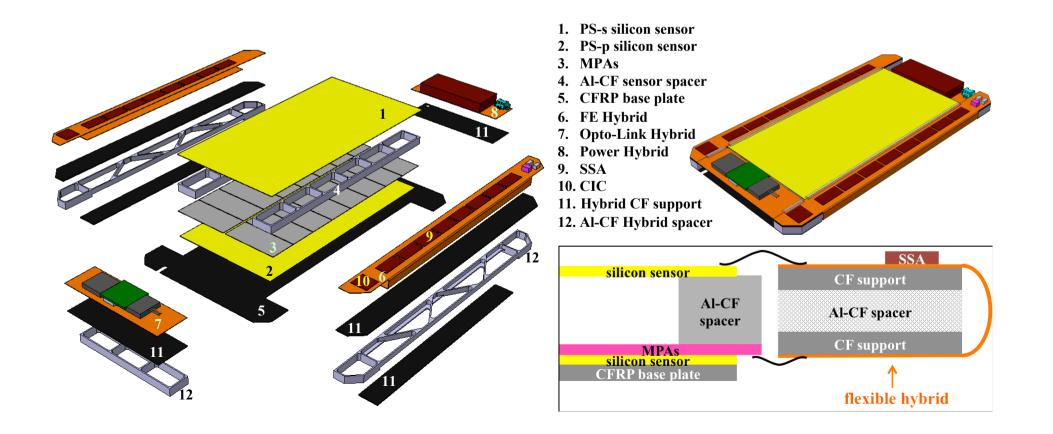

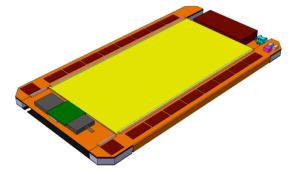

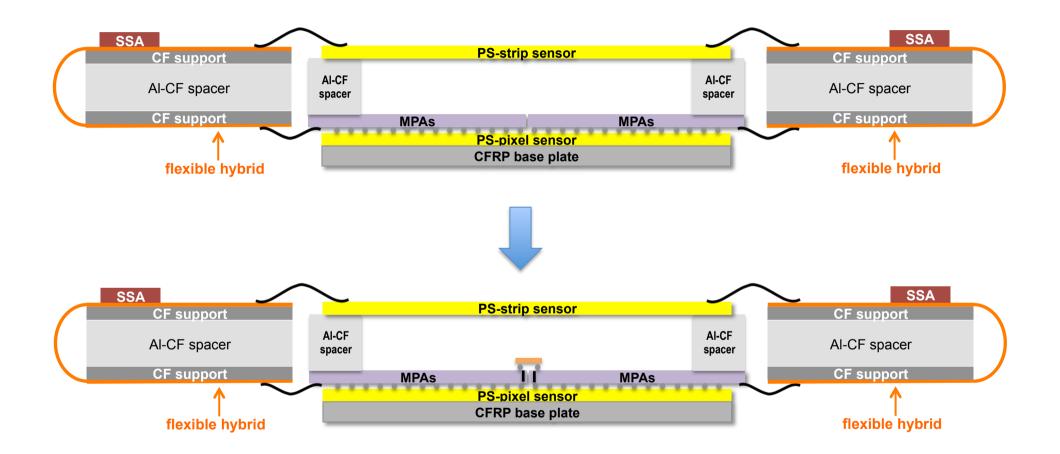

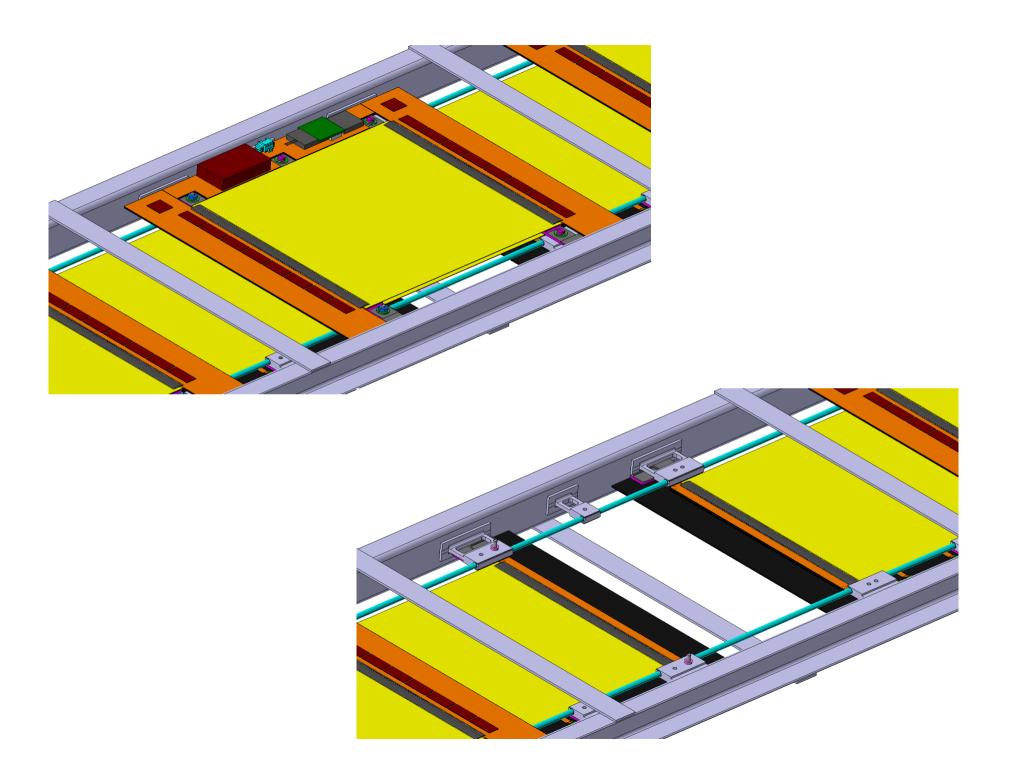

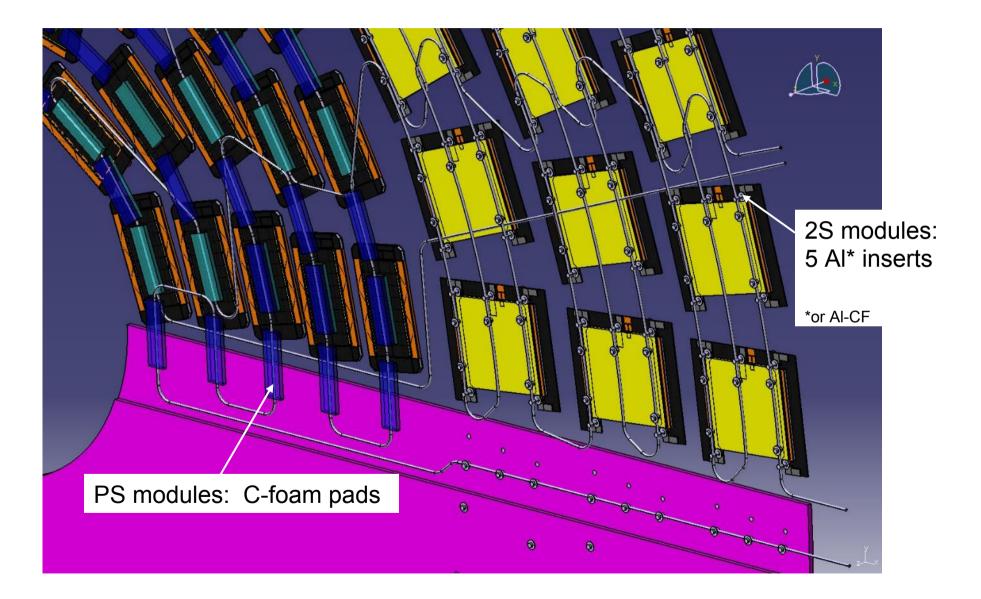

# **PS module**

- Heat dissipation in the MPA requires large area cooling contact

- Cooling through CF base plate, glued on a cold surface on the supporting mechanics

- Module assembly starts from the base plate

- Additional spacer under the Opto-Link Hybrid, wire-bonded to the FE Hybrids

# **AI-CF composite**

Aluminium with embedded carbon fibers, randomly oriented in a plane Excellent combination of mechanical and thermal properties Easy to machine

Breakthrough in the design of  $p_T$  modules!

| Property                                                        |               | AI-CF V2-4 | Al  |

|-----------------------------------------------------------------|---------------|------------|-----|

| Density [g cm <sup>-3</sup> ]                                   |               | 2.4        | 2.7 |

| Thermal<br>conductivity<br>[W m <sup>-1</sup> K <sup>-1</sup> ] | In plane      | 230        | 237 |

|                                                                 | Through plane | 120        |     |

| CTE [ppm K <sup>-1</sup> ]                                      | In plane      | 4          |     |

|                                                                 | Through plane | 24         | 23  |

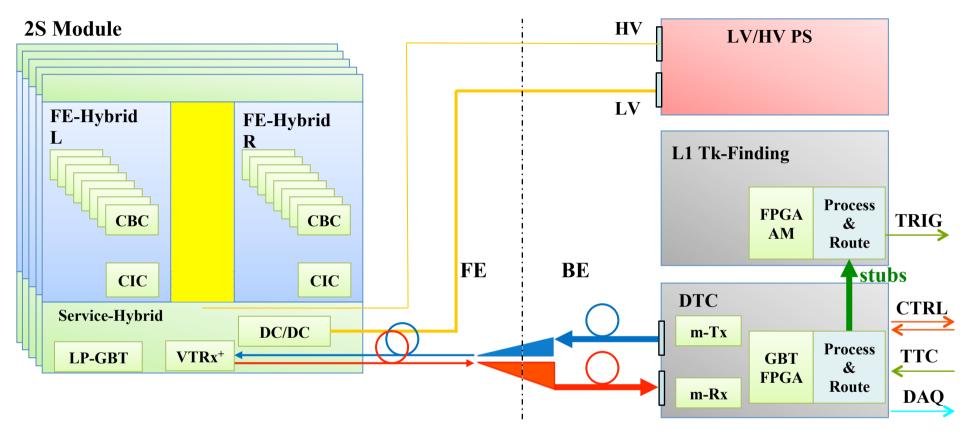

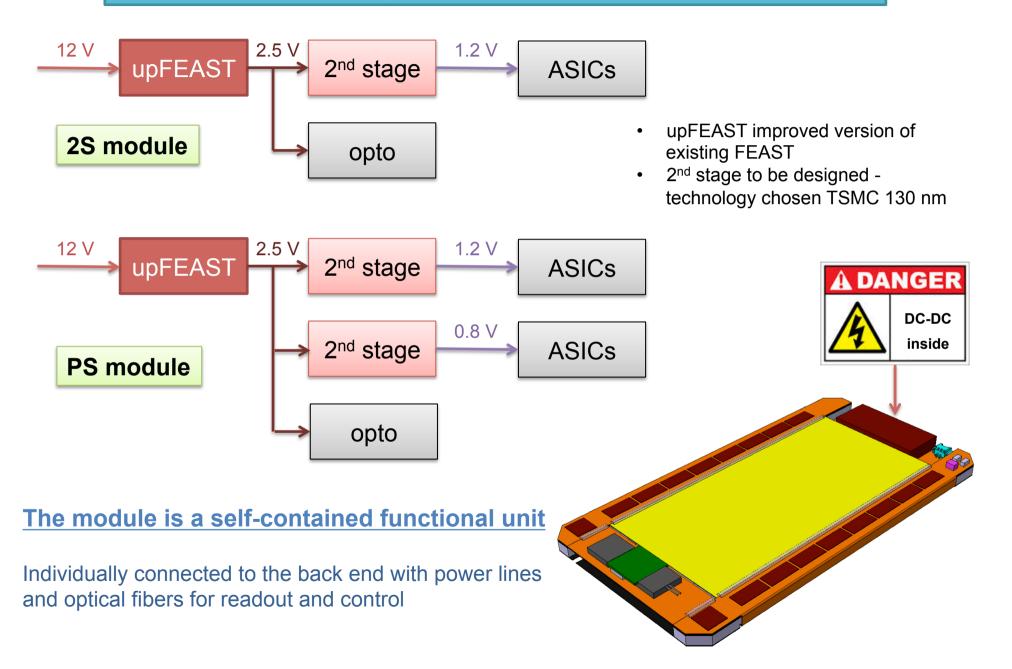

# **Electronics architecture**

### shown for 2S modules

- ◎ 8 CBCs / side, 130 CMOS, bump-bonded on the flex hybrids together with the passive components

- ★ 800 bumps @ 250 µm pitch

- ★ 127×2 channels, performs top-bottom correlations

- ⊙ Sensors wire-bonded to high-density FE hybrid

- Wire bonds from FE Hybrid to Service Hybrid

- FE hybrid implements all line routing (data, control, power)

- ★ Power from Service Hybrid to all chips

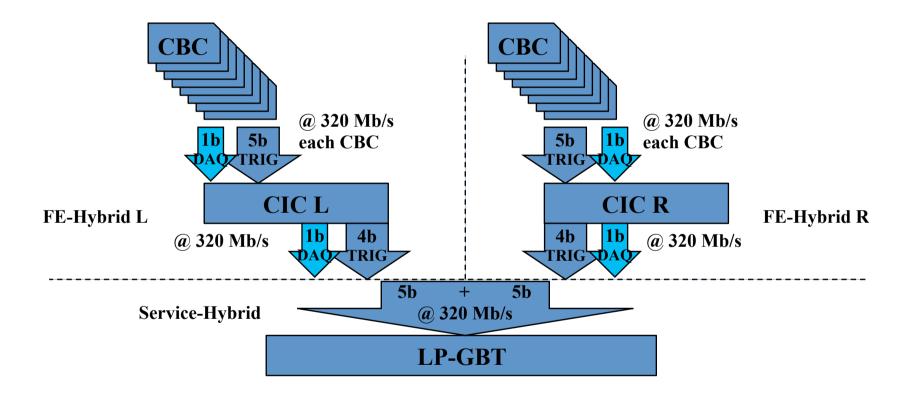

# Data flow (2S modules)

- The Concentrator IC combines data from 8 CBCs and for 8 consecutive BX

- ★ "Block synchronous" system. Efficient use of bandwidth with fixed latency

Initially based on a conservative assumption of 3.2 Gb/s available bandwidth in the phase-1 GBT The real value will be higher

$\rightarrow$  3.84 Gb/s or 4.48 Gb/s, depending on error correction scheme chosen

Option to use the high-speed version (2 × bandwidth) at the cost of some extra power

$\rightarrow$  Can be useful in the first layer of PS modules

### N.B. L1 tracking acceptance is limited at $\eta$ ~2.4

The L1 data output is disabled for modules located at low angle in the End Caps ( $p_T$  discrimination insufficient to achieve reasonable bandwidth and stub purity)

# **FE electronics for PS modules**

- > Two different chips: Macro-Pixel ASIC (MPA) and Short Strip ASIC (SSA). TSMC 65 nm.

- Correlation in the MPA

- ◎ 2×8 MPA per module, ~2000 bumps / MPA, ~30,000 macro-pixels

- Connectivity and data formats as for 2S modules

- Service Hybrid split in two boards (readout and power) since the module is 1/2 length

- ⊙ Sensors  $\rightarrow$  CBCs, CBCs  $\rightarrow$  CIC, CIC  $\rightarrow$  GBT on Service hybrids

- Power from Service Hybrid to all chips

- System fully efficient in layers 2-3

- Limited by bandwidth in layer 1 for the stub data

- With <PU> = 200 as design goal, the high speed version of the LP-GBT will be needed!

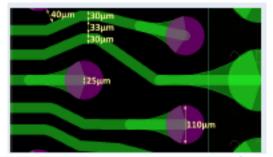

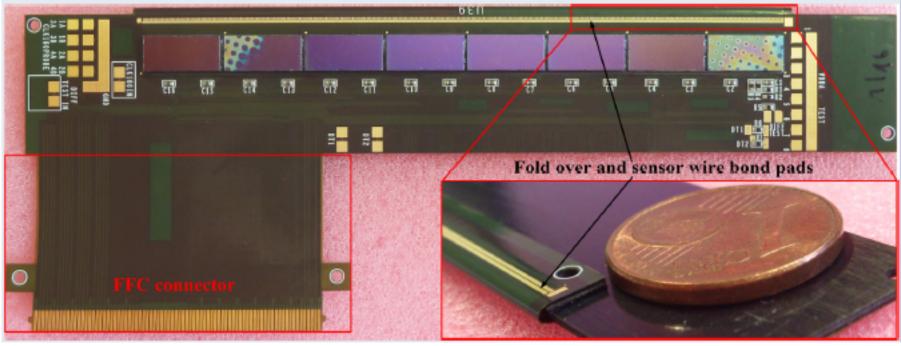

# High density flex hybrids

25  $\mu$ m double-sided polyimide core layer, plus two single-sided 12.5  $\mu$ m polyimide layers on either side. 25  $\mu$ m coverlay on the bottom, solder mask on the top. Total thickness ~130  $\mu$ m.

2S hybrid. Wirebonding pitch to sensor 90  $\mu$ m × 2 sensors. Bump bonding pitch of CBC 250  $\mu$ m, 800 bumps × 8 chips. High-density routing: thinnest line 30  $\mu$ m with spacing 33  $\mu$ m.

Prototype with Flat Flexible Connector (CIC not yet available). Eventually will be wire bonded to the Service Hybrid.

#### Key element for a lightweight module design!

#### Front-End powering with on-board DC-DC converters

#### 2S module

Design of CBC3 in progress Specification document prepared and being discussed (...a lot of details to be addressed!) In principle the final chip – although there is contingency for one further iteration Submission next year.

#### PS module

MPA-light qualification well advanced, specs fully met! Small-size chip, analogue front-end final, part of the digital logic Structures for clock distribution and SLVDS data link OK Memory cell subcontracted to a company, first iteration not fully successful Work in progress...

Started working on the definition of the SSA specifications

#### <u>Common</u>

CIC specs almost fully defined, good progress in the design Implementation in Verilog Plan to submit first prototype in 2016 (funds available)

# 2S module prototyping

#### Dummy module built for assembly studies

Prototype readout hybrids with 8xCBC2 Inactive dummy sensors 3d-printed service hybrid dummy

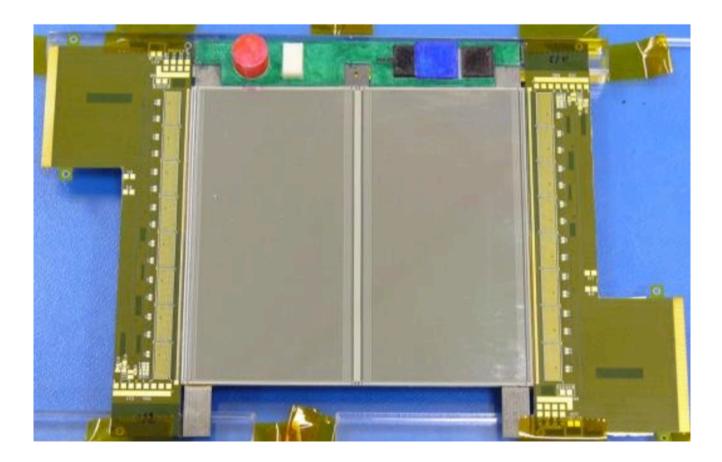

## **PS module prototyping: MaPSA-light**

- <u>MacroPixel</u> <u>SubA</u>ssembly: MaPSA

- Scaled down version of the pixel part of the PS module

- MPA-light chip

- # of pixels: 3 x 16

- Pixel size: 100 x 1446 μm

- Chip size 1.7 x 6.5 mm<sup>2</sup>

- Process: 65 nm TSMC

- PS-p light sensor

- Material: FZ p-type

- Thickness: 200 µm

- # of pixels:  $48 \times 6$  $\rightarrow 6 \times MPA$ -light chips

- Sensor size 7.8 x 12 mm<sup>2</sup>

- Produced at: CiS, Erfurt DE

Status: assembly ordered from 3 different vendors Test system under development

Next (if successful): build a PS-light module

Small prototype: MAPSA light

All parts coming together to assemble full-size functional 2S modules Without service hybrid and without CIC, based on CBC2 hybrids Full-size 2S module prototypes very soon! ... in the beam in November?

Following successful MPA-light → MaPSA-light being assembled If all OK, small-size PS modules prototypes next year

#### **Optimization of the detector**

#### **Optimization of the detector**

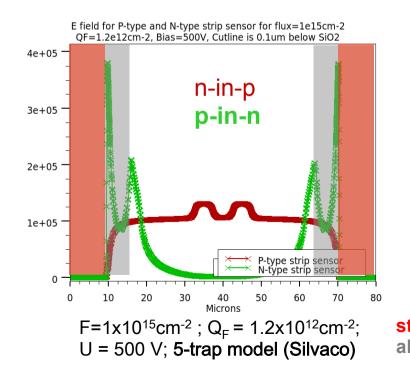

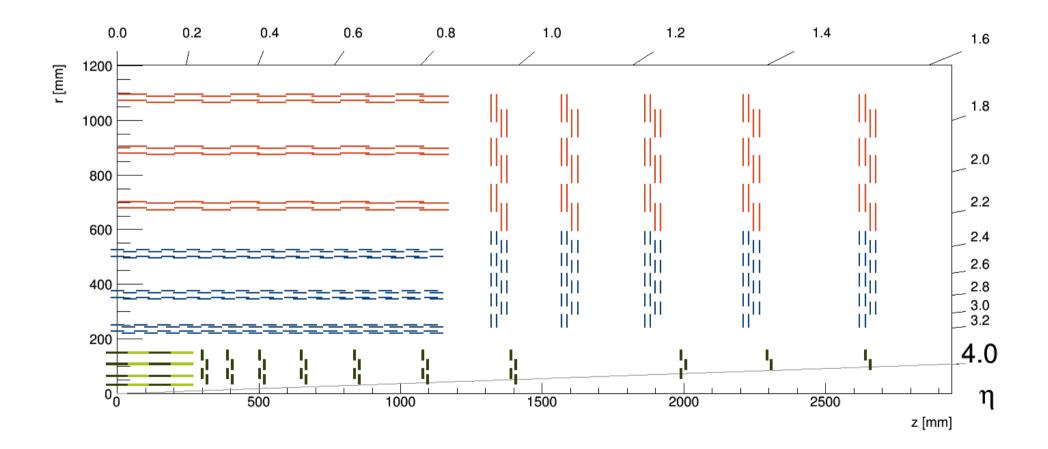

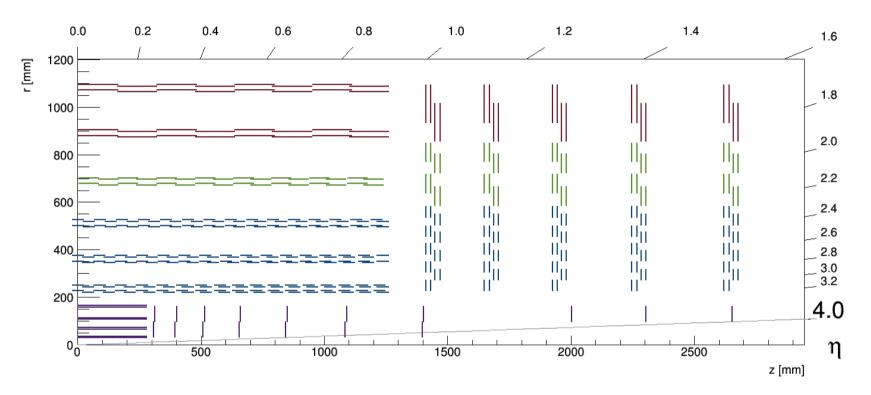

#### **Detector standalone modelling: tkLayout**

Flexible tool to create 3D models of the tracker from simple configuration files and user-defined rules

Includes both active surfaces and inactive materials

#### Simple (semi-automatic) modelling of services

r [mm] 0.1 1200 1000 0.08 800 0.06 600 0.04 400 Ալլ 0.02 200 0 1000 1500 2000 3000 500 2500 z [mm] Material of sensitive elements Dedicated volumes for supports and services

Radiation length map

#### Simple (semi-automatic) modelling of services

r [mm] 0.1 1200 1000 0.08 800 0.06 600 0.04 400 0.02 200 0 1000 2000 2500 3000 500 1500 z [mm] Automatic routing of Material of sensitive elements outgoing services Dedicated volumes for supports and services

Radiation length map

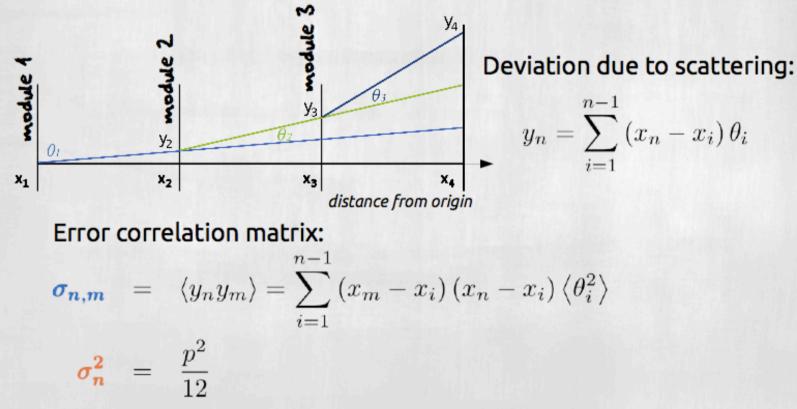

Implements estimates of tracking performance

- Use measurement errors to estimate the errors in track fit parameters

- Multiple scattering treated as (correlated) a measurement error

#### > Provides:

- Estimates of the tracking precision including multiple scattering

- ★ For both offline tracking and L1 tracking

- All useful summaries/statistics

- ★ # of modules, active surface, # of channels, total power, total weight, etc etc....

- Radiation length and interaction length vs rapidity

- Map of leakage current in all modules after irradiation

Input from FLUKA used to optimize module cooling

- $\odot$  Stub  $p_T$  resolution for each module location

- ★ Used to optimize distribution of sensor spacing in the Tracker volume

- ⊙ ... and more...

### > Outputs:

- Mini web-site with full information

- Geometry files for CMSSW

- Module coordinate files for the 3D modelling of the detector structures

- Geometry files for FLUKA

#### Some infos from tkLayout

# **Acceptance window**

Width 5÷15 channels in the barrel, 2÷12 in the endcap

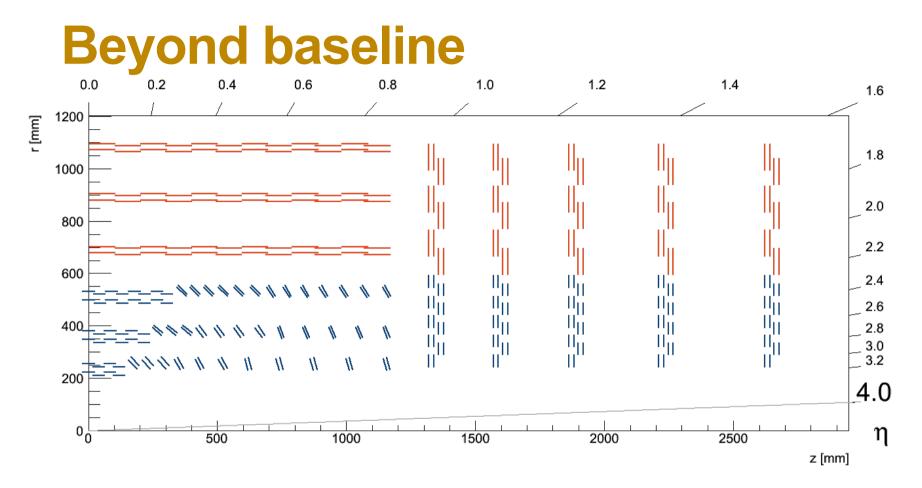

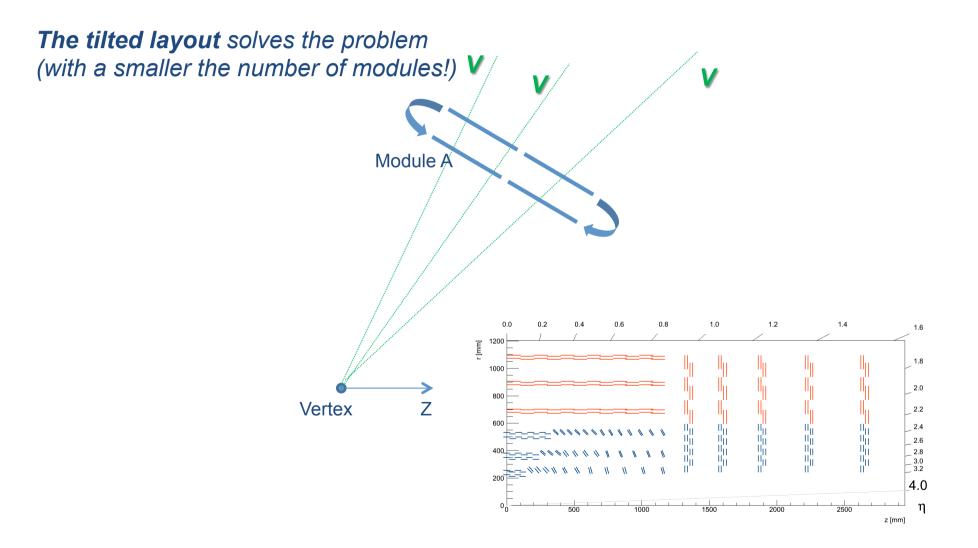

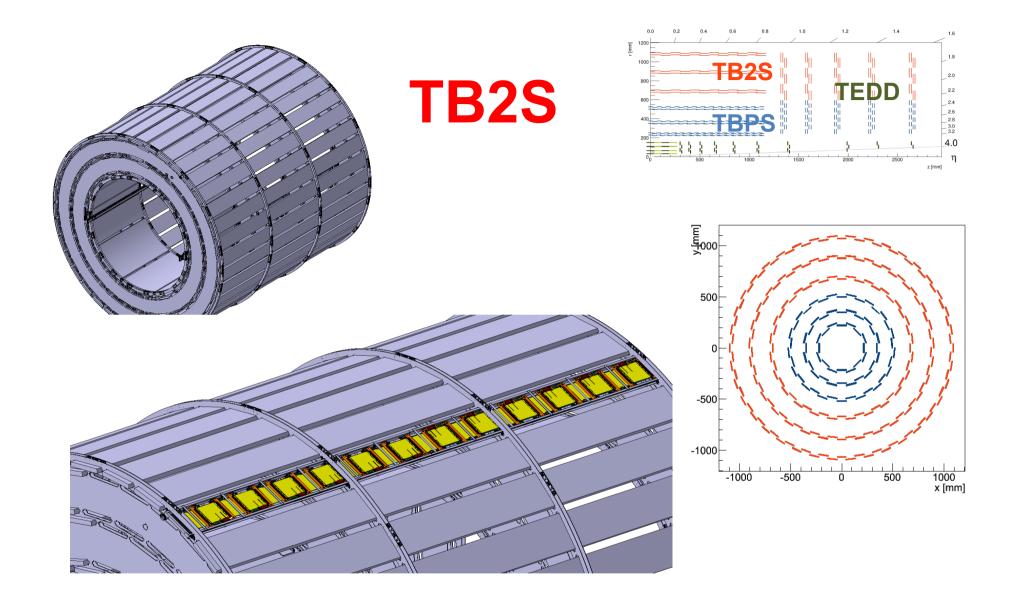

Variant of TBPS with progressively tilted modules

- Short central section followed by groups of rings with same tilt

- Same coverage and ~same tracking performance with a smaller number of modules

## Is it really a good idea???

Many tracking detectors have been designed and built... ... and they don't look like that!

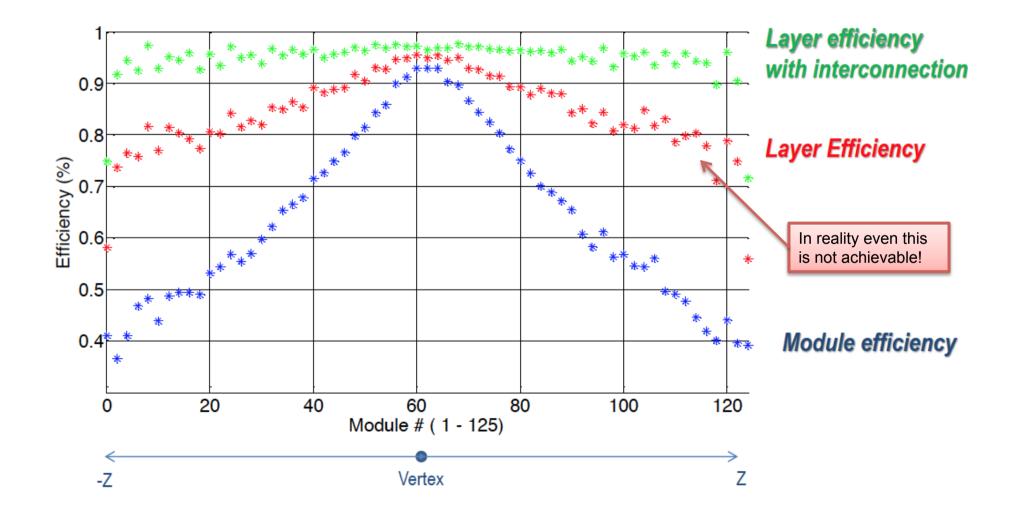

# Stub Finding logic efficiency results

## Stub Finding logic efficiency results

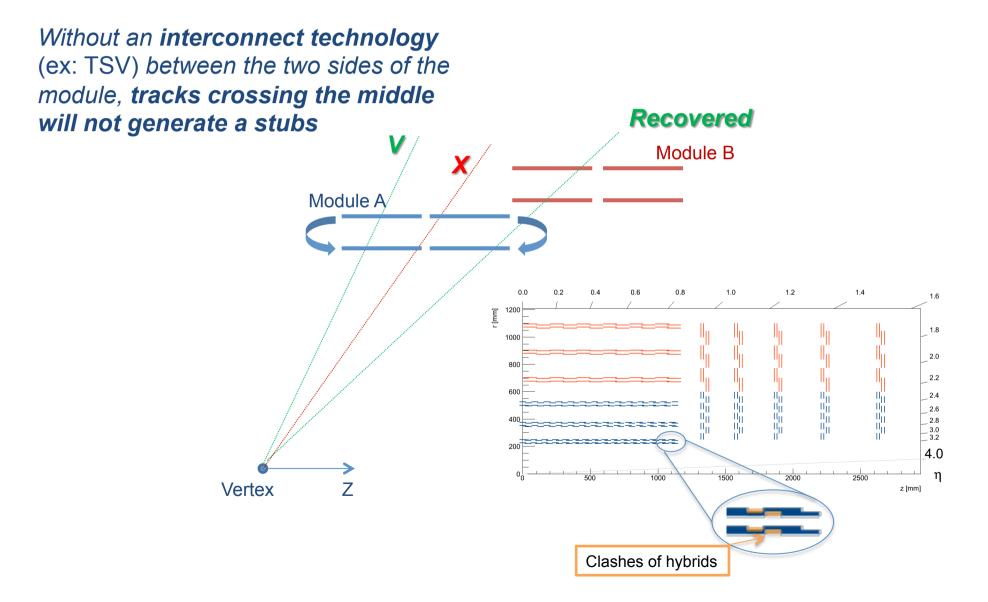

# Through-Silicon Vias would be required to achieve acceptable efficiency in the "flat" layout

# Stub Finding logic efficiency results

#### Three specific facts favour the tilted layout

#### Stub finding efficiency

(1) Avoids needs of TSVs to interconnect the two halves of a PS modules

(2) Avoids huge overlaps between consecutive modules in z Impossible to implement at the edge of the barrel anyway

#### Module length

(3) Modules only 5 cm long in the z direction because of technology limitations Aggravates effects (1) and (2), but makes tilt possible!

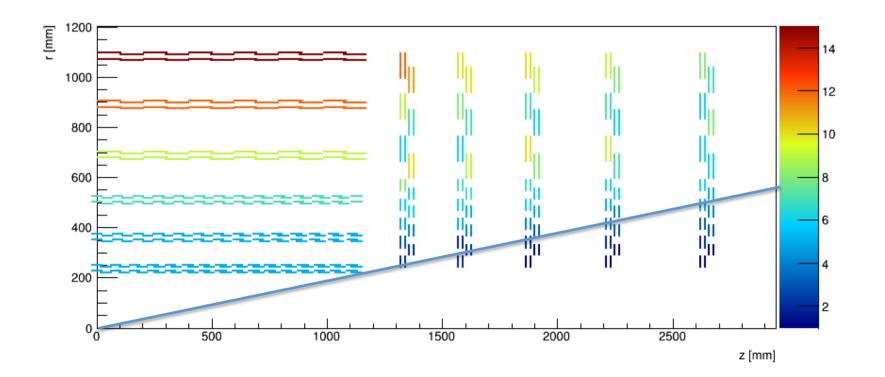

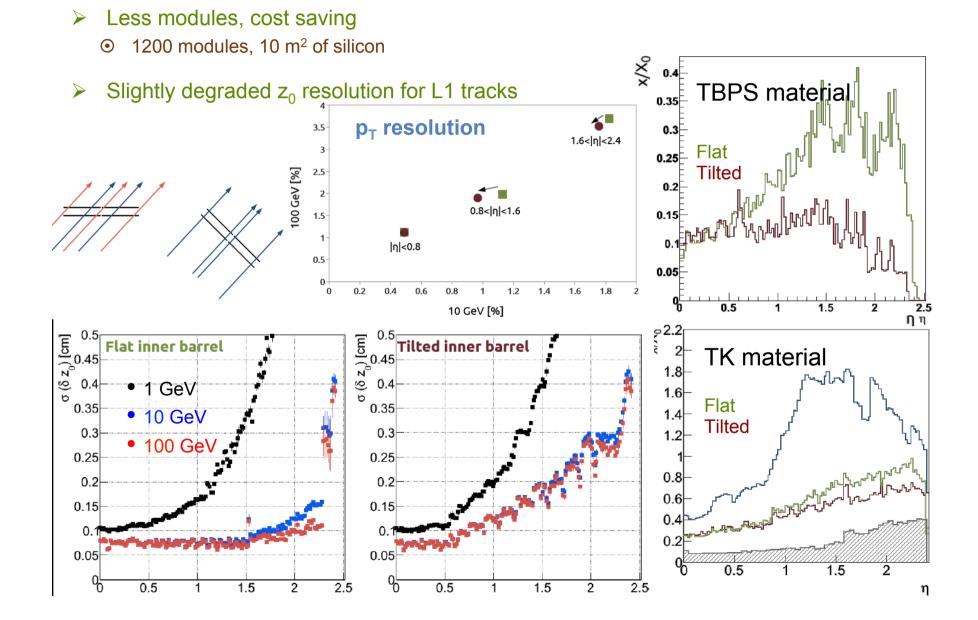

# **Tilted TBPS - performance**

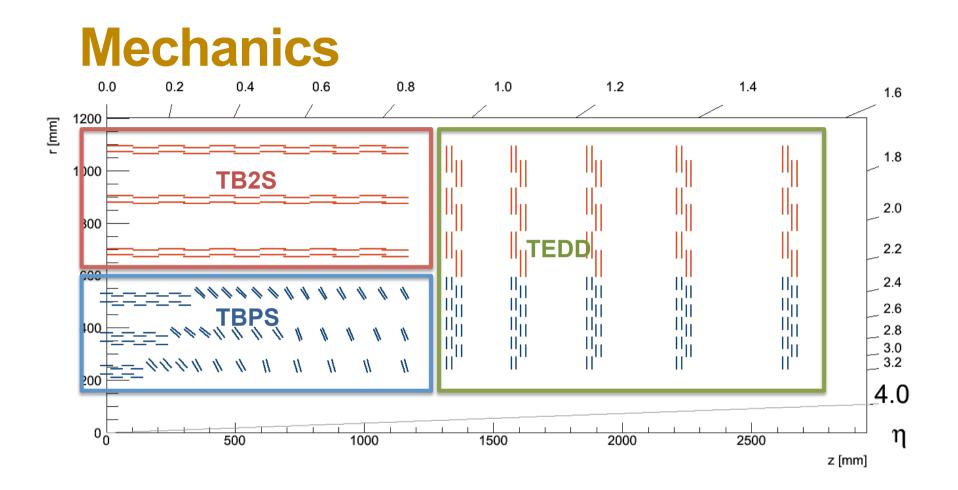

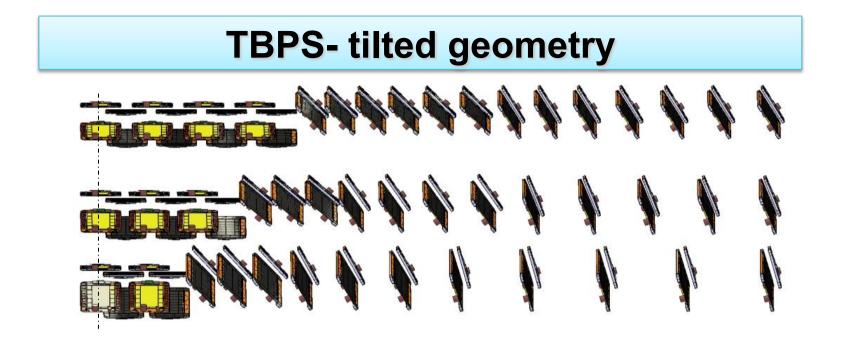

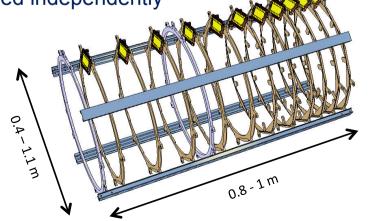

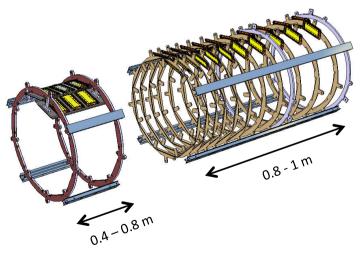

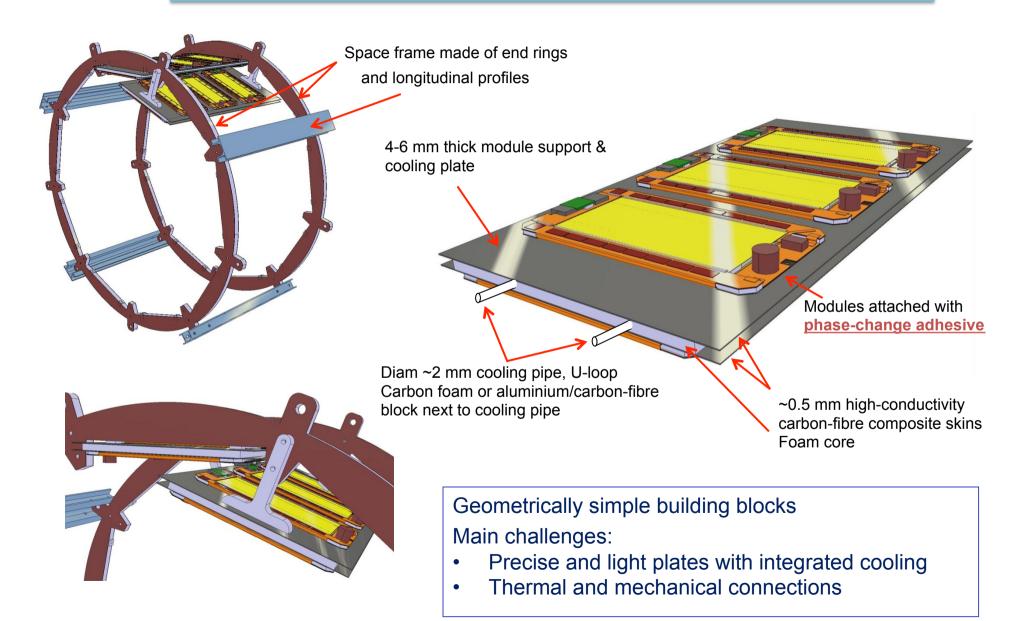

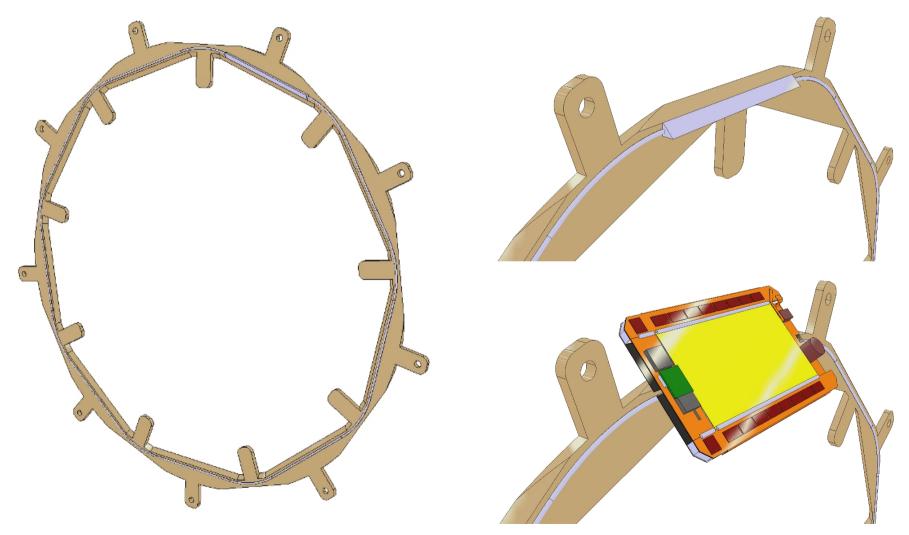

> Less material, equal or better tracking performance, better stub coverage, no need of TSVs

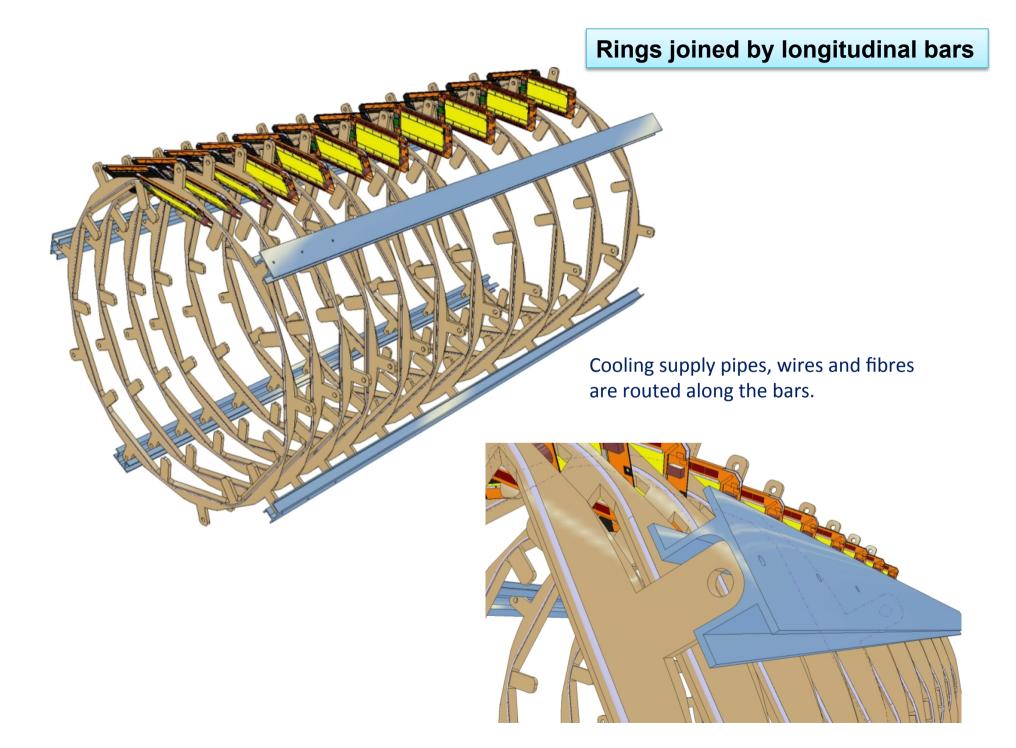

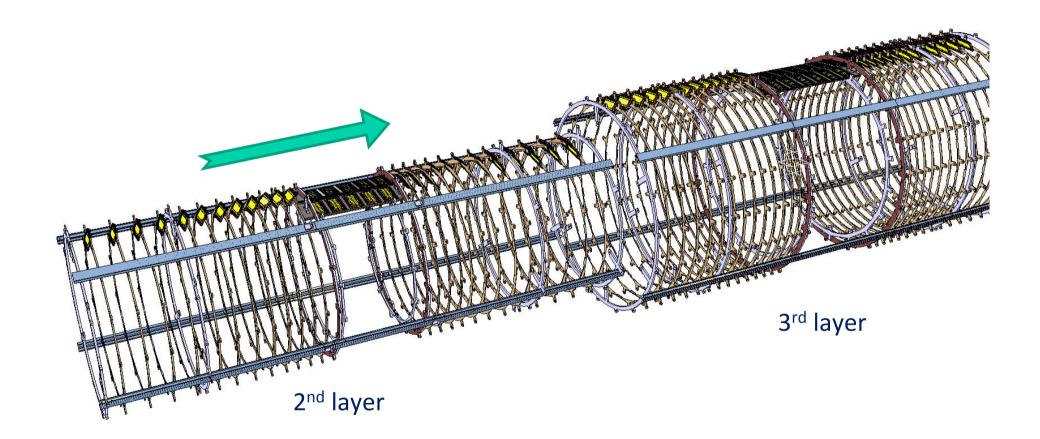

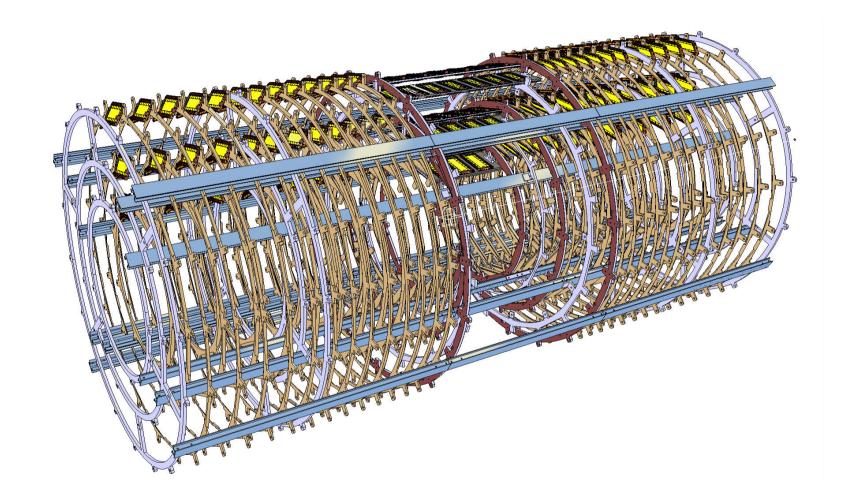

Central flat section made of "staves"

Tilted sections made of "rings"

Three layers assembled independently

#### Stave: modules glued on CF/foam panels

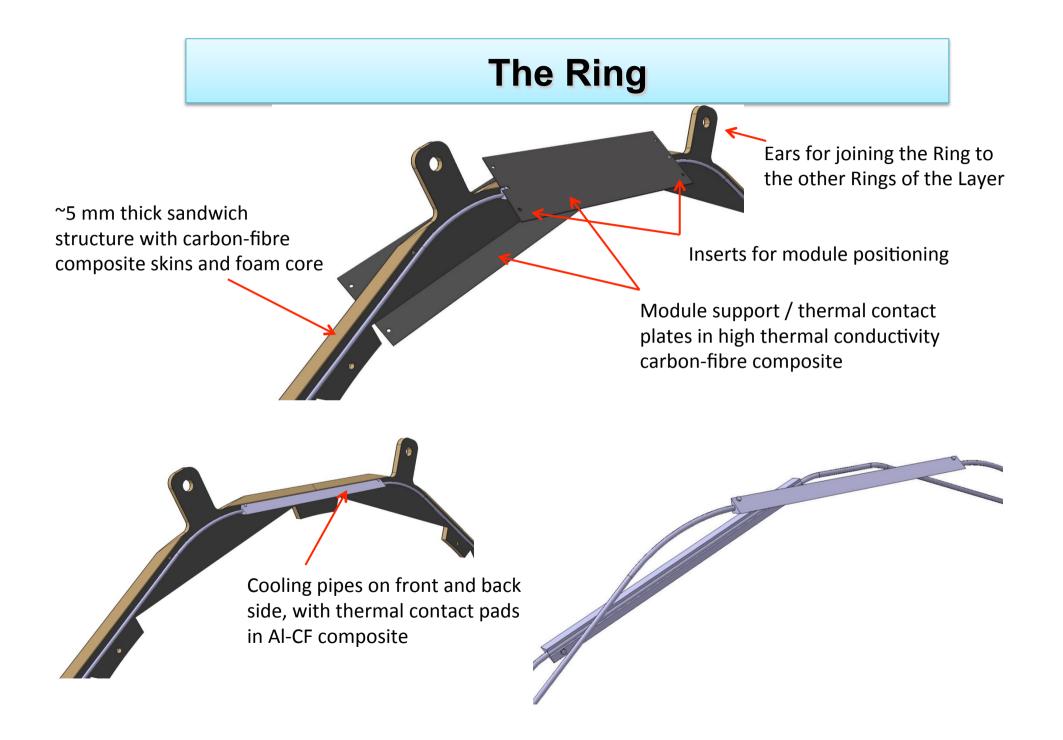

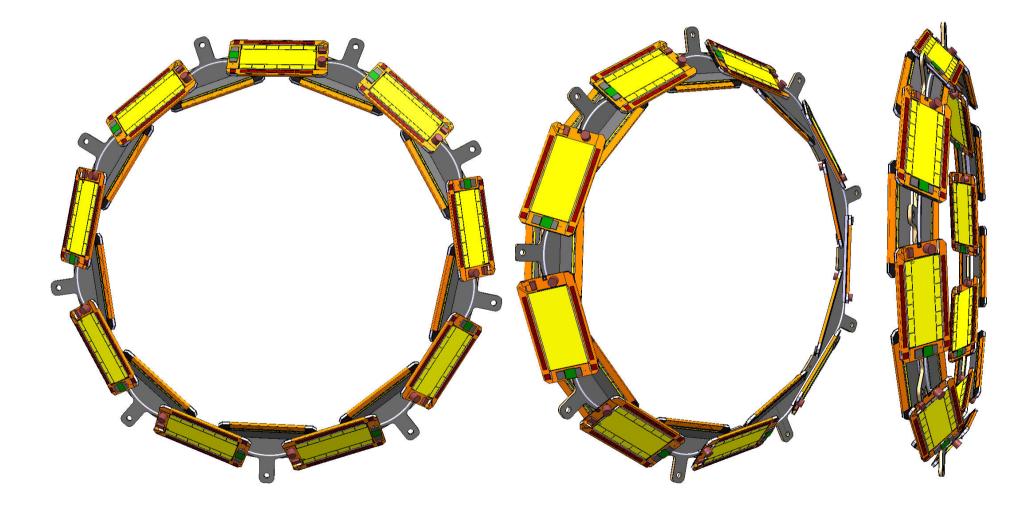

### CF/foam "rings" support modules with the required tilt angle

• Flat disk with cooling pipes and module supports on each side.

### **Ring with modules**

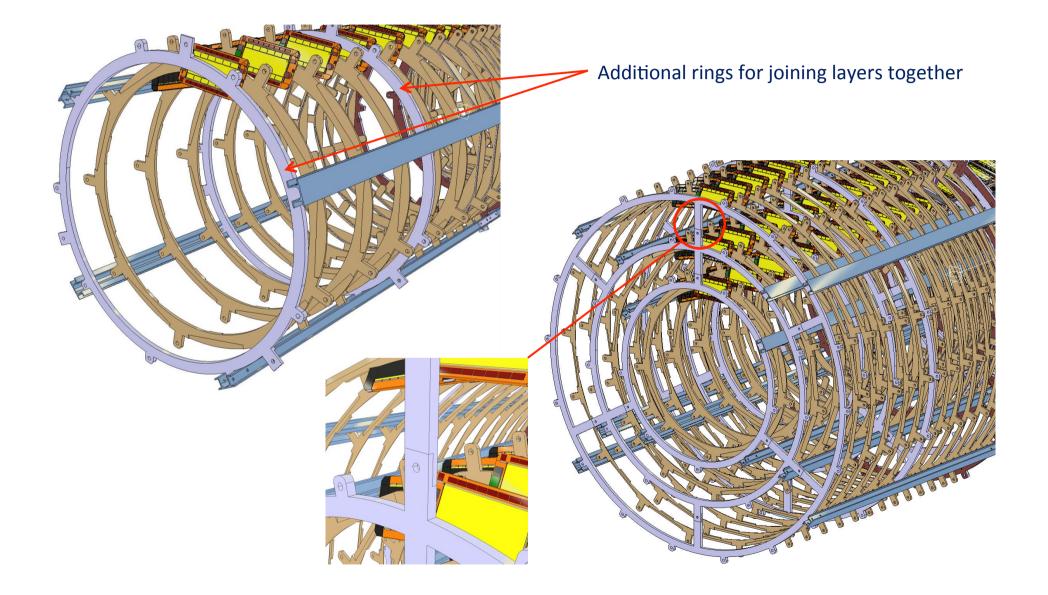

#### **Joining layers**

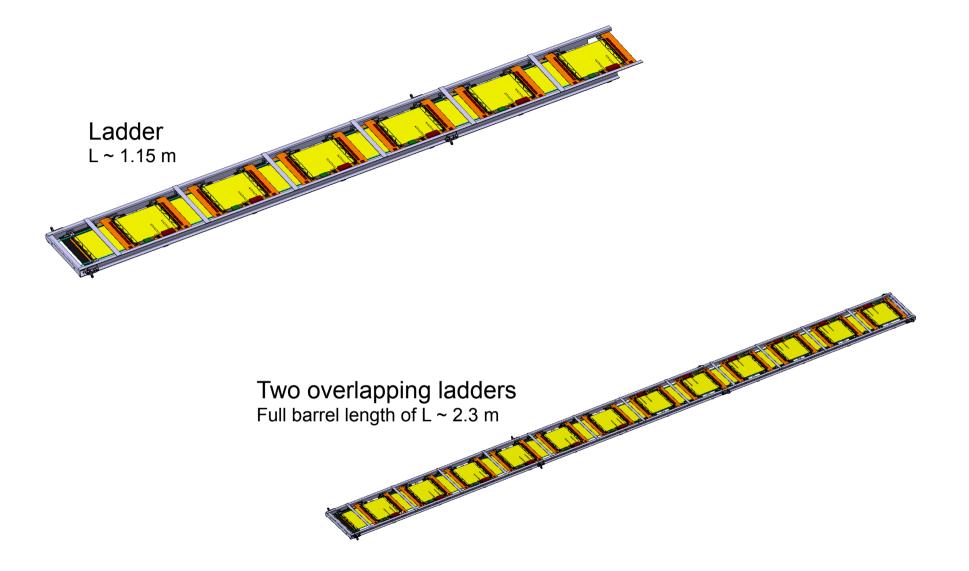

Z overlap within one "ladder"  $\phi$  overlap between consecutive ladders

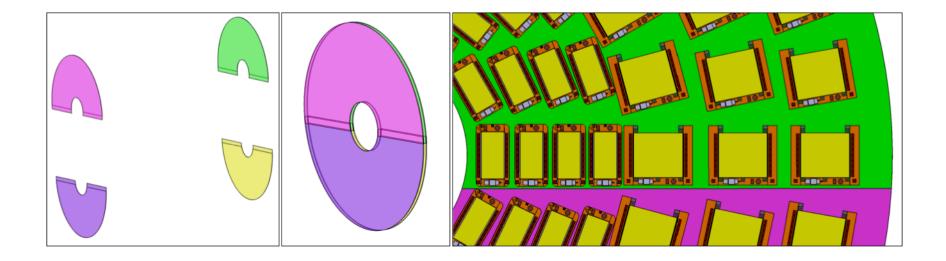

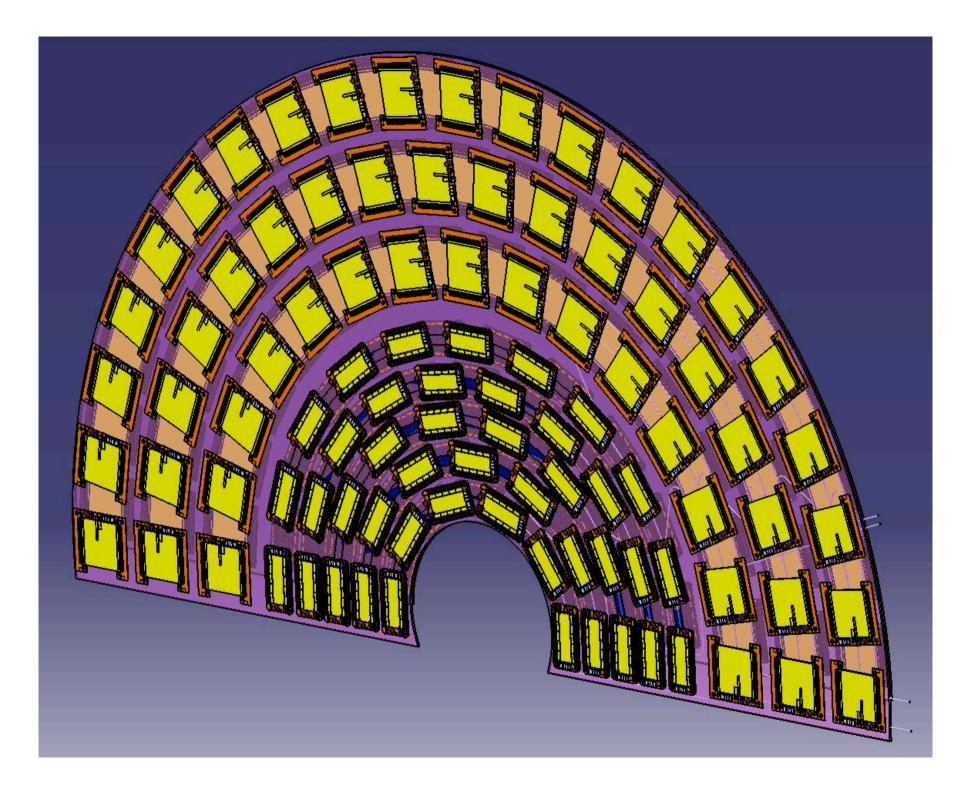

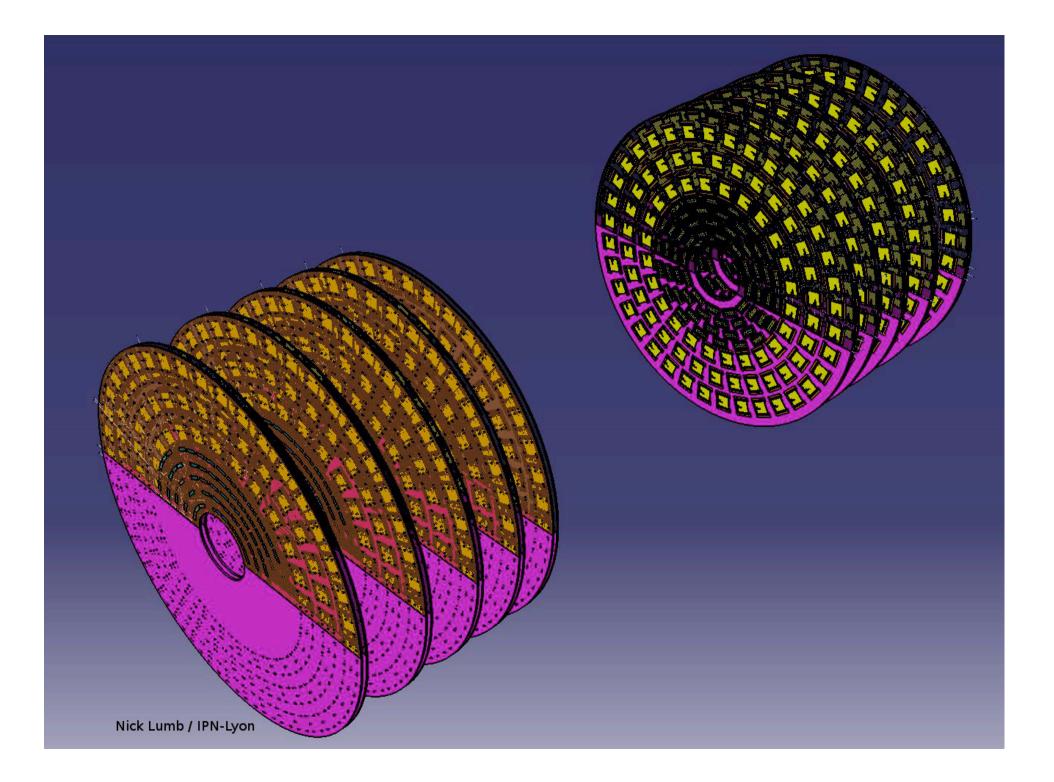

## Tracker End-Cap Double Disks (TEDD)

Modules mounted on four surfaces on two disks, each made of two dees

$\odot \phi$  overlap within disk, R overlap with next disk

- Same rectangular modules as in the barrels

- 9 rings of PS modules + 6 rings of 2S modules

- Cooling pipes embedded in the disk structure, wires and fibers running above and between the modules

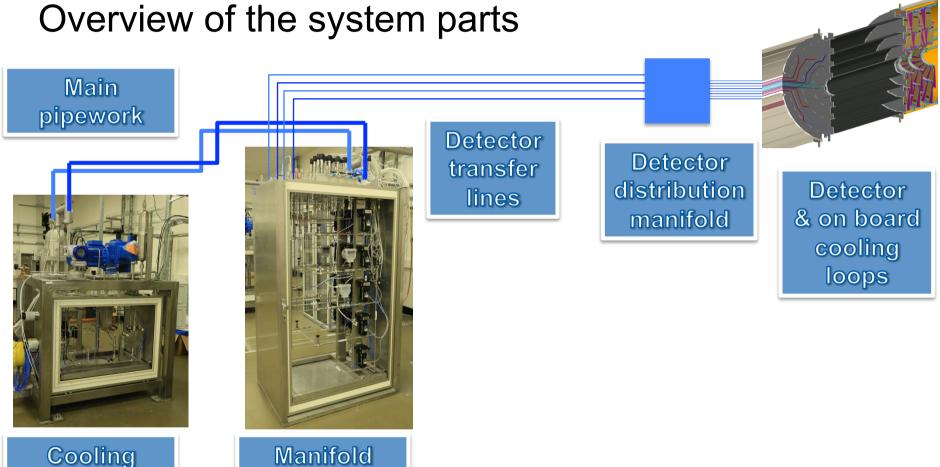

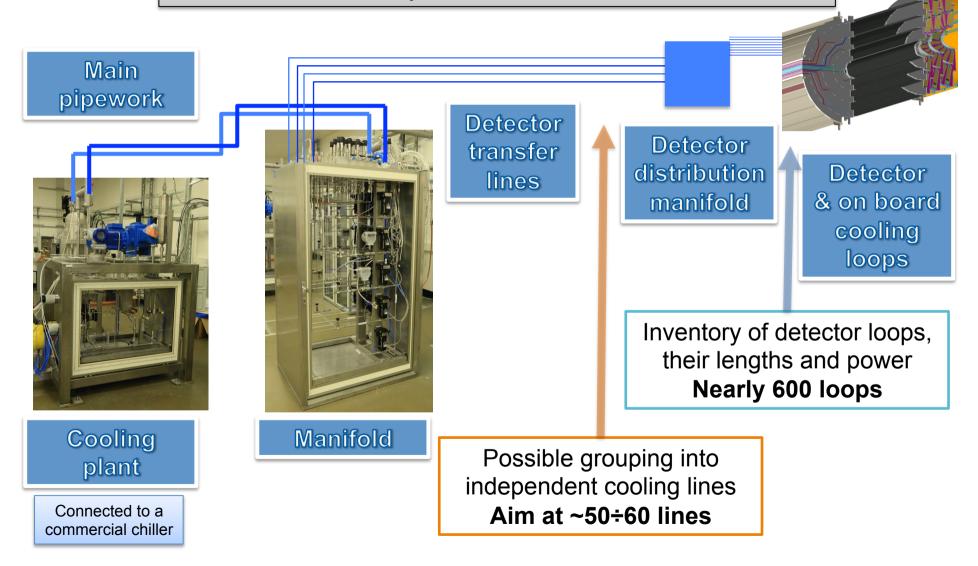

### TEDD: sector-wise cooling loops

Cooling plant

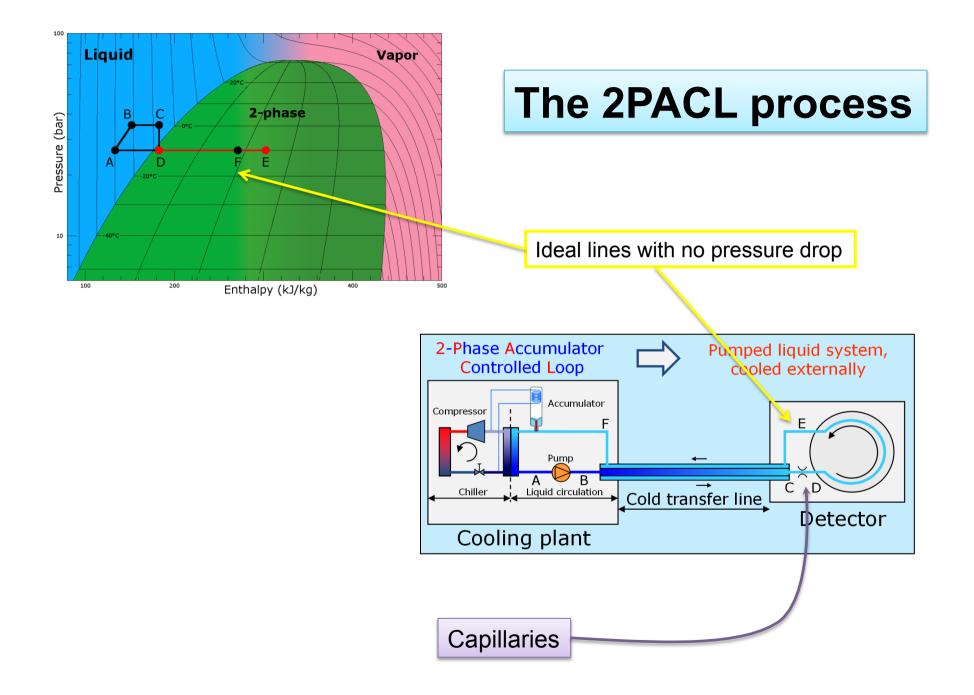

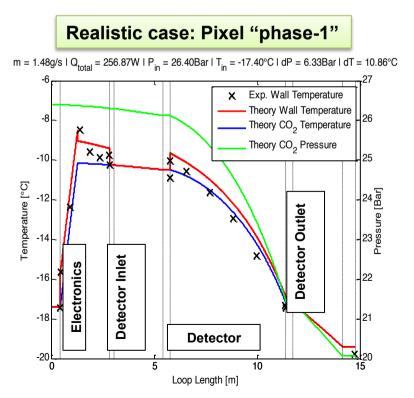

### **Chosen cooling technology: two-phase CO<sub>2</sub>**

#### Advantages of evaporative cooling

Heat Transfer Coefficient higher than for liquid cooling Limited temperature excursion on the detector

(isothermal evaporation - cooling exploits latent heat)

#### Advantages of CO<sub>2</sub>

Large latent heat of evaporation Low liquid viscosity Particularly high heat transfer coefficient Very convenient fluid to work with (environmental friendly, not activated) Convenient range of operating temperature -45°C to +25°C Easier at low temperature

## In practice a quite complex system...

Detector loops must be properly sized (avoid dry out)

Flow distribution must be stable wrt to load changes

In reality there is pressure drop along the detector loops

May require some pre-heating to ensure that the  $CO_2$  boils...

Higher operating temperature  $\rightarrow$  higher pressure rating

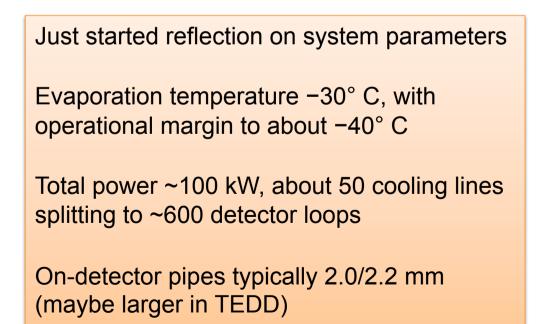

## Study of cooling system started

Reasonably solid estimate of power consumption - Detector modularity defined <u>Common system for Outer Tracker and Pixel</u>

L1 tracking

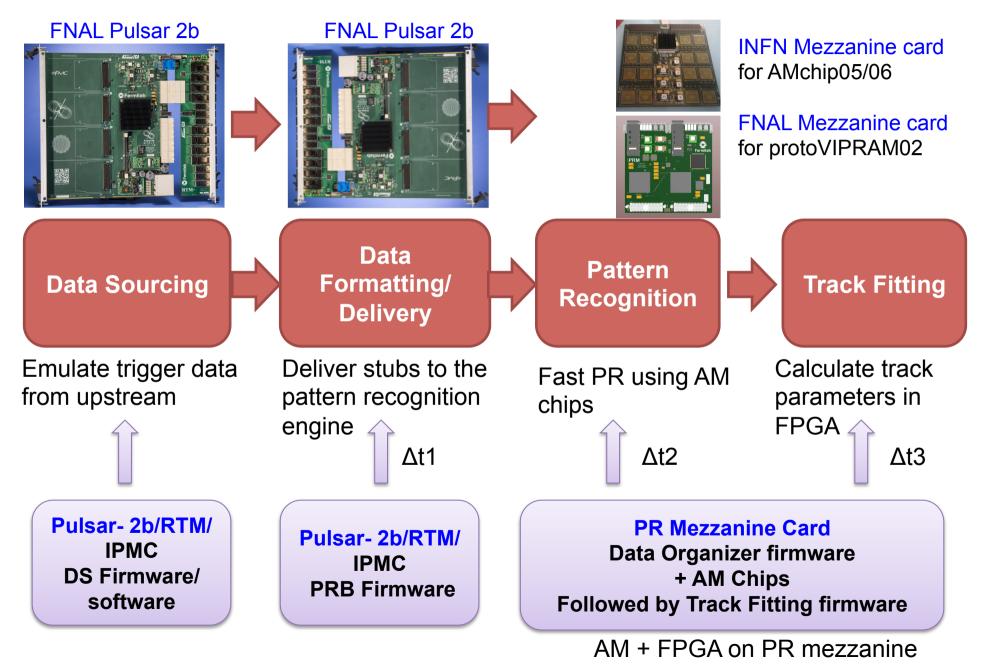

### **Three methods**

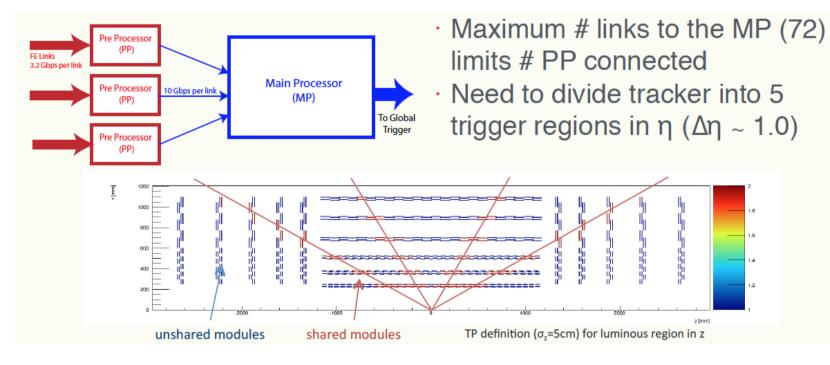

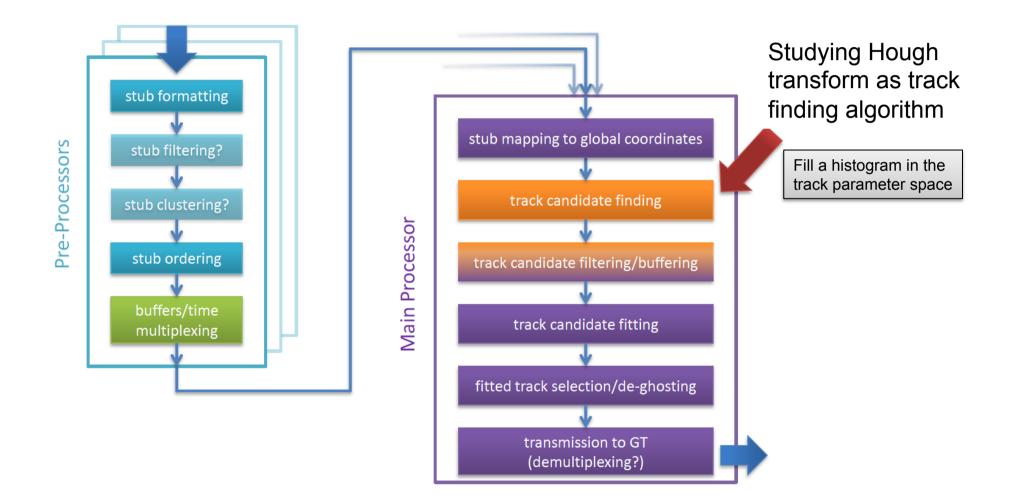

Associative Memories + track fitting Time-Multiplexed architecture – Hough Transform + track fitting Tracklet-seeded road search

## AM concept

### Large bank of patterns ("roads") stored in a dedicated Associative Memory chip

- Roads are defined with coarse-resolution coordinates

- → Keep the number of patterns manageable

- Stub coordinates are loaded in the Memory

- Matched patterns are the track candidates

#### Refit track candidates with full-resolution coordinates

- Achieve ultimate resolution, remove fake combinations / duplicates

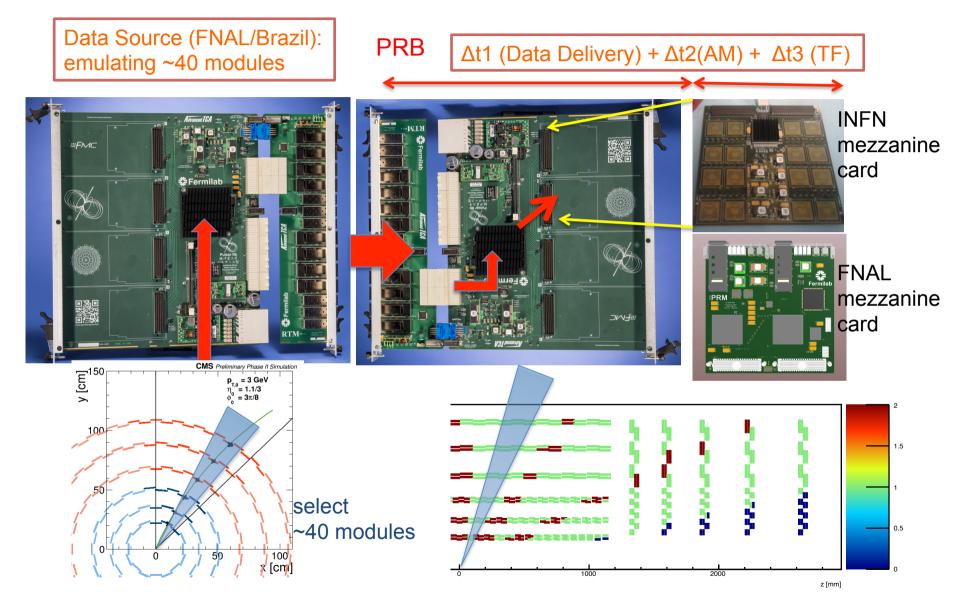

### AM + FPGA approach: Data Flow Stages/Hardware

### **Board Level Demonstration in 2015**

Details are being worked out

### Full-Scale Demonstration (goal of 2016)

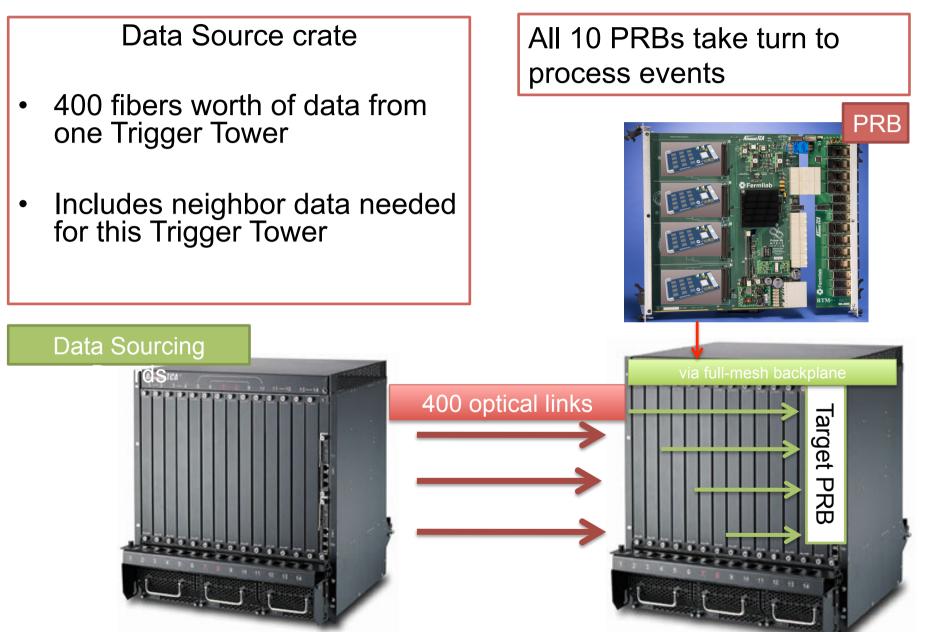

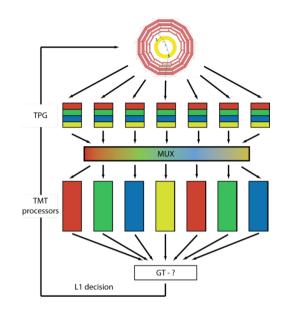

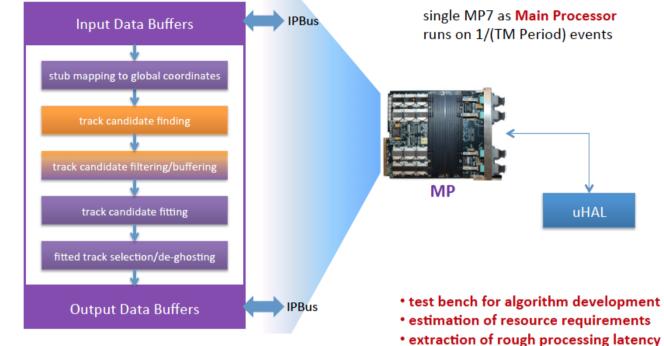

## **TMT** architecture

Principle:

- all data from one event arrives in one processing node, over N BX (the time multiplexing period)

- round-robin scheduling over N nodes, each node processing one event

# Main steps

### **TMT demonstrator**

System available in 904, use MP7 as main processor

Firmware implementation of Hough Transform array ready being integrated with infrastructure firmware

First tests with single board during the summer

Expect first slice tests towards the end of the year

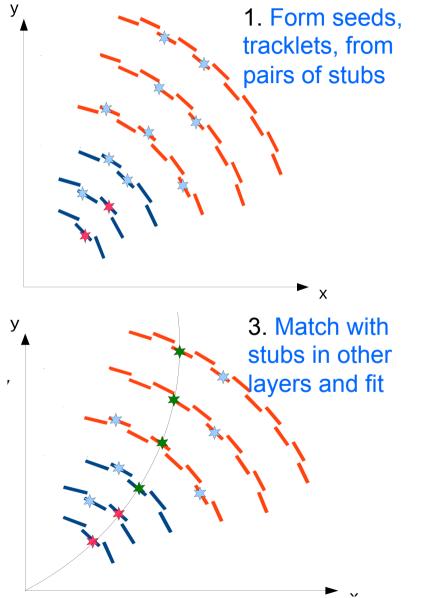

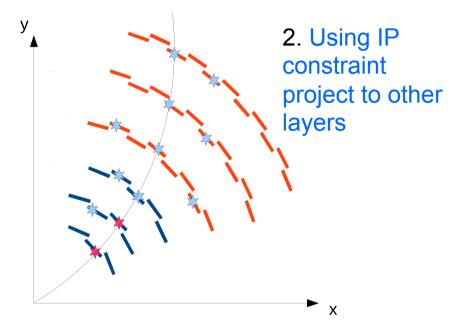

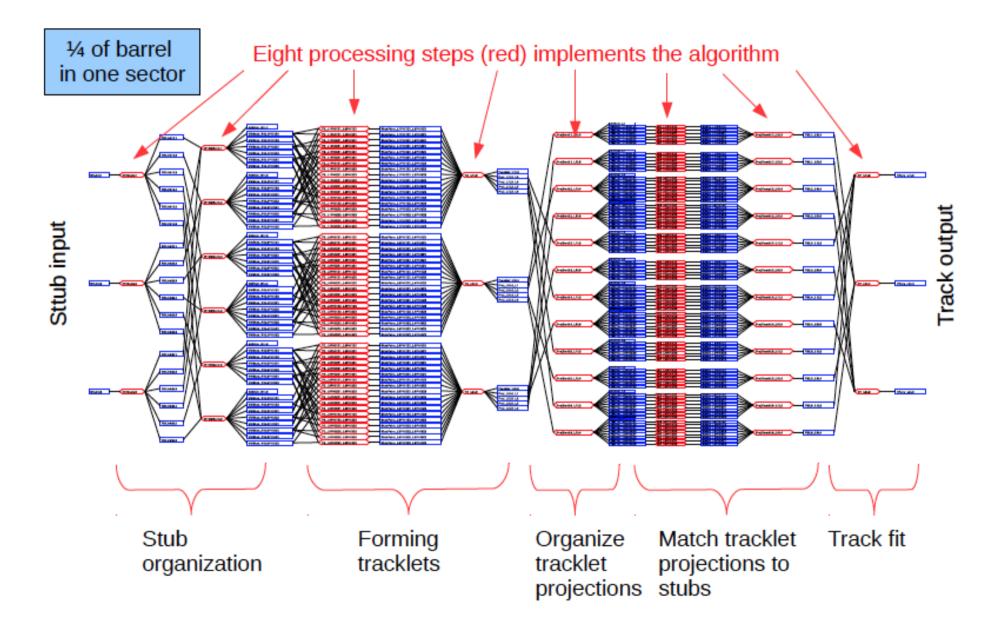

# **Tracklet Algorithm: Road Search**

### Extensive simulation program:

- High level simulation used in TP studies

- Low-level (bitwise) C++ emulation of algorithm

- Implementation in Verilog for FPGA

Steps validated against each other

28 phi-sectors Corresponding to the size of a sector containing a 2 GeV track

## **FPGA** implementation

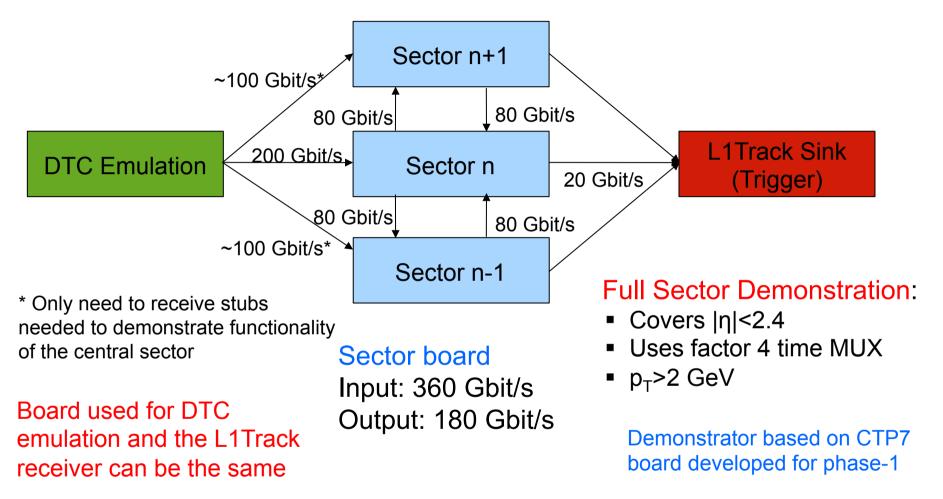

## **Tracklet Demonstrator**

Demonstrate full tracking in a sector, including communication with neighbour sectors Measure latency from DTC output to L1 tracks available

## L1 tracking

### **Three methods**

Associative Memories + track fitting Time-Multiplexed architecture – Hough Transform + track fitting Tracklet-seeded road search

### Hardware demonstrators under development – goals:

Provide evidence that L1 tracking is feasible Support statement that L1 tracking will fit in 5 µsec

### Timeline

First exercises within this year Full sector demonstrator before the end of next year (in time for TDR)

Review of demonstrators will (hopefully) provide insight on best way forward

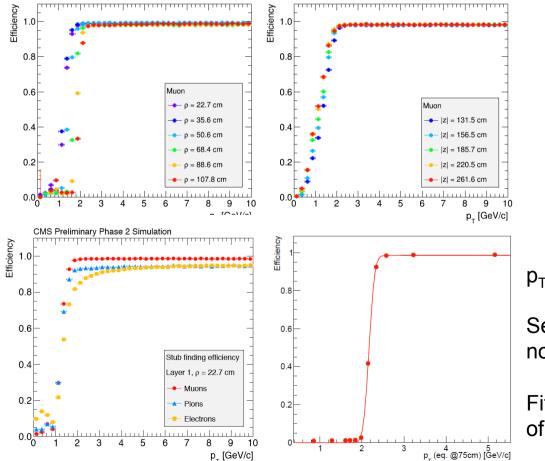

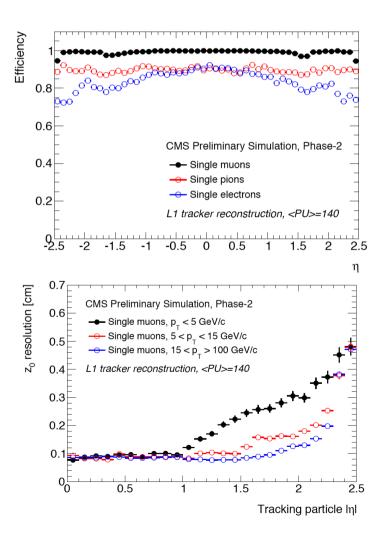

# Some performance plots

## **Stub finding performance**

- Muon stub finding efficiency in all layers (barrel, endcap)

- Barrel layer 1 for muons, pion electrons

- Effect of interactions

- Efficiency measured on DESY beam with 2-CBC2 module prototype

$\boldsymbol{p}_{T}$  simulated with module tilt

Selected threshold equivalent to a nominal  $p_T$  cut of 2.14 GeV @ 75 cm

Fit to data gives effective threshold of  $2.2 \pm 0.1$  GeV

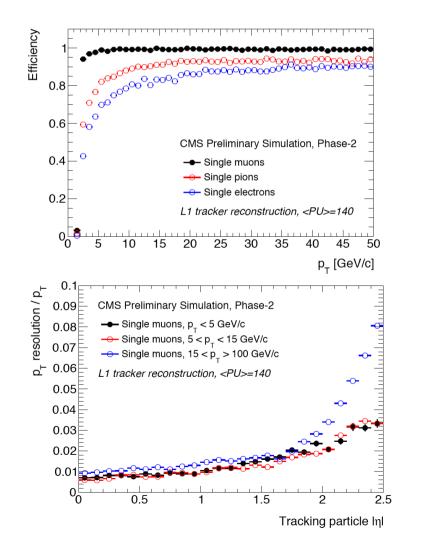

## Level-1 track finding

Track finding performance taken from "tracklet" method

#### ● N.B. Track finding not demonstrated in hardware

★ Indication of the performance that should be achievable

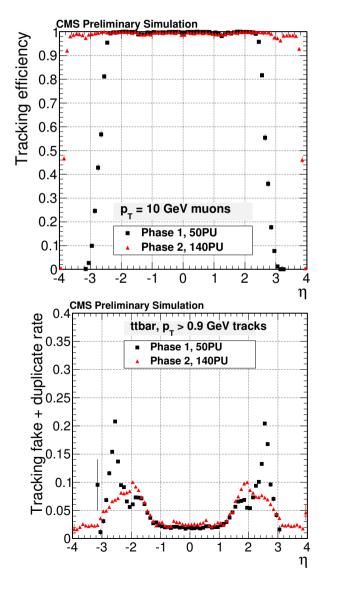

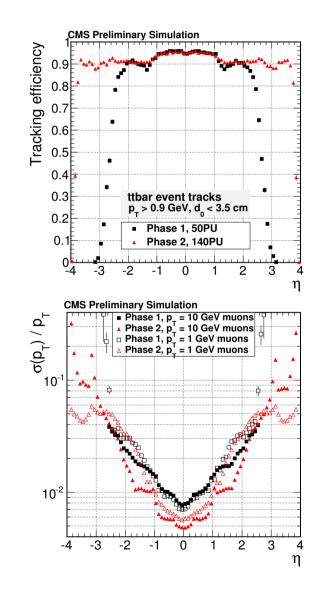

## **Offline tracking**

### Compare Phase-1 @ 50 PU with Phase-2 @ 140 PU

## **The Outer Tracker in numbers**

### OLD

• N of modules 15,148

Total active surface 210 m<sup>2</sup>

- Total n of strips 9.3 M

- Power in the tracking volume ~ 30 kW

### NEW

- N of modules 15,508

- 7084 PS modules (-1200 if tilted)

- 8424 2S modules

- Total active surface 218 m<sup>2</sup>

- 155 m<sup>2</sup> strips (2S)

- 31 m<sup>2</sup> strips (PS)

- 31 m<sup>2</sup> macro-pixels (PS)

- Total n of strips 47.8 M

- Total n of pixels 218 M

- Power in the tracking volume

~ 80 kW

### Estimated CORE cost in MCHF

|                                 | Oute | r Tracker | Inner Pixel |

|---------------------------------|------|-----------|-------------|

| Modules                         | 2S   | 27.9      | 11.8        |

|                                 | PS   | 22.8      |             |

| Mechanics                       |      | 6.6       | 3.6         |

| BE electronics                  |      | 12.4      | 2.0         |

| Power system                    |      | 6.1       | 1.4         |

| Services, cables and pipes      |      | 5.5       | 1.1         |

| Cooling system                  |      | 4.2       | 0.6         |

| Infrastructure and installation |      | 3.5       | 2.7         |

| TOTAL                           |      | 89        | 23          |

|             | Outer Tracker | Inner Pixel |

|-------------|---------------|-------------|

| Austria     | Х             |             |

| Belgium     | Х             |             |

| CERN        | Х             | Х           |

| Finland     |               | Х           |

| France      | Х             |             |

| Germany     | Х             | Х           |

| Greece      | Х             |             |

| India       | Х             |             |

| Italy       | Х             | Х           |

| Pakistan    | Х             |             |

| Spain       |               | Х           |

| Switzerland |               | Х           |

| UK          | Х             |             |

| US          | Х             | Х           |

BACKUP

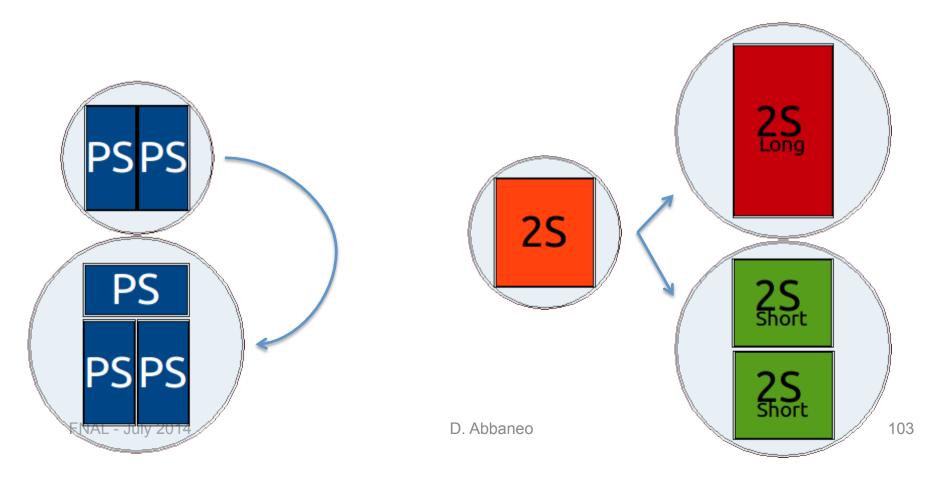

## A variant: sensors from 8"

- PS module: keep the same design, produce 3 sensors from 1 wafer

- Sensors surface could be slightly enlarged if decision taken soon enough (960  $\rightarrow$  1024 channels)

- Possibly small reduction in N of modules

- 2S module: modify module design by changing strip length

- **2S\_long:** stretch to wafer edges. Sensor 10 cm  $\rightarrow$  16 cm (strips 5 cm  $\rightarrow$  8 cm).

- **2S\_short**: shorten to fit two sensors in one wafer. Sensor 10 cm  $\rightarrow$  8 cm (strips 5 cm  $\rightarrow$  4 cm).

# Layout for 8" production

- 2S\_long used in the outer region

- 2S\_short used in the intermediate region

- E.g. Outer barrel half-length goes from 12 modules to 16 modules (2S\_short) or 8 modules (2S\_long)

- Further optimization possible!

# Summary: 6" vs 8"

- Layout with flat TBPS

- 27400 6" wafers or 18450 8" wafers

- Ratio 1.485

- Layout with tilted TBPS

- 25950 6" wafers or 17400 8" wafers

- Ratio 1.491

- The potential interest for the TK is mostly financial

- The designs are basically equivalent

- Bottom line: 8" is interesting if \$(8") << 1.5 × \$(6")

- Taking into account yield of all steps, up to module assembly