# **GigaTracKer: status report** F. Marchetto – INFN, Torino

- Introduction : detector generalities and specifications

- **Progress report about:**

- 1. Final and prototype sensors

- 2. Bump bonding

- 3. Cooling

- 4. Chip prototype design

- 5. DAQ for chip prototype

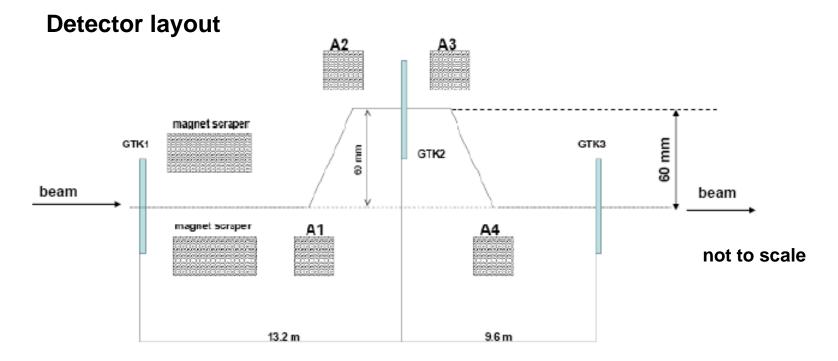

#### Introduction : detector generalities and specifications (1)

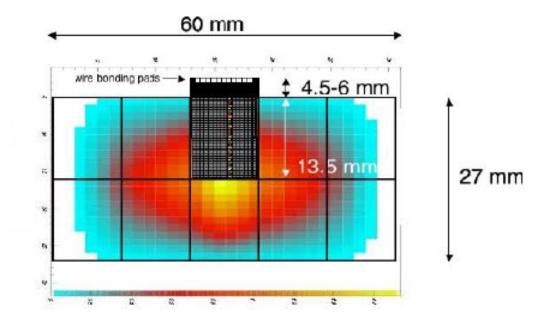

- Three same Si-pixel stations: each station (60x27)mm<sup>2</sup>

- pixel dimensions: (300x300)  $\mu\text{m}^2$  ; thickness: 200  $\mu\text{m}$

To measure the following quantities of the beam particles:

- direction ( $\sigma_{\text{RMS}}$  ~14  $\mu$ rad)

- momentum ( $\sigma_{\text{RMS}} \sim 0.15$  GeV/c)

- track time ( $\sigma_{RMS}$ ~ 200 ps/station -> ~ 150 ps/track)

## Introduction : detector generalities and specifications (2)

Mounted inside the vacuum tube

Dimensions of the stations to match the beam shape

Sensor technology: p-in-n

18000 pixels/ station -> 54000 pixels grand total

Sensor read-out via 10 chips

## **Progress report: final and prototype sensors**

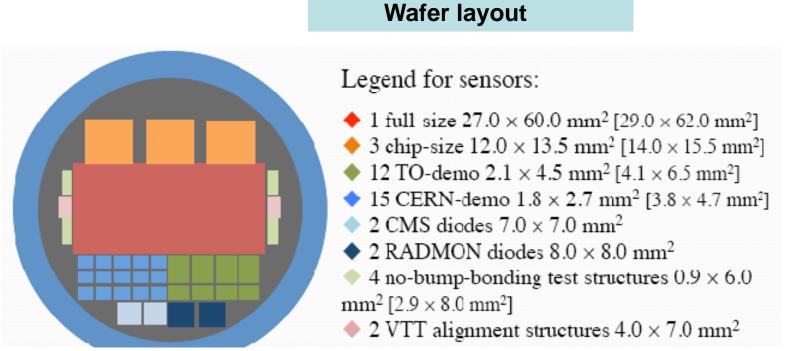

- a batch of 20 wafers (-> 20 sensors) has been ordered to FBK-Trento, Italy

- wafer layout is ready

- bump details (dimensions and position) defined

- wafer to be processed before the end of the year

# **Progress report: bump-bonding**

- <u>Development of the processes with VTT (Finland)</u>

- 1. Bump-bonding of the final chip to the sensor: standard technique

- 2. Bump-bonding of the prototype: how to bond a diced chip to a sensor ?

This is a technical problem related to the lack of room on diced chips for galvanic contacts for electroplating and thus it is impossible to apply the standard bumpbonding technique.

# **Two solutions are however available:**

1) Reverse rework: most promising and preferred solution

2) Au stud bumps practical only for ~100 pixels: technique off-shelves (backup solution)  $\frac{5}{5}$

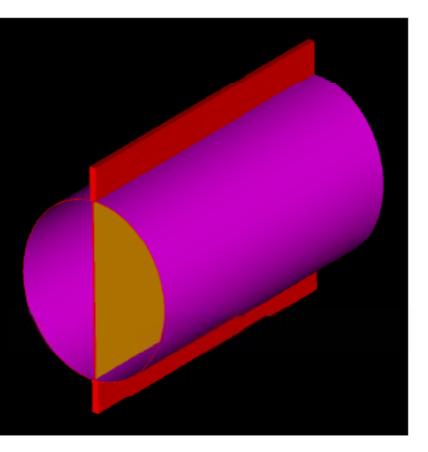

# **Progress report: cooling**

Power to be dissipated: 2W/cm<sup>2</sup> -> 32 W Targ

Target chip temperature < 5 °C

# Base solution: two half-cylinders of carbon fiber enclosing the sensor+chip

CONFIGURATION 2 – COOLING ANALISYS

| COOLING FLUID : NITROGEN |                | К     | °C    |

|--------------------------|----------------|-------|-------|

| Delivery temperature     | Ti             | 100   | -173  |

| Wall temperature         | Tw             | 275,6 | 2,6   |

| dT                       | T = (Tw – Ti)  | 175,6 | 175,6 |

| Tm                       | Tm = (Tw+Ti)/2 | 187,8 | -85,2 |

| NITROGEN PROPERTIES @ Tm and atmospheric pressure |    |          |  |

|---------------------------------------------------|----|----------|--|

| Specific weight (Kg/m^3)                          | ρ  | 1,79     |  |

| Specific heat (J/KgK)                             | Ср | 1041     |  |

| Thermal conductivity (W/mK)                       | λ  | 0,024    |  |

| Kinematic viscosity (m^2/s)                       | ν  | 1,34E-05 |  |

GENERATED POWER (W) Q = q x A = (2E+04) x (27E-03 x 60E-03) = 32,4

COOLING SURFACE (m<sup>2</sup>) S = 2 x (27E-03 x 60E-03) + 0,35E-03 x 2 x (27E-03 + 60E-03) = 3,34E-03

# **Progress report: chip prototype**

## Introduction:

• The challenging specification of the project is the hit time resolution we are aiming at:  $\sim$ 200 ps (rms) per station

• The sensor, bump-bonding technique, and the DAQ are well within reach with the actual status-of-the-art in this field.

• Also the mechanics and the cooling system, though complex, do not necessitate outstanding effort.

• To summarize: the design of the front-end to beat the jitter and the time walk (which are the main sources of errors) and to get to the specified time resolution is the crucial point.

# **Front-end: introduction**

- We are following two design options to cure the time walk:

- Constant Fraction Discriminator, which recovers hardware-wise the time walk of the signal due to the energy deposit fluctuations

- 2. Determination of the Time-over-Threshold of the signal and offline correction of the time walk.

Concerning the architecture two configurations are under study:

- a) All the electronics dedicated to a pixel (preampli-CFD-TDC) is on the pixel itself. The technology that has been chosen (130 nm) allows to comfortably fit all the components into the (300x300)  $\mu$ m pixel area.

- b) Preampli and Time-over-Threshold discriminator is on every pixel and TDC is at the end-of-column and serves 5 pixels.

For each option, in 2007, a prototype has been developed and tested on the bench.

Results have been shown in previous meetings and reports and they resulted to be promising:

$\sigma$  < 100 ps (rms)

# More information about the front-end design status

Option a): on-pixel-TDC option: preampli->CFD->TDC within the pixel area (Torino)

Option b): end-of-column TDC: preampli -> ToT discriminator -> TDC serving 5 pixels placed at the end-of-column.(CERN)

Remark: nothing would prevent to mix the two options, for example CFD with the end-of-column TDC.

- To insist on more than two options seemed not easy to be sustained.

- This possibility, mix of the two options, will be exploited only if the tests will show it is necessary.

#### Some more info about the On-pixel-TDC option

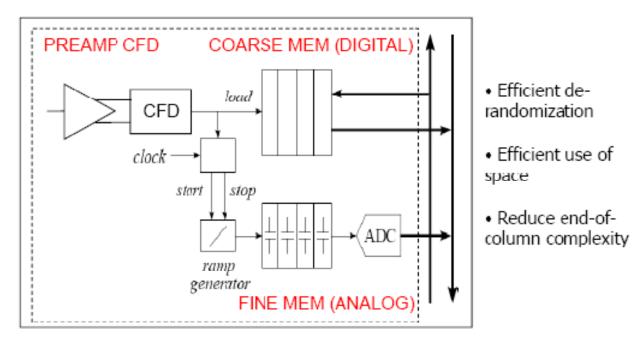

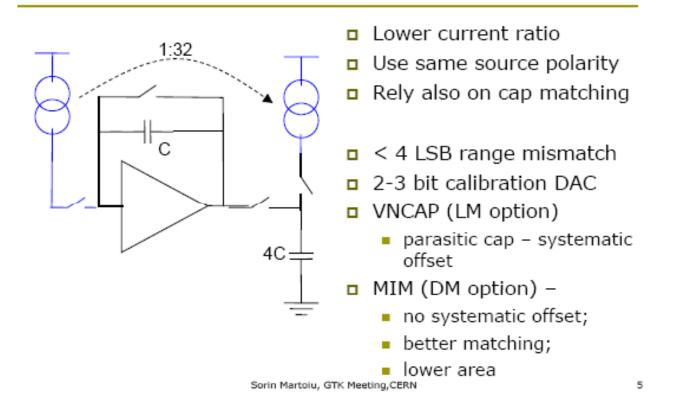

# CFD-FE Overview

Sorin Martoiu, GTK Meeting, CERN

2

#### Some more info about the On-pixel-TDC option (cont'd)

# Wilkinson TDC variant

- The baseline design of the full chain is frozen

- Layout is underway

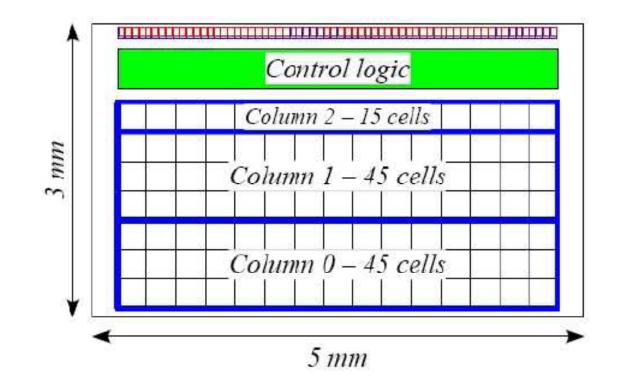

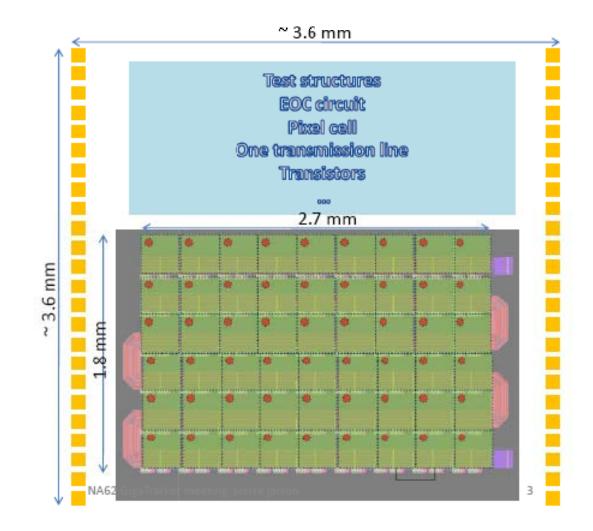

**On-pixel-TDC architecture: chip layout**

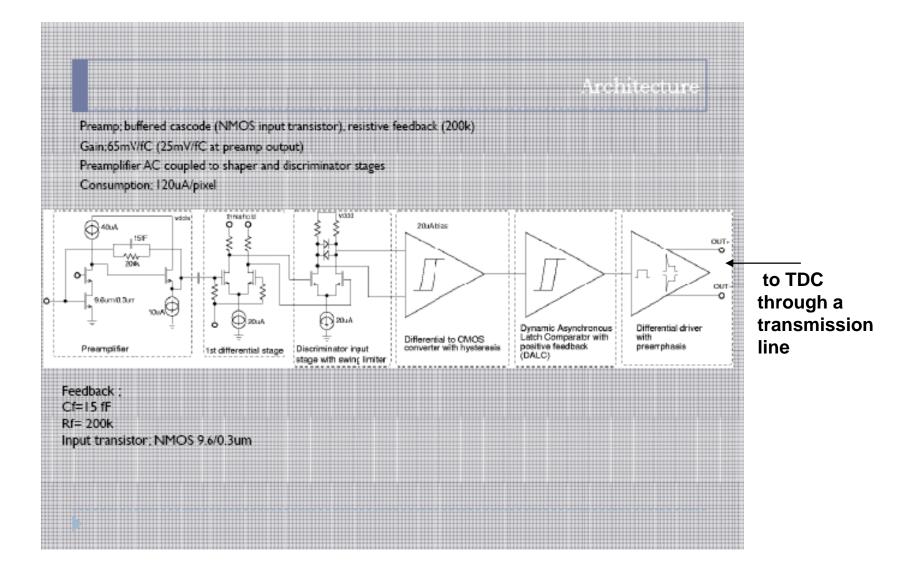

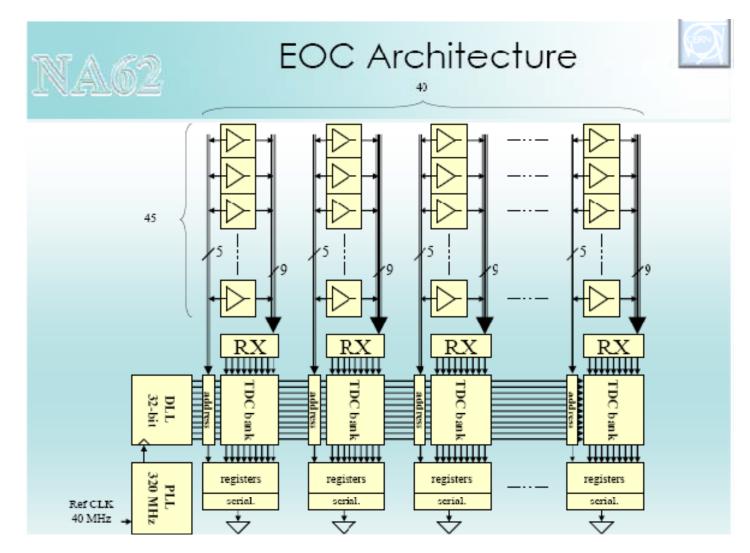

#### Some more info about the End-of-column-TDC option

14

#### Some more info about the End-of-column-TDC option (cont'd)

#### **EOC** architecture: chip layout

# Status of the chip prototypes

- Two options:

- ➢ on-pixel-TDC

- >End-of-Column TDC (EOC)

Design review on Oct. 7-8th with several CERN-LAL designers

- all the building blocks are ready

- no flaws have been spotted

- some further checks to be performed

- layout underway for both options

- submission moved to Jan. 20th 2009, delivery expected by middle of March 2009.

#### **Tests on prototypes in Spring-Summer 2009**

• before bump-bonding: electrical test and measurements of the jitter+time-walk with charge injection method

• after bump-bonding: test with source/laser and beam.

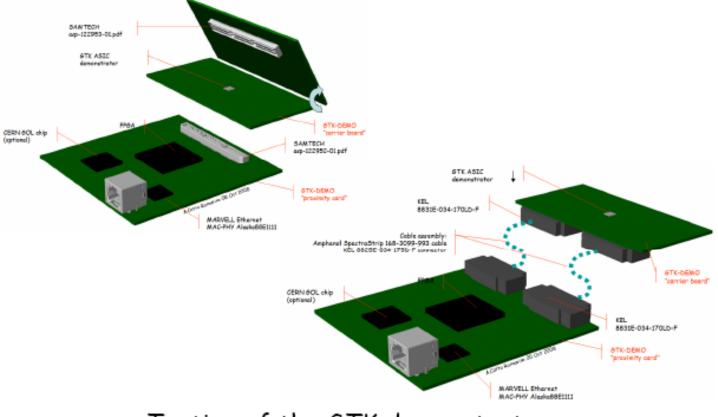

## **Progress report: DAQ for chip prototype**

Testing of the GTK demonstrators