# TID effects in 65nm transistors: summary of a long irradiation study at the CERN X-rays facility

F.Faccio<sup>1</sup>, S.Michelis<sup>1</sup>, D.Cornale<sup>1,2</sup>, A.Paccagnella<sup>2</sup>, S.Gerardin<sup>2</sup> <sup>1</sup>CERN - PH/ESE <sup>2</sup>DEI, Padova University

# LEB Workshop 1998

# LEB Workshop 1998

# TWEPP Workshop 2014-15

Very complex phenomenology Long time to run each experiment Non-ideal test structures Need to make a synthesis

> Approximate Incomplete Hopefully correct

# This is a summary of the results in graphical form (qualitative)

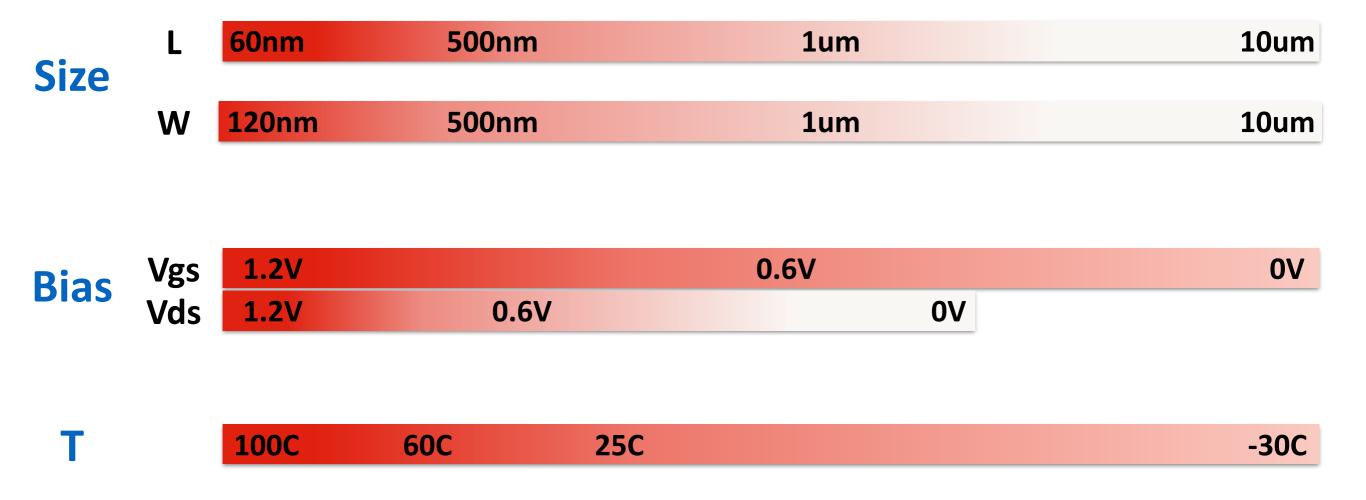

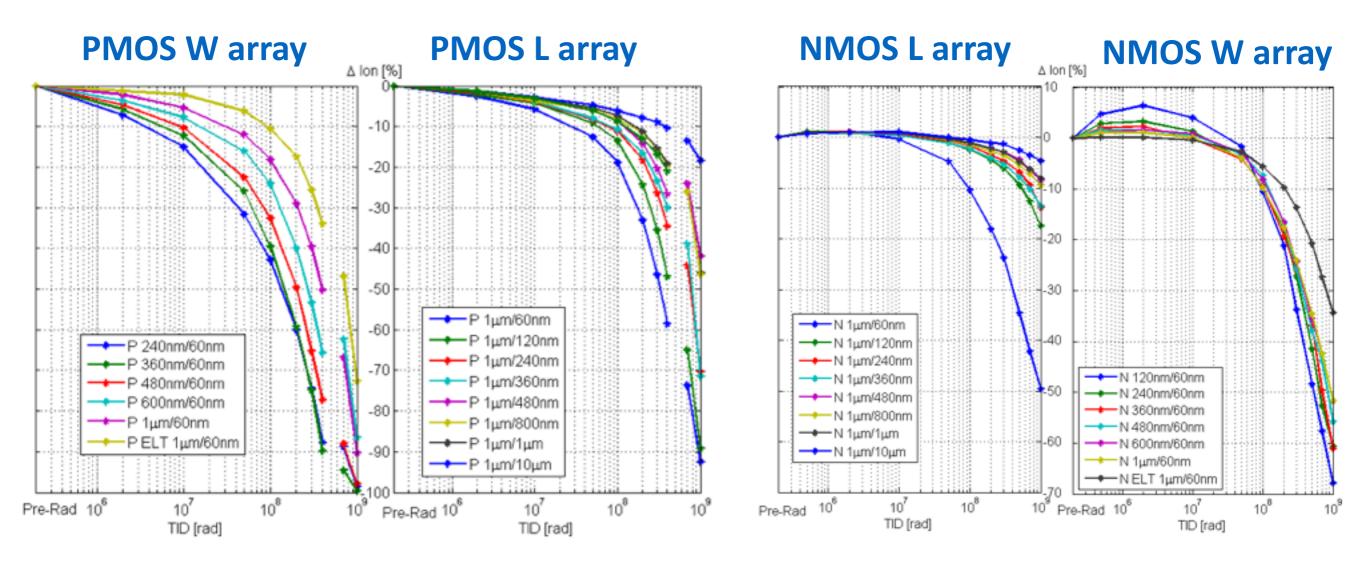

Transistor size matters!!!

Bias and Temperature strongly influence the results, in a way that is difficult to explain on the basis of our previous experience

What was measured?

#### TID-induced degradation of the electrical performance (Ion)

**Results from Negative Bias Thermal Instability stresses (combined with TID)**

**Results from Hot Carrier Injection stresses (combined with TID)**

Variability of the TID-induced degradation

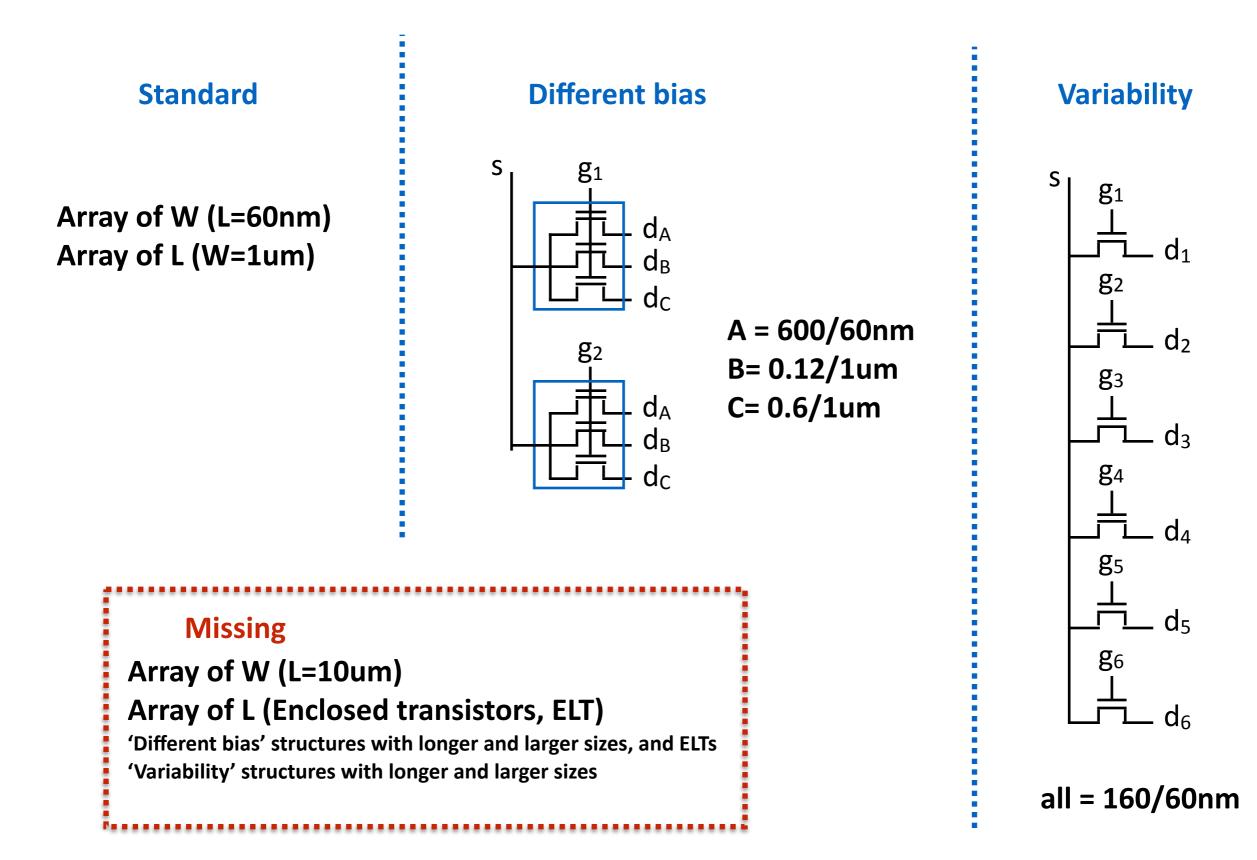

# WHAT Transistors - Only CORE (no I/O)

## HOW

DC bias during irradiation and annealing Regulated T during irradiation and annealing We learnt that the test structures, even with those most recently added, are not sufficient for our purposes

The main parameters extracted from the measurements are:

- Drive current (I<sub>on</sub>)

- Threshold voltage (V<sub>th</sub>)

- Transconductance (G<sub>m</sub>)

- Subthreshold swing (SubS)

- Leakage current

What was measured?

#### **TID-induced degradation of the electrical performance (Ion)**

**Results from Negative Bias Thermal Instability stresses (combined with TID)**

**Results from Hot Carrier Injection stresses (combined with TID)**

Variability of the TID-induced degradation

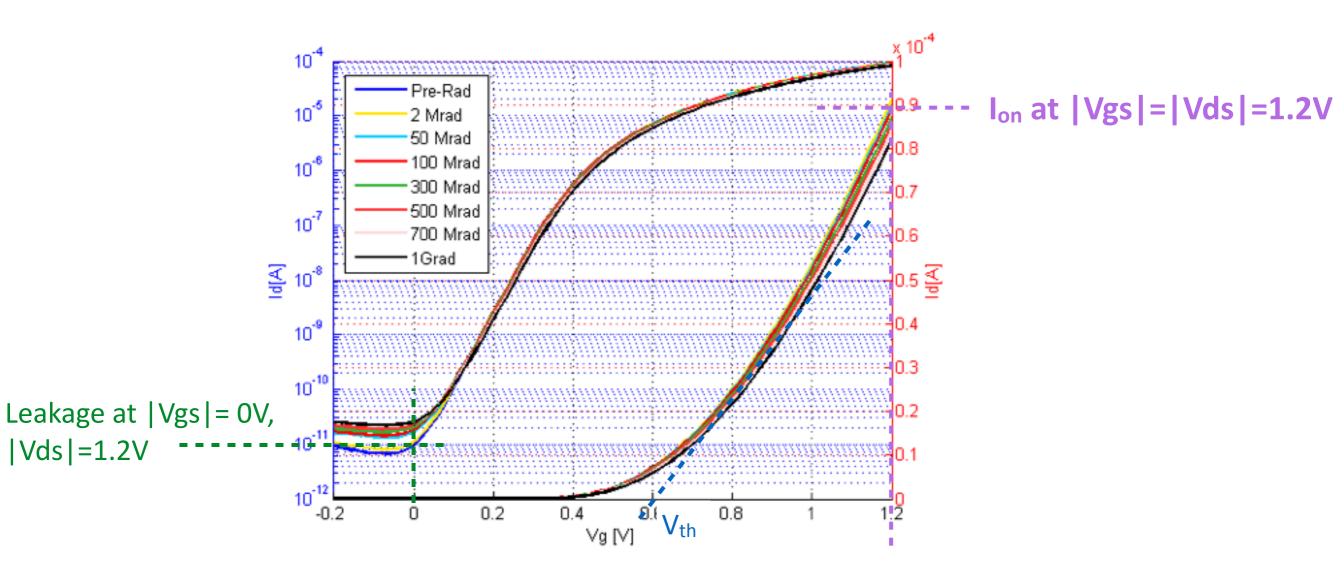

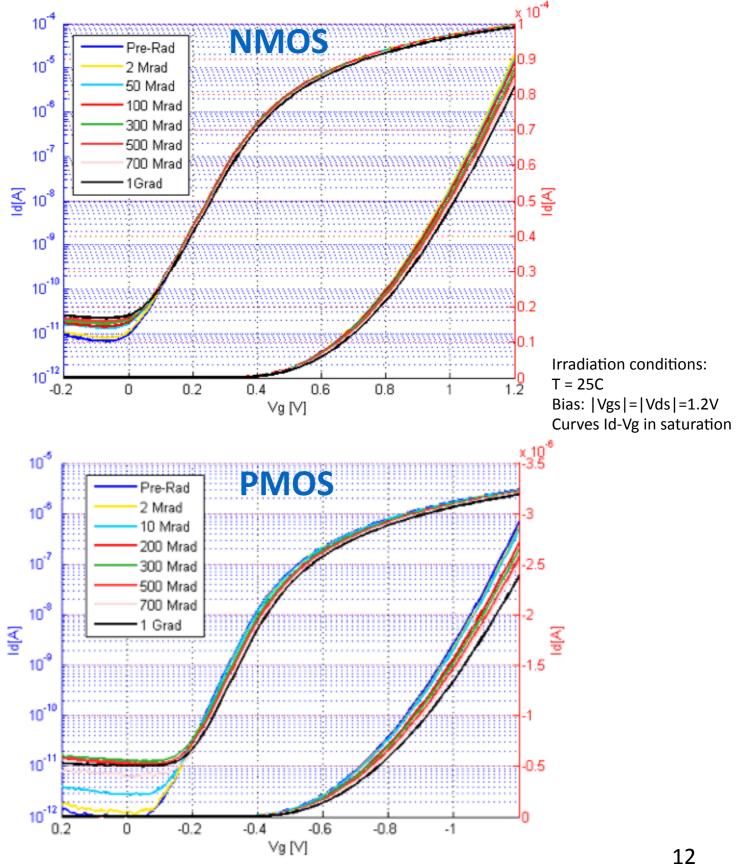

There will be no further comment about leakage currents, because we did not measure significant currents (for typical applications) in either NMOS transistors or FOXFETs

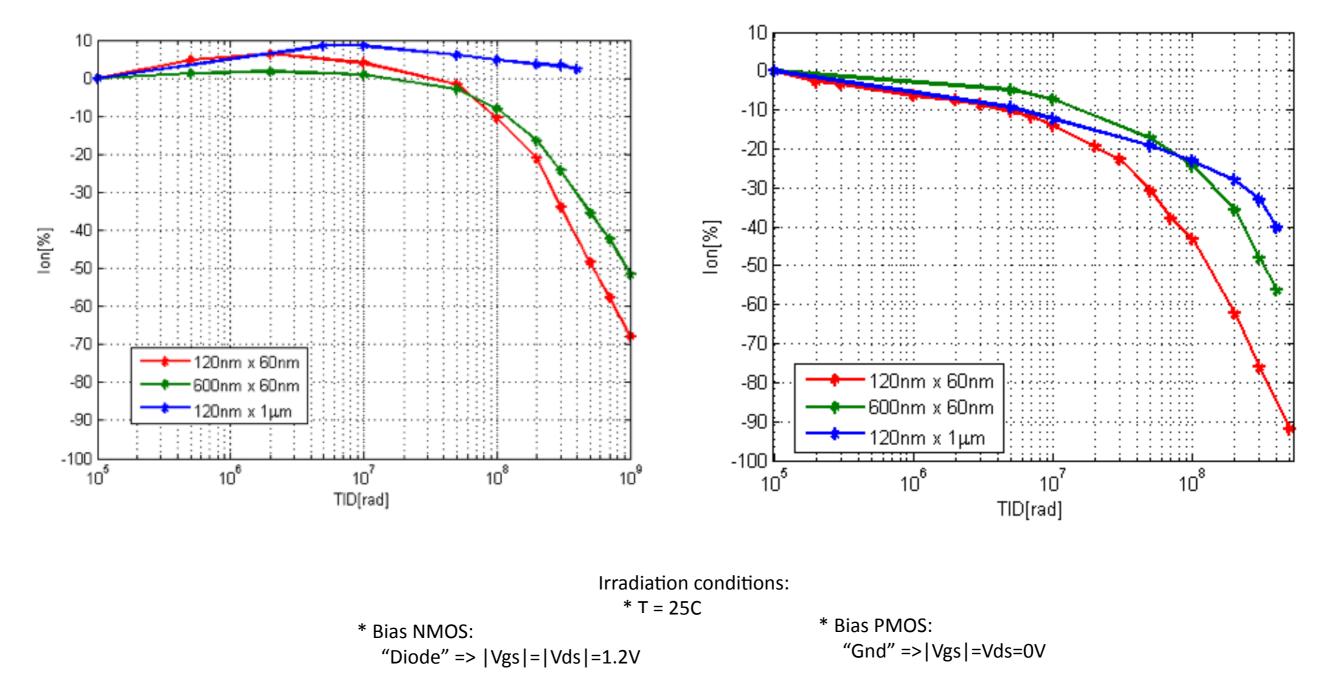

### The degradation of long and large transistors is limited: the thin gate oxide is radiation hard!

Radiation damage is severe in short and narrow channel transistors, where it depends on the <u>bias</u> and <u>temperature</u> applied both during and after irradiation

### Radiation-Induced Narrow Channel Effect (RINCE) Radiation-Induced Short Channel Effect (RISCE)

T = 25C Bias: |Vgs|=|Vds|=1.2V

### Let's try to tidy up a little.....

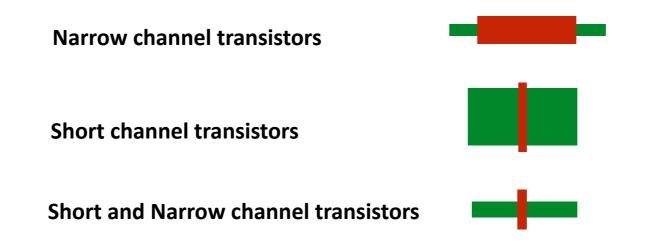

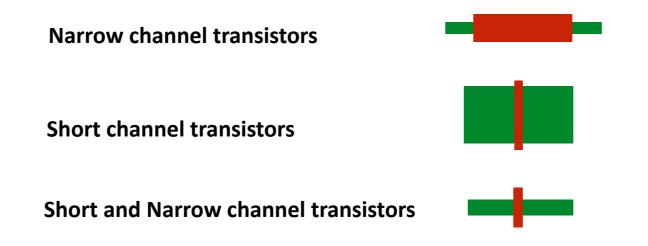

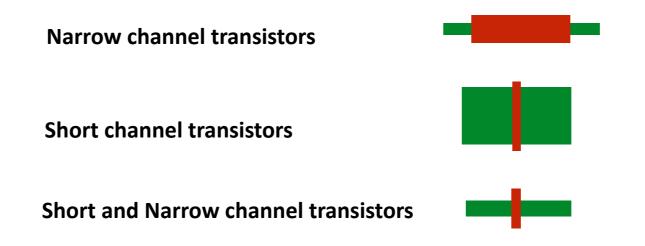

# **Narrow channel transistors**

**Short channel transistors**

# Short and Narrow channel transistors

#### **Radiation Induced Narrow Channel Effect (RINCE)**

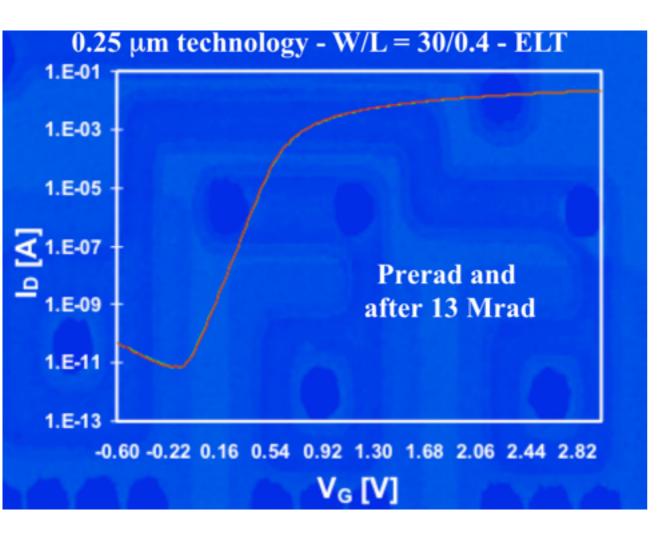

From poster presented at 2005 NSREC, Seattle

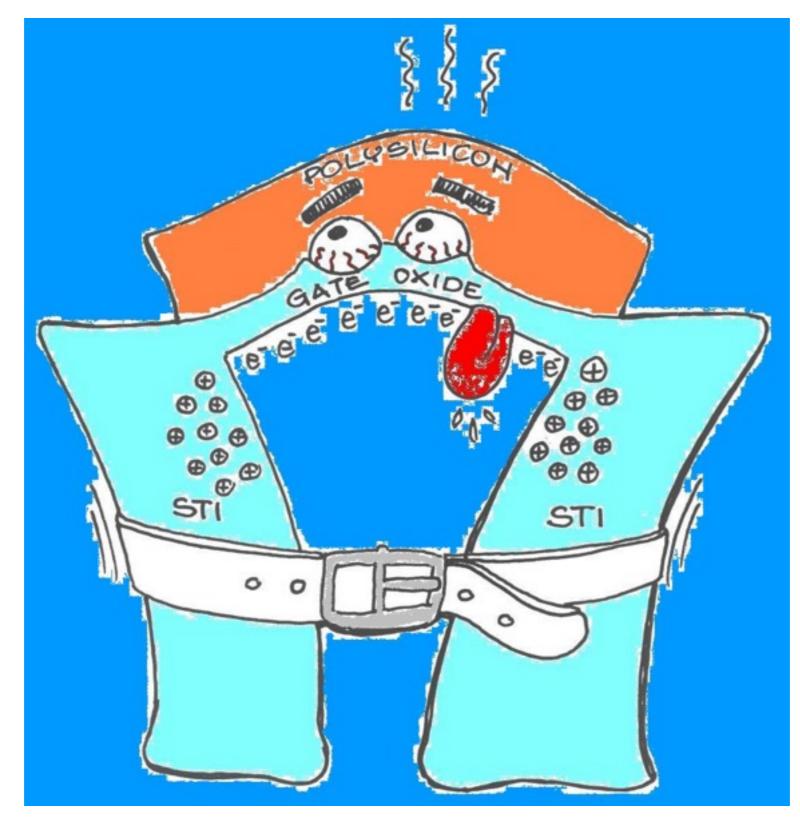

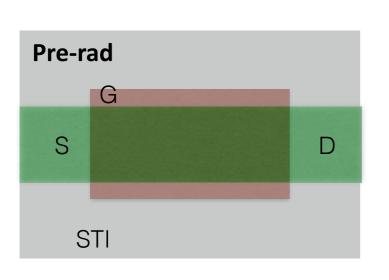

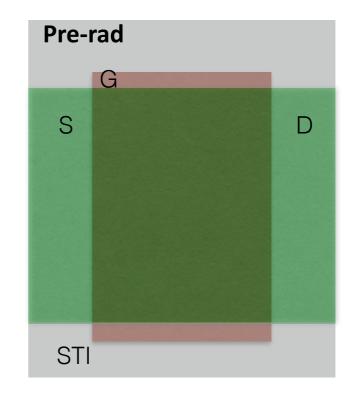

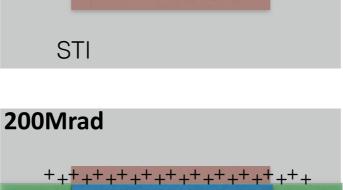

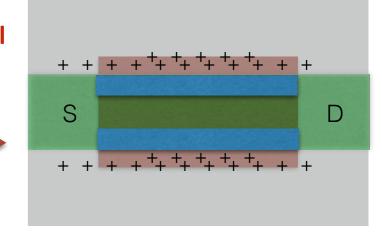

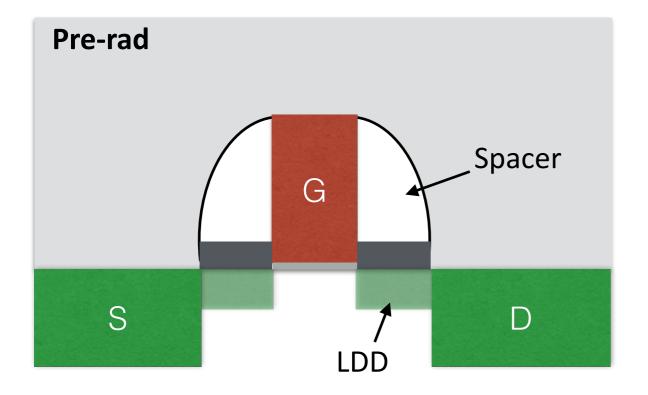

#### **RINCE** is traceable to radiation effects in the STI oxide

T=25C

The dynamics of the trapping of charges in the oxide or in interface traps determines the response of NMOS and PMOS - these are mechanisms that are relatively well known

#### **RINCE** can be conceptually represented by this cartoon

W=min size

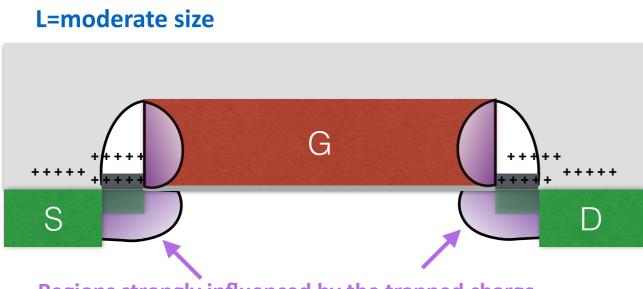

#### W=moderate size

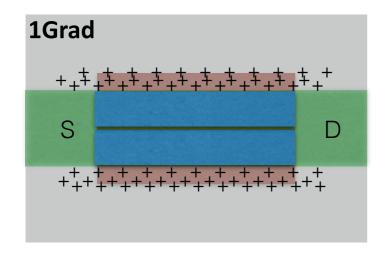

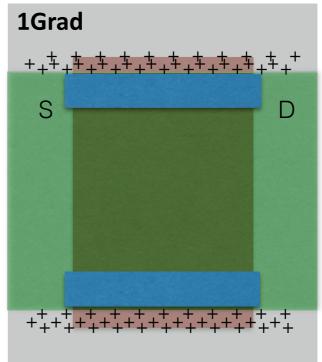

NOTE: In this cartoon, there is no distinction between the positive charge trapped in the oxide or in interface traps

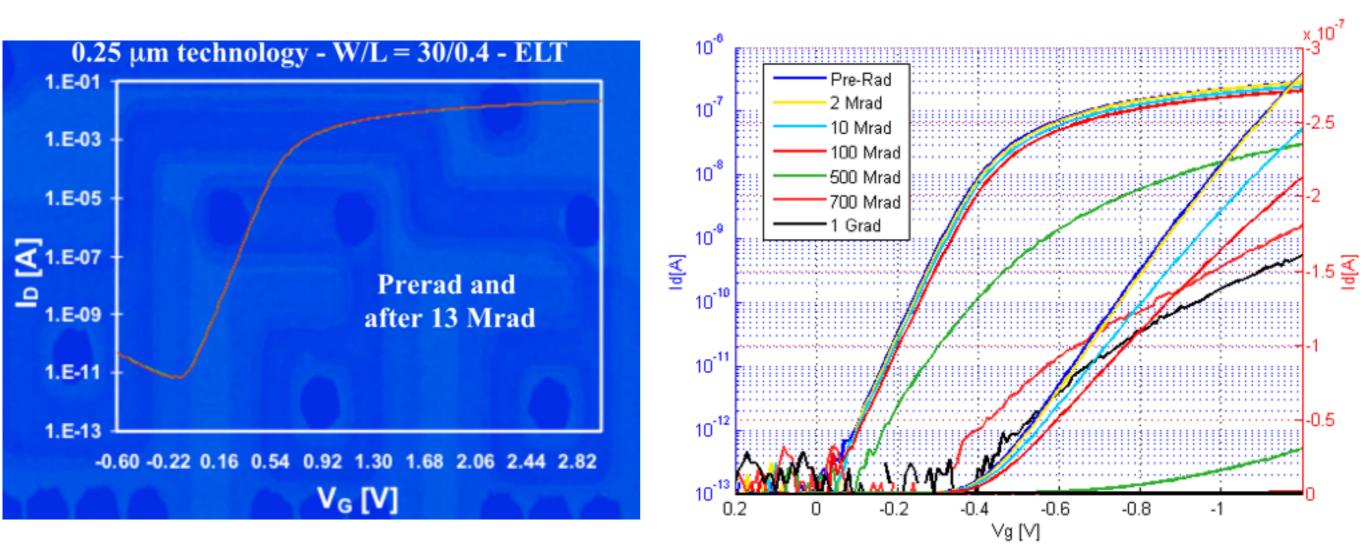

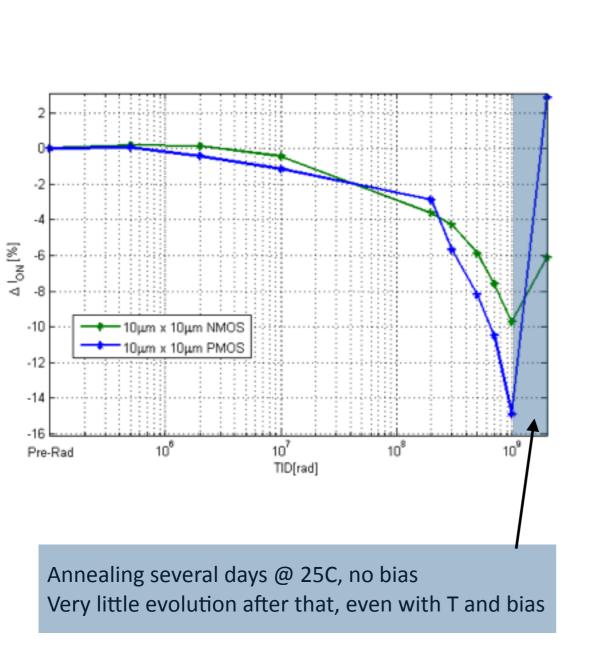

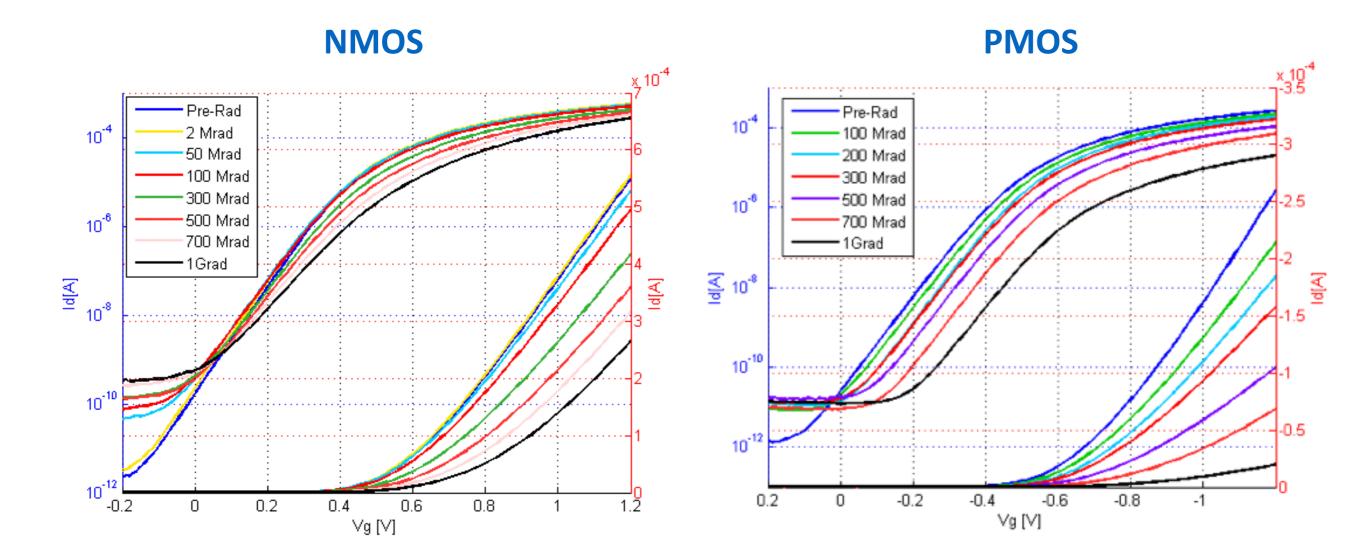

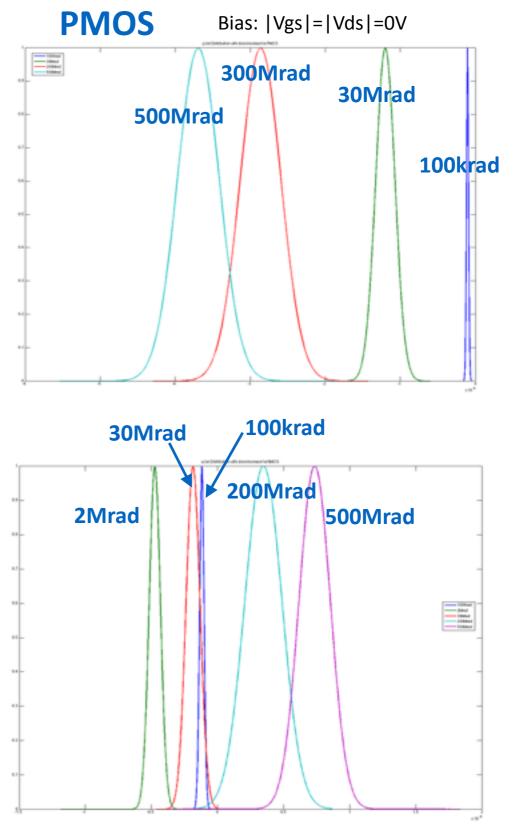

# Narrow channel PMOS transistors do not work above 500Mrad, while NMOS are working without large damage up to 1Grad

Since NMOS damage is always below 20%, it is not discussed in detail - only PMOS are discussed

**NMOS PMOS** 10-6 107 10-6 Pre-Rad Pre-Rad 107 2 Mrad 2 Mrad ≈10x 10.7 10 Mrad 10 Mrad 100 Mrad 100 Mrad 10<sup>-8</sup> ≈100x 10<sup>-8</sup> 500 Mrad 500 Mrad 700 Mrad 700 Mrad 1 Grad 10<sup>-9</sup> 10'9 1 Grad [V] [A] [A] .5 🚽 10<sup>-10</sup> 10<sup>-10</sup> ) 10<sup>-1</sup> 10<sup>-11</sup> 10<sup>-12</sup> -0.5 10<sup>-12</sup> 10.1 0.6 -0.2 0.2 0.4 0.8 ∨g [∨] 101 -0.6 -0.8 -0.4 -0.202 Π -1 ∨g [∨] Very small leakage!

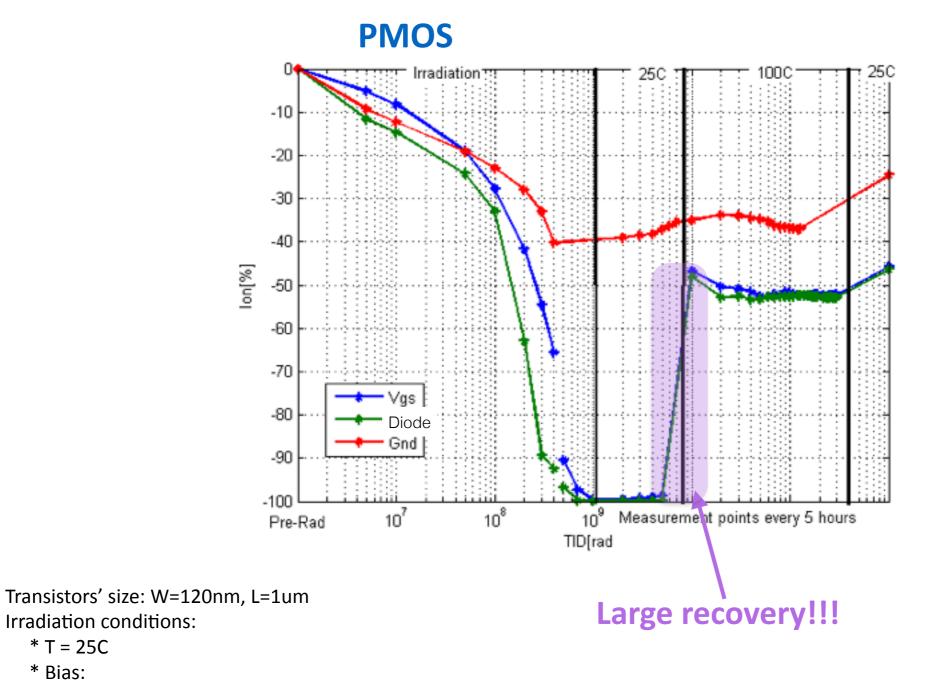

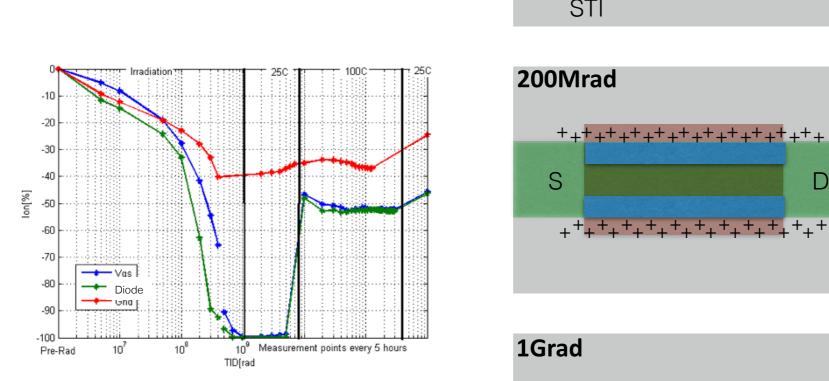

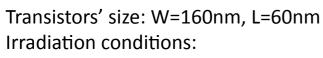

Transistors' size: W=120nm, L=1um Irradiation conditions: T = 25C Bias: |Vgs|=|Vds|=1.2V

#### **Influence of BIAS**

#### For PMOS, there is a strong bias dependence

The damage is larger when a  $V_{gs}$  is applied, in agreement with common sense. However, it is more difficult to explain why the application of a large  $v_{ds}$  enhances the damage.

\* Bias:

\* T = 25C

```

"Vgs" => |Vgs|= 1.2V, Vds=0V

"Diode" => |Vgs|=|Vds|=1.2V

"Gnd" =>|Vgs|=Vds=0V

```

D

D

**Pre-rad**

S

G

NOTE: In this cartoon, there is no distinction between the positive charge trapped in the oxide or in interface traps; it all appears as positive charge

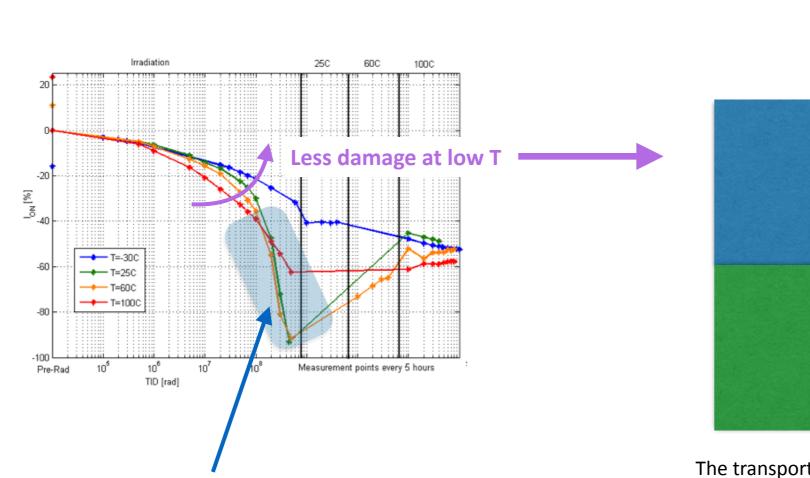

#### **Influence of TEMPERATURE**

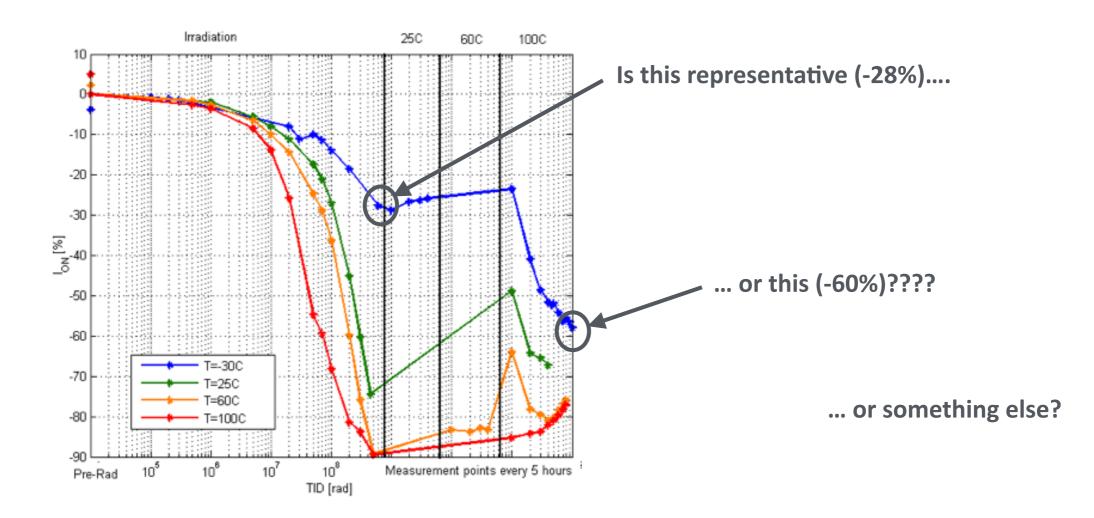

**RINCE:** Radiation damage in PMOS considerably changes with temperature.

At -30C the bias dependence also disappears.

#### Irradiation 25C 60C 100C 20 -20 [%] <sup>NO</sup>I -40 T=-30C -60 =25C T=60C T=100C -80 -100 10<sup>6</sup> 105 107 108 Measurement points every 5 hours Pre-Rad TID [rad] Transistors' size: W=120nm, L=1um Large recovery!!!

#### **PMOS**

Irradiation conditions: \* Bias:

"Diode" => |Vgs|=|Vds|=1.2V

#### Influence of TEMPERATURE

There are two mechanisms at play:

- smaller damage at low T

- larger annealing at high T

Significant annealing of the damage happens already during irradiation at high T

The transport of positive species towards interface is less efficient at low T (and high dose rate)

# Narrow channel transistors

**Short channel transistors**

# Short and Narrow channel transistors

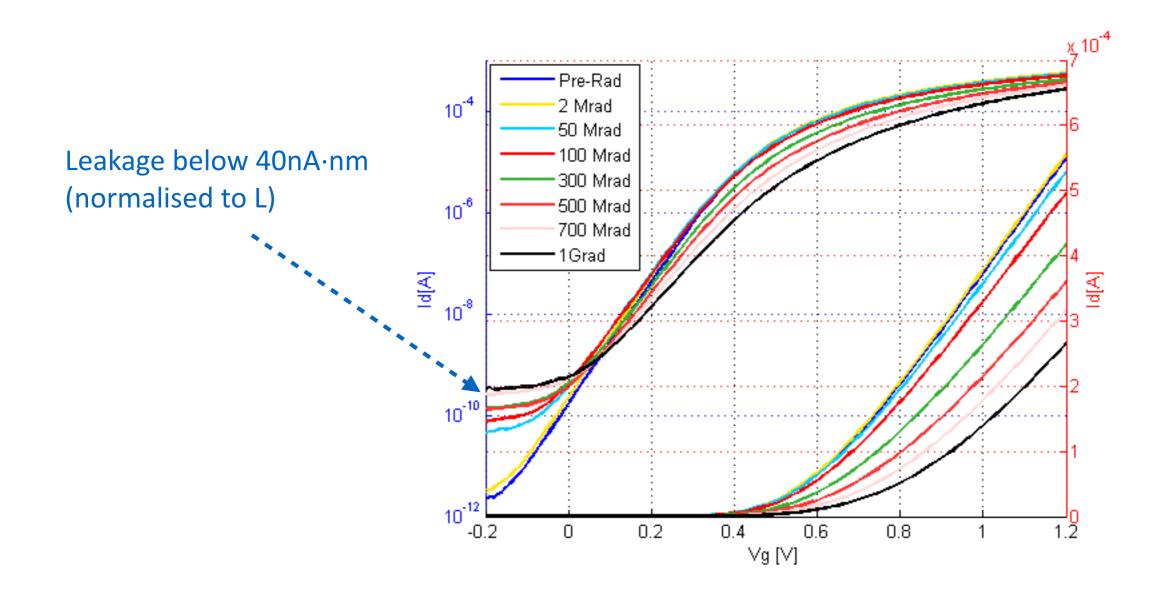

# Short channel PMOS are more damaged than NMOS

Damage occurs also in ELT transistors, hence it can not be due to the STI oxide

Transistors' size: W=1um, L=60nm Irradiation conditions: T = 25C Bias: |Vgs|=|Vds|=1.2V

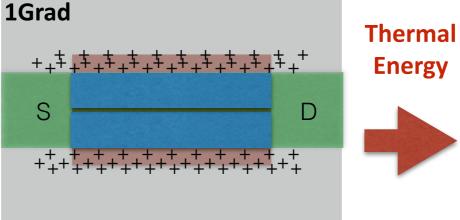

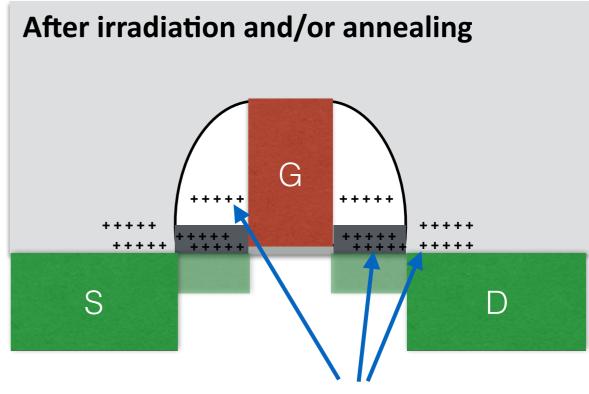

#### **RISCE can be conceptually represented by this cartoon**

Which defect? Which charge trapped? Where?

**Regions strongly influenced by the trapped charge**

#### L=min size

#### **Influence of BIAS**

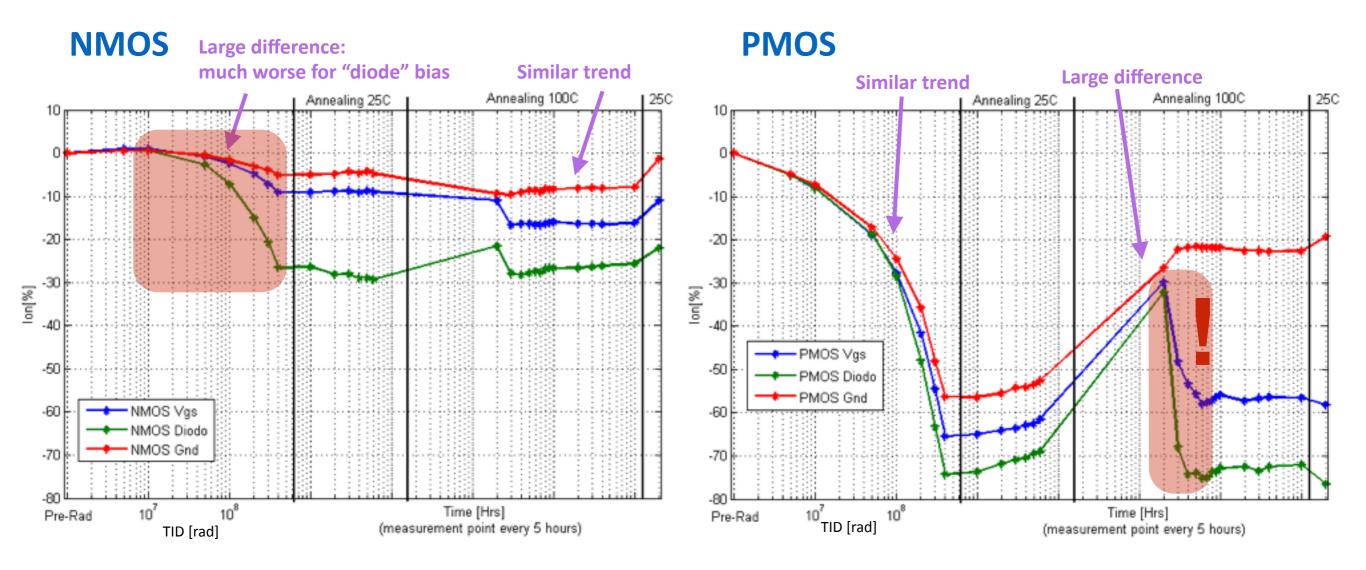

For NMOS, RISCE is very dependent on the bias applied during irradiation For PMOS, the bias dependence happens rather during high-T annealing (here the irradiation T is 25C)

```

Transistors' size: W=0.6um, L=60nm

```

Irradiation conditions:

\* T = 25C

\* Bias:

```

"Vgs" => |Vgs|= 1.2V, Vds=0V

"Diode" => |Vgs|=|Vds|=1.2V

"Gnd" => |Vgs|=Vds=0V

```

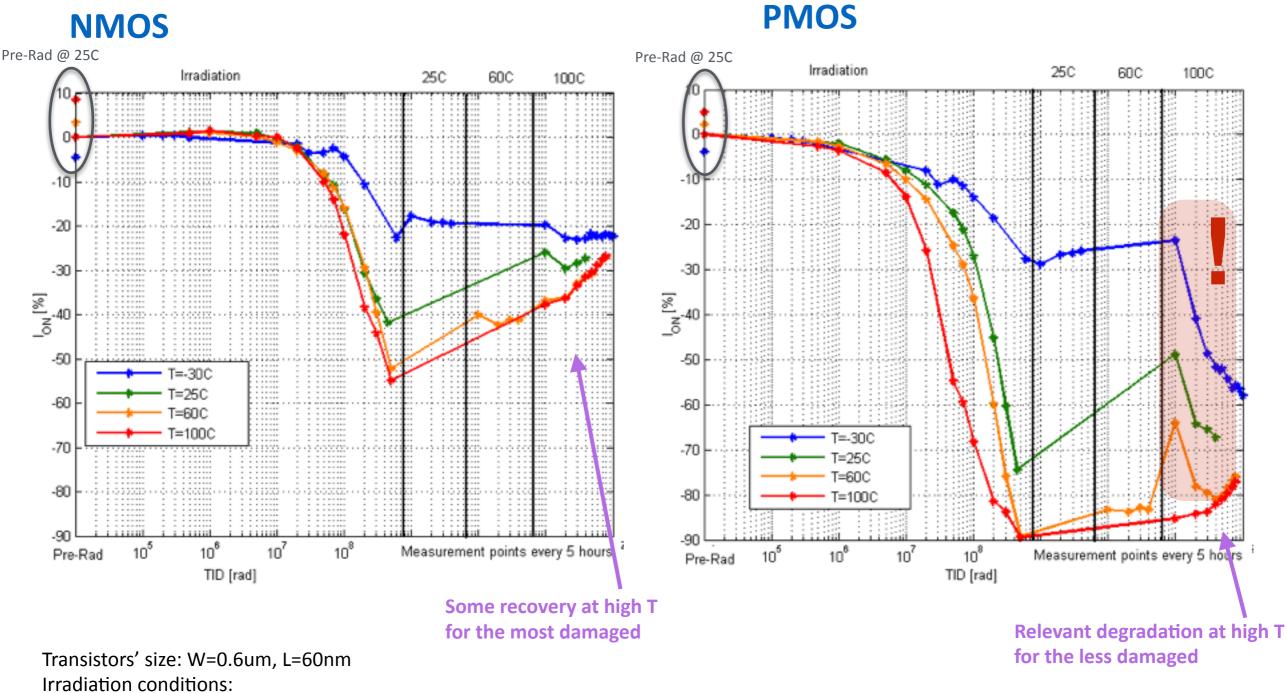

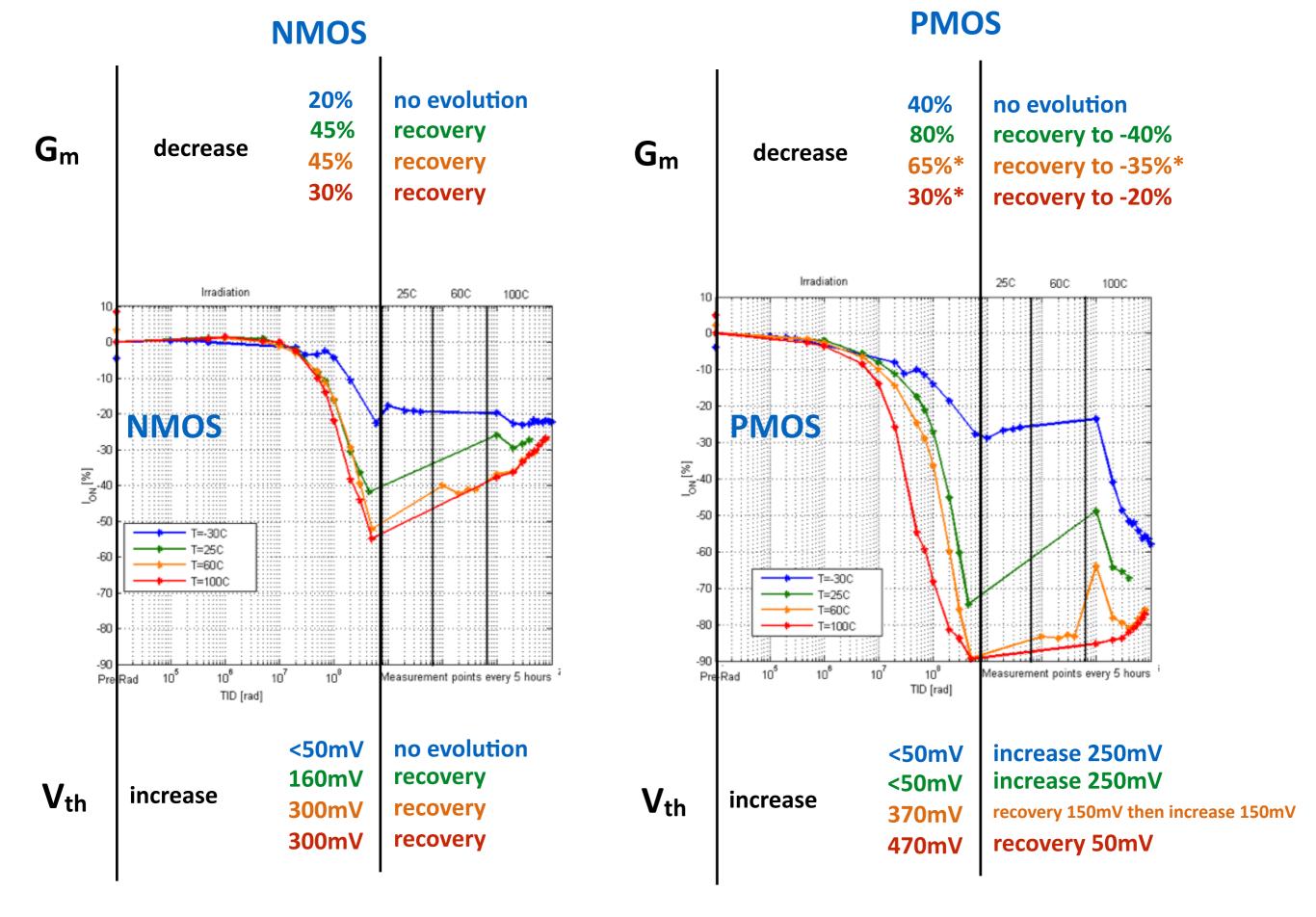

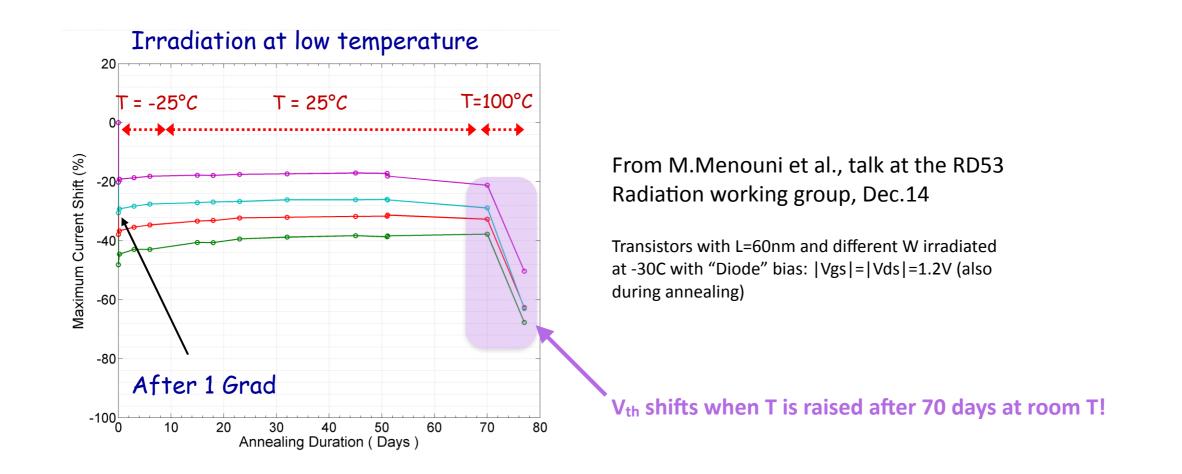

#### Influence of TEMPERATURE

### **RISCE:** Radiation damage increases with temperature

Transistors are much more tolerant at -30C (and their bias dependence decreases as well) PMOS have to be kept cold also after exposure!

Bias: |Vgs|=|Vds|=1.2V

\* = Rough estimate (the peak G<sub>m</sub> is out of the V<sub>gs</sub> range due to V<sub>th</sub> shift)

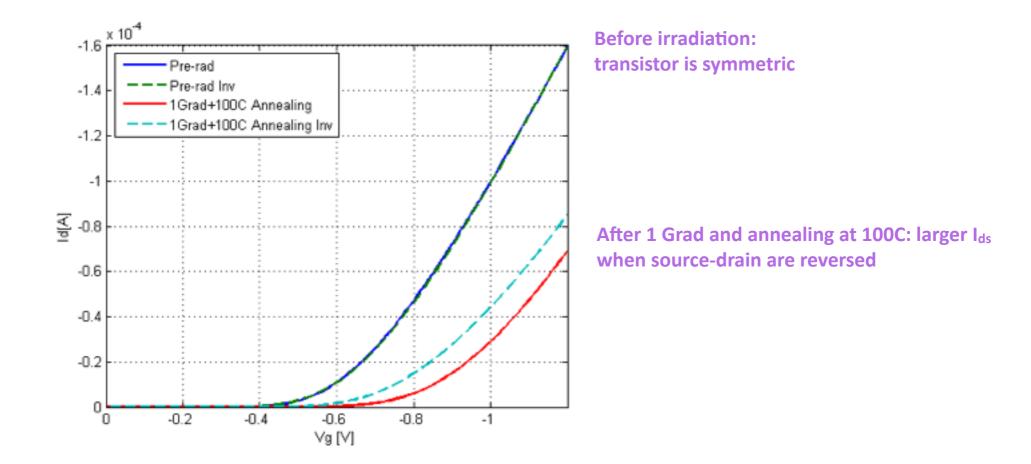

#### In PMOS transistors the shift of V<sub>th</sub> is accompanied by a source-drain asymmetry The damage appears to be larger at the source side

Transistors' size: W=1um, L=60nm Irradiation conditions: T=25C Bias: |Vgs|=|Vds|=1.2V

#### In NMOS transistors measurements on symmetry are not consistent

No conclusion can be reached on possible radiation-induced asymmetry

#### The post-irradiation evolution (V<sub>th</sub> shift) is clearly a thermally activated process

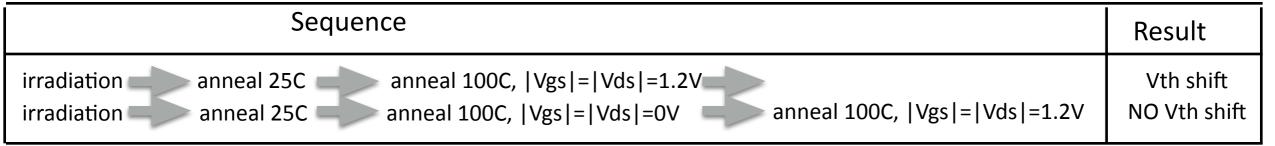

# Also, If no bias is applied in the first few hours when T is raised at 100°C then there is no V<sub>th</sub> shift when bias is applied

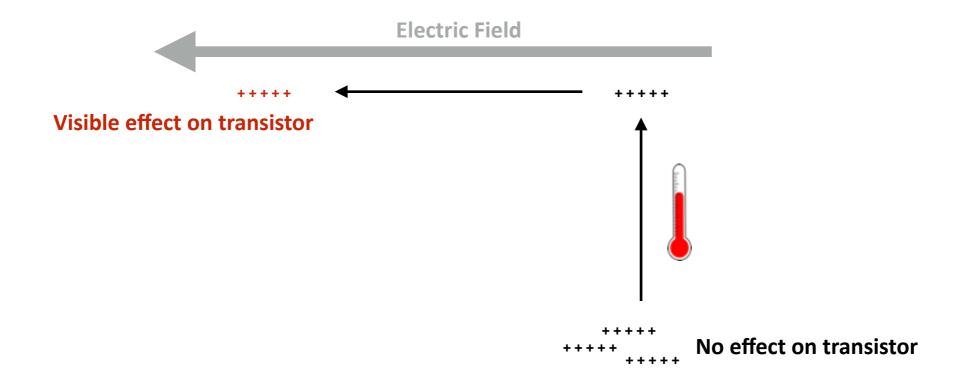

#### Thermal energy AND bias are needed at the same time for the damage to appear

... as if thermal energy allows the migration of charges, and bias drives them in the 'right' place for the damage to appear

#### Thermal energy AND bias are needed at the same time for the damage to appear

What is the activation energy, and can this still happen at low T over long times??? (damage at high dose rate and low T is much smaller: is this representative of the damage in the application?)

# Narrow channel transistors

# Short channel transistors

# **Short and Narrow channel transistors**

# Short AND Narrow transistors are simultaneously affected by RISCE and RINCE, hence their degradation is the worst measured

NMOS

What was measured?

#### TID-induced degradation of the electrical performance (Ion)

#### **Results from Negative Bias Thermal Instability stresses (combined with TID)**

**Results from Hot Carrier Injection stresses (combined with TID)**

Variability of the TID-induced degradation

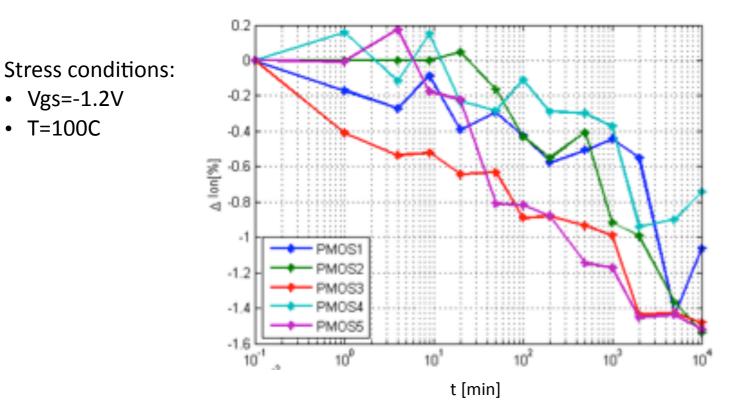

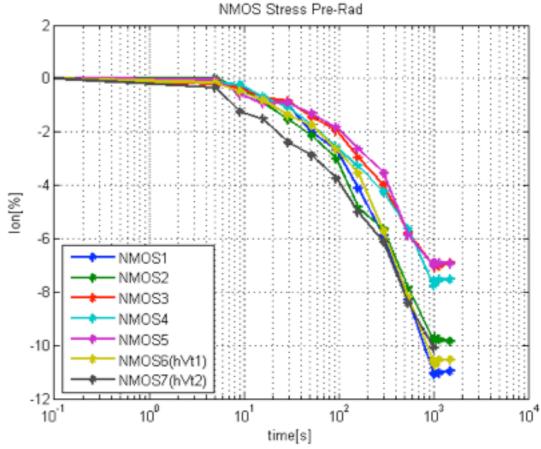

An NBTI stress is a procedure where negative gate voltage and high temperature are applied simultaneously for a long time on PMOS transistors, observing their performance degradation.

(There is a large and rapid evolution after the stress, complicating the experiment)

• T=100C

#### Fresh PMOS transistors (not irradiated), W=1um, L=60nm

Small degradation (≈1%) after 10,000 minutes of stress (measurements taken within 3 minutes after each stress)

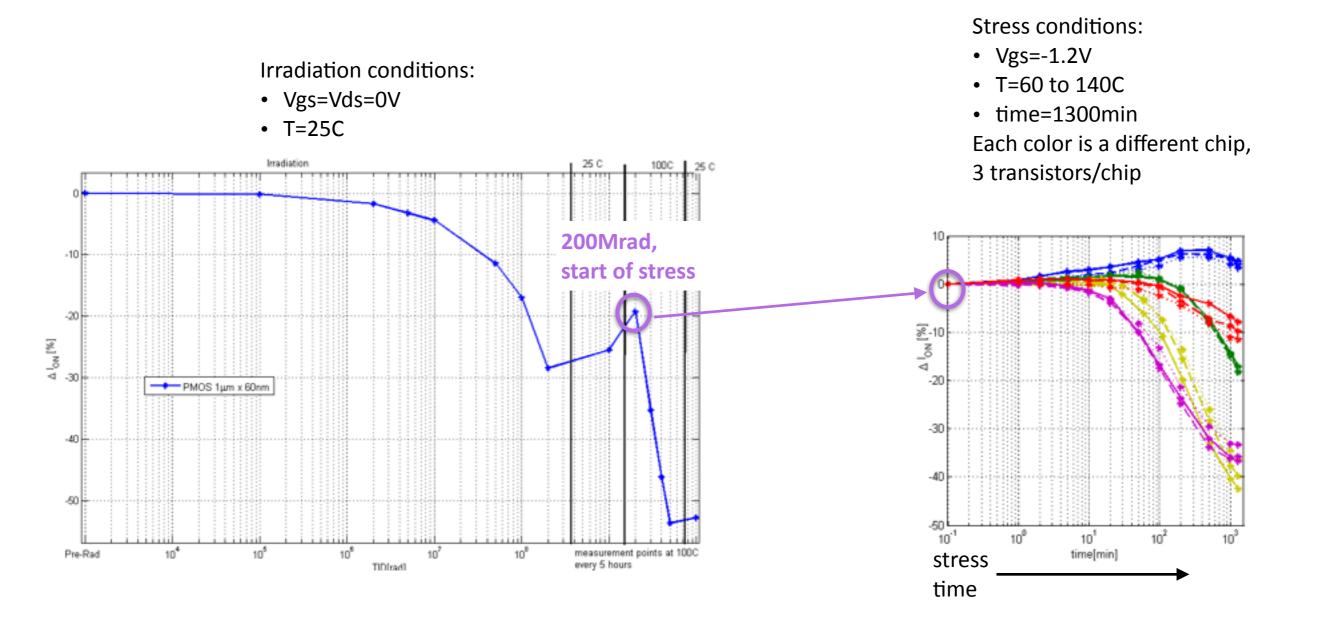

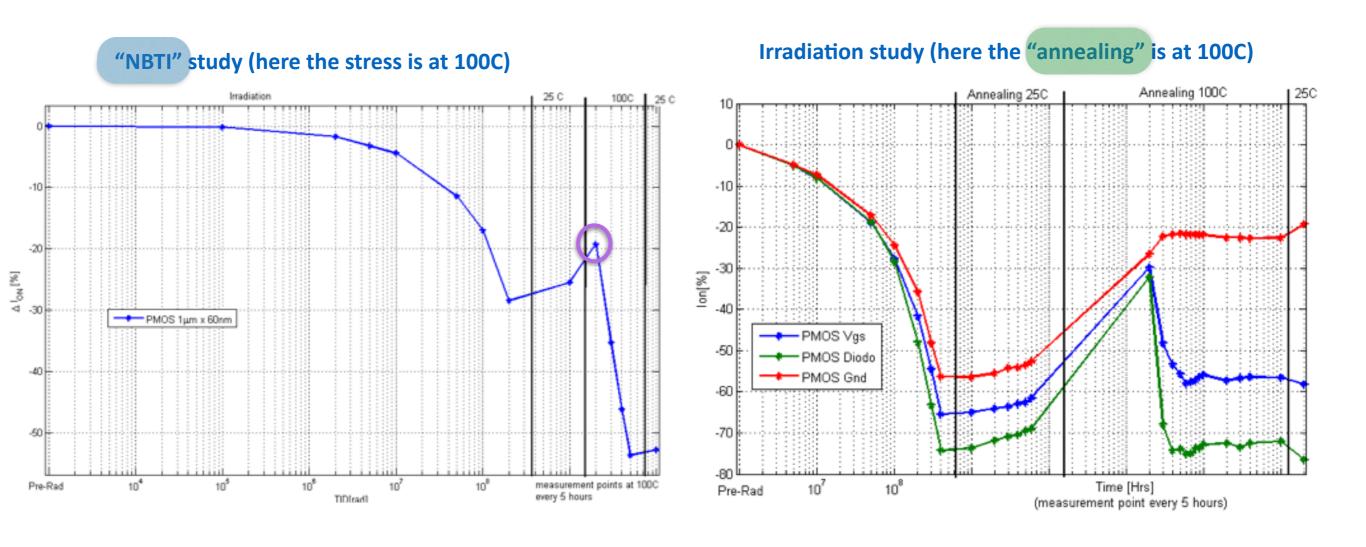

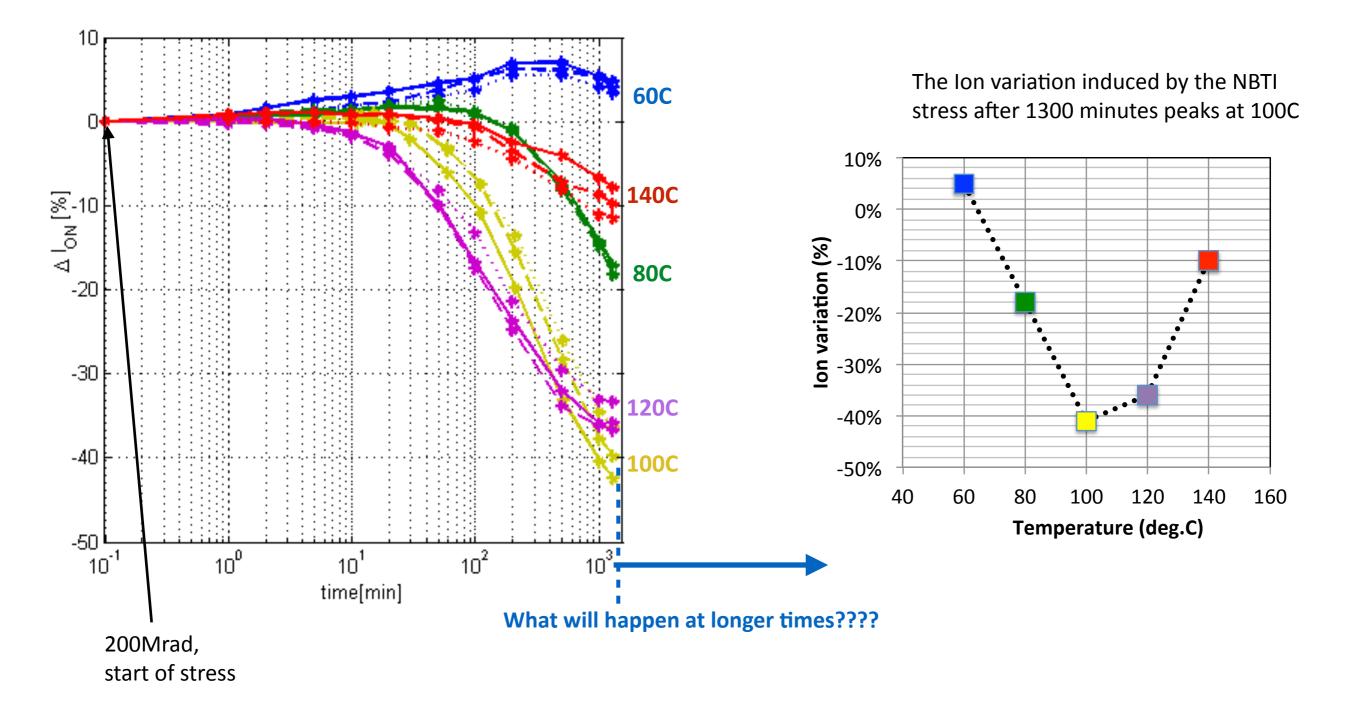

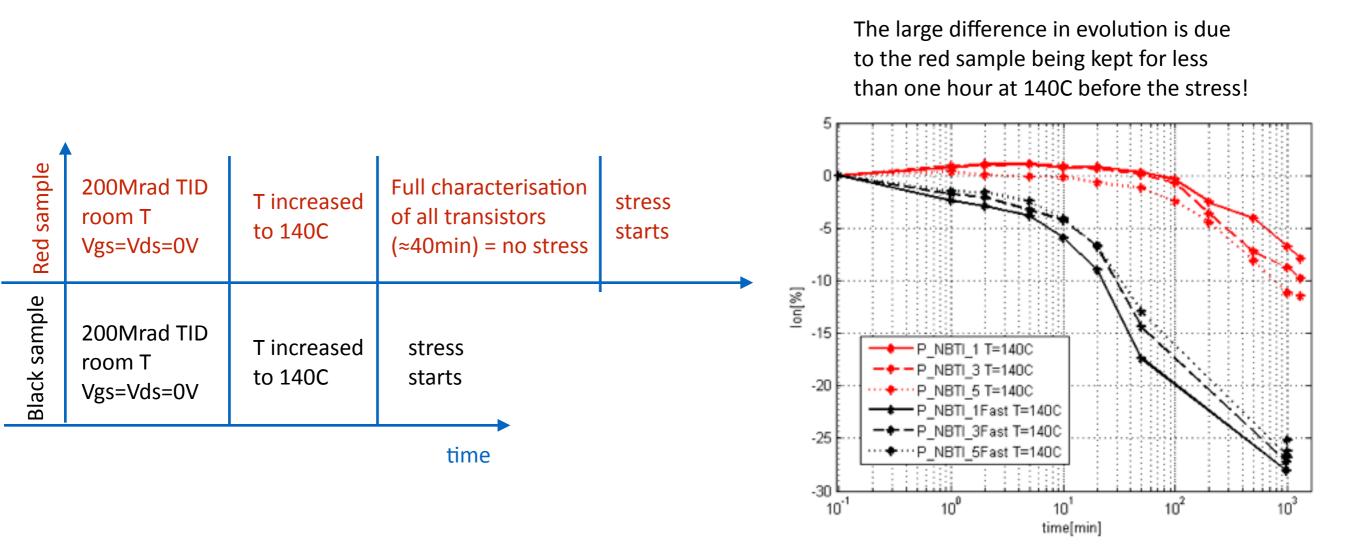

### NBTI stresses at different T have been applied to PMOS samples irradiated to 200Mrad in the same conditions (size: W=1um, L=60nm) (There is a large and rapid evolution after the stress, complicating the experiment)

The objective of the test was the extraction of an "activation energy" for the post-irradiation evolution

# The procedure is the same used for all irradiated samples: irradiation, annealing at room T, annealing at hight T

(however now the annealing at room T is as short as possible while the high T annealing takes place at different temperatures for different samples - all other conditions being the same!)

What is normally "annealing" at 100C is now "NBTI" at different T

# The evolution of the degradation is not monotonic. We can not extract an activation energy!

(More than one phenomenon is responsible for the evolution)

# The evolution of the degradation is strongly dependent on the detailed story of the sample

What was measured?

### TID-induced degradation of the electrical performance (Ion)

**Results from Negative Bias Thermal Instability stresses (combined with TID)**

**Results from Hot Carrier Injection stresses (combined with TID)**

Variability of the TID-induced degradation

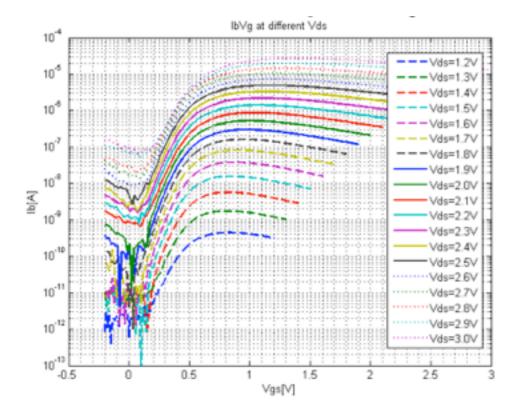

An HCI stress is a procedure where a pre-defined bias (normally well exceeding the nominal voltages of the technology) is applied to the transistor for a limited time, degrading its characteristics

1. Measurements to define the appropriate stress bias

### 2. Application of the stress and measurements of the transistor's degradation

Chosen conditions:

- NMOS: Vgs=1.1V, Vds=2.3V

- PMOS: different stress conditions used and compared: Vds=-2.6 to -3V, Vgs=-1.2 to -0.5V

# A set of measurements was performed to study the correlations between TID irradiation and Hot Carriers Injection damage

Irradiation was done at room T and with 'Vgs' bias: |Vgs|=1.2V, Vds=0V The size of the studied transistors is W=1um, L=60nm

| FirstHClThenIrradiationOnlyHClOnlyIrradiation | NMOS                                               | PMOS                                                                                                                                 |

|-----------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| First Irradiation Then HCI                    | Worse HCI damage<br>after irradiation<br>(a few %) | HCI after irradiation<br>leads to recovery<br>(radiation damage is so large<br>than anything seems to<br>contribute to the recovery) |

What was measured?

### TID-induced degradation of the electrical performance (Ion)

**Results from Negative Bias Thermal Instability stresses (combined with TID)**

**Results from Hot Carrier Injection stresses (combined with TID)**

Variability of the TID-induced degradation

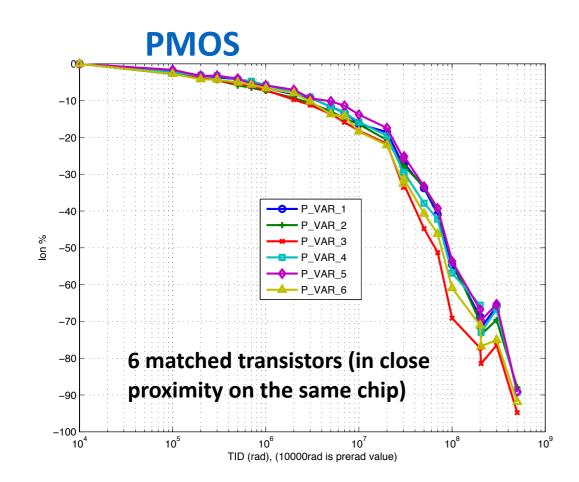

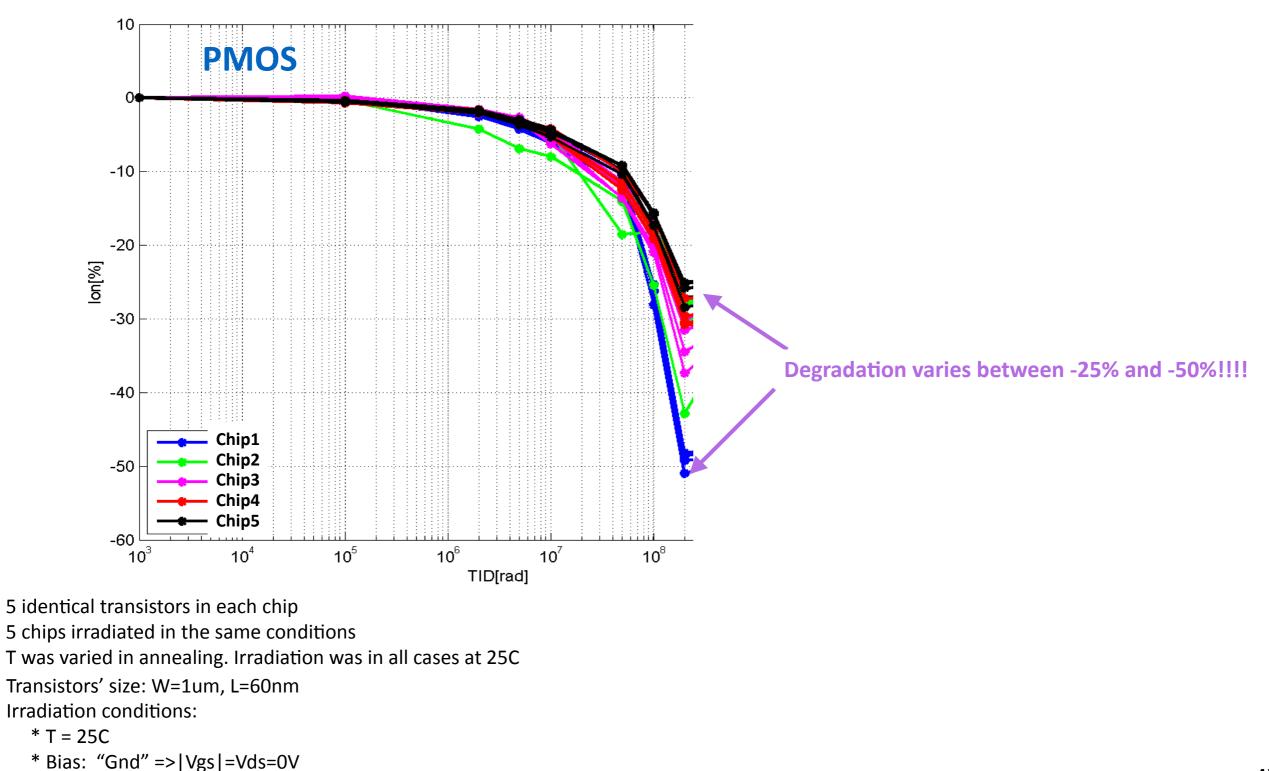

### The variability of 'matched' transistors increases with TID

T = 25C

Bias: |Vgs|=1.2V, |Vds|=0V

46

## The variability between identical transistors irradiated in the same condition on different chips is quite large!

### **Short Wrap-up**

NMOS: RISCE dominates, avoiding minimum L transistors guarantees limited damage (for minimum L transistors, damage can also be limited depending on the applied bias)

PMOS: both RISCE and RINCE contribute to a strong degradation. It is very difficult to predict the net radiation effects in the application: bias and temperature influence the results in an interwoven way, and more than one mechanism is involved (different activation energies)

#### **Generalisation of the observed effects**

Comparison with 130nm from same manufacturer evidences that the effects are similar in the two nodes (although considerably less relevant in 130nm)

Comparison with another 65nm process at -30C (CPPM, Fermilab) reveals some similarities as well (comparison of the full range of effects would require irradiation and annealing at different T)

Some additional comments based on other published work in the radiation effects field

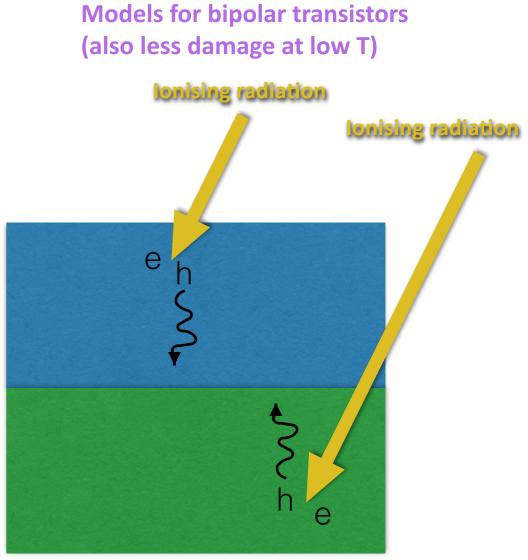

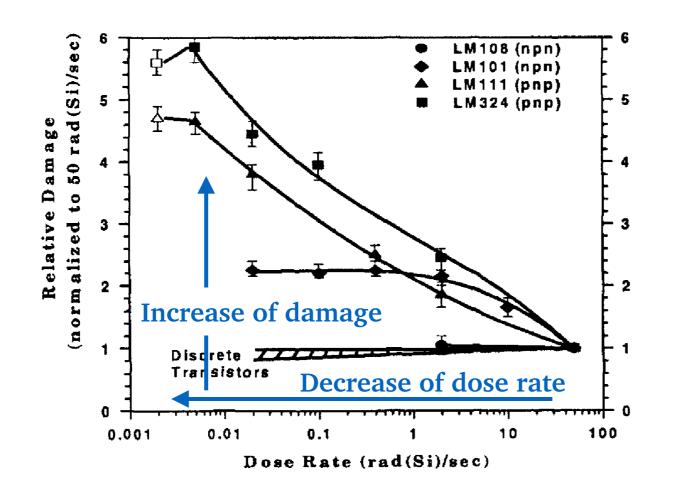

Enhanced Low Dose Rate Sensitivity (ELDRs): in a large number of bipolar technologies the TID-induced degradation increases at low dose rates

A.H.Johnston et al., IEEE Trans. Nucl. Science. Vol.41, N.6, 1994

Some of the reasons why this happens in bipolars only:

- the phenomena takes place in thick oxides of "poor quality"

- the electric field in the oxide is small

Damage increases with irradiation temperature! Qualification protocols for bipolar technologies foresee irradiation at high T to simulate the increased damage at low dose rates!

### **Bipolars:**

- the phenomena takes place in thick oxides of "poor quality"

- the electric field in the oxide is small

- damage increases with irradiation T

- annealing at 100°C for 3-5 hours after a HDR irradiation enhances the damage making it closer to LDR

### 65nm RISCE (RINCE to a smaller extent):

- the phenomena takes place in thick oxides of "poor quality" (STI, Spacers)

- the electric field in the oxide could be comparable, along fringing field lines, to the one in bipolar oxides

- damage increases with irradiation T

- annealing at 100°C for 3-5 hours after a HDR irradiation enhances the damage

Could the radiation damage observed in 65nm at a dose rate of 9Mrad/hour be "enhanced" at lower dose rates (ELDRS)??

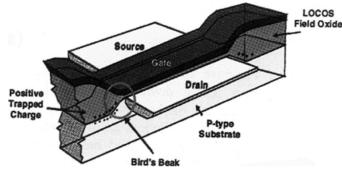

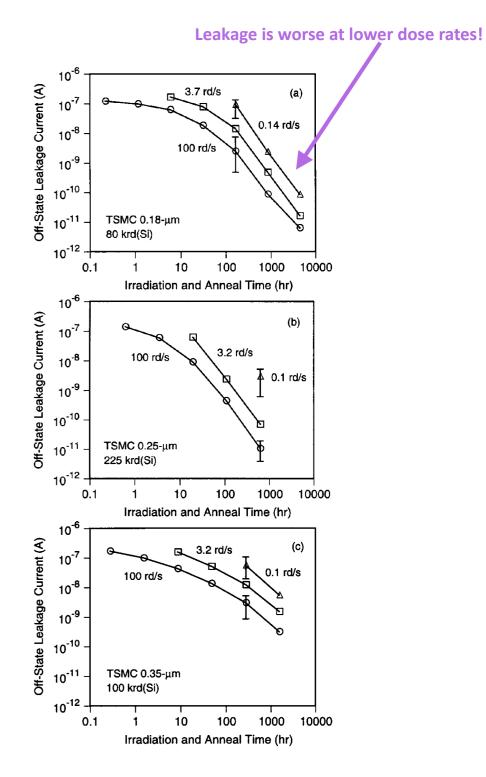

## Enhanced Low Dose Rate Sensitivity (ELDRs) has been observed in CMOS, for the source-drain leakage in NMOS

The work observed this feature on TSMC technologies (0.35, 0.25 and 0.18um)

2602

IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 52, NO. 6, DECEMBER 2005

#### Dose-Rate Sensitivity of Modern nMOSFETs

Steven C. Witczak, Member, IEEE, Ronald C. Lacoe, Member, IEEE, Jon V. Osborn, Member, IEEE, John M. Hutson, Student Member, IEEE, and Steven C. Moss, Senior Member, IEEE

Abstract—Radiation-induced edge-leakage current in minimum geometry n-channel MOSFETs from five submicron technologies is examined as a function of dose rate. Under worst-case bias, degradation of transistors from the TSMC 0.35-, 0.25-, and 0.18-µm processes is more severe following low-dose-rate irradiation than following high-dose-rate irradiation and anneal. The leakage current anneals with an activation energy of  $\sim 1.0$  eV. which suggests that charge trapping in the field oxide is associated with shallow defects such as  $E'_{s}$  centers. A comparison of the device response to a first-order kinetics model for hole trapping and annealing indicates that the enhanced degradation results from slower annealing rates following low-dose-rate irradiation. These results suggest that space charge in the field oxide may contribute to the dose rate sensitivity by altering the spatial distribution of trapped holes. In contrast to the response of the TSMC parts, high-dose-rate irradiation and anneal bounds low-dose-rate degradation of transistors from the HP 0.50- and 0.35- $\mu$ m processes. These results imply that existing qualification approaches based on high-dose-rate irradiation and anneal may not be conservative for the hardness assurance testing of some advanced CMOS devices.

Index Terms—Anneal, dose rate,  $E'_{\delta}$  center, edge-leakage current, field oxide, hardness assurance, ionizing radiation, MIL-STD-883F Method 1019.6, metal–oxide–semiconductor field-effect transistor (MOSFET), space charge.

Fig. 1. Cross-section of an n-channel MOSFET isolated by a field oxide. Positive trapped charge in the field oxide can cause off-state leakage current to flow along the channel edges (previously published in [6]).

following ionizing irradiation and anneal. Under worst-case bias conditions, enhanced degradation at low dose rate compared to high-dose-rate irradiation and anneal is observed for transistors from three of the processes. A first-order kinetics model for hole trapping and annealing is used to infer that the enhanced degradation results from slower annealing rates following low-dose-rate irradiation. An activation energy for

### Common Origin for Enhanced Low-Dose-Rate Sensitivity and Bias Temperature Instability Under Negative Bias

Leonidas Tsetseris, Ronald D. Schrimpf, Fellow, IEEE, Daniel M. Fleetwood, Fellow, IEEE, Ronald L. Pease, Senior Member, IEEE, and Sokrates T. Pantelides

Abstract-Degradation due to irradiation is known to be associated with the presence of hydrogen in the bulk of the gate oxide, in bulk Si, and at the Si/SiO2 interface. Previous studies have shown that the migration of protons in the oxide for positive applied gate bias and their reactions at the interface can account for the time and dose-rate dependence of the degradation. Recent experiments, however, have shown that interfacial degradation can occur even in the presence of strong negative gate bias that prevents the arrival of protons at the interface from the oxide side. This result suggests that mechanisms in addition to proton drift in SiO2 can lead to radiation-induced interface-trap formation. Since previous work on modeling the enhanced low-dose-rate sensitivity (ELDRS) of irradiated bipolar devices was based on formation of an electrostatic barrier that hinders proton transport to the interface at high dose rates, this effect also must be examined in more detail. In this work we use results from first-principles calculations to demonstrate that hydrogen can also be released easily in bulk Si, and especially in the near interfacial area. This hydrogen moves readily to the interface under negative bias. Typical hydrogen precursors in Si are identified as H-dopant complexes. ELDRS shares thus a common origin with another critical reliability phenomenon, the negative bias-temperature instability.

Index Terms—Bipolar transistors, enhanced low-dose-rate sensitivity, interface phenomena, interface traps, radiation effects.

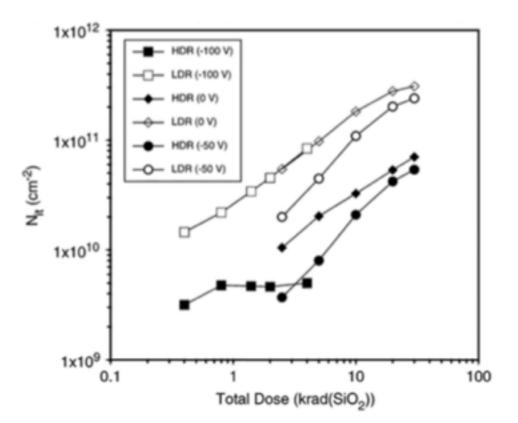

Fig. 1. Density of interface traps (N<sub>it</sub>) in a gated LPNP transistor after irradiation at high (HDR) and low (LDR) dose rates under gate biases 0, −50, and −100 V (See also [5]).

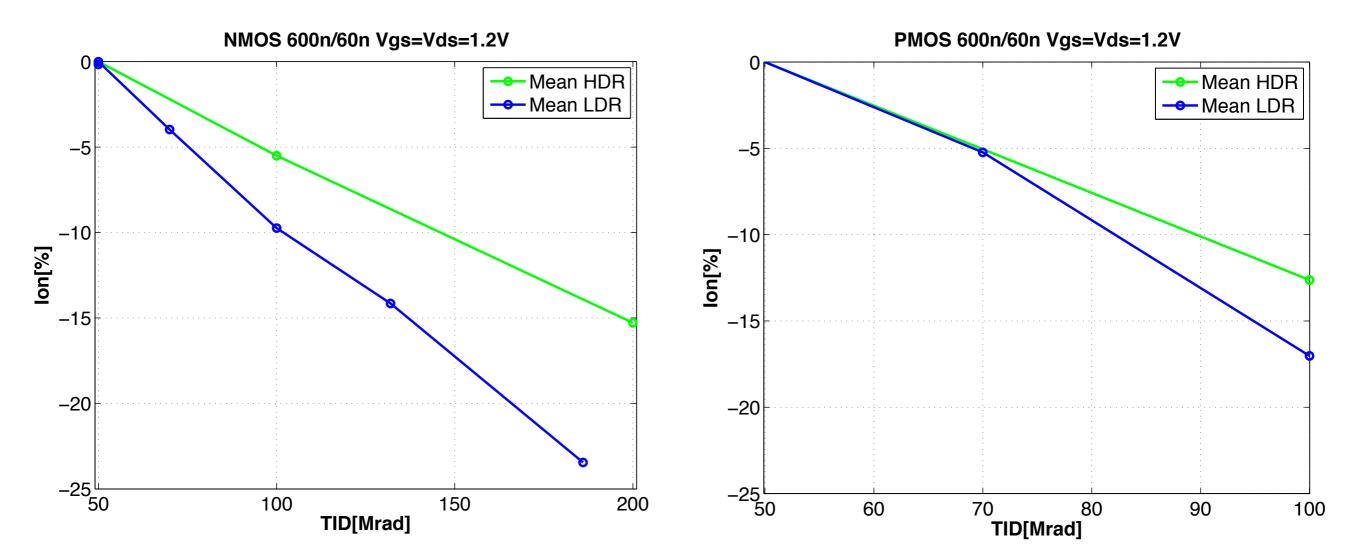

## The only experiment comparing damage at 2 different dose rates is compatible with ELDRS

Given the variability between transistors, this result needs confirmation by more accurate experiments

T = 25°C HDR = 9Mrad/hour LDR = 325krad/hour ratio of the dose rate HDR/LDR=27.7 all samples irradiated at HDR up to 50Mrad, then either at HDR or LDR measurements averaged over 3 samples (HDR) and 2 samples (LDR) We do not understand it all - by far!

Difficult to imagine our community investing much more effort in this study to understand the physical mechanism (new test structures, new set of measurements with other techniques, ....)

Enough data is available to extract damage coefficients for models helping ASIC designers (effort under way at CPPM)

We do not know how/if we can predict the real degradation in the application