L

# CMS HCAL Working Group FE Electronics: New GOL Nov 20, 2007

HCAL personnel interested in GOL/GBT: Jeremy Mans, Tullio Grassi, Drew Baden, Chris Tully, Julie Whitmore

Slides borrowed from Chris Tully, Paolo Moreira, Sandro Marchioro, Jan Troska, Jorgen Christiansen, Terri Shaw

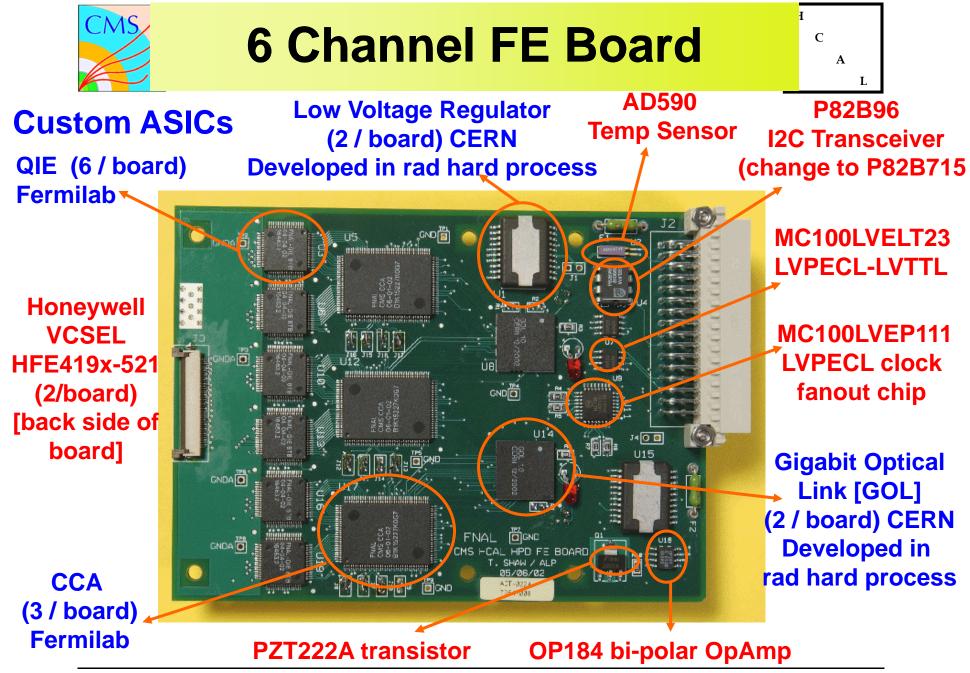

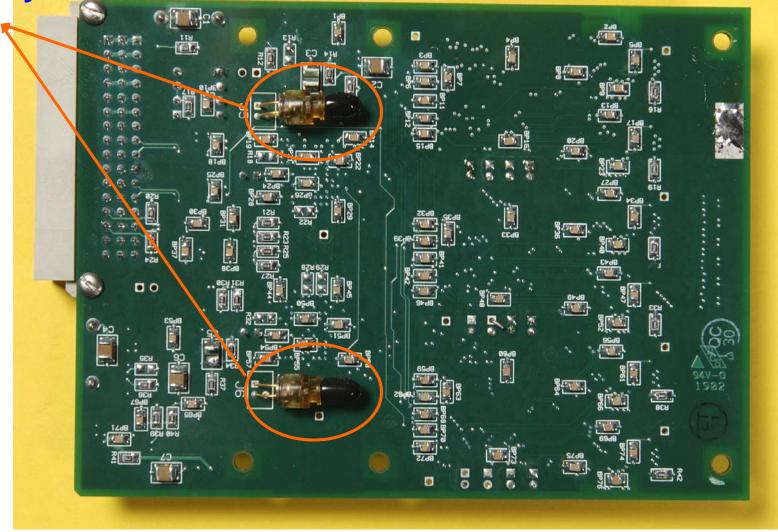

### 6 Channel FE Board (Backside)

### **Honeywell VCSELs**

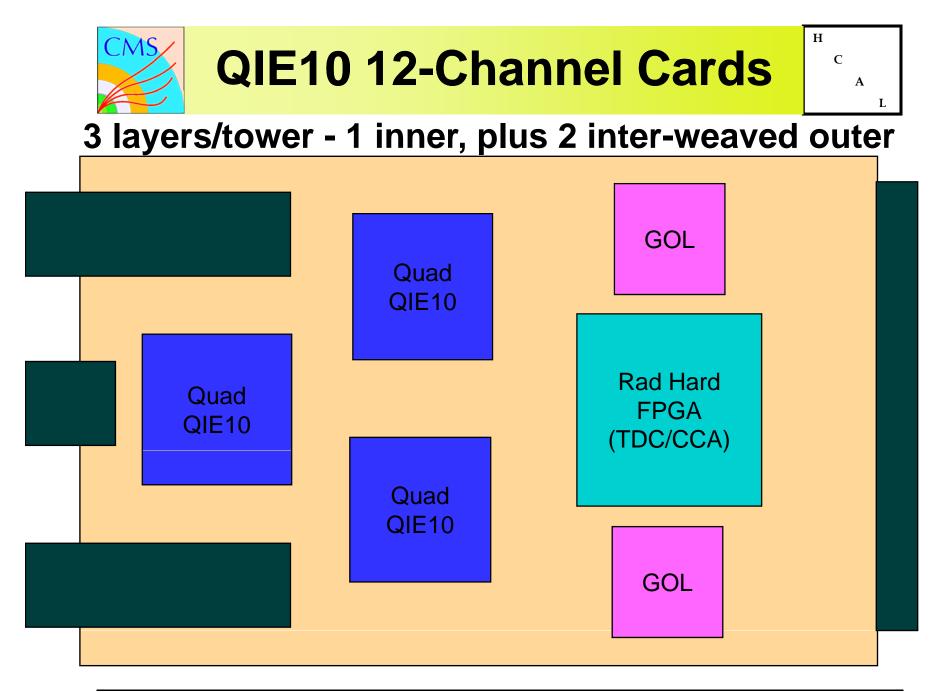

## HB Digital Readout Bandwidth

L

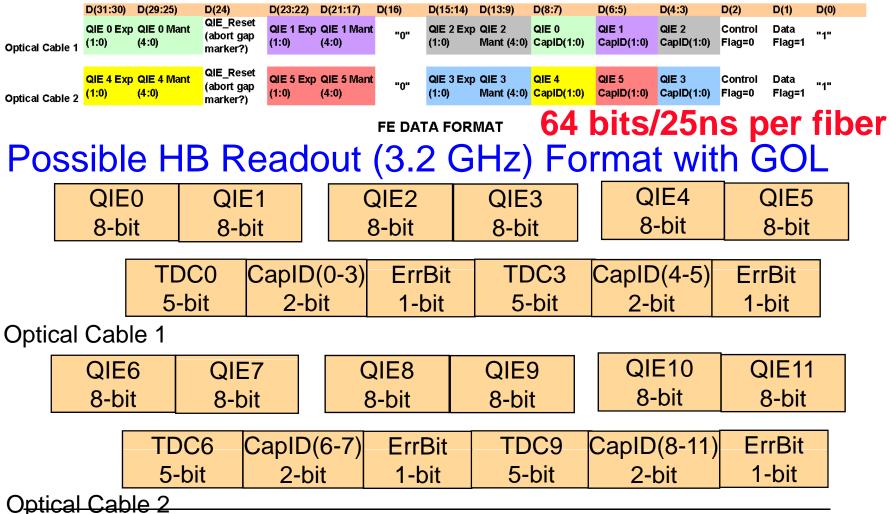

## Current Readout (1.6 GHz) Format

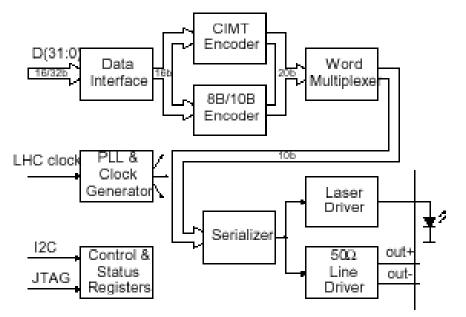

## **Gigabit Optical Link (GOL) Configuration**

- 32 bit mode; 1.6 Gb/s (8-bit/10-bit); Gigabit Ethernet Protocol

- Need to confirm max speed (3.2 Gbps?) w/ bit error rate test UMinn

- At CERN, 30 Wafers with 1770 chips/wafer

- Packaging (for order ~10,000, \$2.5/chip, NRE already paid)

- Place order soon to avoid re-negotiating export license

Figure 1 GOL block diagram.

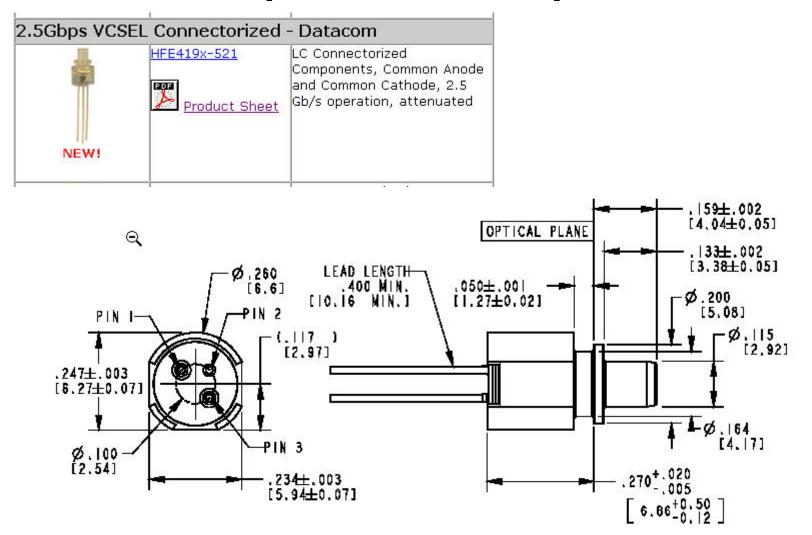

## Connectorized VCSEL (HPD Boards)

# **HCAL Fiber Bandwidth**

L

### Specifications Graded-Index Multimode Optical Fibre. Type: 50 / 125 µm

|   | Characteristics                                                                                | Conditions        | Specified Values |       |                                | Units                |

|---|------------------------------------------------------------------------------------------------|-------------------|------------------|-------|--------------------------------|----------------------|

|   | Optical Characteristics<br>Attenuation Coefficient                                             | 850 nm            | ≤ 2.3            | s 2.4 | ≤25                            | [dB/km]              |

| 1 | Attenuation coefficient                                                                        | 1300 nm           | ≤ 0.5            | ≤ 0.6 | ≤ 2.5<br>≤ 0.7                 | [dB/km]              |

|   | Minumum Modal Bandwidth [1,2]                                                                  | 850 nm<br>1300 nm |                  |       | 400 to > 1000<br>600 to > 1500 | [MHz.km]<br>[MHz.km] |

|   | Numerical Aperture                                                                             |                   |                  |       | $0.200 \pm 0.015$              |                      |

|   | Chromatic Dispersion                                                                           |                   |                  |       | FDDI Spec                      |                      |

|   | Backscatter Characteristics [3]<br>Step [4]<br>Irregularities over fibre length<br>Reflections | 1300 nm           |                  |       | s 0.1<br>s 0.1<br>Not allowed  | [dB]<br>[dB]         |

|   | Group Index of Refraction (Typical)                                                            | 850 nm<br>1300 nm |                  |       | 1.482                          |                      |

Fiber specifications Modal Bandwidth - measure of signal amplitude to drop 3dB 1000 MHz-km = 700-800 Mbps HCAL fiber - 0.1 km 850nm --> 1000 MHz-km --> 7-8 Gbps

Cable

L

### **Cable requirements**

- Able to transmit 1.6 Gbps over 90 m with low dispersion

- 50/125 μm rather than 62.5/125 μm

- Very little darkening of fiber at HCAL radiation levels (3E11 n/cm2 and 1kRad TID)

- Plasma Optical Fiber Graded-Index Multi-mode (Atlas)

- CMS HCAL rad test of RM fiber – no measurable change in transmission

- Controlled environment → No thermal or moisture issues (or rodents!)

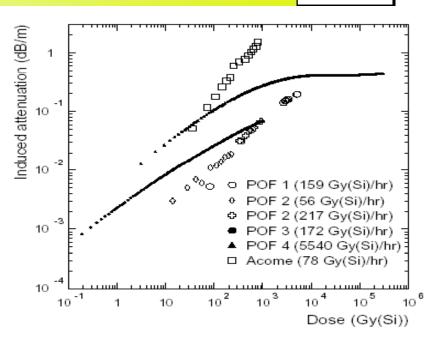

- Fiber radiation study (Atlas)

- Plasma Optic Fiber 50/125µm

Graded Index Multi-mode

Ge-doped fiber selected

- •Rad Tolerant (~0.1 dB/m at

- 800 Gy(Si) and 2E13 n/cm<sup>2</sup>)

Atlas Liquid Argon Cal (ATL-ELEC-99-001)

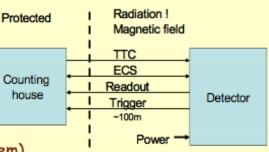

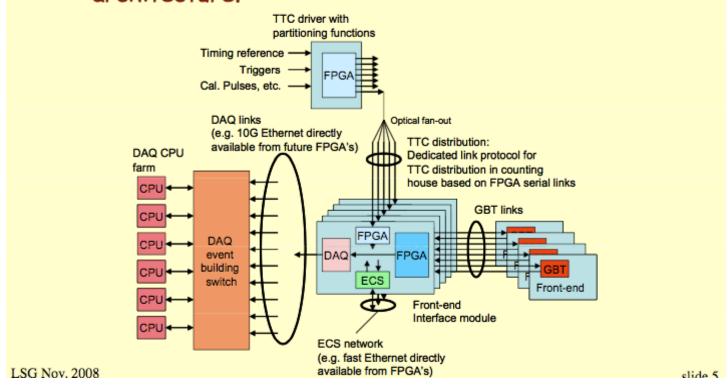

## Link requirements (General)

L

## **Functions needed**

### o TTC: Trigger and timing control

- O Timing reference: clock(s), timing adjust , jitter, , ?

- 0 Trigger signals: trigger accept(s), trigger type, , , ?

- 0 Sync control signals: reset, calibration pulse injection, , , ?

- 0 Fixed and stabilized delay and latency (as short as possible)

- O Unidirectional: down

- 0 Number of signals needed ?

- o Handling multiple FE chips: simple fan-out ?

- 0 Reliability: Very high (SEU sensitive PIN/TIA in radiation !)

### Controls/monitoring: ECS (Experiment Control System)

- 0 Control of parameters in front-ends (with readback)

- o Monitoring: temp, voltage, etc.

- Also DSS related signals ? (very high reliability required, fail safe, etc.)

- Effective data rate needed ? (normally not very high)

- o Bidirectional

- 0 Handling multiple FE chips: addressing, serial/parallel bus ?, other ?

- 0 Reliability: high

### o Readout

- 0 Readout of event data

- o Maximum data rate possible

- Latency not an issue

- Unidirectional: up

- Handling data from multiple FE chips: Merging data streams or local event building

- o Serial or parallel connections ?

- Reliability: high ( single bit flips in readout data can be accepted at low rate)

- o Trigger data

- 0 Similar to readout but constant (and short) latency may be required.

LSG Nov. 2008

### Very expensive if developed by each expt/subsystem

# **SLHC Link Project**

L

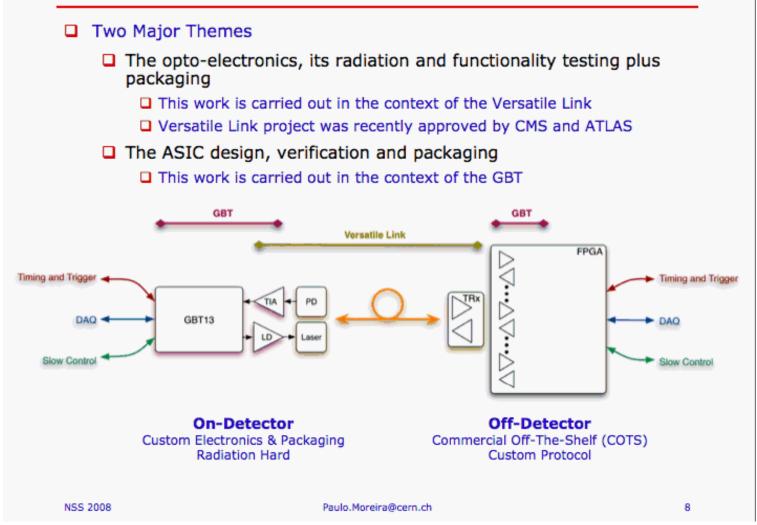

### **Radiation Hard Optical Link: Themes**

# **Develop Architecture**

## **System architecture**

O Decisions on the topology of the front-end link have significant effects on the global system architecture.

# **GBT** chipset

Α

L

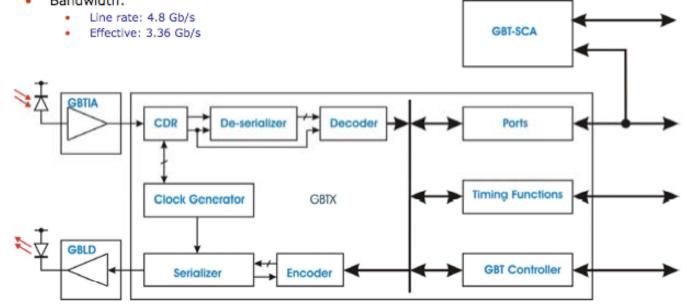

### **GBT** Chipset

- Radiation tolerant chipset:

- GBTIA: Transimpedance optical receiver ٠

- GBLD: Laser driver ٠

- GBTX: Data and timing and transceiver ٠

- GBT-SCA: Slow control ASIC

- Supports:

- Bidirectional data transmission •

- Bandwidth: ٠

- The target applications are:

- Data readout ٠

- TTC •

- Slow control and monitoring links. •

- Radiation tolerance:

- Total dose

- Single Event Upsets ٠

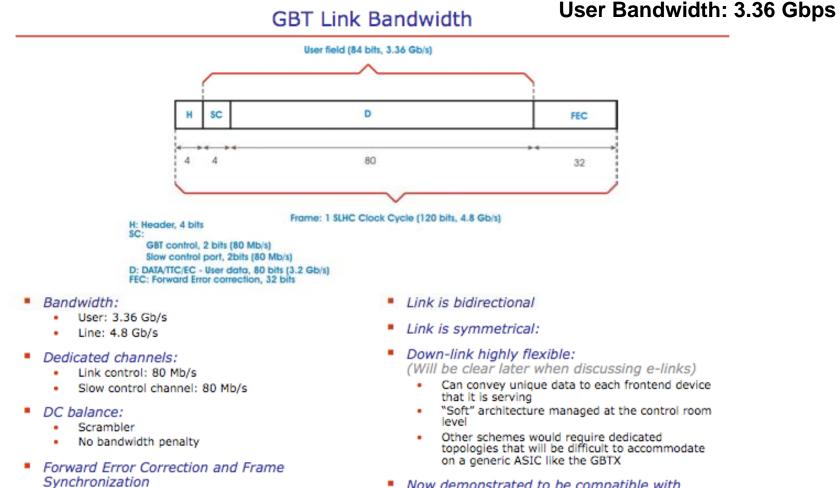

## **GBT Link Bandwidth**

Now demonstrated to be compatible with FPGAs

.

٠

Efficiency: 73%

correction capability)

To be compared with 8B/10B: 80% (no error

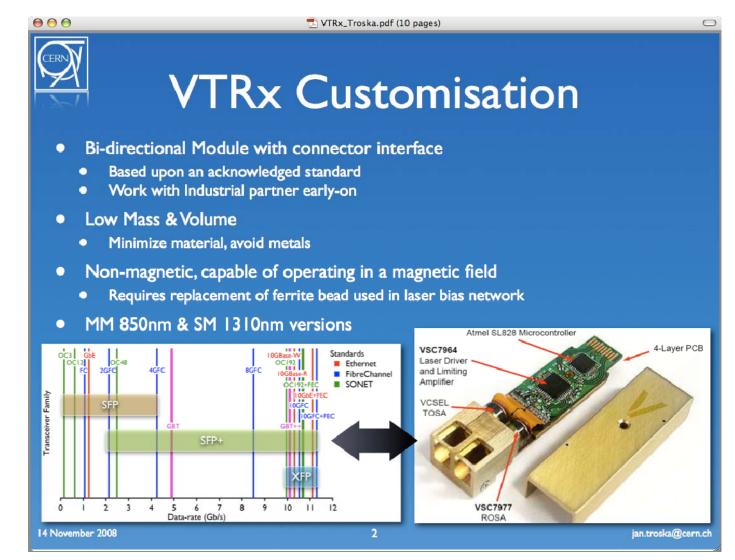

## **VTRx Development**

L

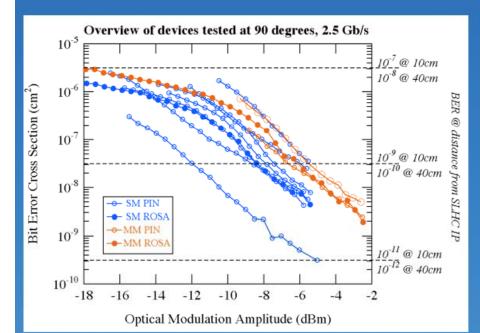

## **COTS SEU studies**

L

# **SEU Result Overview**

| • Device Survey: | Family  | Wavelength | # Device Types (# tested) |

|------------------|---------|------------|---------------------------|

|                  | PIN MM  | 850nm      | 2 (4)                     |

|                  | ROSA MM | 850nm      | I (2)                     |

|                  | PIN SM  | 1310nm     | 7 (14)                    |

|                  | ROSA SM | 1310nm     | I (2)                     |

|                  | MSM MM  | 850nm      | I (2)                     |

- Very Similar overall trend

- ROSA (solid symbols) not much worse than bare PINs

- Several orders of magnitude difference in response between devices

- BER independent of Data-rate

- Burst Errors observed

- max. 10-bits long in PINs

- max. 00's bits long in ROSAs

- Error correction mandatory

- Plans:

- Total Fluence testing of Laser, PINs and possibly TIAs and Laser Drivers in early 2009

## **GBT Schedule**

L

### **Project Schedule**

#### 2008

- Design and prototyping of performance critical building blocks:

TIA, laser driver, PLL, serializer, de-serializer, phase shifter

- First tests of optoelectronics components

- (e.g. to understand SEU in PIN receivers)

- Proceed with the link specification meetings

- General link specification

#### 2009

- Design/prototype/test of basic serializer/de-serializer chip

- Design/prototype/test of optoelectronics packaging

- Detailed link specification document

#### 2010

- Prototype of "complete" link SERDES chip

- Full prototype of optoelectronics packaging

#### 2011

- Extensive test and qualification of full link prototypes

- System demonstrator(s) with use of full link

- Schedule of the final production version is strongly dependent on the evolution of the LHC upgrade schedule

#### NSS 2008

# **HCAL Needs for GBT**

### **GBT - HCAL "requirements" (from Tullio)**

- Investigate 8bit/10bit (64 bit/66 bit)

- Latency does matter

- Max latency should not be greater than existing links

- Jitter needs to be better than QPLL

- Power dissipation should be lower than TTCrx/QPLL/GOL chipset

- Variations in latency of the GBT receiver (at detector) should be smaller than existing TTCrx receiver

- 8ns maximum over all range of operating conditions (temp, power supply, etc.)

- Estimate Latency Variations over a more limited range of operating conditions (15 35 C)

## **Issues - GOL**

L

### Concerns

- Need to package GOLs (~\$25k)

- Test speed of GOL link

- Fiber speed OK. Test final config for BER

- Connections will reduce max speed

- Need to live with TTC system

- Will this system be maintained when other subsystems switch to GBT in Phase II?

## **Issues - GBT**

L

### **Concerns/Comments**

- Need to design HCAL system architecture/topology

- How do we establish bunch synchronizing across asynchronous links? (from Jeremy)

- Similar to GCT problem

- GBT protocol data frames are self synchronizing

- No need to send idle frames (abort gaps can be used for other things (Tullio comment)

- System requirements set by large users

- HCAL does not have many channels

- HCAL needs will not get priority

- Adding additional features adds "unnecessary" complexity to the chips/system

- GBT schedule is very tight for Phase I upgrades

- Tullio is starting to work on this project

- FPGA market survey and GBT emulator for FPGA testing