# HV Energy Dosing dc-to-dc Converter in PWM Mode

Alex Pokryvailo Spellman High Voltage Electronics Corporation Hauppauge, NY 11788 USA Apokryva@spellmanhv.com

Abstract— Energy-dosing (ED) topology is effective for capacitor charging and long- flat-top pulse generation. The inherent advantages for these applications are high efficiency and excellent predictability. ED converter power is proportional to the switching frequency  $f_s$ . Thus, strict realization of ED is possible only when the output is frequency-regulated. At light loads,  $f_s$  might become unacceptably low. Then Pulse Width Modulation (PWM) becomes necessary. This paper develops theory of operation of ED converters in PWM mode. Duty cycle corresponding to a predefined load is calculated, which is sufficient to predict the converter state after any transition. All possible scenarios have been covered and verified with PSpice simulations and experiments with HV converters.

Keywords—high voltage converter, energy dosing, frequency modulation, pulse width modulation, zero-current switching, prediction

#### I. INTRODUCTION

Energy-dosing (ED) topology was shown to be effective for capacitor charging and long- flat-top pulse generation (see [1]-[3] and their bibliography for examples of implementation and for the theory of operation). The inherent advantages for these applications are zero-current switching and excellent predictability following from the ED principle of operation. As the term ED implies, the output power is proportional to the switching frequency fs. Thus, strict realization of ED is possible only when the output is frequency-regulated.

The theory of operation of energy-dosing converter (EDC) at what we term as frequency mode (FM) is described in [1]. In this mode, the switching frequency,  $f_s$ , in a normalized form, is equal to or lower than

$$f_{\text{w}}(V_{load}, E) := \frac{1}{\left[\frac{2}{\pi}\left(\frac{1}{2} \operatorname{acos}\left(\frac{V_{load}}{V_{load} - E}\right) + \frac{E}{2V_{load}} \cdot \sqrt{1 - \frac{2V_{load}}{E}}\right)\right]}$$

(\*)

where *E* is the rail voltage, and both the rail voltage and the load voltage,  $V_{load}$ , are referenced to the same side of the transformer. Then Zero-Current Switching (ZCS) is ensured.

On the base of (\*), a predictive algorithm enabling forming flat pulses at exceptionally fast transitions and high power was formulated and tested elsewhere [3]; it is limited to FM. Some low-power operating scenarios cannot be met in FM if the conversion frequency needs to be kept above certain value, e.g., because of the audibility constraints. Such scenarios can be realized with relay (hysteretic) control or Pulse-Width Modulation (PWM). The latter is desirable in view of better output quality, although the transistor losses increase considerably.

This paper extends theory of operation of ED converters into the PWM mode. Full set of equations is derived for calculation of duty cycle corresponding to a predefined load. All possible scenarios have been covered and verified with PSpice simulations and experiments with HV converters. Thus, this paper paves way to implementing prediction similar to that used in FM.

### II. EDC IN NORMAL MODE (FM)

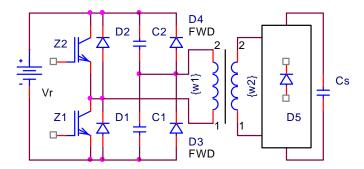

We will need the equations for FM mode as a starting point for the PWM analysis. A simplified schematic diagram of an EDC is shown in Fig. 1, and its full and reduced equivalent circuits (EC) and correspondent timing diagrams are shown in elsewhere [2-3]. We neglect here rail/busbar voltage oscillations and the FWD forward drop on the discharged capacitor. Most important, we neglect also all parasitic capacitances including that of the secondary. We assume that the load voltage does not change much during a half-period of the conversion frequency; then the storage capacitor can be represented by a counter EMF equal to the load voltage. These and other assumptions are detailed in [2-3].

Fig. 1. Half bridge inverter with energy dosing capacitors.

The operation of EDC in FM is described in [1] for both steady-state and charging mode. We will reiterate this analysis to some extent here. All variables and parameters are referenced to the secondary. Usually, parameters in lowercase are dimensionless, whereas uppercase denotes dimensional parameters. The equivalent circuits (EC) are not reproduced here.

The inductance *L* current and the resonant capacitor *C* voltage before  $t_i$  are

$$i_1 = \frac{V_r - V_L}{\rho} \sin \omega t , \quad v_1 = (V_r - V_L) \cos \omega t + V_L, \quad (1)$$

where  $\omega = \frac{1}{\sqrt{LC}}$ ,  $\rho = \sqrt{\frac{L}{C}}$ , and  $V_r$ ,  $V_L$  are rail and load voltage,

respectively. Moments  $t_1$  and  $t_2$  are given as

$$t_{1} = \frac{1}{\omega} a \cos\left(\frac{v_{l}}{v_{l}-1}\right) \ t_{2} = t_{1} + \frac{1}{\omega v_{l}} \sqrt{1 - 2v_{l}}$$

(2)

The winding current at moment  $t_l$  is found from (1) by substituting  $t_l$ :

$$i_{1t1} = \frac{v_r}{\rho} \sqrt{1 - 2v_l} \tag{3}$$

Here  $v_l = V_L/V_r$  is normalized load voltage. It can change from zero (short circuit) to  $\frac{1}{2}$  (maximum voltage). Since the load voltage changes little during half-period, it be set as a constant. Thus, it serves as a parameter and not a variable.

With this assumption, the energies transferred to the load in a half- and full period are, respectively

$$W_{\rm hp} = V_{\rm L} \int_0^{t_2} i \mathrm{d}t, \, W_p = 2W_{hp}. \tag{4}$$

Obviously, for FM they are

$$W_{\rm hp} = C_{\rm d} V_{r1}^2, P_{pwm} \le P_{FM} = 2W_{\rm hp}f = 2C_{\rm d} V_r^2 f,$$

where  $C_d$  (subscript *d* stands for capacitive "divider") is the capacitance of the resonant capacitor (C1 and C2), and  $V_{rl}$  is the rail voltage measured at the primary side. Power generated in PWM,  $P_{pwm}$ , can be only less than that,  $P_{FM}$ , in FM.

#### III. PWM MODE

Our goal is finding duty cycle (DC) corresponding to a predefined load. Contrary to FM, the load cannot be defined in terms of power only; both the power and load voltage have to be specified.

In the following analysis, all variables and parameters are reflected to the secondary side of the transformer.

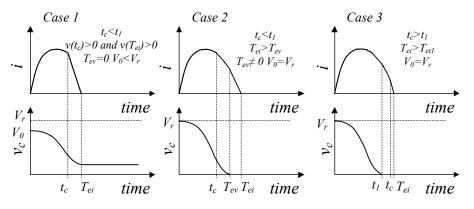

We assume that at the beginning of a half-period the resonant capacitors are charged to a voltage  $V_0 \leq V_r$ . No longer is their voltage swing always equal to  $V_r$ , as in FM, which complicates the analysis considerably. We will make use of timing diagrams Fig. 2 and their notation to render the analysis as transparent as possible.

The gate shut-off time is designated as  $t_c$  (chopping moment). It can occur any time within  $0 \le t_c \le t_2$  ( $t_2$  is the time of natural ZCS). There are three possible scenarios:

Case 1. Capacitor voltage  $v_c$  does not fall to zero at both  $t_c$  and  $T_{ei}$  ( $T_{ei}$  denotes current zero).

Case 2. Chopping occurs before  $t_1$  ( $t_1$  is moment when  $v_c$  falls to zero), but  $v_c$  reaches zero before the current does.

Case 3. Chopping occurs after  $t_1$ .

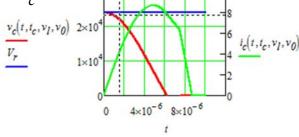

Fig. 2. Timing diagrams of EDC in PWM mode.

We note that diagrams Fig. 3 were derived from experimental observations and circuit simulations.

In steady state, voltage  $v_c$  must satisfy the periodicity condition (here and further a Mathcad notation is used):

$$V_{r} \cdot (1 - v_{0}) = v_{c} \left( \frac{T_{I}(v_{l})}{2}, t_{c}, v_{l}, v_{0} \right)$$

(5)

where  $v_0 = \frac{V_0}{V_r}$ , and  $T_1/2=t_2$  is the current pulse duration in FM:

$$T_{I}(v_{l}) := \frac{2}{\pi} \left( \frac{1}{2} \operatorname{acos} \left( \frac{v_{l}}{v_{l} - 1} \right) + \frac{1}{2v_{l}} \cdot \sqrt{1 - 2v_{l}} \right) \cdot T , \quad T := 2 \pi \sqrt{L \cdot C}$$

Thus, for Case 1,  $V_r/2 \le V_0 \le V_r$ , and for Cases 2, 3,  $V_0 = V_r$ .

In PWM mode the output is regulated by changing  $t_c$  at a constant conversion frequency. Operating in terms of energy per half-period, rather than power, we rewrite (4) as

$$W_{hp} = V_{L} \int_{0}^{T_{ei}} idt, or$$

$$w_{hp}(t_{c}, v_{l}, v_{0}) \coloneqq \frac{V_{r} \cdot v_{l}}{W_{hptmax}} \cdot \int_{0}^{\frac{T_{l}(v_{l})}{2}} i_{c}(t, t_{c}, v_{l}, v_{0}) dt \qquad (6)$$

where  $w_{hp} = W_{hp}/W_{hpmax}$  is normalized energy; the quantity

$$W_{hpmax} = C_d V_{r1}^2 \tag{7}$$

is the maximum energy that can be supplied to the load in a halfperiod. Assigning

$$W_{hp} = W_{hpt}$$

, or  $w_{hp} = w_{hpt}$  (8)

and solving system (5), (8) for  $t_c$ ,  $v_0$ , we find  $t_c$ , or duty cycle, necessary to provide the *targeted energy*  $W_{hpt}$ . The initial state  $V_0$  is for reference only.

Prior to  $t_c$ , the operation of an EDC can be described by modified equations (1) recognizing that C can be charged to  $V_0$ rather than  $V_r$ . Thus, the inductance L current and the resonant capacitance C voltage before  $t_1$  are given as:

$$i_{1} = \frac{V_{0} - V_{L}}{\rho} \sin \omega t, \ v_{1} = (V_{0} - V_{L}) \cos \omega t + V_{L}, \qquad (9)$$

The winding current at moment  $t_l$  is found from (9) by substituting  $t_l$  from (2):

$$i_{ItI}(v_l, v_0) \coloneqq \frac{V_r}{\rho} \cdot \sqrt{v_0 \cdot (v_0 - 2v_l)} \tag{10}$$

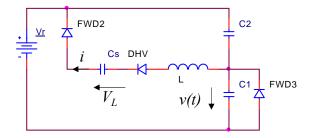

After  $t_c$ , the EC transforms to that of Fig. 3. (The values are irrelevant.) This EC is actually valid for all the three Cases if we recognize that the current switches to the FWD3 (capacitor clamping diode) after the resonant capacitor C1 has discharged to zero. Full analysis of all possible combinations has been performed. In this short paper, we provide only final equations and their selected solutions.

Fig. 3. Equivalent circuit with notation according to Fig. 1 after *t<sub>c</sub>*. (FWD2 is parallel to transistor Z2, DHV stands for HV rectifier.) Current *i* is split equally between C1 and C2 if FWD3 does not conduct.

Starting from t=0 to the end of half-period, the voltage across the resonant cap  $v_c$  and the winding current  $i_c$  (all reflected to the secondary) are expressed by

. . .

$$v_{c}(t, t_{c}, v_{l}, v_{0}) := v_{I}(t, v_{l}, v_{0}) \text{ if } t < t_{c}$$

$$if \ t > t_{c} \land T_{ev}(t_{c}, v_{l}, v_{0}) = 0$$

$$(11)$$

$$v(t - t_{c}, t_{c}, v_{l}, v_{0}) \text{ if } t < t_{c} + T_{el}(t_{c}, v_{l}, v_{0})$$

$$v(T_{el}(t_{c}, v_{l}, v_{0}), t_{c}, v_{l}, v_{0}) \text{ otherwise}$$

$$if \ t_{c} < t_{I}(v_{l}, v_{0}) \land t > t_{c} \land T_{ev}(t_{c}, v_{l}, v_{0}) \neq 0$$

$$v_{2}(t - t_{c}, t_{c}, v_{l}, v_{0}) \text{ if } t > t_{c} \land t \leq t_{c} + T_{ev}(t_{c}, v_{l}, v_{0})$$

$$0 \text{ otherwise}$$

$$0 \text{ if } t_{c} > t_{I}(v_{l}, v_{0}) \land t > t_{c}$$

$$\begin{split} i_{c}(t,t_{c},v_{l},v_{0}) &\coloneqq & i_{l}(t,v_{l},v_{0}) \text{ if } t < t_{c} \\ &\text{if } (t > t_{c} \land T_{ev}(t_{c},v_{l},v_{0}) = 0) \\ & \begin{bmatrix} i(t-t_{c},t_{c},v_{l},v_{0}) & \text{if } t < t_{c} + T_{el}(t_{c},v_{l},v_{0}) \\ 0 & \text{otherwise} \\ &\text{if } t_{c} < t_{l}(v_{l},v_{0}) \land (t > t_{c} \land T_{ev}(t_{c},v_{l},v_{0}) \neq 0) \\ & \begin{bmatrix} i_{2}l(t-t_{c},t_{c},v_{l},v_{0}) & \text{if } t < t_{c} + T_{ev}(t_{c},v_{l},v_{0}) \\ i_{2}2(t-t_{c} - T_{ev}(t_{c},v_{l},v_{0}),t_{c},v_{l},v_{0}) & \text{if } t > t_{c} + T_{ev}(t_{c},v_{l},v_{0}) \\ 0 & \text{if } t > T_{e2}(t_{c},v_{l},v_{0}) + t_{c} \\ & \text{if } t_{c} > t_{l}(v_{l},v_{0}) \land t > t_{c} \\ & \begin{bmatrix} i_{l}(t-t_{c},v_{l},v_{0}) & \text{if } t > t_{l}(v_{l},v_{0}) \land t > t_{c} \\ & i_{l}(t-t_{c},t_{c},v_{l},v_{0}) & \text{if } t < t_{c} + T_{etl}(t_{c},v_{l},v_{0}) \land t > t_{c} \\ & 0 & \text{if } t > T_{etl}(t_{c},v_{l},v_{0}) + t_{c} \\ \end{bmatrix}$$

Calculations were performed for a hypothetical EDC with the following parameters:

$$E=480 \text{ V}, k_{tr}=50, V_r=Ek_{tr}, V_L=V_r/2, L=6 \text{ mH}, C_d=2 \mu\text{H}.$$

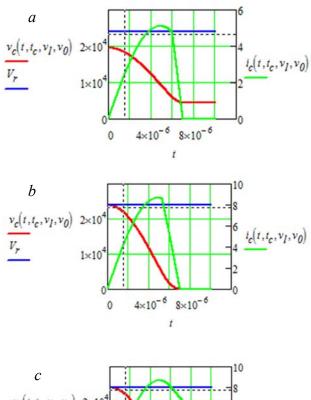

Several examples of waveforms derived from System (5), (8) with voltage and current given by (11), (12) for different combinations of  $w_{hp}$  and  $v_l$  are given in Fig. 4. The  $V_r$  value is shown for reference to accentuate the  $v_c$  symmetry relative to rail.

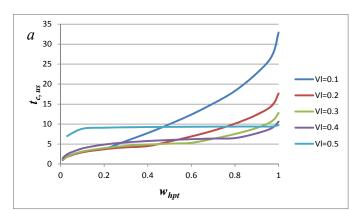

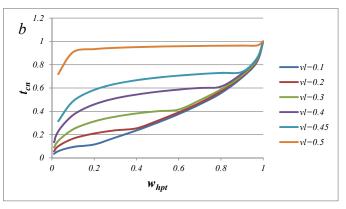

We will normalize also the pulsewidth  $t_c$ :

$$t_{cn} = \frac{2t_c}{T_1} \tag{13}$$

The base here is  $T_1/2$ , which is the current pulse duration in FM. Fig. 5 shows the pulsewidth versus energy per half-period, in both dimensional (for the above EDC) and non-dimensional forms.

We note that both  $t_c$  and  $t_{cn}$  values corresponding to  $w_{hpt}=1$  were calculated straight from (6), because solution of (5), (8) does not converge well at  $w_{hpt}=1$ . Neither does it always converge around  $v_t=0.5$  and very small  $w_{hpt}$  values. Using Fig. 5b (or its tabulated version) and basis values for a specific converter, we can calculate the actual pulsewidth (duty cycle).

We will give an example for the converter module described in [3]. Its rated power is 50 kW which can be generated in FM at  $f_s \approx 70$  kHz at low line. In PWM, the converter operates at  $f_s = 16$  kHz. The converter state can be defined in terms of power that is calculated as  $P_{PWM} = 2W_{hp}f_s$ . This module has L=1.33 mH,  $C_d=1.8 \mu$ F,  $k_{tr}=50$ , and the bases for it are E=480 V,  $W_{hpmax}=C_dE^2=0.415$  J.

Fig. 4. Current and voltage waveforms (referenced to secondary) illustrating all three cases. Horizontal scale – time, s; vertical – voltages, V. a - Case 1:  $w_{hpt}$ =0.5,  $v_t$ =0.4,  $t_t$ =8.974 µs,  $t_c$ =6.02 µs; b - Case 2:  $w_{hpt}$ =0.6,  $v_t$ =0.3,  $t_t$ =6.239 µs,  $t_c$ =5.312 µs; c - Case 3:  $w_{hpt}$ =0.8,  $v_t$ =0.3,  $t_t$ =6.239 µs,  $t_c$ =7.509 µs.

An example of recalculation for dimensional variables using (13) is shown in Table 1. This information can be used in the following way. If the converter needs to transit abruptly from one state to another, e.g., from a lower voltage to a higher level, *prior* knowledge of DC in PWM mode (or f in FM) allows correct setting of the feedback circuitry, analog or digital, on the point of the transition. Thus, the developed equations, or more correctly, the tabulated results as Look-up-Tables, can serve for prediction of pulsewidth/DC in PWM mode.

Fig. 5. Pulsewidth dependence on energy per half-period.

TABLE 1. DUTY CYCLE, D, VERSUS POWER WITH LOAD VOLTAGE AS PARAMETER.

|              | D, %        |             |             |             |                             |             |

|--------------|-------------|-------------|-------------|-------------|-----------------------------|-------------|

| <i>P</i> , W | $v_l = 0.1$ | $v_l = 0.2$ | $v_l = 0.3$ | $v_l = 0.4$ | <i>v</i> <sub>l</sub> =0.45 | $v_l = 0.5$ |

| 133          | 0.82        | 0.71        | 0.82        | 1.02        |                             |             |

| 1328         | 2.22        | 2.09        | 2.24        | 2.79        | 3.48                        | 6.31        |

| 2656         | 2.71        | 2.64        | 2.86        | 3.48        | 4.18                        | 6.49        |

| 6640         | 7.12        | 4.03        | 3.66        | 4.30        | 4.93                        | 6.64        |

| 9296         | 10.81       | 5.97        | 4.52        | 4.55        | 5.15                        | 6.68        |

| 11952        | 16.24       | 8.82        | 6.46        | 5.49        | 5.28                        | 6.71        |

| 13280        | 23.52       | 12.61       | 9.13        | 7.57        | 7.16                        | 6.96        |

## REFERENCES

- B. Kurchik, A. Pokryvailo and A. Schwarz, "HV converter for capacitor charging", Pribory i Tekhnika Experimenta, No. 4, pp.121-124, 1990, Translation to English Plenum Publishing Corp.

- [2] A. Pokryvailo, C. Carp, and C. Scapellati, "High power, high performance, low cost capacitor charger concept and implementation", IEEE Trans. Plasma Sci., Vol. 38, No. 10, October 2010, pp. 2734-2745.

- [3] A. Pokryvailo, C. Carp, and C. Scapellati, "A 100 kW high voltage power supply for dual energy computer tomography applications", IEEE Trans. Dielectr. Electr. Insul., Vol. 22, No. 4, August 2015, pp. 1945-1953.