## Calorimetry systems for the ILC

<u>Outline</u>

- Calorimetry at a future linear collider

- CALICE Analog Hadronic Calorimeter

- Active Elements Silicon Photomultipliers & Scintillating tiles

- Electronics development

Konrad Briggl, KIP HighRR seminar 28.10.15

UNIVERSITÄT HEIDELBERG ZUKUNFT SEIT 1386

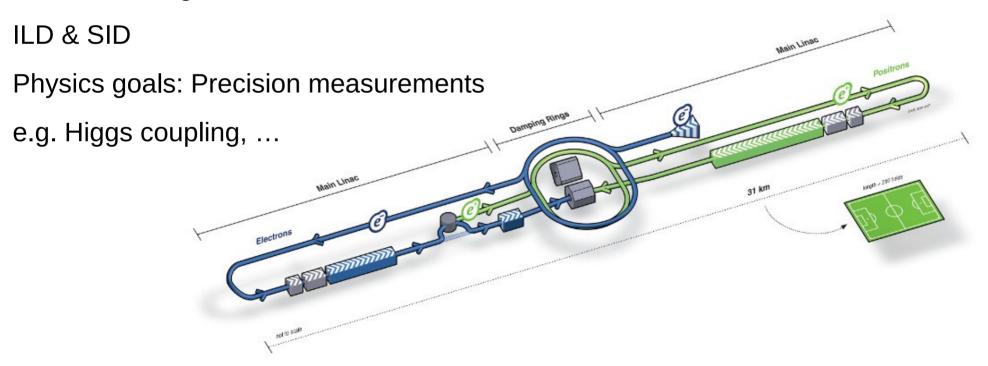

# ILC: The international linear collider

Future e<sup>-</sup>-e<sup>+</sup> accelerator, sqrt(s) up to 500 GeV (Possible upgrade to 1TeV) 31km length in 500GeV baseline design Mature machine technology

Two interchangeable Detectors:

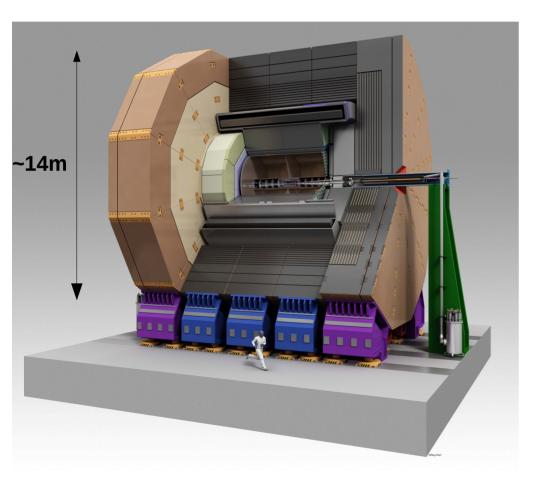

# ILD - International Large Detector

### Tracking:

Pixel Detectors (CMOS/CCD/DEPFET) TPC (Micromegas / GEM)

### Calorimetry

Si / Scintillator+SiPM (ECAL)

RPC / Scintillator+SiPM (HCAL)

**Muon system**

RPC / Scintillator+SiPM

# Calorimetry in HEP

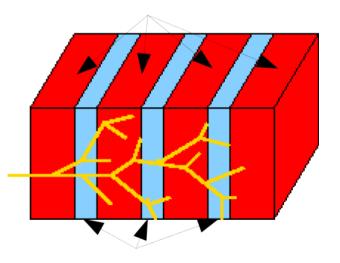

#### Most common structure: Sampling Calorimeter

Dense absorber (e.g. steel, tungsten, ... )

Cost optimization: material volume ↔ magnet size

Active medium (e.g. scintillator, RPC, LAr)

Energy measurement by "counting" of tracks in shower

absorber

active layers

# Calorimetry for ILC experiments

#### **CALICE** collaboration

Calorimetry for a future linear collider experiment. Includes SiD, CLIC

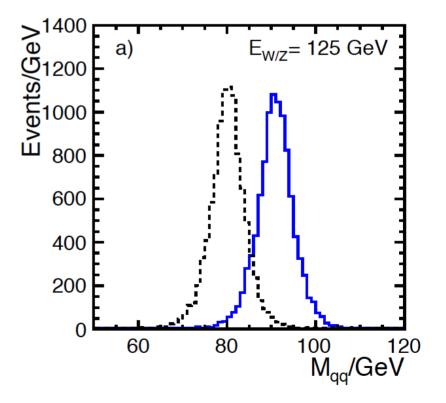

Seeking energy resolution:

$\sigma(E_{iet})/E_{iet} \approx 3-4\%$  for  $E_{iet} = 40 - 500$  GeV

Differentiate decays W  $\rightarrow$  jj ,Z  $\rightarrow$  jj from mass reconstruction

Typical hadronic calorimeter:

$$\sigma(E_{iet})/E_{iet} \approx 60\%/\sqrt{E[GeV]} + 2\%$$

→ 10% for

$$E_{jet} = 50 GeV$$

ILD approach: Particle flow algorithms

# Calorimetry for ILC experiments

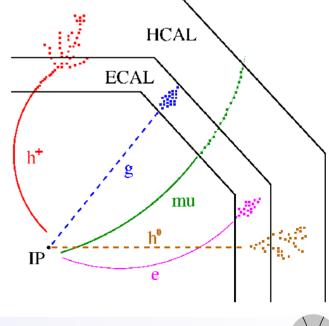

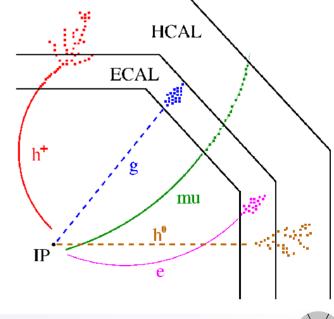

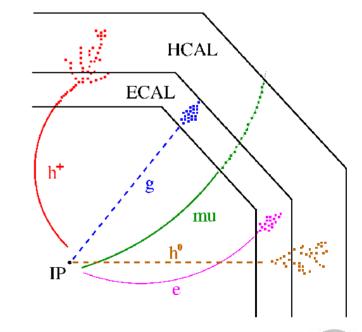

### **Particle flow algorithms**

Use sub-detector with highest resolution:

Charged particles  $\rightarrow$  Tracking

e,  $\gamma \rightarrow ECAL$

n, K  $\rightarrow$  HCAL

Ideally: Only measure energy of neutrals in HCAL

# Calorimetry for ILC experiments

### **Particle flow algorithms**

Use sub-detector with highest resolution:

|                   |            | typical jet |  |

|-------------------|------------|-------------|--|

| n, K              | → HCAL     | ~10 %       |  |

| е, ү              | → ECAL     | ~30 %       |  |

| Charged particles | → Tracking | ~60 %       |  |

<u>Ideally:</u> Only measure energy of neutrals in HCAL 10 % neutrals in typical jet

### **Particle flow algorithms**

Charged particles

e, γ

Use sub-detector with highest resolution:

n, K → HCAL

typical jet

~60 %

~30 %

~10 %

Ideally: Only measure energy of neutrals in HCAL

$\rightarrow$  Tracking

→ ECAL

10 % neutrals in typical jet

... still 16%/ $\sqrt{E}$  contribution from neutral Hadrons

... still need a good calorimeter!

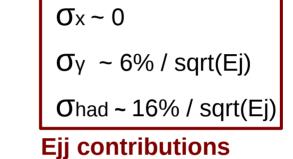

$\sigma^{2}_{jet} = \sigma^{2}_{X} + \sigma^{2}_{Y} + \sigma^{2}_{had} + \sigma^{2}_{loss} + \sigma^{2}_{conf}$

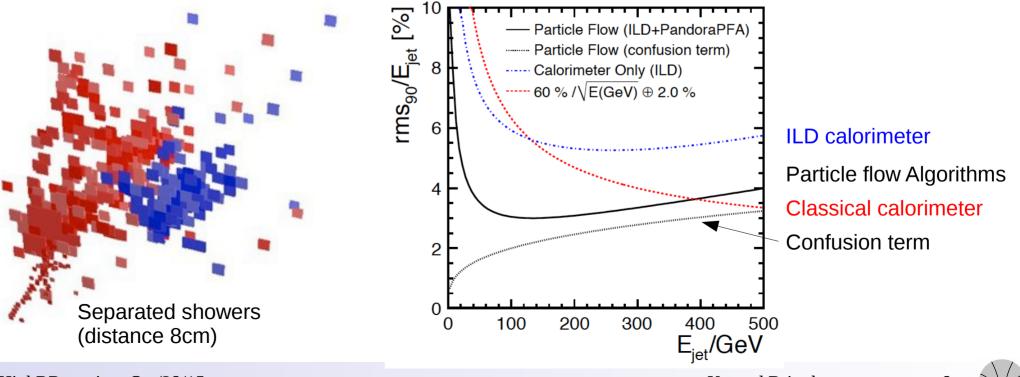

#### **Higher energies: Confusion term dominates**

$\sigma^{2}_{jet} = \sigma^{2}_{X} + \sigma^{2}_{Y} + \sigma^{2}_{had} + \sigma^{2}_{loss} + \sigma^{2}_{conf}$

Wrong association of tracks ↔ showers

- → Good Tracking

- $\rightarrow$  Good shower separation

HighRR seminar Oct/28/15

#### **Parameters for energy resolution**

- $\rightarrow$  electromagnetic performance

- $\rightarrow$  hadronic performance

- $\rightarrow$  shower separation

Requires precise modeling of shower structure

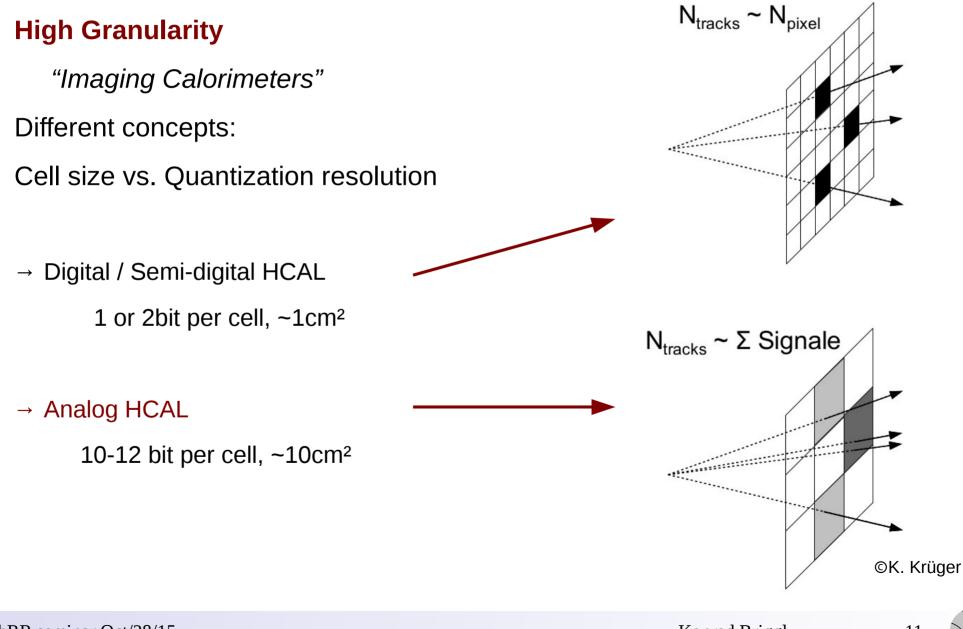

#### **Detector optimization**

→ High Granularity

"Imaging Calorimeters"

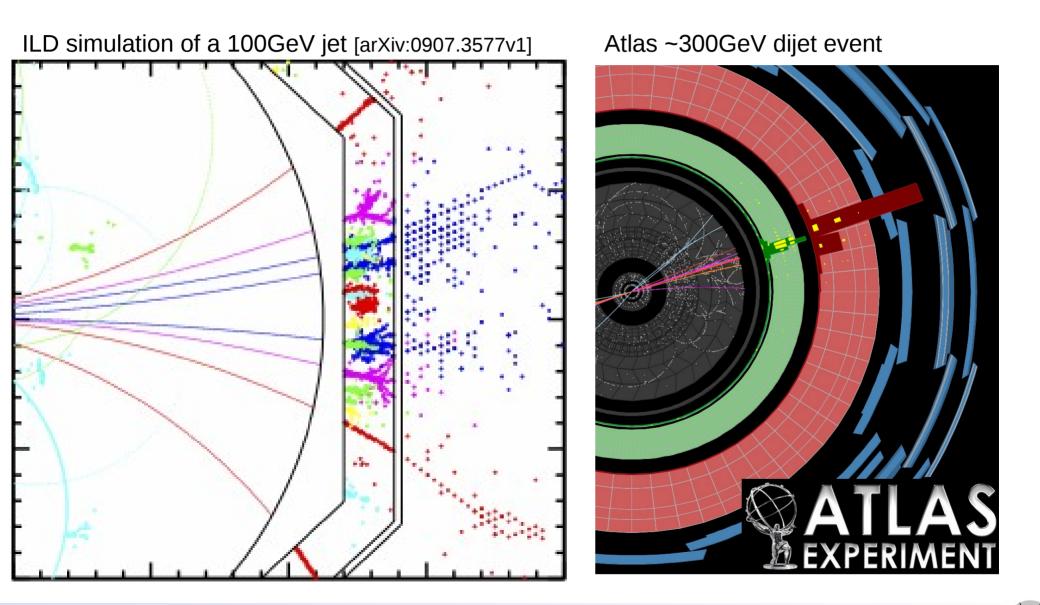

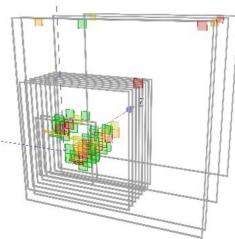

# High granularity?

HighRR seminar Oct/28/15

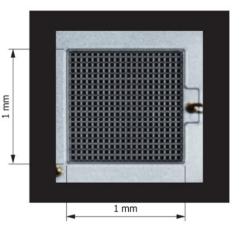

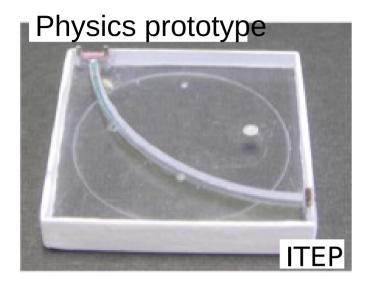

### CALICE AHCAL

- Analog Hadronic Calorimeter concept

- Scintillator based sampling calorimeter, tiles of 3x3cm<sup>2</sup>

- Individual SiPM readout per cell

- 1m<sup>3</sup> physics prototype operated 2006 2012

- Intensive performance studies:

EM&Hadronic showers, Imaging capabilities

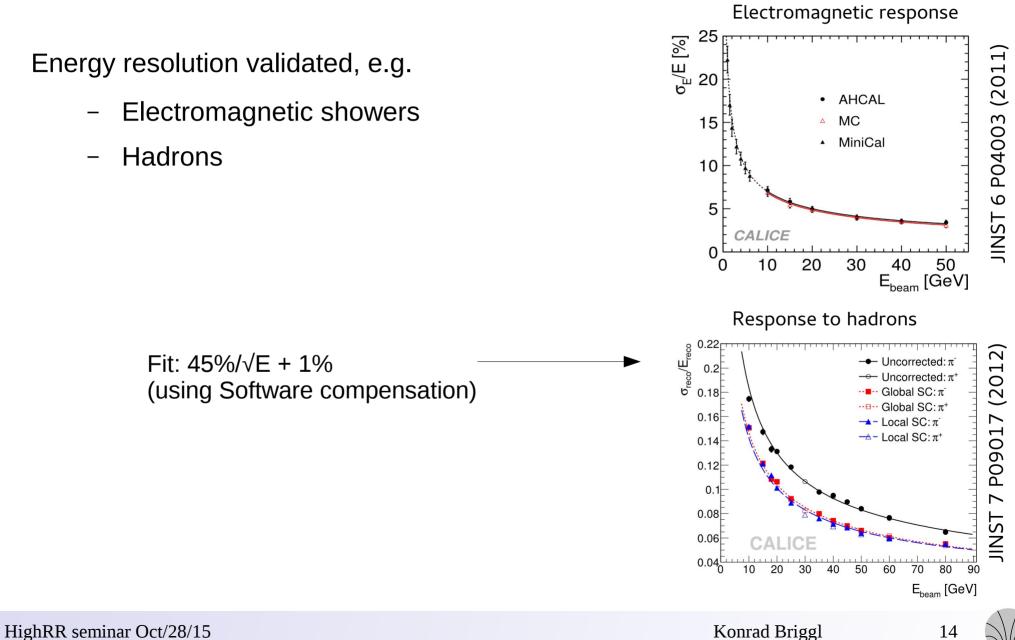

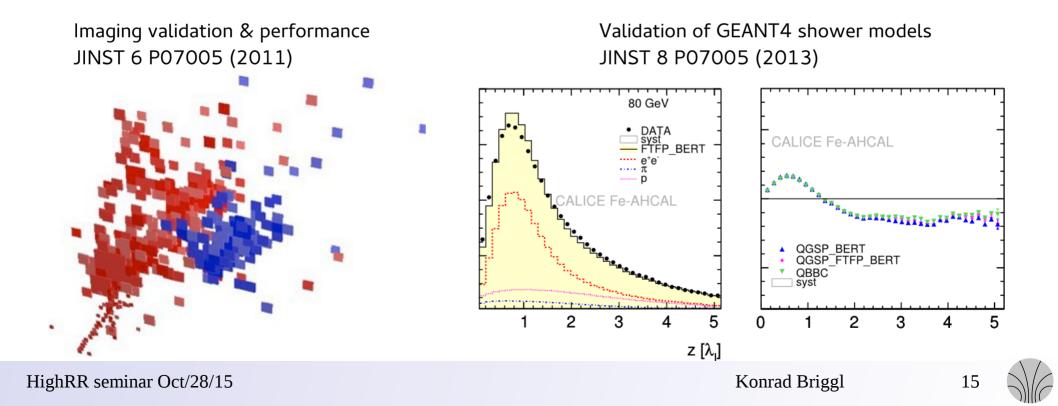

## Performance of the physics prototype

## Performance of the physics prototype

Validation of PFA capabilities and monte carlo shower models

- Shower separation

- GEANT4 shower model validation

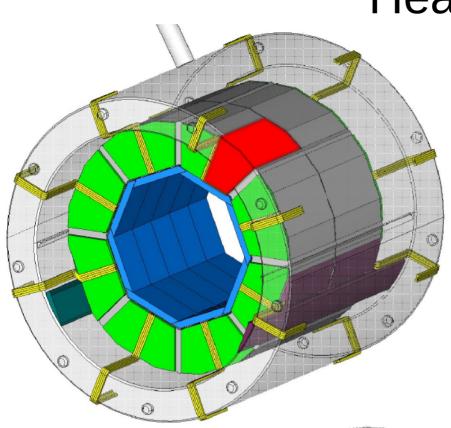

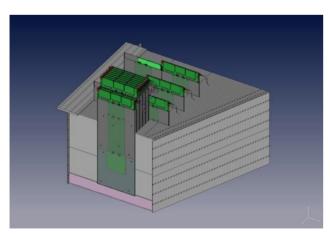

# Heading to a scalable system - Engineering prototype

### <u>Goal:</u>

Develop part of full calorimeter that could be scaled to full size

### Challenges:

Scalability:

10 000 channels in physics prototype

8 000 000 channels in ILD detector

→ Tile R&D for scalability

### Compactness:

- High integration level

- No active cooling

- → Destinct readout electronics, DAQ and calibration system

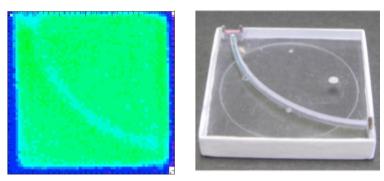

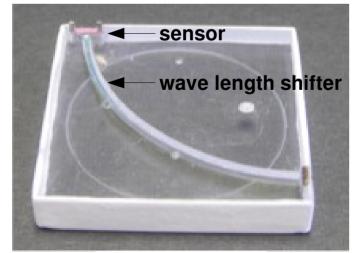

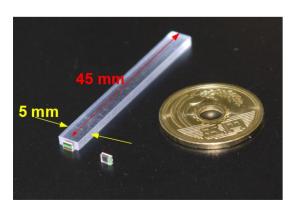

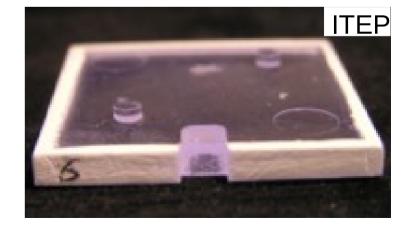

## Active Elements – Scintillating Tiles

Parameters for tile R&D

Light yield, Signal-to-noise ratio

**Response uniformity**

Cell to cell crosstalk

Scalable prototypes:

Possibility of mass production cost ...

→ Simplification of tile design

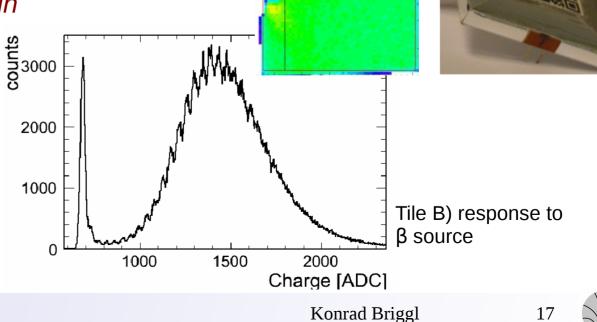

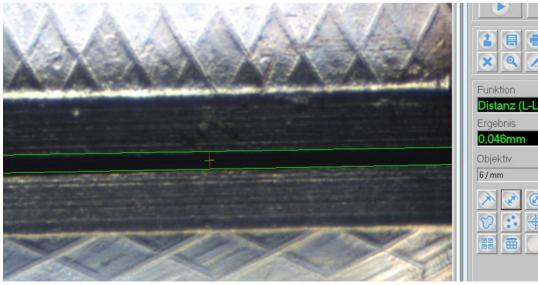

Uniformity scans using Sr90 source

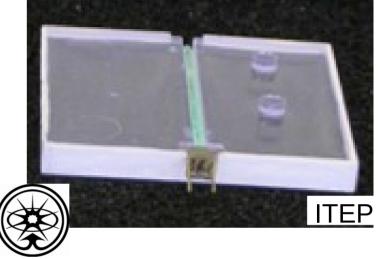

## Active Elements – Scintillating Tiles

#### Mass production & testing possibility becomes important

Simplifictation of tile production:

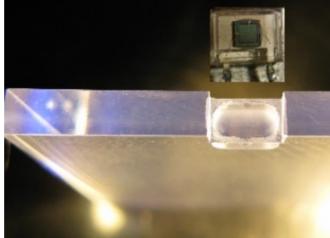

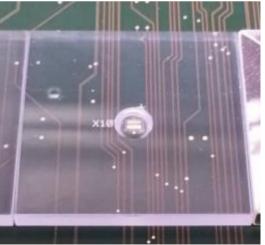

Availability of Blue & nUV sensitive sensors  $\rightarrow$  Fiberless coupling Improved yield & Quality of sensors  $\rightarrow$  SMD mounting of sensors

Cost, Time per tile: Production, Testing, Mounting, ... 1s / tile

→ Dedicated work on Mass Characterization & Assembly

**Physics prototype**

**Concepts for fiberless coupling**

**SMD** mounted SiPMs

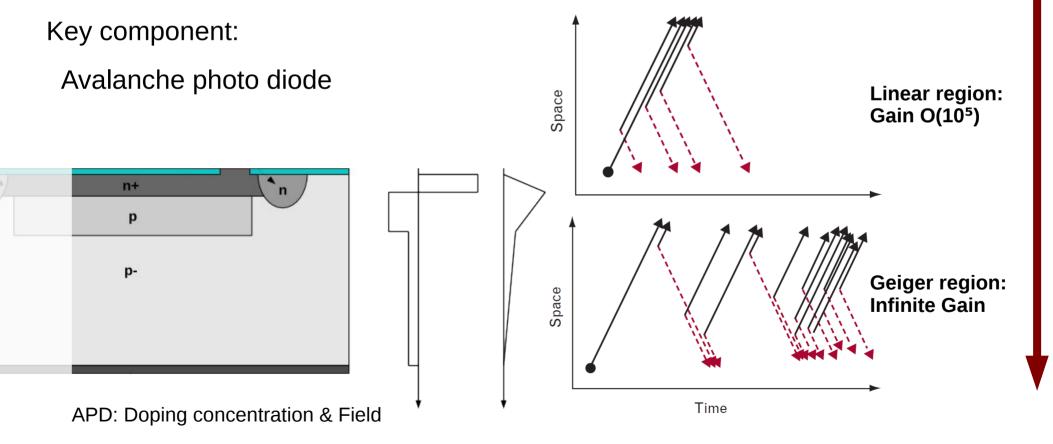

## Active elements – Silicon Photomultipliers

Read-out of scintillation light - O(10) detected photons

Normal Photomultipliers: Large, B-Field sensitive

Compact semiconductor devices:

### **Silicon Photomultipliers**

**Bias voltage**

Drift: Gain = 1

## Active elements – Silicon Photomultipliers

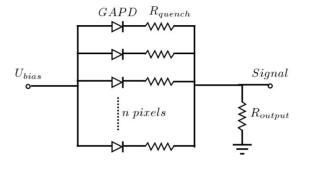

### **Silicon Photomultipliers**

Parallel connected APDs in geiger mode

Avalanche Quenching resistor

→ APD pixels are 'binary devices'

$Q = N_{px} * C_{px} (U - U_{br})$ fired pixels

single pixel gain

- ~ Incident photons

- ~ Traversing particles

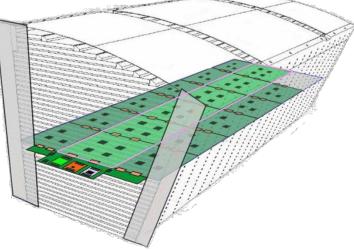

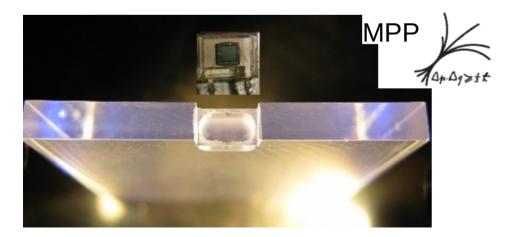

## Scintillator ECAL option

Even higher granularity than HCAL

Segmentation: 1cm<sup>2</sup>

One option: Scintillating strips & SiPM readout

Similar scintillator optimizations as for AHCAL

Large dynamic range

$\rightarrow$  Large pixel count SiPMs (10k pixels/mm<sup>2</sup> – low gain)

SCECAL: scintillator strips

Layer for engineering prototype

HighRR seminar Oct/28/15

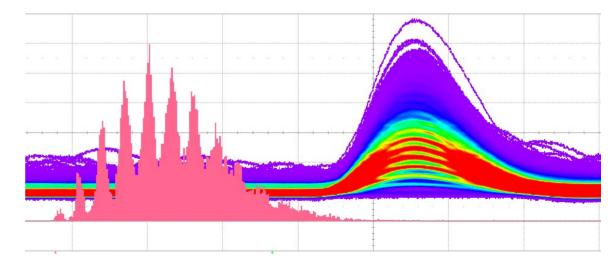

### **Measurements**

Shower timing [<1ns]

Energy measurement:

Small signals (SiPM gain calibration)

[Charge ~15fC ... 2pC]

Large signals (MIP counting)

[Charge up to 150pC]

### High integration level

Fully integrated readout electronics

No active cooling  $\rightarrow$  Low power

Self-triggered operation

SiPM gain adjustment

### $\rightarrow$ Requires a versatile chip

### **Measurements**

- Shower timing [<1ns]

- Energy measurement:

- Small signals (SiPM gain calibration)

- [Charge ~15fC ... 2pC]

- Large signals (MIP counting)

- [Charge up to 150pC]

### High integration level

#### Fully integrated readout electronics —

- SiPM gain adjustment

- No active cooling  $\rightarrow$  Low power

#### **Development of Mixed signal ASICs**

- Analog Front-end

- Integrated ADC, TDC

- Digital readout

Baseline solution: SPIROC, designed by French group

Development for low gain SiPMs: KLauS ASIC (KIP)

SPIROC2b, Omega/F

### **Measurements**

Shower timing [<1ns]

Energy measurement:

Small signals (SiPM gain calibration)

[Charge ~15fC ... 2pC]

Large signals (MIP counting)

[Charge up to 150pC]

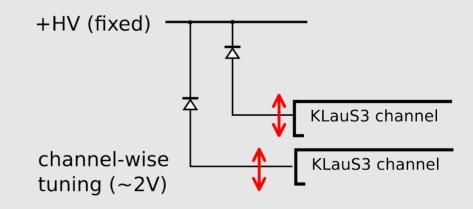

### High integration level

Fully integrated readout electronics

#### SiPM gain adjustment

No active cooling  $\rightarrow$  Low power

Temperature & SiPM parameter fluctuations

Gain adjustments per channel

Large number of channels

-One HV source per layer (~2500 channels)

-Small tuning range for each SiPM (~2V)

### **Measurements**

Shower timing [<1ns]

Energy measurement:

Small signals (SiPM gain calibration)

[Charge ~15fC ... 2pC]

Large signals (MIP counting)

[Charge up to 150pC]

### High integration level

Fully integrated readout electronics

SiPM gain adjustment

No active cooling  $\rightarrow$  Low power

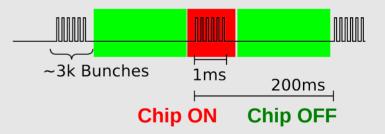

#### Low power consumption

- Constraint: ~25uW / channel

#### Met by:

- Intrinsic low power design

- Power gating (1% duty cycle)

#### Main constraint in design!

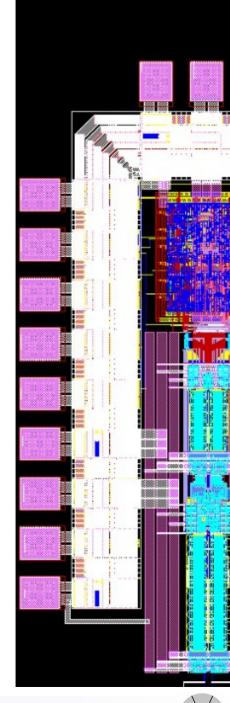

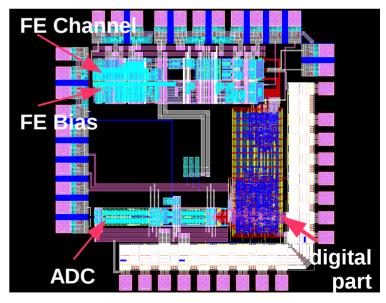

### Development of 'KLauS'

- Analog front-end,

- ADC for digitization,

- digital parts ...

- $\rightarrow$  Multi channel ASIC planned for 2016

### All blocks optimized for

- Low power consumption (Power pulsing capable)

- Different requirements for Calibration [small signals, low noise]

- and 'Physics' [Large dynamic range]

[KLauS2.0 – analog only]

[KLauS3.0 – frontend & ADC]

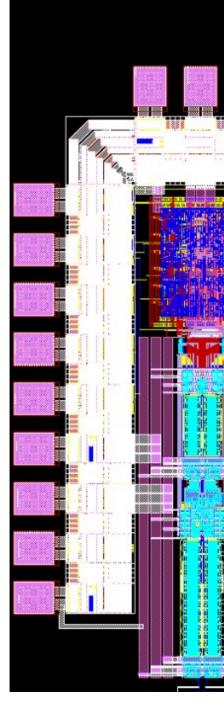

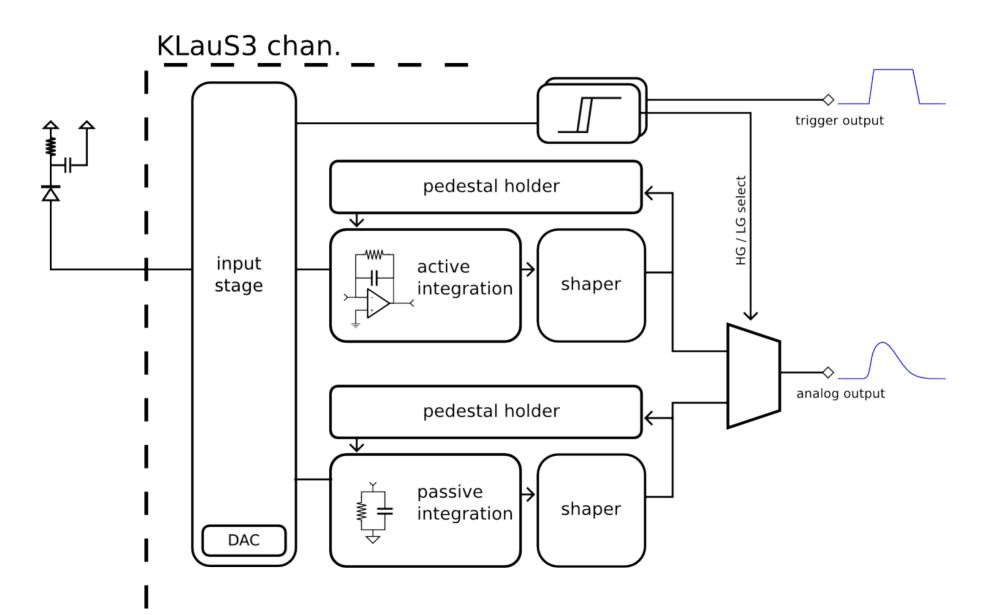

## KLauS3 front-end: Blocks

#### Input stage:

Low input impedance SiPM bias voltage DAC

#### High gain stage:

Single pixel spectra O(10ths of pixels) Low noise

### Low gain stage:

Full SiPM dynamic range

### 2 Trigger branches

Minimize power consumption Power gating Dual supply scheme

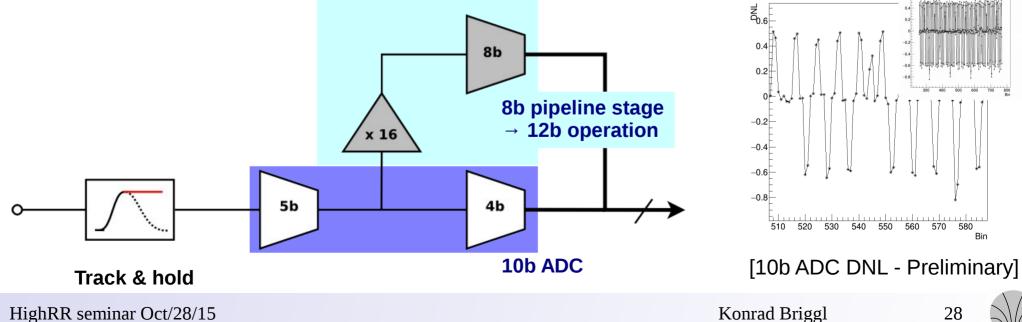

### ADC for KLauS

1 ADC per front-end channel  $\rightarrow$  Development of low power ADC

Two operation modes: SiPM gain calibration – 12bit resolution MIP quantization – 10bit resolution

Maximum Event rate: 3MHz

## Summary

The CALICE collaboration is developing **calorimeters for a future linear collider** Detector optimization for Particle flow algorithms

- High Granularity

- AHCAL concept: SiPM + Scintillator based hadronic calorimeter

### Scalable prototype

• New challenges for active elements:

Stronger focus on scalability of production,

testing and assembly

• Development of readout electronics

Fully integrated

Very low power consumption

### - Backup -

### **CALICE AHCAL Contributors**

### Google

## Engineering prototype – Current state

#### **Testbeam 2015 at CERN SPS**

- Steel stack

- 2x ECAL layers

- 8x 30x30cm HCAL layers

- 4x 60x60cm HCAL layers

- Pions runs

- Muons

# Evolution of tile designs

Simplified assembly Mechanical alignment

### 1st design for tech. prototype

Fiber-less coupling, Injection molding

Fiber-less coupling, Tighter tolerances

## After the tile production...

### **Quality assurance**

SiPM functionality test

Tile characterization

### Assembly in larger modules:

Precise tile placement

Soldering

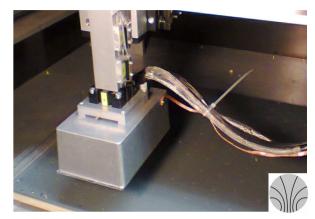

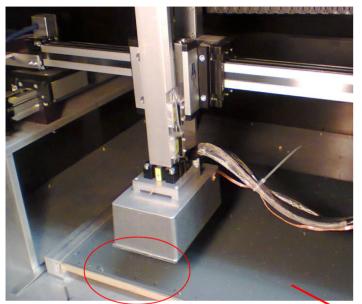

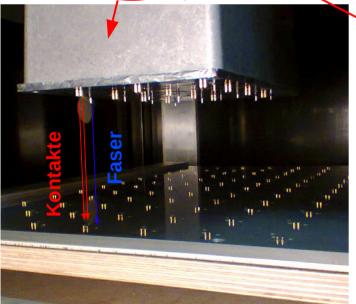

## Automated characterization of Tiles

- Fast measurement → Only basic parameters measured

- Parallelization (12 channels)

- UV Laser instead of source

- Currently 2min for 12 tiles, then repositioning

- Automatic electronic and optical connection

- $\approx$  1500 tiles characterized for testbeam prototypes

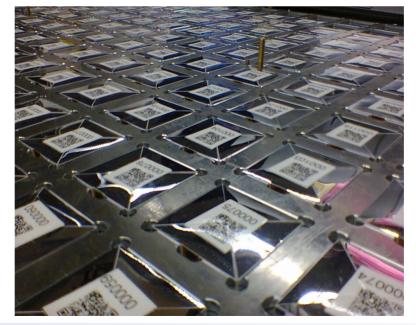

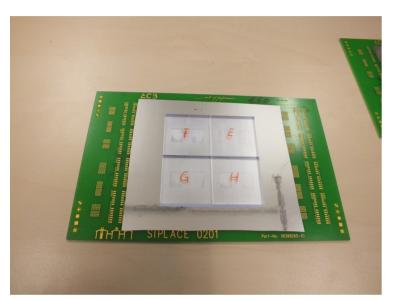

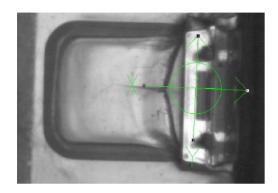

## Automated assembly of HBUs

- Large number of components require automatic Placement and soldering of Tiles to HBU

- Precise & fast placement

- Fast gluing procedure

- $\rightarrow$  Possibility to place tiles without mechanical alignment

# Automated assembly of HBUs

Melted tile dimple after first soldering tests

Multi point head for selective soldering

- Different options for soldering technology

- Challenge: Soldering of (very) heat sensitive components

- Automation poses additional requirements on PCB design

- Wave soldering:

- Heat protecting mask to avoid heating up other components

- Selective soldering

- Slower, possible speed up by multi point head

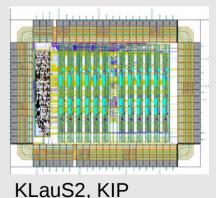

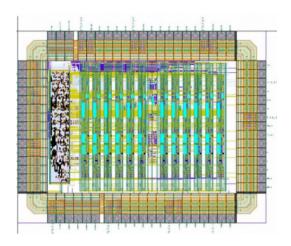

## **KLauS Development status & Plans**

#### KLauS development status

'KLauS2' : AMS 350nm Technology [Design: W. Shen, 2010]

→ Validation of input stage topology

'KLauS3.0a/b' : UMC 180nm (March/15 & May/15)

→ ADC [Design: W. Shen; Layout: H. Chen]

$\rightarrow$  New front-end [Design: K. Briggl]

#### Further development plans

Until Summer 2016 Multi-channel readout ASIC Combined front-end; ADC; basic TDC blocks

[KLauS2.0 – analog only]

[KLauS3.0 miniASIC – front-end & ADC]

#### Front-end: block level schematic

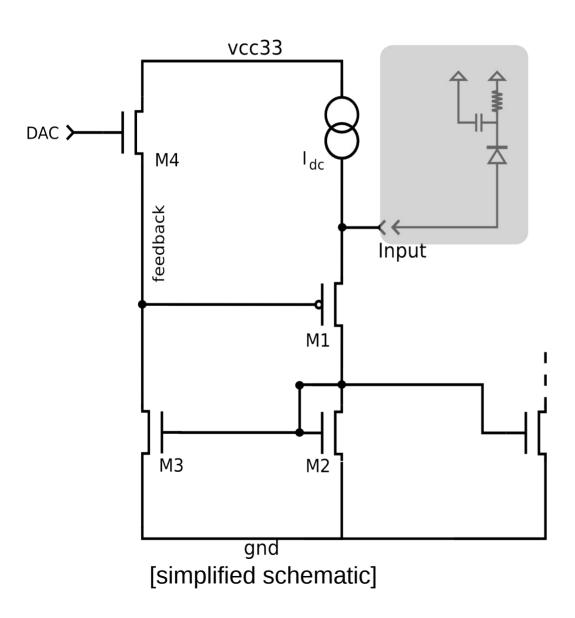

# Input stage topology

Common gate & current feedback

$$\mathbf{R_{in}^{DC}} = \frac{1}{\mathbf{g}_{m1}} - \left(\frac{\mathbf{g}_{m3}}{\mathbf{g}_{m2}} \times \frac{1}{\mathbf{g}_{m4}}\right)$$

Nominal input impedance  $\sim 50\Omega$

150uA bias current @ 3.3V

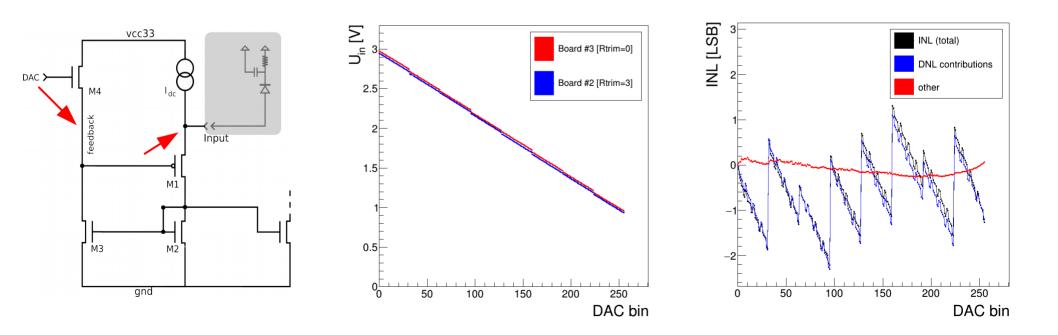

#### SiPM Bias voltage tuning

['DAC' → 'feedback' → input] ~ 2V tuning range Low power 8bit DAC 2nA / LSB

#### Power gating compatible

Small DC input voltage change in low power mode

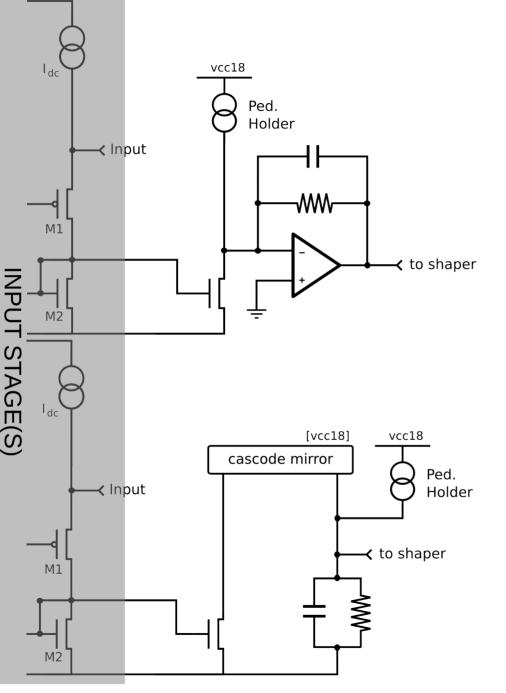

# Charge integration

#### **High gain stage:** Active integration scheme for small signals on single pixel level Miller-opamp with 400MHz GBW

Low gain stage: Passive integration for large signals input stage mirror: regulated cascode pmos integration mirror: low voltage cascodes

Pedestal stabilization DC feedback of channel output Using subthreshold Amplifiers

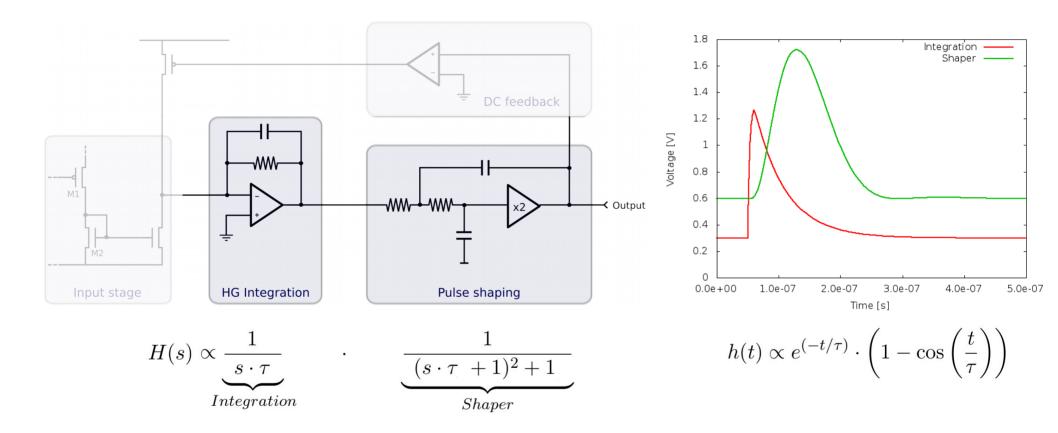

### Shaper and channel pulse response

Shaper: Sallen-Key topology  $\rightarrow$  pair of complex poles

Same time constants for integration & shaper  $\rightarrow$  Semi gaussian pulse, small undershoot

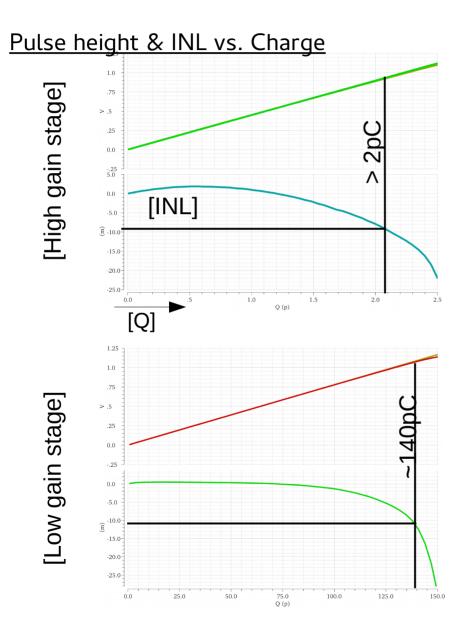

# Simulations: Linearity & Noise

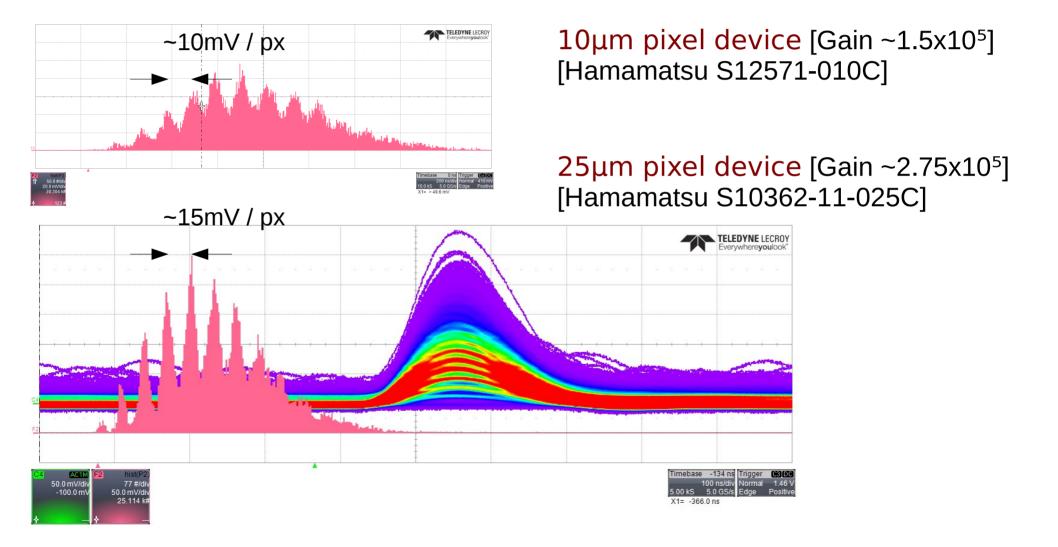

High gain stage

Design goal:

Allow decent SNR for very low gain Sensors

[e.g. Hamamatsu 10μm series, Gain ~10<sup>5</sup>]

Expected ENC < 3fC</li>

→ Single pixel S/N > 5

Dynamic range ~ 2pC @ INL < 1% FSR [ $\approx$  135px for 10 $\mu$ m ;  $\approx$ 34px for 25 $\mu$ m MPPC]

<u>Low gain stage</u> Exploit SiPM dynamic range ~ 140pC @ INL < 1% FSR

Moderate SNR requirements Equivalent noise charge ~ 50fC

#### Front-end measurements: SiPM bias voltage DAC

Measure DC voltage at SiPM input

2V tuning range achieved

Analysis of Nonlinearity sources

Main source is DNL (3 LSB) [Layout update in next submission] Other sources negligible & as expected

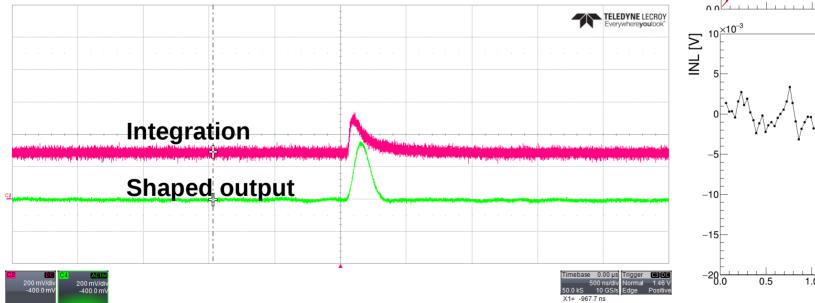

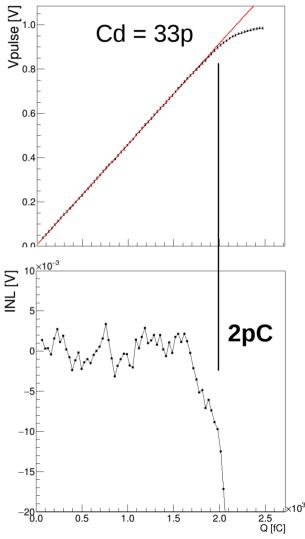

## Front-end measurements: Charge injection

Test of high gain stage

- Pulse shape after integration & shaping

- Dynamic range

Sufficient for single pixel spectra

Preliminary bias settings

Limited by off-chip driver dynamic range

# Front-end measurements: test with sensors

Two SiPM models tested

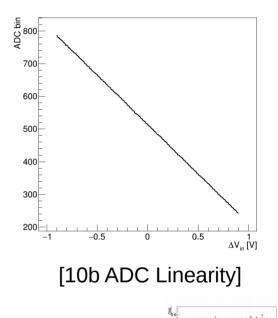

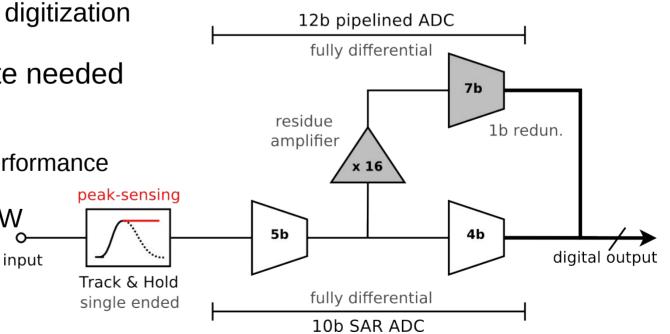

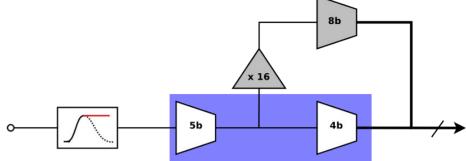

#### SAR ADC development for KLauS

1 ADC per front-end channel

$\rightarrow$  Development of low power ADC

Two operation modes: MIP quantization – **10bit resolution** 5+4bit SAR ADC

SiPM gain calibration – **12bit resolution** Additional pipelined stage Residual amplification & digitization

Relatively low Sampling rate needed Peak voltage digitization validated up to 3MHz No constraint on dynamic performance

DC Power consumption  $< 1 \text{mW}_{\odot}$

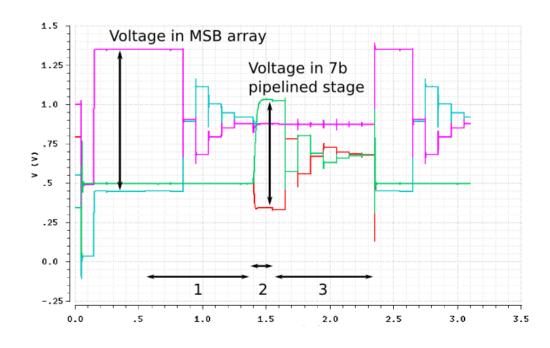

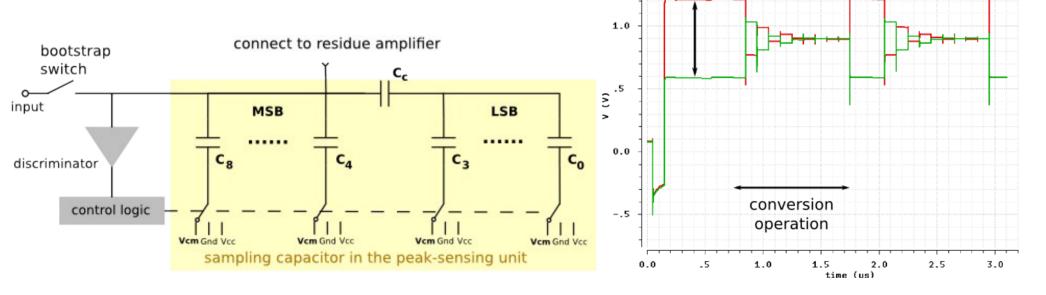

### ADC – 10bit main SAR

Voltage in MSB array

#### SCA:

5+4bit binary MIM capacitor array Unit capacitor ~ 34fF

#### **Other blocks:**

Dynamic comparator Bootstrap sampling switch Control logic in digital part

1.5

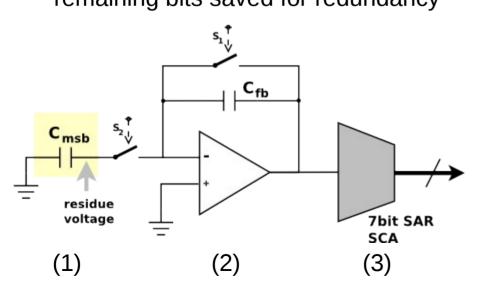

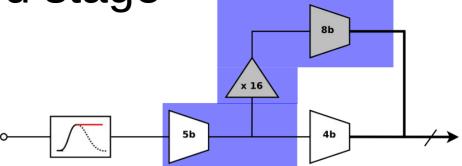

## ADC: Pipelined stage

12b resolution operation mode for SiPM spectrum digitization

#### 3 digitization steps:

- (1) 5b digitization in main SAR

- (2) Amplification of residual error Fully differential folded cascode amplifier

- (3) 8b digitization in pipelined stage

5+4 split MIM capacitor array

Unit capacitor ~ 34fF

remaining bits saved for redundancy