# **Resistive coatings**

### P. Colas, CEA/Irfu Saclay

**Definition of surface resistivity** Practical examples of coating applications **Measurement techniques Applications of resistive coatings** Charge dispersion Spark mitigation protection **Drawbacks** Characterization (uniformity, robustness,...) New ideas

'Wallpaper' ASIP photo-cell (EPFL/MIT)

## Surface resistivity

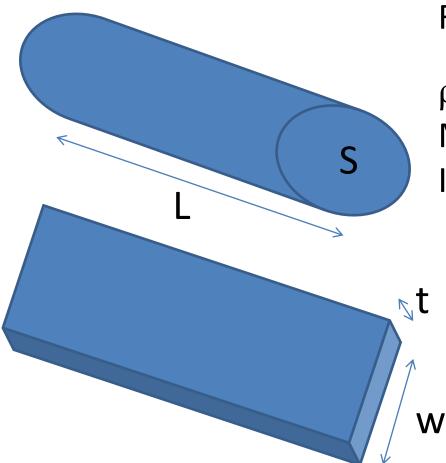

$R = \rho L/S$

$\rho~$  : bulk resistivity Metal : 10<sup>-6</sup> - 10<sup>-5</sup>  $\Omega.cm$  Insulator >10<sup>17</sup>  $\Omega.cm$

R = ρ L/wt Flat layer: t small Square L=w Surface resistivity R= ρ/t Units : Ohm per square

# Measurement techniques (1)

Cut a long band of resistive. Hold it both ends with conductive adhésive on an insulating surface, measure the resistance and divide by the number of squares L/w.

# Measurement techniques (2)

Circular probe (for example ETS model 803B)

Measure the resistance between 2 rings

$\rho_{s} = \frac{(D_1 + D_2)}{(D_2 - D_1)} \pi R_m \text{ Ohms/sq}$

$D_1$  = Outside Diameter of inner ring  $D_2$  = Inner Diameter of outer ring  $R_m$  = Measured resistance in ohms

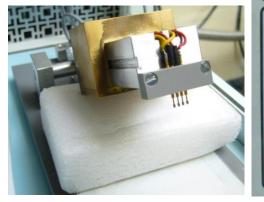

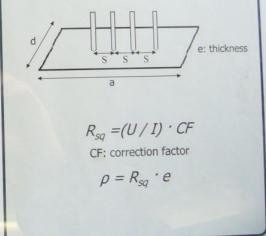

### Measurement techniques (3)

#### Four-point probe

Necessary for uniformity measurements, but might scratch the layer

#### Goal of the measurement

To determine the sheet resistance  $R_{sq}$  and the electrical resistivity  $\rho$  of a thin-film without any influence of the contact resistance, which becomes significant for materials with a high conductivity.

#### **Correction Factor**

The need for correction factors is caused by the proximity of a boundary (the sample's edges) which limits the possible current paths in the sample. This correction factor depends on the dimensions of the sample:

| d/s  | a/d = 1 | a/d = 2 | a/d = 3 | a/d = 4 |

|------|---------|---------|---------|---------|

| 1.0  |         |         | 0.9988  | 0.9994  |

| 1.25 |         |         | 1.2467  | 1.2248  |

| 1.5  |         | 1.4788  | 1.4893  | 1.4893  |

| 1.75 |         | 1.7196  | 1.7238  | 1.7238  |

| 20   |         | 1.9454  | 1.9475  | 1.9475  |

| 2.5  |         | 2.3532  | 2.3541  | 2.3541  |

| 3.0  | 2.4575  | 2.7000  | 2.7005  | 2.7005  |

| 4.0  | 3.1137  | 3.2246  | 3.2248  | 3.2248  |

| 5.0  | 3.5098  | 3.5749  | 3.5750  | 3.5750  |

| 7.5  | 4.0095  | 4.0361  | 4.0362  | 4.0362  |

| 10.0 | 4.2209  | 4.2357  | 4.2357  | 4.2357  |

| 15.0 | 4.3882  | 4.3947  | 4.3947  | 4.3947  |

| 20.0 | 4.4516  | 4.4553  | 4.4553  | 4.4553  |

| 40.0 | 4.5120  | 4.5129  | 4.5129  | 4.5129  |

| 00   | 4.5324  | 4.5324  | 4.5325  | 4.5324  |

#### Principle

The probe consists on two current carrying probes (1 and 4), and two voltage measuring probes (2 and 3).

### Measurement techniques (4)

Use the saturation of the rate on a counting chip (GridPix) in a X-ray gun (M. Lupberger, H. van der Graaf, see talk by Fred Hartjes)

# Applications of resistive coatings

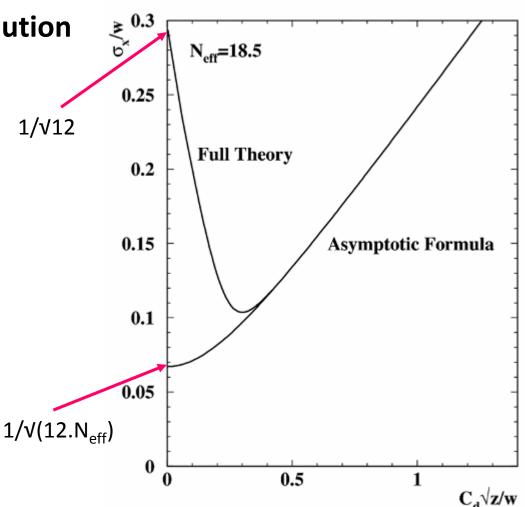

### Analytical theory of resolution

In a MPGD (especially Micromegas) with pads or strips, the avalanche is typically 15-20 micron wide. Charge sharing between pads is only due to diffusion in the drift gas

Taking into account ionization fluctuations, gain fluctuations, and the finite pad size, the resolution of a MPGD as a function of z (the drift distance, is given by the following plot

D. Arogancia et al., NIM A602 (2009) 603

# Applications of resistive coatings Charge spreading

Need to spread the charge to improve resolution.

Insulator + resistive coverlay = resistive-capacitive continuous network. (M. Dixit et al.)

(1)

$$\frac{\partial \rho}{\partial t} = h \left( \frac{\partial^2 \rho}{\partial x^2} + \frac{\partial^2 \rho}{\partial y^2} \right),$$

where h = 1/RC.

The solution to Eq. (1) for a resistive anode of finite size is an infinite Fourier series. A closed form solution becomes possible, however, for the case of a delta function point charge deposited at x = y = t = 0 and when the edges are at infinity:

$$\rho_{\delta}(x, y, t) = \left(\frac{1}{2\sqrt{\pi th}}\right)^2 \exp\left[-\left(x^2 + y^2\right)/4th\right].$$

(2)

For t ~shaping time, r~sqrt(2t/RC) Should be close to the pad size.

```

M. Dixit, A. Rankin, NIM

A 566 (2006) 28

```

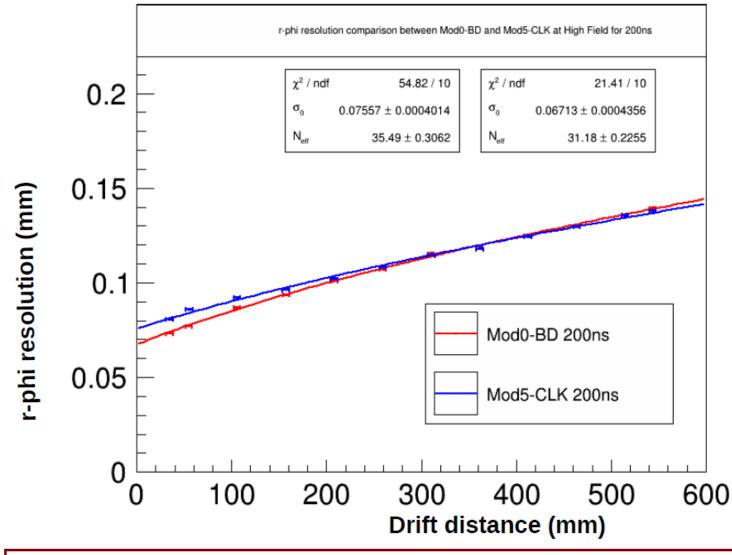

# r-phi resolution comparison between a BD and a CLK (mod5) is shown. The two are very comparable.

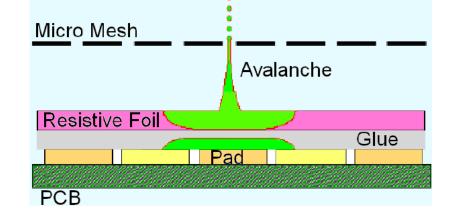

# Applications of resistive coatings Spark mitigation

- The avalanche charge is kept locally for some time

- This lowers the potential locally

- This in turn lowers the gain and avoid the Rather limit to be attained

- Moreover, as the charge goes to ground through a resistance, this limits the current through the preamplifiers, protecting them

- You can also pattern resistors in your PCB (see Max Chefdeville's talk)

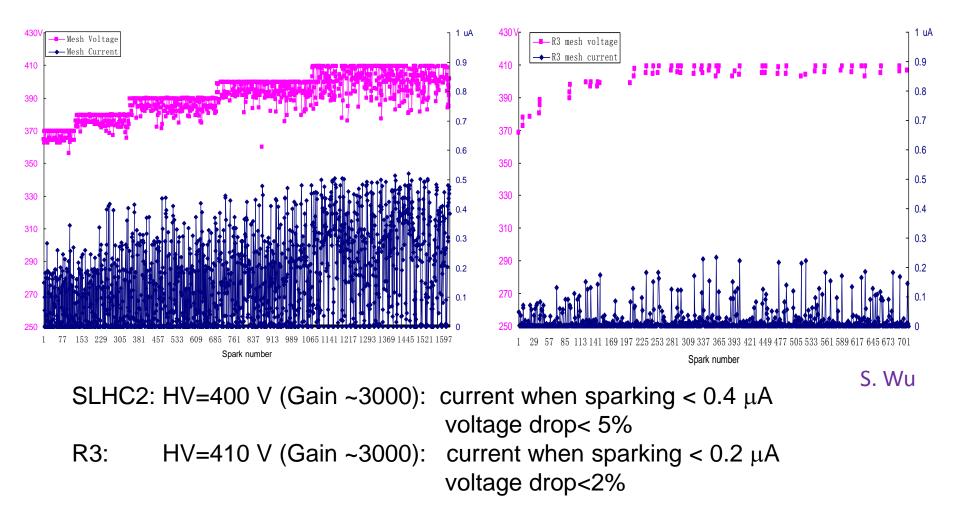

### Different sparking behaviours of standard and resistive detector:

### Standard SLHC2(@10KHz):

Resistive R3(@wide beam,15KHz):

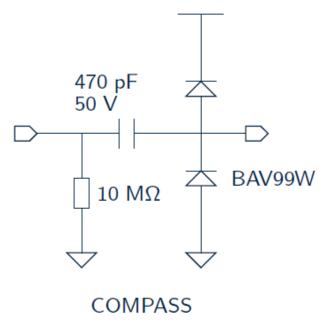

## Spark protectection

Protection diodes, resistors and capacitors no longer needed : this saves space on the FE boards

# Resistive coating technologies

- Sheldal film + cermet (Al Si) (Madhu Dixit)

- Resistive paste or ink (Rui de Oliveira, Imad Laktineh, Nick Lumb, José Répond)

- Spray of carbon powder in glue (G. Mikenberg)

- Kapton with Diamond-like Carbon by sputtering (see Atsuhiko Ochi's talk)

- aSiH deposition (Nicolas Wyrsch)

- Several presentations in WG1

### Simulating and understanding SiProt

- A single spark kills a TimePix chip

- High current, hot plasma -> destroys circuit

- A sufficiently thick SiProt layer reduces and softens the sparks

#### • How protection works?

- Allows charge to stay over the pad, lowering the local potential

- Limits the current thru the amplifier

- Protects mechanically

- Avoids points, softens the surface?

#### • Any damage to the signal?

- Amplitude loss?

- Charge sharing with neighbouring pads?

- Short-circuit of the amplifiers

- Introduces dead time?

### TO ANSWER, NEED A SIMULATION

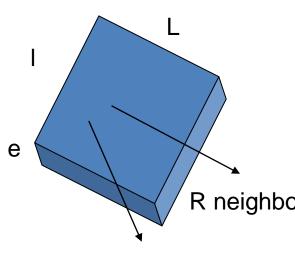

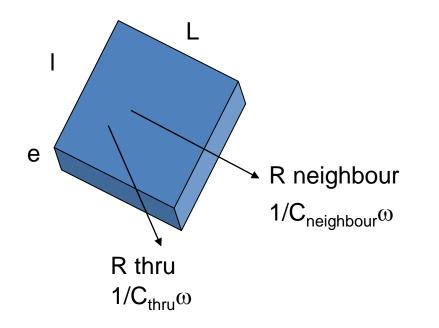

# Orders of magnitude

R thru

$$\begin{split} &\mathsf{R}_{\text{neighb}} = \rho \; \text{L/el} = \rho/\text{e} \; \text{for square pads} \\ &\mathsf{For} \; 10 \; \mu \; a\text{Si}, \; \rho {=} 10^{11} \; \Omega.\text{cm}, \; \text{R} {=} 10^{14} \; \Omega/\text{square} \\ &\mathsf{R}_{\text{thru}} = \rho \; \text{e/Ll} \sim 0.04 \; 10^{14} \; \Omega \\ &\mathsf{R}_{\text{neighb}}/\mathsf{R}_{\text{thru}} = \mathsf{L}^2/\mathsf{e}^2 \end{split}$$

e<<L to avoid spreading the charge by side conductivity. The charge preferentially escapes thru the pad, but with an extremely high resistance.

$C_{\text{neighb}} = \epsilon_r \epsilon_0 \text{ Le/I} = \epsilon_r \epsilon_0$  /e for square pads

$C_{thru} = \varepsilon_r \varepsilon_0 Ll/e$  (note  $\varepsilon_r \sim 11$  for Si)

The influence acts preferentially thru the pad if L>>e

Also  $R_{thru} >> 1/C\omega$  to leave the induced signal (OK with 10<sup>11</sup>  $\Omega$ .cm within 3 orders of magnitude for 10 ns signals)

Equivalently, RC time constant >> 10ns

#### The signal is fully capacitive

Charge injected in the middle of the pad

| thickness | Signal frac. on<br>central pad | Signal frac. on<br>central pad |

|-----------|--------------------------------|--------------------------------|

|           | (Full pads)                    | (cross)                        |

| 10 µ      | 94 %                           | 76 %                           |

| 15 µ      | 83 %                           | 57 %                           |

| 20 µ      | 70 %                           | 44 %                           |

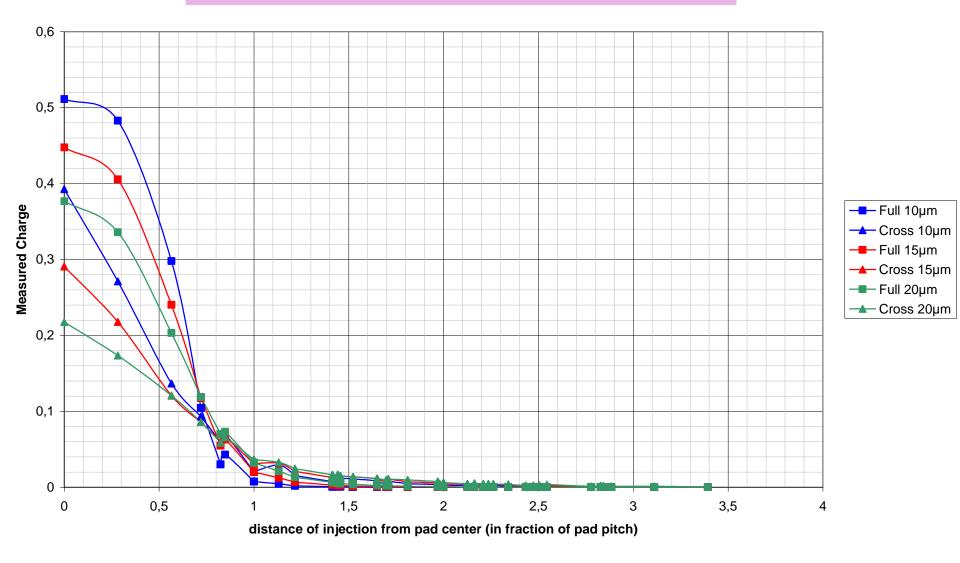

### Pad Response Function

## Drawbacks

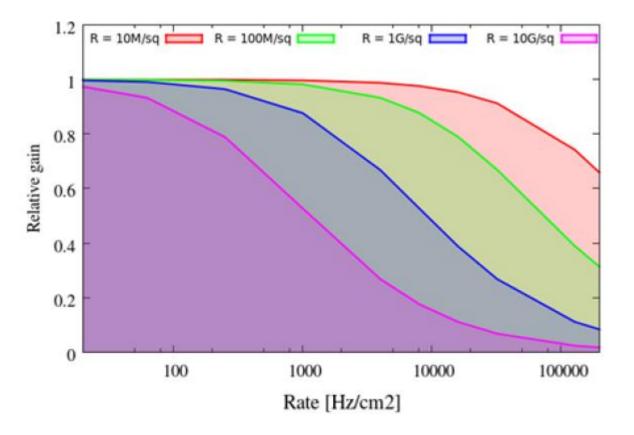

Resistive layers slow down the detector, as the charge remains some time on the anode. They degrade slightly the rate capability.

Simulation by J. Galan

D. Attié et al., JINST (2013), 'A piggyback Micromegas'

For 10 M $\Omega$ , there is a 20% gain drop at 100 kHz/cm2

## **New Ideas**

Use photo-lithographic and electrolithographic techniques to make patterned protection layers, burried resistors, on pixel chips