## LHCb upgrade: status and milestones

### G. Passaleva

On behalf of the LHCb collaboration

LHCC meeting December 1, 2015

CALORIMETER

VELO

# Milestones

**EDR**

Sensor and thinned bump bonding EDR

Front-End ASIC

sensors

| UPSTREAM TRACKER                                                                                | SALT Chip             | SALT EDR                               | Jun-15 | 22/06/2015 |            |  |

|-------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------|--------|------------|------------|--|

| UPSTREAM TRACKER                                                                                | FLEX cables           | FLEX CABLE EDR                         | Jun-15 | 23/06/2015 |            |  |

| UPSTREAM TRACKER                                                                                | Staves                | Stave EDR                              | Jun-15 | 19/06/2015 |            |  |

| SCIFI                                                                                           | Fibres, mats, modules | Joint EDR                              | Jul-15 | 16/07/2015 | Several    |  |

| UPSTREAM TRACKER                                                                                | Sensor                | SENSOR EDR                             | Jul-15 | 18/06/2015 |            |  |

| UPSTREAM TRACKER                                                                                | ELECTRONICS           | PEPI/LV EDR                            | Jul-15 | 23/06/2015 | internal   |  |

| VELO                                                                                            | electronics           | ASIC EDR                               | Aug-15 | 29/06/2015 | milestones |  |

| RICH                                                                                            | MaPMT                 | Place MaPMT order and start production | Nov-15 | 01/11/2015 | also       |  |

| VELO                                                                                            | cooling substrate     | Cooling Substrate EDR                  | Nov-15 | 25/11/2015 |            |  |

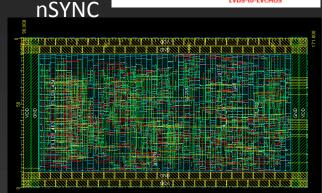

| MUON                                                                                            | nSYNC                 | EDR                                    | Dec-15 | 24/11/2015 | achieved   |  |

| MUON                                                                                            | nODE                  | EDR                                    | Dec-15 | 24/11/2015 |            |  |

| MUON                                                                                            | nPDM                  | EDR                                    | Dec-15 | 24/11/2015 |            |  |

| MUON                                                                                            | nSB                   | EDR                                    | Dec-15 | 24/11/2015 |            |  |

| VELO                                                                                            | electronics           | hybrid EDR                             | Dec-15 | 17/11/2015 |            |  |

| <ul> <li>A set of important EDRs took place since last meeting, will discuss some of</li> </ul> |                       |                                        |        |            |            |  |

May-15

Jun-15

24/04/2015

01/06/2015

them in this report

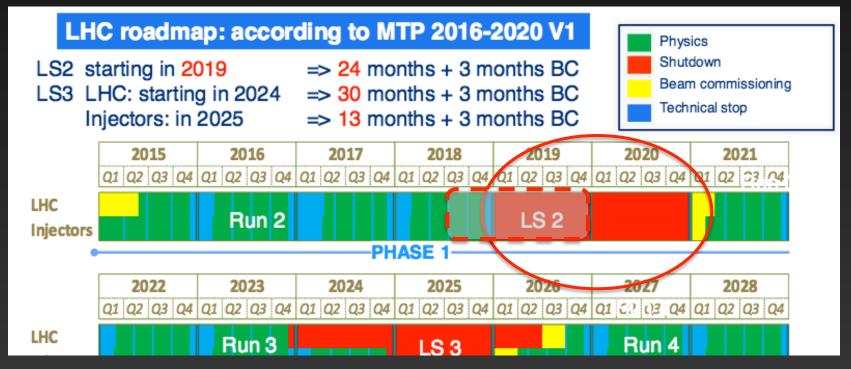

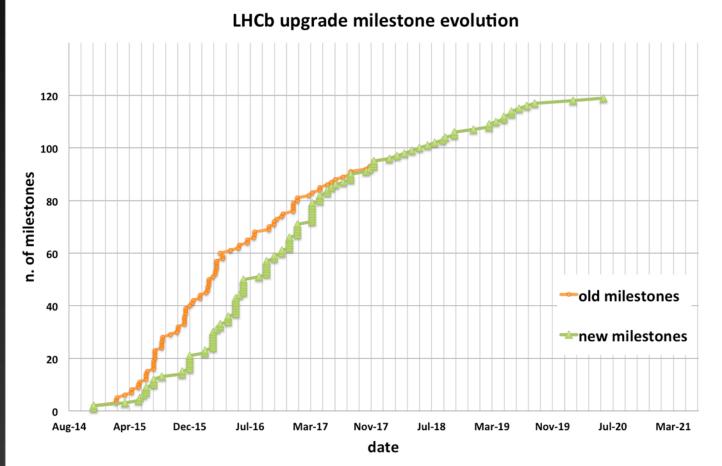

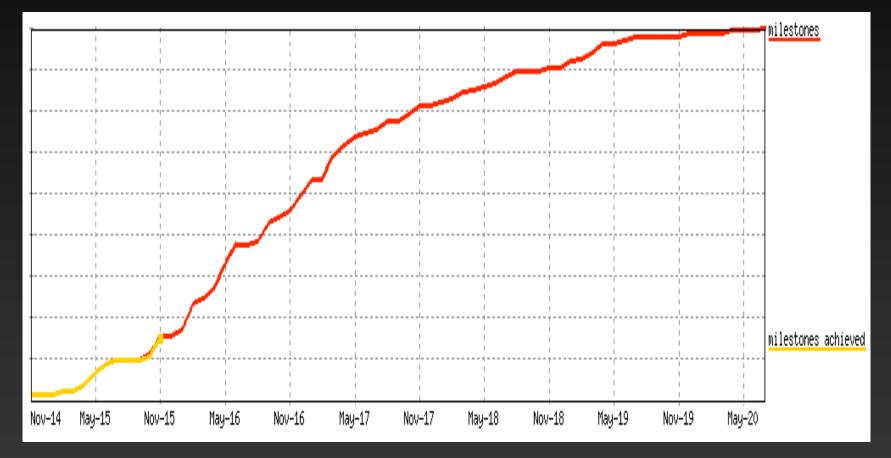

As discussed at previous LHCC meetings, a revision of the milestones have been made. Two main drivers for this revision:

#### New LHC schedule

Two main drivers for this revision:

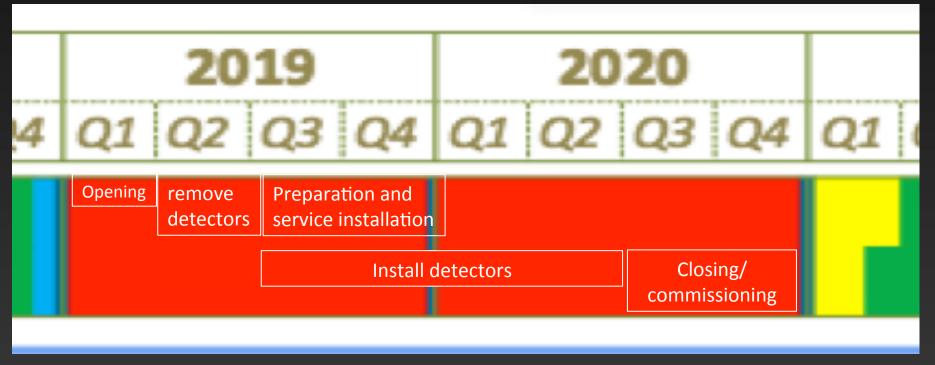

2. Preliminary installation schedule (R. Lindner, Technical Coordinator)

- Modifications wrt previous schedule take into account:

- ★ New LHC schdule (+1 year)

- ★ Preliminary installation schedule by the technical coordinator

- **★** Better and more realistic assessment of production schedule after the first round of EDRs → additional milestones!

- Milestones shifted generally by 3-7 months (reflecting the new LHC schedule)

- Globally the upgrade project fits well in the new LHC schedule

# Milestone status

## Progress report: UT

#### Introduction

Review Committee

Support Documents

**Timetable**

My Conference

My Sessions

My Contributions

Registration

Participant List

Extra Files

Videoconference Rooms

#### Introduction

#### Review Sessions (June 18-23, 2015)

The engineering design reviews of key components of the UT tracker for the LHCb upgrade will take place at CERN, in the rooms listed below. Vidyo connection will be provided. There will be 4 sessions:

- 1. June 18 (Thursday), Silicon sensor review, in room CERN-4-3-004

- 2. June 19 (Friday), Stave construction review, in room CERN 14-4-030

- 3. June 22 (Monday), SALT8 ASIC review, in room CERN 4-S-030

- 4. June 23 (Tuesday), Electronics review, in room CERN 4-S-030

#### Links to formal reviews:

- Nov 14-15, 2013, UT conceptual design review http://utreview2013.syr.edu/.

- Oct 20-21, 2014, UT Electronics review https://indico.cern.ch/event/334042/.

Reference material, such as specifications and relevant technical reports can be found in Support Documents page.

#### Four EDRs in June:

- Silicon sensors

- Staves

- SALT ASIC

- Electronics/FLEX cables

- Reports from the reviewers received

- Generally positive

- Main remarks and actions taken discussed in the following

## Progress report: UT sensors

#### Remarks on:

- top biasing: test long term stability and radiation effect

- embedded pitch adapter: test charge collection efficiency, cross-talk, radiation effects

Top side bias

#### Actions:

- Irradiated sensors with top side biasing tested in July test beam; more data acquired in September and November.

- Back side biased sensors will also be irradiated for comparison

Embedded pitch-adapters

#### **Actions:**

- two designs tested

- Irradiated sensors with different configurations tested in July test-beam

- Charge collection lab tests with laser ongoing

test-beams in September and November

PRR: Q1 2016

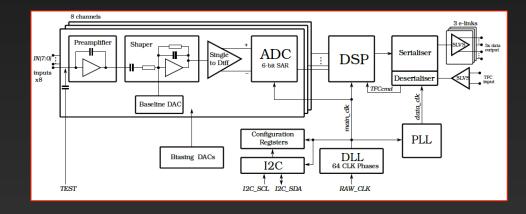

# Progress report: UT SALT ASIC

- In depth review of SALT8 version by a team of TSMC technology experts (mainly from CERN)

- 9 chips submitted (full SALT8 plus building blocks: ADC, PLL, DLL, ...)

- Many remarks, most of them will be incorporated in a second version of SALT8

- Tests of first version still ongoing, test infrastructure developed in parallel

#### Schedule:

- ★ SALT8 V2 submission: end 2015 🗸

- ★ First version of SALT128: spring 2016

- ★ Engineering run: end 2016

- ★ Production: Q2 2017

Very aggressive/critical schedule. Test infrastructure crucial!

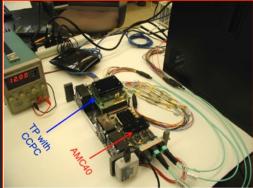

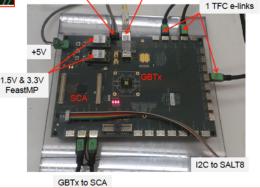

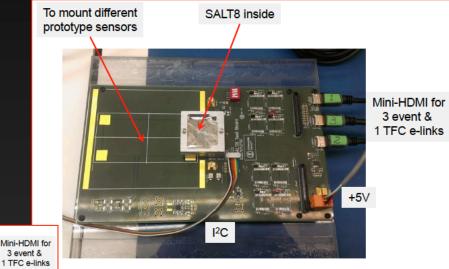

# **Progress report: UT SALT ASIC tests**

- Test setup of SALT chip is progressing

- Long learning curve and complex setup

MINI-DAQ board

(VTRx)

I2C for

SALT test board board

VLDB board (GBTX + optcal links)

01/12/2015 LHCC meeting G. Passaleva 11

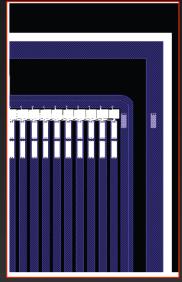

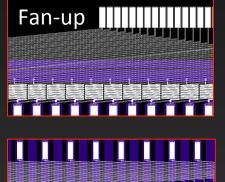

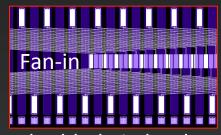

### Progress report: UT FLEX cables, power distribution, staves

### FELX cables

First batch of cables tested in Milano, Syracuse and Maryland.

reviewers already implemented in a new versions made at CERN

Test results positive. Remarks by

Another manufacturer identified in USA

PRR: Q3 2016

and now under test

01/12/2015

Power distribution

Very complex layout. Constraints come from the amount of material in the sensitive area.

Concerns were raised about CM noise due to grounding and coupling of conducting planes

Action: An accurate test setup is already in place in

Maryland and all the aspects of the layout are being extensively tested

PRR: Q2 2017

LHCC meeting

Staves

Design well advanced also concerning the integration with the supporting infrastructure

Construction will start soon!

Reviewers recommended extensive thermal and mechanical stress tests during the various phases of the construction.

Action: final design incorporates rev. suggestions;

construction procedure will incorporate some of the proposed checks

G. Passaleva 12

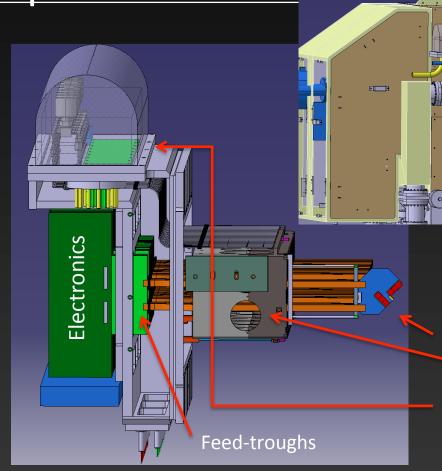

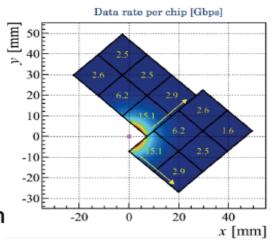

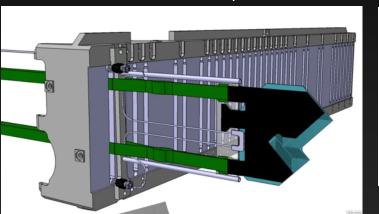

Progress report: VELO

### INFN

#### Four EDRs since June

- Sensors

- VELOPIX ASIC

- Hybrid and electronics

- Microchannel cooling

### Mechanics workshop

All aspects of VELO mechanics reviewed

EDR: end 2016

VELO mechanics

Above: the hood with

electronics and services

Left: detail of:

modules,

base

Feed-throughs

tertiary vacuum for

safety valves

01/12/2015

LHCC meeting

G. Passaleva 13

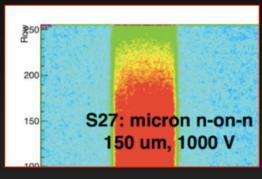

## Progress report: VELO sensors

Main remarks concerning: use of parylene coating for HPK p-on-n sensors which prevents bias at 1000 V on non uniformly irradiated sensors; hot spots on Micron sensors; rounded corners. Recommendations were made on the final design (thickness, pixel size etc.)

Intense test beam activity to face the open problems

A pre-series with rounded corners is in

preparation

sensor T6 Irradiated at KIT HPK parylene Coated sensor T21 Irradiated at KIT MicronN-on-N sensor T2 Irradiated at KIT HPK parylene Coated sensor S4 Irradiated at KIT HPK parylene Coated sensor S22 Irradiated at JSI annealed sensor S27 Irradiated at JSI N-or cron Annealed on N Micron GR 450 sensor S34 Before Irrad NonN Micron GR 250 sensor T1 Irradiated at KIT HPK sensor S23 Irradiated at JSI N On P Micron sensor S6 Irradiated at JSI Coated HPK 39um sensor S24 Irradiated at JSI N On P Micron

## Progress report: VELOPIX

| Pixel size                          | 55 μm x 55 μm                             | Operational temperature range                                                                                       | -40 'C to + 60'C                            |

|-------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Pixel matrix                        | 256x256                                   | Startup temperature range                                                                                           | -60 'C to + 60'C [note 9]                   |

| Chip size                           | 14 mm x ~16 mm [note 1]                   | Power consumption                                                                                                   | < 3W/ full chip                             |

| Input charge                        | Optimized for e- (h+ if possible)         | Radiation hardness                                                                                                  | > 400 MRad [note 10]                        |

| Input coupling                      | DC                                        | SEU protection                                                                                                      | ves [note 11]                               |

| Leakage current compensation        | 20 nA per pixel [notes 2-4]               | Timing and fast control (TFC)                                                                                       | See note 12                                 |

| Input referred noise (ENC)          | σ < 100 e- (Cdet < 50 fF, planar silicon) |                                                                                                                     | Compatible with LHCb ECS: e.g. SPI over     |

| Minimum threshold, full chip        | <800 e-                                   | Siew control                                                                                                        |                                             |

| Threshold spread after equalisation | σ < 30 e-                                 | Monitorifications  Noniterifications  Specifics counters Fast (data) reset / clear buffers lamp pad window diameter | GBT [note 13]                               |

| Timewalk                            | < 25 ns for 1 ke-                         | MonitoritiCation                                                                                                    | Voltage, temperature                        |

| Time over Threshold                 | No, binary readout, TeT only for          | COCUMUS counters                                                                                                    | see note 14                                 |

|                                     | monitoring [note 5]                       | X Organt-end disable                                                                                                | yes (shutter-like mode), see TFC            |

| ToT: pixel to pixel spread          | <5%                                       | Fast (data) reset / clear buffers                                                                                   | yes                                         |

| Average max. hit rate               | > 590 (880) MHits/s (note 6)              | Jump pad window diameter                                                                                            | 12 μm, like Timepix3                        |

| Allowed hit loss at max. rate       | 2.10 (2.10.10.1)                          | 10 signal levels                                                                                                    | SLVS                                        |

| Technology                          | 130 nm CMOS                               | Global (trigger) OR                                                                                                 | Yes                                         |

| System clock frequency              | 40 MHz                                    | Calibration                                                                                                         | Internal and/or external testpulse (1-2 ns  |

| Output data format                  | Data-driven, zero-suppressed, grouping of |                                                                                                                     | time resolution), internal delay in case of |

|                                     | hits to reduce bandwidth (superpixel      |                                                                                                                     | external TP.                                |

| Data output                         | concept) At least 4 GWT links [note 8]    | Power on reset (pin)                                                                                                | Yes                                         |

| Data Output                         | reference a data mines [more of           | tomer our coor (pm)                                                                                                 |                                             |

- ◆ Floorplan

- High speed output circuit

- ◆ ECS/TFC

- ◆ analog front end

- digital architecture

All elements put in place to launch

a summer of verification before first submission

End of 2015

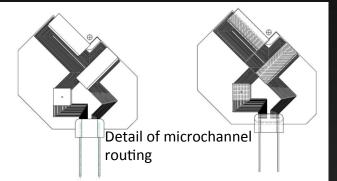

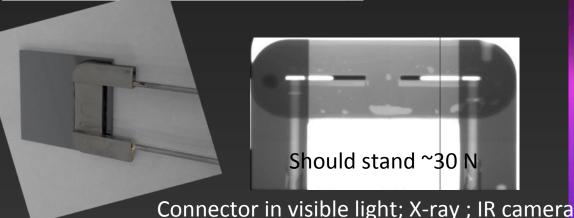

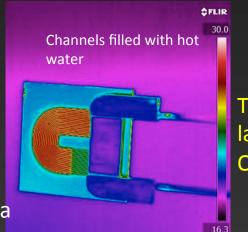

### Progress report: Microchannel cooling EDR

400  $\mu m$  thick silicon substrate; 200x120 um<sup>2</sup> channels; CO<sub>2</sub> pressure ~20 bar

Many challnging issues

Safety is a paramount priority

Some concerns on the connector design and mounting procedure

Tender to be launched in Q1 2016

01/12/2015 LHCC meeting G. Passaleva 16

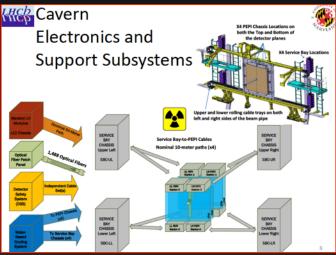

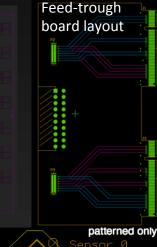

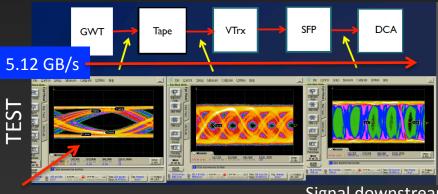

### Velo electronics

Key blocks of the electroncis chain were reviewed

- Opto-power board (OPB) & Feedthrough boards.

- Velopix hybrid.

- Flex tapes (data & control).

No major problems were spotted by the reviewers but high speed data transmission is challenging!

**OPB** layout

GWT signal (with known jitter problem)

Signal downstream the optical fiber

G. Passaleva 17

01/12/2015

LHCC meeting

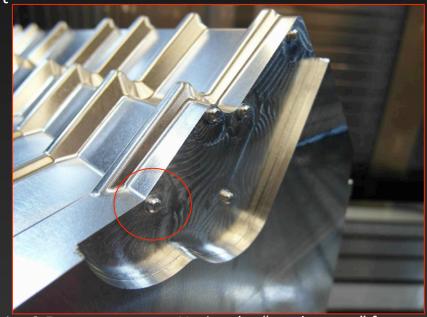

## Velo RF foil

No showstopper seen so far, but several warnings; structure of the box (when closed) gives a Im(Zeff/n)

~4.7 mOhm (while full LHC is 90 mOhm). This can contribute to longitudinal instabilities. However, the

small beta\* at the VELO mitigates the effect. New measurements indicate that instabilities are well

understood under control. No major problems even at

HL-LHC intensities

- First half-sized prototype at Nikhef finished

- Machined from a full Al block ~500x300x300 mm³

- nominal thickness: 500 micron

- deviations from nominal geometry <100 um

- Leak tight

- half-size box 0.25 mm (ongoing)

- full-size box 0.5 mm (expected Q2 2016)

- full-size box 0.25 mm (expected Q3 2016)

1/2 size 0.5 mm prototype. Notice the "mushrooms" for WF suppressors connection

## Progress report: RICH

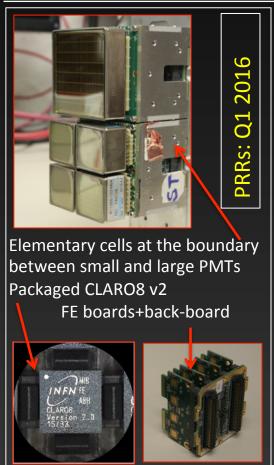

First EDRs (CLARO ASIC + elementary cell) one year ago

- A complete set of tests of the integrated photon detector module structure was felt mandatory before going to the PRRs

- a second version of the CLARO ASIC (CLARO8 v2) was designed incorporating the remarks made at the EDR

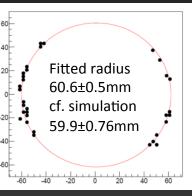

- Crucial test beams this summer before the PRRs. Tested 2 prototype photon detection modules each with 2 ECs mounted on the cooling bar; CLARO8 v2; digital board prototype

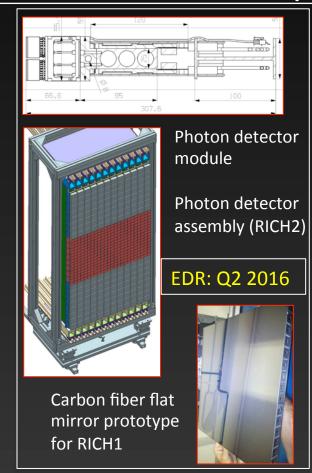

- Design of photon detector assembly for RICH2 almost finalised

- RICH1 mechanics progressing and converging towards final design. Will inherit as much as possible from RICH2

- MaPMT tender finalised. Order placed Nov 2015

Test beam setup

01/12/2015 LHCC meeting G. Passaleva 19

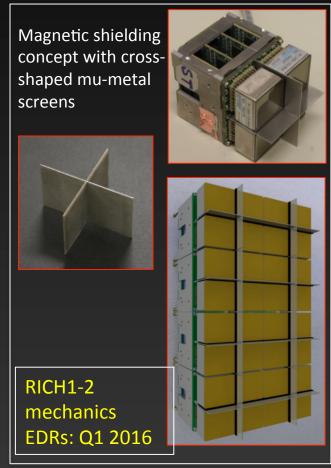

### Progress report: RICH elementary cell, mechanics

01/12/2015

LHCC meeting

G. Passaleva 20

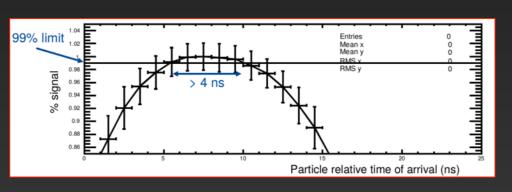

## Progress report: Calorimeter

### EDR of ICECAL in April 2015

Suggestions and remarks from the reviewers implemented in ICECAL v3

ICECAL v3 and prototype Front-End Board tested on beam in September with a fully equipped Calorimeter module.

Results positive

Signal integration plateau of +-4 ns as desired

Readout electronics EDRs: Q3 2016

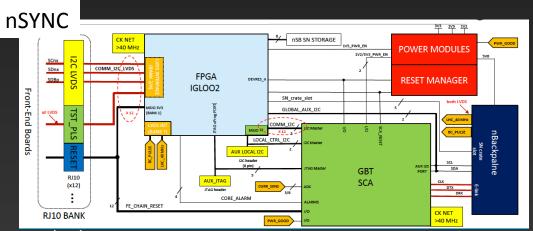

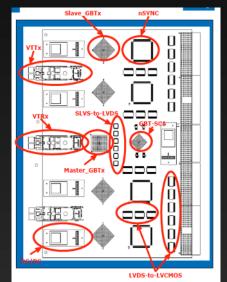

## Progress report: Muon electronics EDR

- Full review of the new electronics

- Key elements:

- ★ New TDC chip (nSYNC)

- ★ New data transmission board (nODE board)

- ★ New control/configuration boards (nPDM, nSB)

- " The design of all four items of hardware is well advanced and there are no apparent technical 'show-stoppers'"

nODE

01/12/2015 LHCC meeting G. Passaleva 22

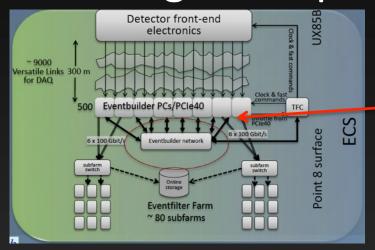

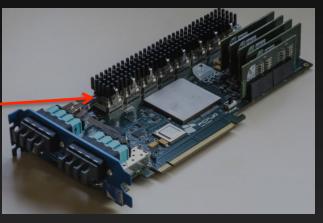

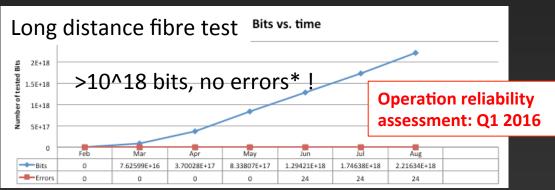

## Progress report: ONLINE

Prototype PCIe40 with ARRIA10 ES2 which implements GEN3 received in June Will equip the MiniDAQ2 Already integrated in a server

Market survey for tender amost completed

<sup>\*</sup> Except for 24 due to an LHC-wide power glitch...

# Summary

• The upgrade project is generally progressing well

Updated milestones have been provided

New milestones for the production phase also included

• Some area of concern are constantly and strictly monitored