# The ALICE ITS UPGRADE

Paolo Camerini

Università degli Studi di Trieste & INFN

on behalf of the ALICE collaboration

### **ALICE UPGRADE**

Major upgrade of ALICE forseen during Long Shutdown 2 (2019/20) Expected Run3&4 Pb-Pb luminosity 6x10<sup>27</sup> cm<sup>-2</sup>s<sup>-1</sup> (10nb<sup>-1</sup> integrated, factor 100 gain in statistics wrt Run1-2)

#### Physics Goal: Study of Quark Gluon Plasma properties via high-precision measurements of rare probes

- identification of secondary vertex of short lived particles @ low p<sub>T</sub>

- large minimum bias data sample needed (no hardware trigger possible)

Present ITS

Present ITS

Present ITS

r<sub>in</sub> = 3.9 cm r<sub>out</sub> = 43 cm

6 silicon detector layers:

2 hybrid pixel (SPD), 2 silicon drift (SDD), 2 silicon strip (SSD)

SPD thickness (X/X<sub>0</sub>): 1.14%/layer Readout rate: ~1kHz

To cope with the increased luminosity and improve the tracking performances, several upgrades planned: new Inner Tracking System, new Muon Forward Tracker, TPC, Readout electronics, Trigger, Online/Offline

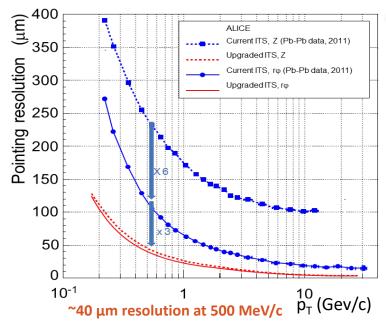

Major Upgrade of the Inner Tracking System to improve low p<sub>T</sub> tracking and data rate performances

# ITS UPGRADE KEY REQUIREMENTS

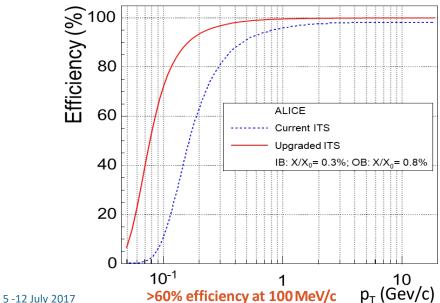

#### Improve impact parameter resolution

- Get closer to IP:  $1^{st}$  layer 39 mm  $\rightarrow$  23 mm (new beam pipe)

- o Reduce material budget: 1.14%  $X_0 \rightarrow 0.3\% X_0$  (Inner Barrel stave) Constraints on chip thickness, power density, support structures

- O Reduce pixel size: 50 μm x 425 μm  $\rightarrow$  O(30 μm x 30 μm)

#### Improve low pT resolution and tracking efficiency

- Pixel, drift, strip detectors → pixel detector

- $\circ$  6 layers  $\rightarrow$  7 pixel layers

#### Improve readout to exploit increased luminosity

Interactions readout rate (2x LHC expected interaction rate): Pb-Pb ~100kHz, minimum bias

#### Capability of fast insertion and removal during end of year shutdown

possibility to replace non-functioning detector modules

#### **Expected radiation load** (10 yrs + safety factor, innermost layer):

$\circ$  TID: ~ 2.7 Mrad; NIEL: ~1.7x10<sup>13</sup> 1MeV n<sub>eq</sub> /cm<sup>2</sup>

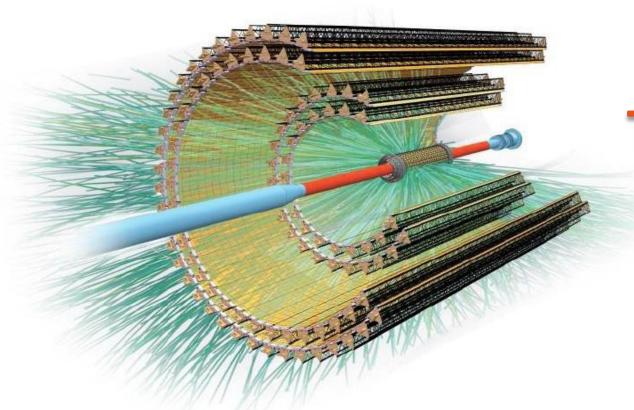

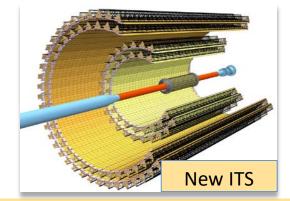

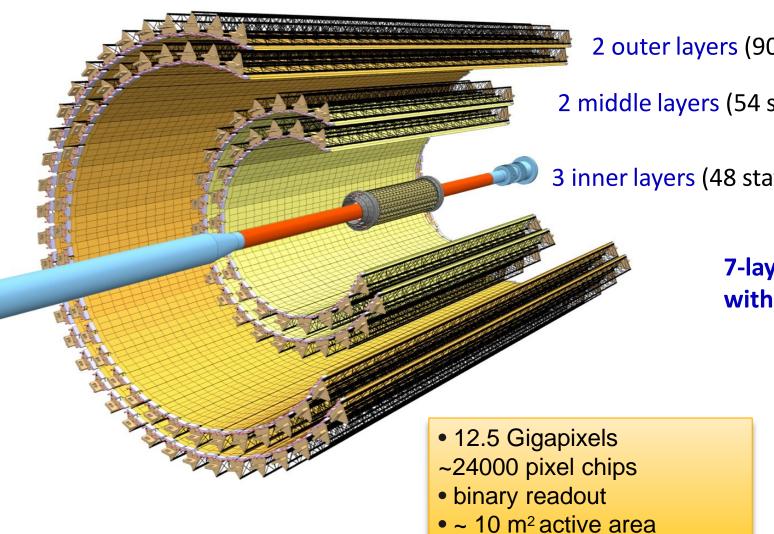

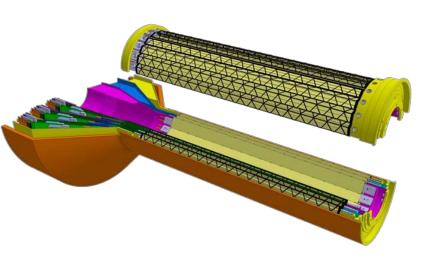

# **INNER TRACKING SYSTEM UPGRADE LAYOUT**

2 outer layers (90 staves) Outer Barrel (OB) 2 middle layers (54 staves)

3 inner layers (48 staves)

Inner Barrel (IB)

7-layer barrel geometry equipped with Monolithic Active Pixel Sensors

IB **Radius** (mm) ~ **23**, 31, 39

IB stave length (mm): ~290

OB Radius (mm): ~196, 245, 344, 393

Middle layers stave **length** (mm): ~900

Outer layers, stave **length** (mm): ~1500

η coverage:  $|η| \le 1.22$

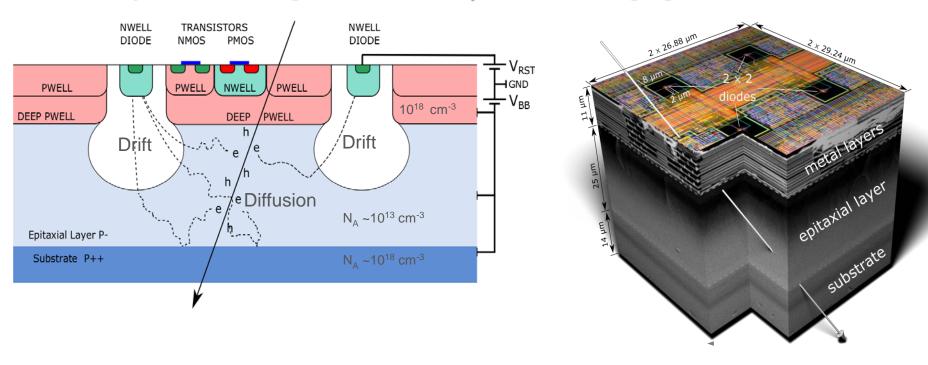

# **ALPIDE: THE MONOLITHIC ACTIVE PIXEL SENSOR**

#### Pixel Sensor produced using TowerJazz 0.18μm CMOS Imaging Process

- Deep Pwell allows in-pixel full CMOS (complex in-pixel circuitry without charge loss).

- Key to enable low-power read-out.

- High granularity, low material budget (~1/7 w.r.t. present ITS pixel chip)

- Resistivity (>1 kΩ·cm) p-type epitaxial layer (25 μm);

- Possibility of reverse biasing

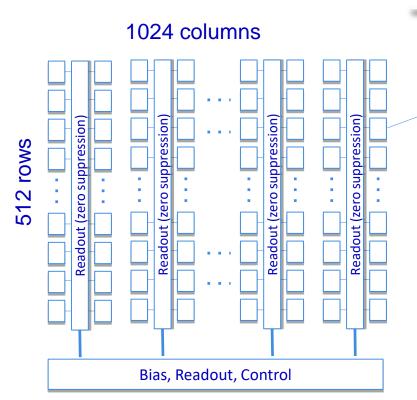

# **ALPIDE: THE MONOLITHIC ACTIVE PIXEL SENSOR**

- In matrix zero suppression.

- Triggered or continuous readout

- Connects directly to 5-m away off-detector electronics via high speed link

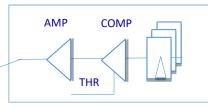

#### In pixel:

- > Amplification

- o Discrimination

- o multi-event buffer

Chip size: 30 mm x 15 mm

Pixel size: 27 μm x 29 μm

| Parameter                   | Inner Barrel                                               | Outer Barrel                                           | ALPIDE                           |

|-----------------------------|------------------------------------------------------------|--------------------------------------------------------|----------------------------------|

| Silicon thickness           | 50μm                                                       | 100µm                                                  | OK                               |

| Spatial resolution          | 5µm                                                        | 10µm                                                   | ~ 5µm                            |

| Chip dimension              | 15mm x 30mm                                                |                                                        | OK                               |

| Power density               | < 300mW/cm <sup>2</sup>                                    | < 100mW/cm <sup>2</sup>                                | <40mW/cm <sup>2</sup>            |

| Event-time resolution       | < 30µs                                                     |                                                        | ~ 2µs                            |

| Detection efficiency        | > 99%                                                      |                                                        | OK                               |

| Fake-hit rate *             | < 10 <sup>-6</sup> /event/pixel                            |                                                        | < 10 <sup>-10</sup> /event/pixeD |

| NIEL radiation tolerance ** | 1.7x10 <sup>13</sup> 1MeV n <sub>eq</sub> /cm <sup>2</sup> | 10 <sup>12</sup> 1MeV n <sub>eq</sub> /cm <sup>2</sup> | OK                               |

| TID radiation tolerance **  | 2.7Mrad                                                    | 100krad                                                | tested at 500krad                |

<sup>\*</sup> revised numbers w.r.t. TDR

<sup>\*\*</sup> including a safety factor of 10, revised numbers w.r.t. TDR

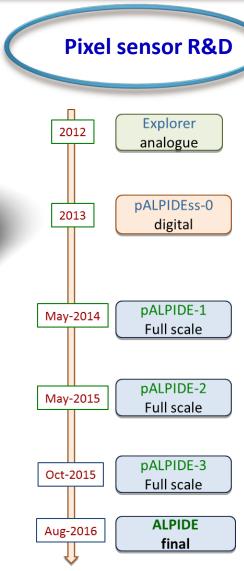

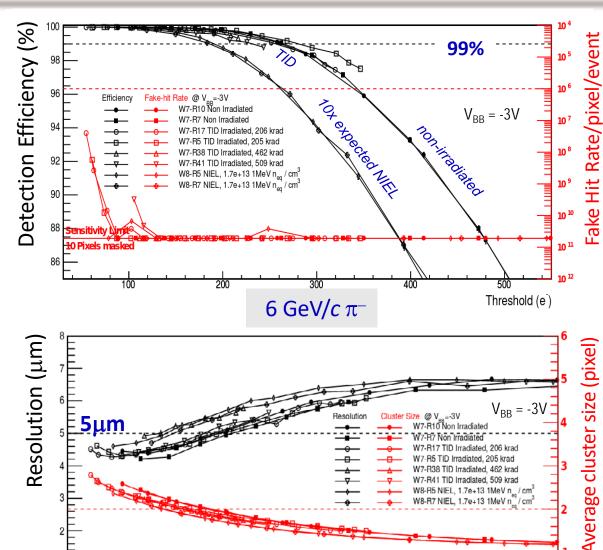

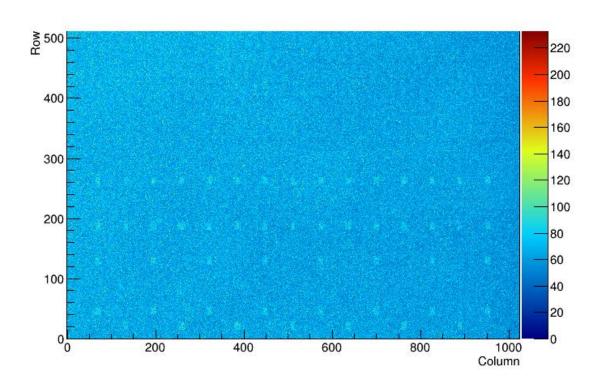

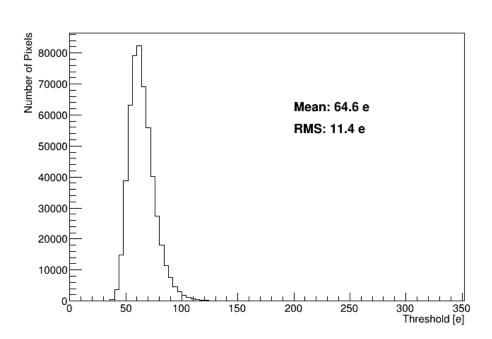

# **ALPIDE PROTOTYPES: TESTS AND QUALIFICATION**

Extensive chip qualification campaign of laboratory and test beam measurements on irradiated and non irradiated sensors:

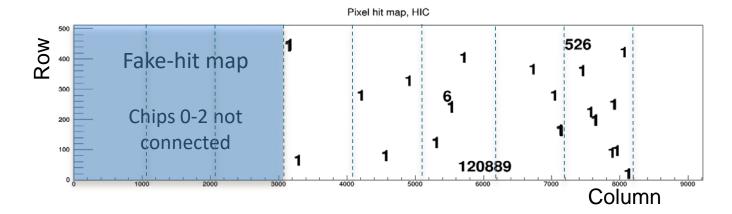

- fake-hit rate < 10<sup>-10</sup>/pixel/event (10<sup>-6</sup>required)

→ Big operational margin (only 10 masked pixels)

- Negligible chip-to-chip fluctuations

- Sufficient operational margin after 10x lifetime

NIEL dose

- efficiency >99% up to ~200 electrons threshold

- Resolution of about 5μm @ threshold of 200 electrons

- NIEL irradiated chips show no significant degradation of operation margins

Threshold (e)

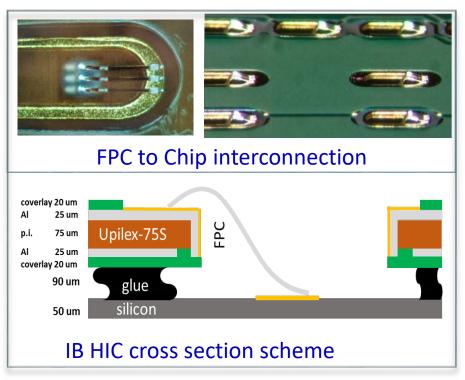

### **ITS-UPGRADE HIBRID INTEGRATED CIRCUIT**

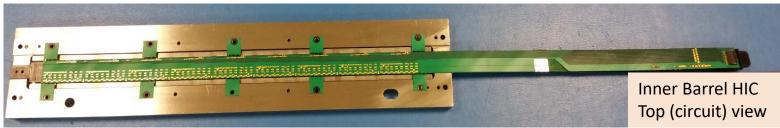

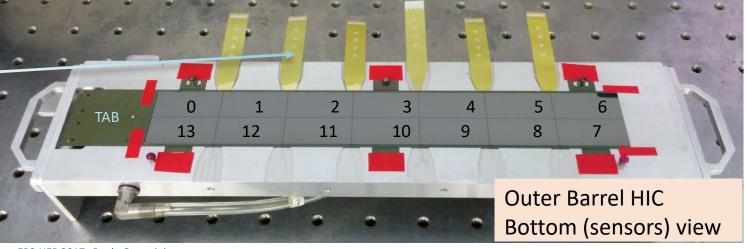

#### Low mass Hybrid Integrated Circuits (HIC)

- IB-HIC: 9 master chips (50 um);

- OB-HIC: 2x7 (1 master, 6 slaves) chips (100um)

- IB (OB): double sided Al(Cu)/polyamide Flexible Printed Circuits (FPC)

- Interconnection based on flip chip and wire bonding technology

EPS-HEP 2017 Paolo Camerini

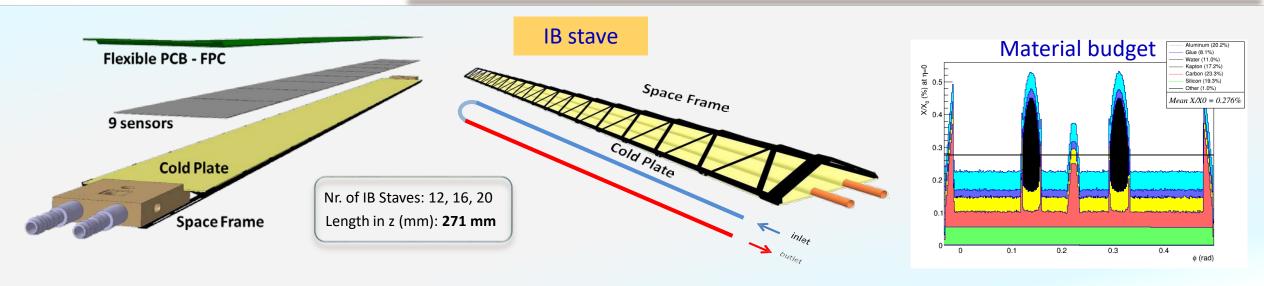

# **ITS-UPGRADE STAVES LAYOUT**

#### **Staves Material budget**

IB: ~0.3% X<sub>0</sub> OB: ~1% X<sub>0</sub>

- Ultra-light stiff space frame C structure

- Ultra-light C laminate Cold Plate (with integrated polyimide cooling ducts; single-phase H<sub>2</sub>O coolant

- Low mass Hybrid Integrated Circuit

5 -12 July 2017

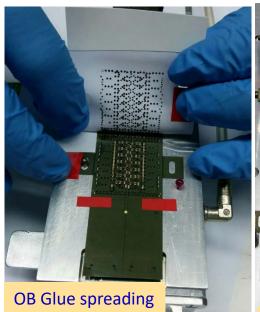

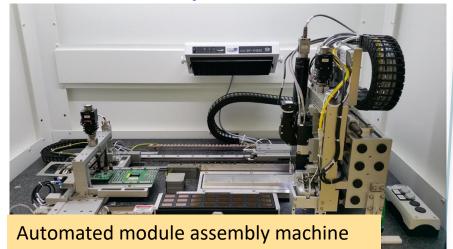

# HIC, STAVE, MECHANICS ASSEMBLY AND PRODUCTION

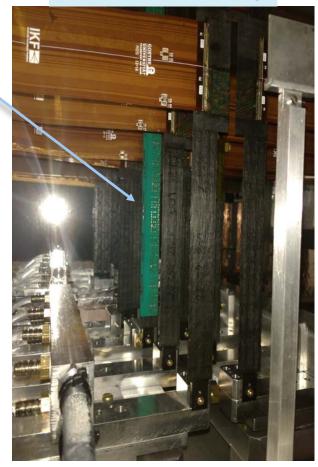

OB stave assembly

**HIC assembly**

TAB removal

HIC Preparation for assembly

Cold plates and space frames

**Staves production:**

IB and OB staves assembly

IB Space Frame + HIC gluing

5 -12 July 2017 EPS-HEP 2017 Paolo Camerini

# HICS AND STAVES PROTOTYPES CHARACTERIZATION

11

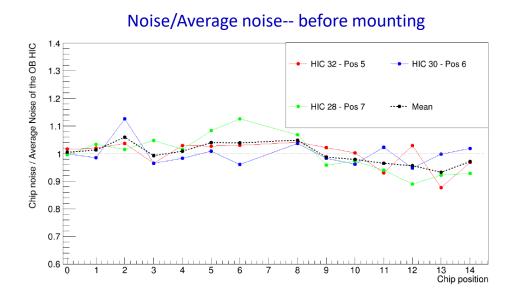

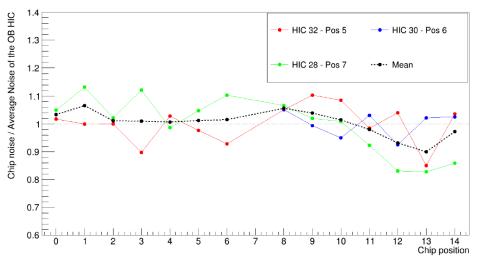

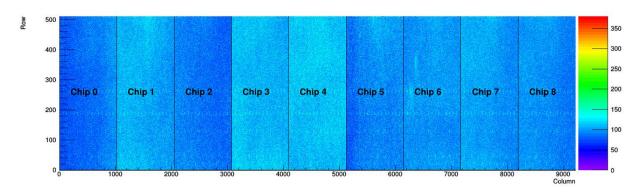

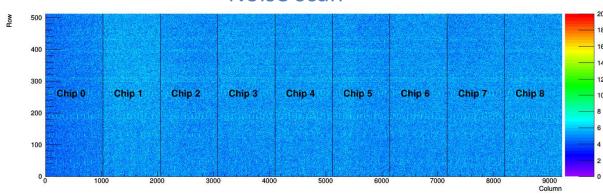

# **HICs and Staves prototypes**

- HICs were characterized in different conditions, operation modes and readout rates

- No significant difference in performance found between standalone chip and chip mounted on HIC

- No significant difference in performance found between HICs and HICs mounted on staves.

- All performances comparable to standalone ALPIDE chip

#### Noise/Average noise-- after mounting

# HICS AND STAVES PROTOTYPES CHARACTERIZATION

12

# **IB stave tested in Pb-Pb run in NA61/SHINE experiment**

- Hit densities: up to 30 hits/cm² (realistic Pb-Pb ALICE running conditions)

- No cooling, no substrate reverse-bias used.

- Fake hit rate < 10<sup>-10</sup> hits/pixel/event (10 pixels masked)

- Detection efficiency: >99%

- Performance comparable to standalone ALPIDE chip

#### IB HIC in NA61 setup

**IB-HIC**

5 -12 July 2017 EPS-HEP 2017 Paolo Camerini

### **CONCLUSIONS**

- The ALICE collaboration will perform a major detector upgrade during LS2 to improve readout and tracking capabilities for runs 3&4 at LHC.

- The ALICE Inner Tracking System Upgrade project has successfully completed the R&D phase. All requirements have been met or exceeded.

- The ITS Upgrade will be the largest existing pixel detector with an innovative monolithic pixel sensor with in pixel full CMOS circuitry.

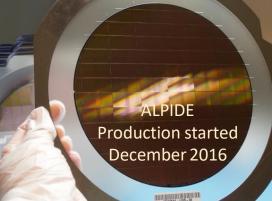

- Detector production started Dec 2016 with the ALPIDE chip start of production.

- Fabrication of staves and barrel mechanics and cooling structures in a very advanced stage.

- HIC production is starting.

- All sites are entering the production phase, expected to finish by the end of 2018.

EPS-HEP 2017 Paolo Camerini 13

# **SPARE SLIDES**

5 -12 July 2017 EPS-HEP 2017 Paolo Camerini 14

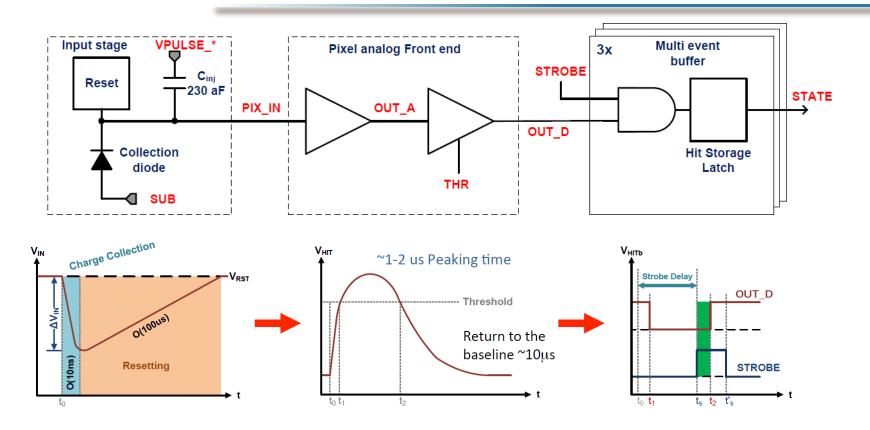

### **PIXEL**

15

- Charge generated in epitaxial layer is collected

- Signal is shaped and compared to threshold

- Signal is strobed (global shutter) into an in-pixel memory (3 hit storage register)

- Hit pixels are read out asynchronously (priority encoding)

### **SINGLE CHIP THRESHOLD SCAN**

Example of thresholds from S-curve scans (obtained with charge injections)

### **HIC THRESHOLD AND NOISE SCANS**

#### Threshold scan

#### Noise scan

- Example of threshold and noise scans of an Inner Barrel HIC

- Chip-to-chip fluctuations comparable to single chips

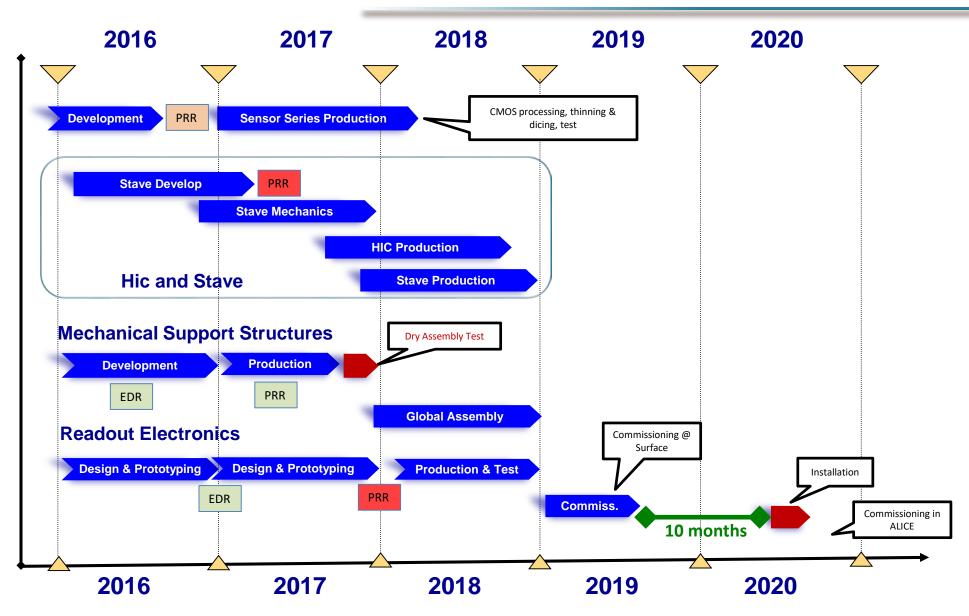

# **OVERALL ITS PLANNING**