# Readout board upgrade for the Pixel Detectors: reasons, status and results in ATLAS

**EPS Conference on High Energy Physics** Venice, Italy 5-12 July 2017

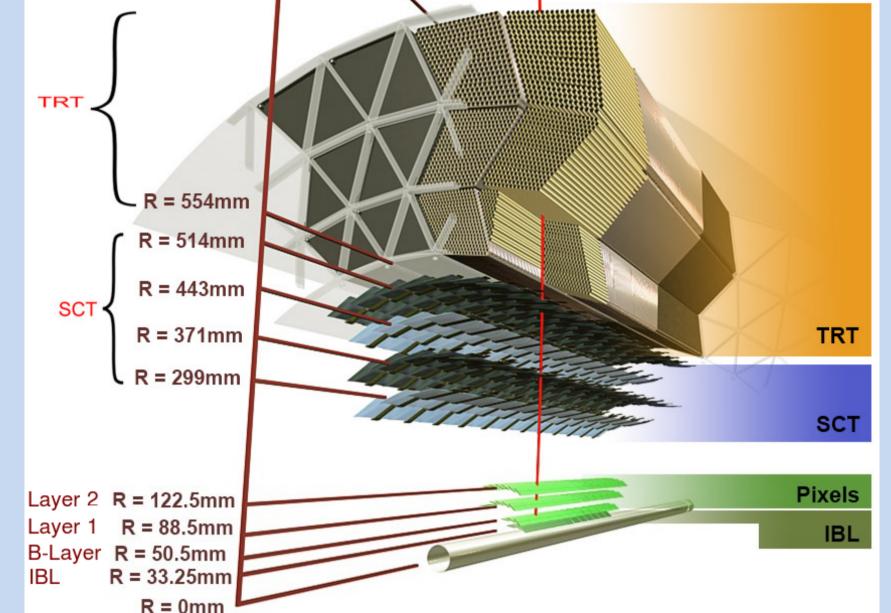

The LHC design luminosity, 10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup>, has already been reached and surpassed during Summer 2016. LHC is planning, in the short term future, to further enhance the luminosity, the trigger frequency and the pileup. These factors constitute a challenge for the data readout since the rate of data to be transmitted depends on both pileup and trigger frequency. In the ATLAS experiment, the effect of the increased luminosity is most evident in the Pixel Detector, which is the detector closest to the beam pipe. In order to face the difficult experimental challenges, the readout system was upgraded during the last few years. The main purpose of the upgrade was to provide a higher bandwidth by exploiting more recent technologies. The new readout system is composed by two paired electronic boards named Back Of Crate (BOC) and ReadOut Driver (ROD). In this poster the main readout limitation related to increased luminosity will be discussed as well as the strategy and the technological solutions adopted in order to cope with the future operational challenges. In addition the general progress and achievements will be presented.

#### A new readout system for IBL

## Readout upgrade for all the Pixel Detector Layers

# **Insertable B-Layer (IBL)**

- Innermost detector of ATLAS

- Installed during 2013 2015 shutdown

- Increase tracking robustness against failures

- High precision tracking

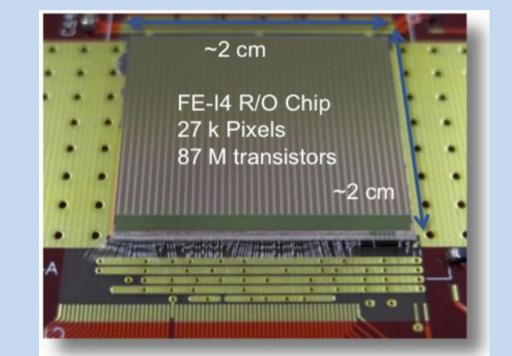

- front-end •FEI4 (130 chips nm technology)

# Limits of the old readout

- Limited bandwidth

- Very high **link occupancy** (throughput/bandwidth)

- Link saturation for Layer 2 foreseen in 2016 (readout speed: 40 Mbps)

- Link saturation for Layer 1 foreseen in 2017 (readout speed: 80 Mbps)

- High level of **desynchronization** and **data loss**

| Layer 2       R = 122.5mm       Pixels       CECNNOIOGY)         Layer 1       R = 88.5mm       IBL       IBL       IBL         B-Layer R = 50.5mm       IBL       IBL       IBL       R = 33.25mm                                     | Module Link Occupancy at 100kHz L1       Readout upgrade         B-Laver       Laver 1         • Same electronic boards as IBL ones (BOC)                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATLAS Inner Detector; the four layer of the Pixel<br>Detector are shown: IBL (innermost), B-Layer, Layer                                                                                                                               | μB-Layer<br>160<br>MbpsLayer 1<br>160<br>                                                                                                                                                                                         |

| 1 and Layer 2<br>27 k Pixels<br>87 M transistors<br>-2 cm                                                                                                                                                                              | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                             |

| <ul> <li>Obsolete components (Spartan 3 FPGAs)</li> <li>Limited bandwidth (1.04 Gbps per pair)</li> </ul>                                                                                                                              | (Estimation<br>based on<br>2016 Dup) 60 81%<br>$103\% 159\% - 52\% 79\% [\mu = 60]$                                                                                                                                               |

| <ul> <li>Limited speed of VME bus, used to calibrate pixels</li> <li>Limitations in control and recovering system</li> <li>Imitations in control and recovering system</li> <li>Imitations in control and recovering system</li> </ul> | 80 101%<br>125% 188%<br>63% 98%<br>125% 188%<br>98%<br>$101\%$ $-5maller link occupancy for Layer 1 (103\% \rightarrow 52\% [\mu = 60])-B-Layer upgrade for system uniformity$                                                    |

| New off-detector electronics                                                                                                                                                                                                           | *Assuming bandwidth before the upgrade (readout speed not enhanced)                                                                                                                                                               |

| <ul> <li>2 new cards: IBLBOC and IBLROD (also called simply BOC and ROD)</li> <li>Maximum bandwidth: 5.12 Gbps</li> <li>Calibration via Gbit-Ethernet</li> <li>PowerPC (PPC) to interface software facilities</li> </ul>               | 20142015201620172018IBL<br>READOUT<br>INSTALLEDPIXEL<br>LAYER 2<br>READOUT<br>UPGRADEPIXEL<br>LAYER 1<br>READOUT<br>UPGRADEPIXEL<br>B-LAYER<br>AND DISKS<br>READOUT<br>UPGRADEPIXEL<br>B-LAYER<br>AND DISKS<br>READOUT<br>UPGRADE |

| New readout overview                                                                                                                                                                                                                   | Main features                                                                                                                                                                                                                     |

| ATLAS Pixel Detector readout<br>chain:                                                                                                                                                                                                 | Old Readout New Readout                                                                                                                                                                                                           |

| •TIM: interface with L1 ATLAS trigger                                                                                                                                                                                                  | Max Bandwidth<br>(Gbps) 1.04 5.12                                                                                                                                                                                                 |

| <ul> <li>Front-end Module (FEI4 for IBL and FEI3<br/>+ MCC for the other layers)</li> <li>BOC: clock + optical interfaces</li> </ul>                                                                                                   | BMF     DATA OUT       NORTH     DATA IN   Software interface DSP + VME PPC + Ethernet                                                                                                                                            |

| •ROD: data processing and<br>histogramming                                                                                                                                                                                             | ROD<br>ICATION BMF CONFIGURATION CONFIGURATION INTO FORCE VME Gbit-Ethernet                                                                                                                                                       |

| •ROS: data gathering and event reconstruction                                                                                                                                                                                          | # of FPGAs per<br>ROD 12 4                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                   |

##

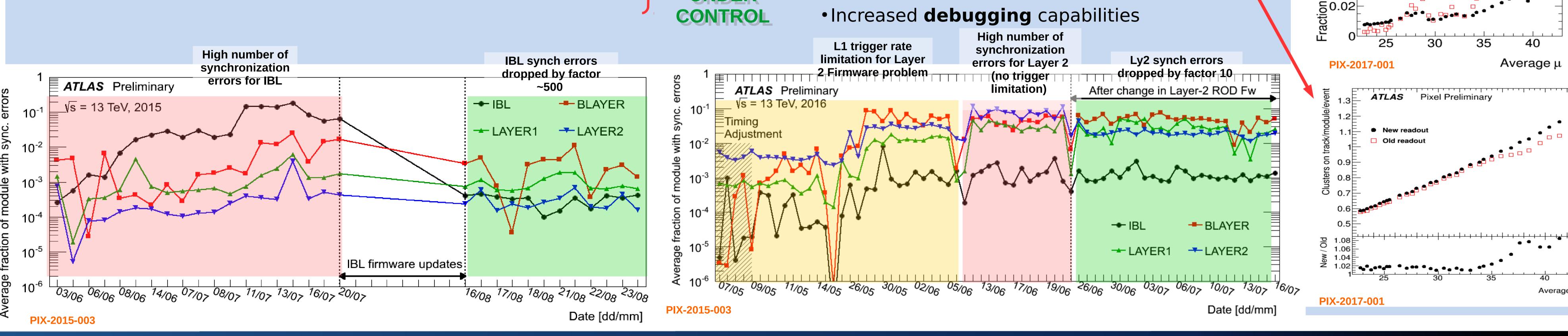

### Readout upgrade results

#### Firmware developments and effects on readout

# **READOUT UPGRADE RESULTS:**

Reduction in average desynchronization

Increased efficiency in event reconstruction

• Link occupancy reduction

• Reduction in **data-losses**

| တ္ 0.12<br>စို န <i>ATLAS</i> Pixel Preliminary |  |

|-------------------------------------------------|--|

|                                                 |  |

ഴ്<del>ഞ</del>0.06

දි0.04

- Firmware development still ongoing  $\rightarrow$  bug correction and new features implementation (i.e. more debugging signals/registers and improvement in the resynchronization algorithm)

- •2015-2016  $\rightarrow$  firmware problem for IBL and Layer 2: high ROD induced desynchronization and limitation on trigger rate.

FIXED:

NOW

SITUATION

UNDER

Nico Giangiacomi (Univ. Bologna & INFN) on behalf of the ATLAS collaboration