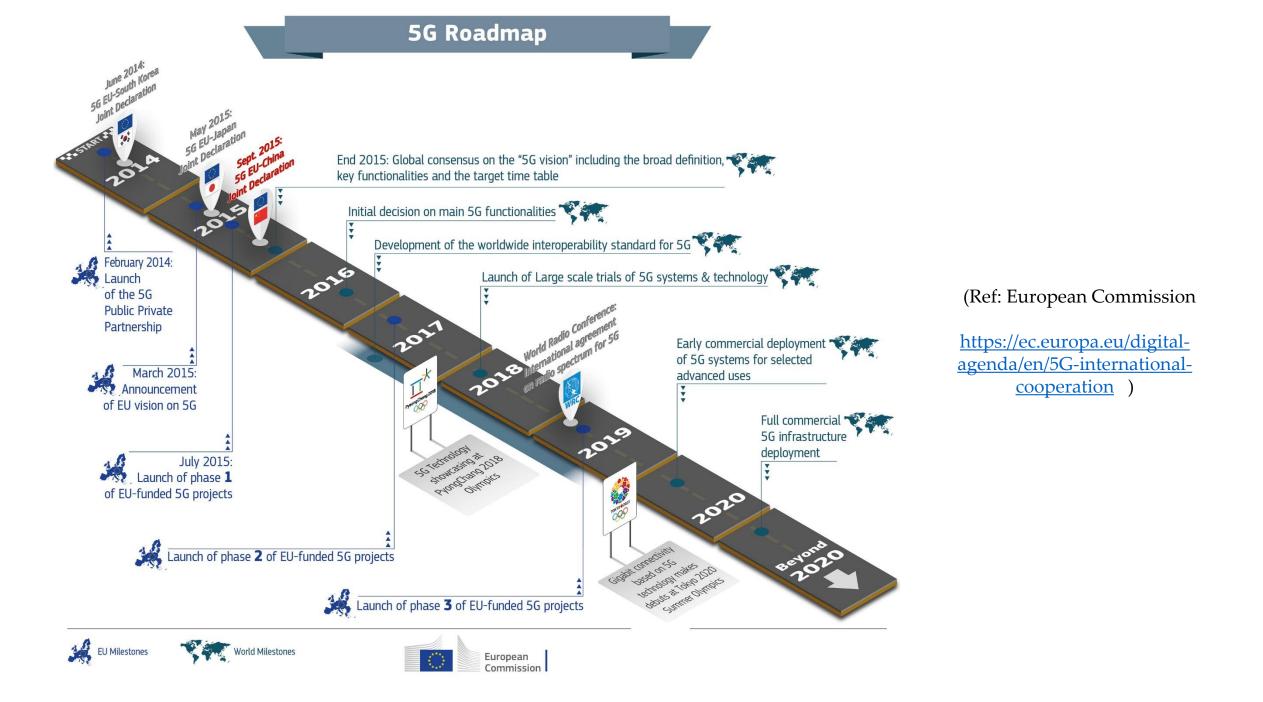

# Technology Trends for TWD Symposium

## Detection and Imaging related Pablo Tello (CERN)

# Reminder

CMOS Scaling

| Constant l | Electric Field Scaling                     |

|------------|--------------------------------------------|

|            | Technology scaling<br>Scaling factor K > 1 |

| Technology scaling   |  |

|----------------------|--|

| Scaling factor K > 1 |  |

#### Primary scaling factors:

| Tox, L, W, Xj (all linear dimensions) 1/K<br>Na, Nd (doping concentration) | К                |

|----------------------------------------------------------------------------|------------------|

| Vdd (supply voltage)                                                       | 1/K              |

| Derived scaling behavior of transistor:                                    |                  |

| Electric field                                                             | 1                |

| lds                                                                        | 1/K              |

| Capacitance                                                                | 1/K              |

| Derived scaling behavior of circuit:                                       |                  |

| Delay (CV/I)                                                               | 1/K              |

| Power (VI)                                                                 | 1/K <sup>2</sup> |

| Power-delay product                                                        | 1/K³             |

| Circuit density ( $lpha$ 1/A)                                              | K <sup>2</sup>   |

## Constant Voltage Scaling

| <u>Primary scaling factors:</u><br>Tox, L, W, Xj (all linear dimensions) 1/K |                  |

|------------------------------------------------------------------------------|------------------|

| Na, Nd (doping concentration)<br>Vdd (supply voltage)                        | K²<br>1          |

| Derived scaling behavior of transistor:                                      |                  |

| Electric field                                                               | К                |

| Ids                                                                          | К                |

| Capacitance                                                                  | 1/K              |

| Derived scaling behavior of circuit:                                         |                  |

| Delay (CV/I)                                                                 | 1/K <sup>2</sup> |

| Power (VI)                                                                   | К                |

| Power-delay product                                                          | 1/K              |

| Circuit density ( $lpha$ 1/A)                                                | K <sup>2</sup>   |

#### TABLE II

Scaling Results for Interconnection Lines

| Parameter                          | Scaling Factor |

|------------------------------------|----------------|

| Line resistance, $R_L = \rho L/Wt$ | κ              |

| Normalized voltage drop $IR_L/V$   | К              |

| Line response time $R_L C$         | 1              |

| Line current density $I/A$         | К              |

| Generalized Sca   Technology scaling   Scaling factor K > 1   1< α < K                                                                               | aling                            | <b>Non Scaling Factors</b><br>Bandgap of Silicon Eg=1.12eV   |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------|

| Primary scaling factors:                                                                                                                             |                                  | Thermal voltage kT/q                                         |

| Tox, L, W, Xj (all linear dimensions) 1/K<br>Na, Nd (doping concentration)<br>Vdd (supply voltage)<br><u>Derived scaling behavior of transistor:</u> | αΚ<br>α/Κ                        | Mobility degradation<br>Increasing doping and electric field |

| Electric field<br>Ids<br>Capacitance                                                                                                                 | α<br>α²/Κ<br>1/Κ                 | Velocity saturation                                          |

| <u>Derived scaling behavior of circuit:</u><br>Delay (CV/I)<br>Power (VI)                                                                            | 1/αΚ<br>α³/Κ²                    | Parasitic s/d resistance                                     |

| Power-delay product<br>Circuit density (α 1/A)                                                                                                       | $\alpha^2/K^3$<br>K <sup>2</sup> | Process tolerance                                            |

R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of ion-implanted MOSFET's with very small physical dimensions," IEEE J. Solid-State Circuits, vol. SC-9, p. 256, 1974.

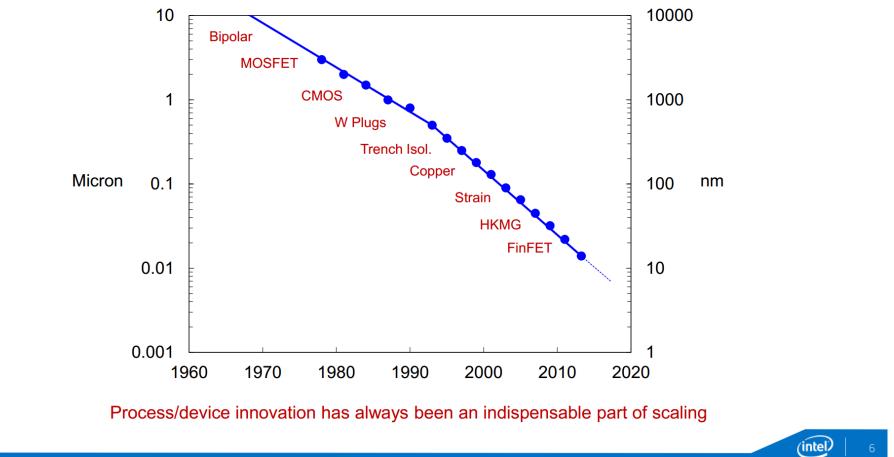

## General Scaling Trends CMOS Transistors

(EP1) Moore's Law Challenges Below 10nm: Technology, Design and Economic Implications

(Ref: Moore's law challenges below 10nm: Technology, design and economic implications, ISSCC (Solid- State Circuits Conference ) Panel, 2015) http://ieeexplore.ieee.org/xpl/mostRecentIssue.jsp?punumber=7054075

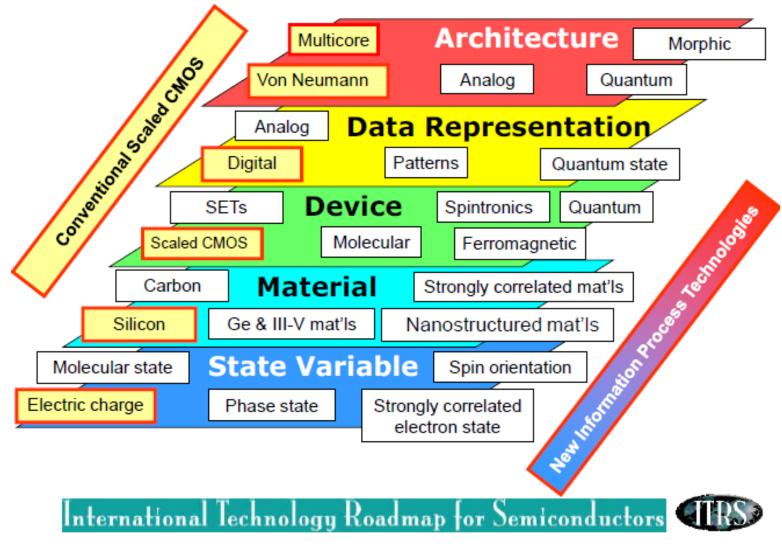

#### A Taxonomy for Nano Information Processing Technologies

(Ref: ITRS <u>http://www.itrs.net/reports.html</u>)

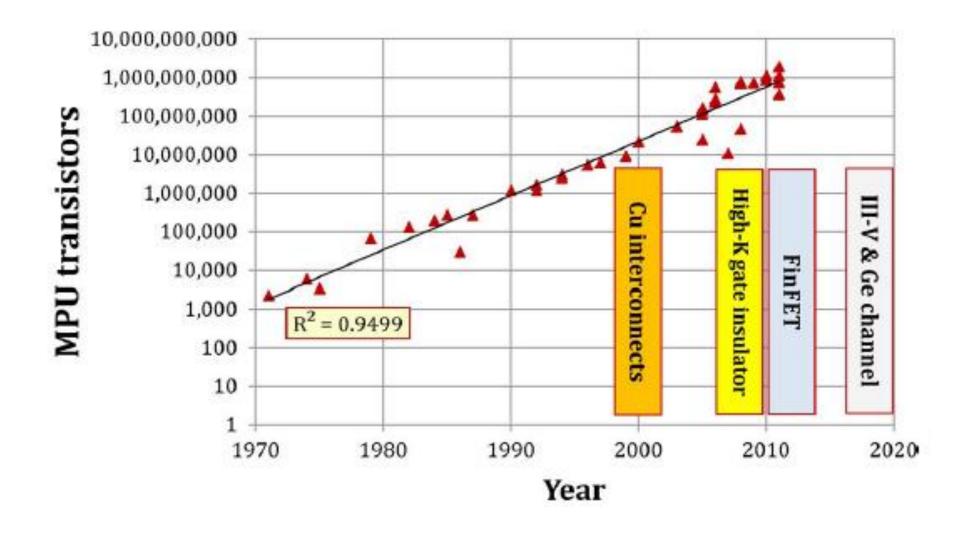

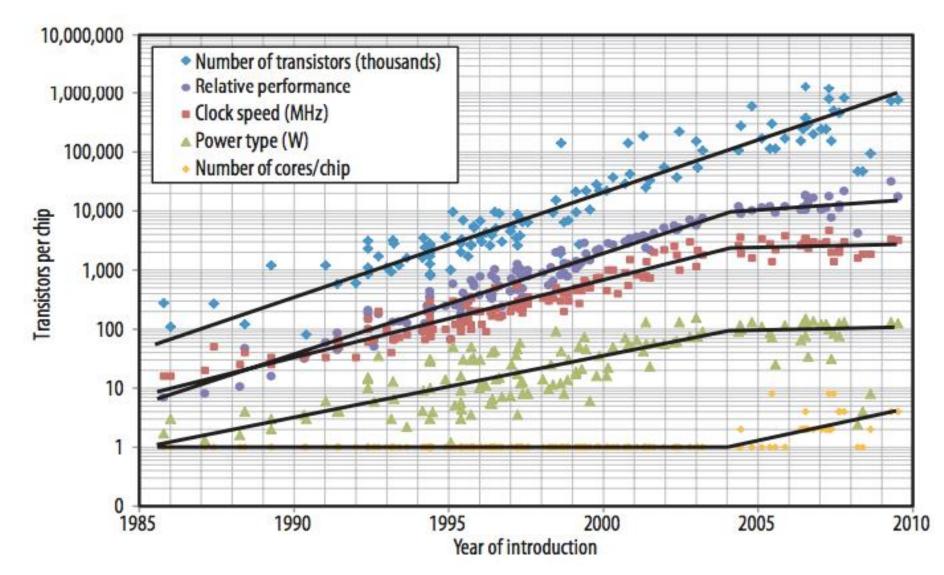

The number of transistors per microprocessor chip versus time, showing introduction of new enabling technologies.

(Ref: Cavin et al, Science and Engineering Beyond Moore's Law, Proceedings of the IEEE | Vol. 100, May 13th, 2012)

The number of transistors per microprocessor chip versus time, showing introduction of new enabling technologies.

(Ref: National Research Council, The Future of Computing Performance: Game Over or Next Level? Nat'l Academies Press, 2010)

# Trends & Wishes (various technologies)

#### INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS 2013 EDITION

#### CMOS Scaling Roadmap

| Year of Production                                               | 2013     | 2015       | 2017        | 2019      | 2021      | 2023     | 2025     | 2028     |

|------------------------------------------------------------------|----------|------------|-------------|-----------|-----------|----------|----------|----------|

| Logic Industry "Node Name" Label                                 | "16/14"  | "10"       | "7"         | "5"       | "3.5"     | "2.5"    | "1.8"    |          |

| Logic <sup>1</sup> / <sub>2</sub> Pitch (nm)                     | 40       | 32         | 25          | 20        | 16        | 13       | 10       | 7        |

| Flash ½ Pitch [2D] (nm)                                          | 18       | 15         | 13          | 11        | 9         | 8        | 8        | 8        |

| DRAM <sup>1</sup> / <sub>2</sub> Pitch (nm)                      | 28       | 24         | 20          | 17        | 14        | 12       | 10       | 7.7      |

| FinFET Fin Half-pitch (new) (nm)                                 | 30       | 24         | 19          | 15        | 12        | 9.5      | 7.5      | 5.3      |

| FinFET Fin Width (new) (nm)                                      | 7.6      | 7.2        | 6.8         | 6.4       | 6.1       | 5.7      | 5.4      | 5.0      |

| 6-t SRAM Cell Size(um 2) [@60f2]                                 | 0.096    | 0.061      | 0.038       | 0.024     | 0.015     | 0.010    | 0.0060   | 0.0030   |

| MPU/ASIC HighPerf 4t NAND Gate Size(um2)                         | 0.248    | 0.157      | 0.099       | 0.062     | 0.039     | 0.025    | 0.018    | 0.009    |

| 4-input NAND Gate Density (Kgates/mm) [@155f2]                   | 4.03E+03 | 6.37E+03   | 1.01E+04    | 1.61E+04  | 2.55E+04  | 4.05E+04 | 6.42E+04 | 1.28E+05 |

| Flash Generations Label (bits per chip) (SLCMLC)                 | 64G/128G | 128G /256G | 256G / 512G | 512G / 1T | 512G / 1T | 1T / 2T  | 2T / 4T  | 4T / 8T  |

| Flash 3D Number of Layer targets (at relaxed Poly half pitch)    | 16-32    | 16-32      | 16-32       | 32-64     | 48-96     | 64-128   | 96-192   | 192-384  |

| Flash 3D Layer half-pitch targets (nm)                           | 64nm     | 54nm       | 45nm        | 30nm      | 28nm      | 27nm     | 25nm     | 22nm     |

| DRAM Generations Label (bits per chip)                           | 4G       | 8G         | 8G          | 16G       | 32G       | 32G      | 32G      | 32G      |

| 450mm Production High Volume Manufacturing Begins (100Kwspm)     |          |            |             | 2018      |           |          |          |          |

| Vdd (High Performance, high Vdd transistors)[**]                 | 0.86     | 0.83       | 0.80        | 0.77      | 0.74      | 0.71     | 0.68     | 0.64     |

| 1/(CV/I ) (1/psec) [**]                                          | 1.13     | 1.53       | 1.75        | 1.97      | 2.10      | 2.29     | 2.52     | 3.17     |

| On-chip local clock MPU HP [at 4% CAGR]                          | 5.50     | 5.95       | 6.44        | 6.96      | 7.53      | 8.14     | 8.8      | 9.9      |

| Maximum number wiring levels [unchanged                          | 13       | 13         | 14          | 14        | 15        | 15       | 16       | 17       |

| MPU High-Performance (HP) Printed Gate Length (GLpr) (nm) [**]   | 28       | 22         | 18          | 14        | 11        | 9        | 7        | 5        |

| MPU High-Performance Physical Gate Length (GLph) (nm) [**]       | 20       | 17         | 14          | 12        | 10        | 8        | 7        | 5        |

| ASIC/Low Standby Power (LP) Physical Gate Length (nm) (GLph)[**] | 23       | 19         | 16          | 13        | 11        | 9        | 8        | 6        |

|                                                                  |          |            |             |           |           |          |          |          |

\*\* Note: from the PIDS working group data; however, the calibration of Vdd, GLph, and I/CV is ongoing for improved targets in 2014 ITRS work

**IMEC LOGIC DEVICE ROADMAP**

DEVICE TECHNOLOGY FEATURES

| Early       | 2013 - 20       | 014                                             | 2015       | - 2016                                                                                      | 2017 - 2018   |                  | 2019 -            |         |

|-------------|-----------------|-------------------------------------------------|------------|---------------------------------------------------------------------------------------------|---------------|------------------|-------------------|---------|

| production  | 16 -14n         | IM                                              | 1          | 0nm                                                                                         | 7nm           |                  | 5nm               |         |

| Vdd (V)     | 0.8             |                                                 | (          | ). <mark>8-0.7</mark>                                                                       | 0             | .7-0.5           | 0.7-0.            | 5       |

|             | Planar SOI      | Bulk FinFET                                     | SOI FINFET | SiGe/Ge channel                                                                             | IIIV channel  | Lateral Nanowire | Vertical Nanowire |         |

| Device      | FinFET (Bulk, S | OI), FDSOI                                      |            |                                                                                             | AA, QIV, SOI) | GAA lateral NW;  | (Vert. NV         |         |

|             |                 |                                                 | Improve    | Electrostatics                                                                              |               |                  |                   |         |

| Channel n/p | Si / S          | i                                               | Si         | / SiGe                                                                                      | Si / 5        | SiGe (Ge)        | Si / SiGe (III    | V / Ge) |

| S/D Strain  | P S/D eSiGe     | N S/D Si:P<br>P S/D eSiGe (55%)<br>Low-k spacer |            | N S/D Si:P:C N S/D Si:P:C<br>P S/D eSiGe (>60%) P S/D eSiGe (>6<br>Low-k spacer Low-k space |               |                  | TBD               |         |

|             |                 |                                                 | Improve    | Performance                                                                                 | -             |                  |                   |         |

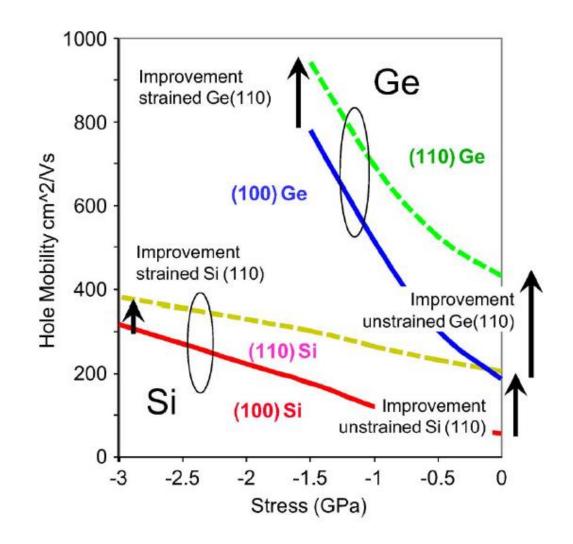

Mobility and strain in Si and Ge as a function of stress and wafer orientation illustrating the reduction in improvement between (100) and (110) material (with a <110> channel direction) as a function of stress.

(Ref: Kelin J. Kuhn, IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 59, NO. 7, JULY 2012)

(Ref: Electronics Cooling Magazine 2015, http://www.electronics-cooling.com/)

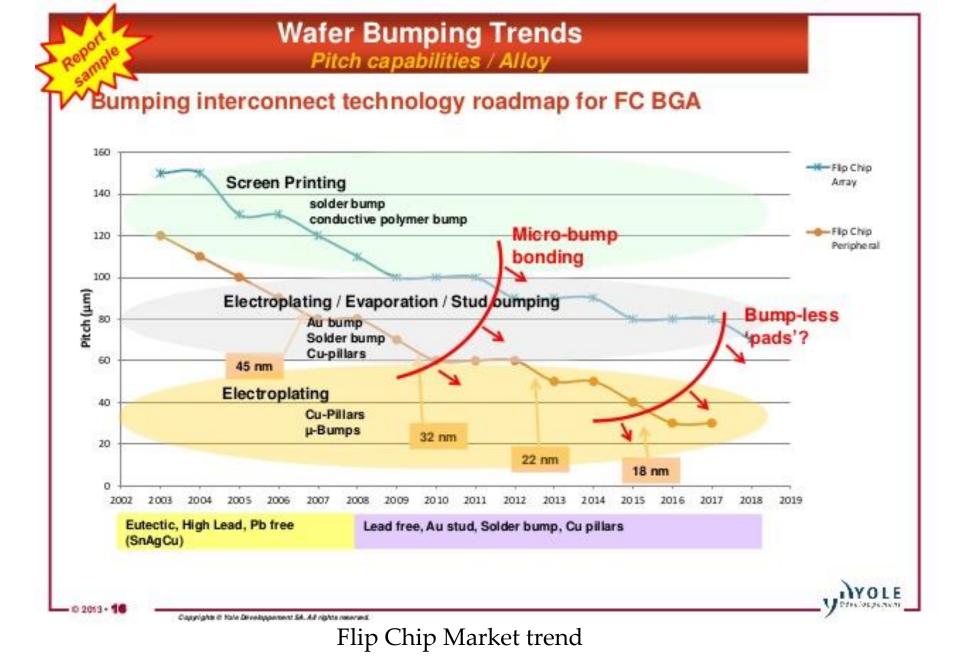

(Ref: Yole Developpement <u>http://www.yole.fr/</u>)

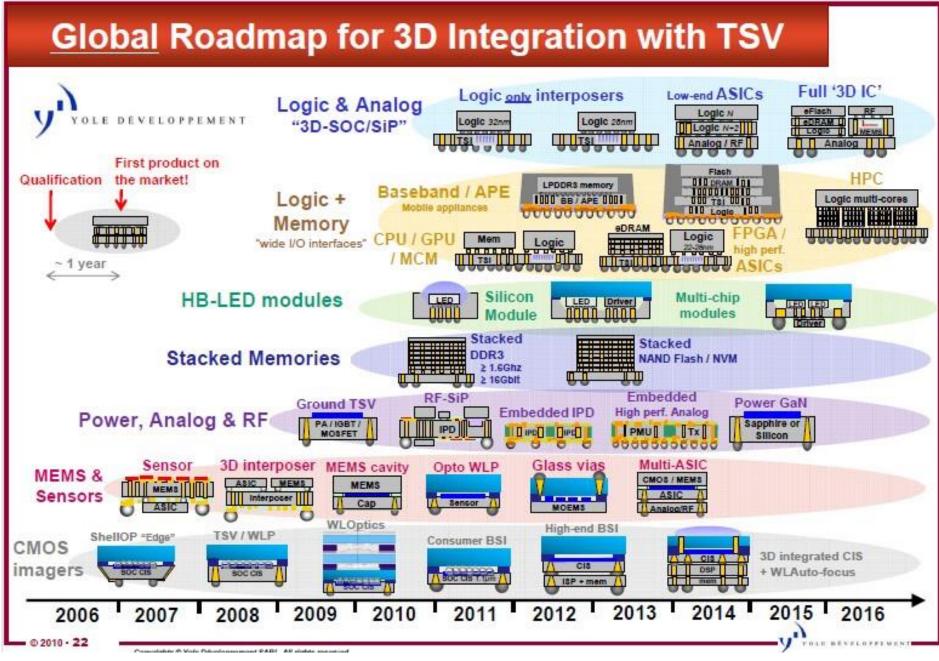

## **3D TECHNOLOGY LANDSCAPE**

|                                    | 3D-SIC                                                                                                                                 |                                      | 3D-SOC                                                                                       |                                                                                             | 3D-IC                    |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|

| wiring level                       | Global                                                                                                                                 | Semi-global                          | Intermediate                                                                                 | Local                                                                                       | FEOL                     |

| 2-tier<br>stack                    |                                                                                                                                        |                                      |                                                                                              | 2 <sup>nd</sup> FEOL<br>after stacking                                                      | Multi-tier FEOL          |

| Contact Pitch<br>Relative density: | $\begin{array}{c} 40 \Rightarrow 20 \Rightarrow 10 \Rightarrow 5\\ 1/_{16} \Rightarrow 1/_{4} \Rightarrow 1 \Rightarrow 4 \end{array}$ |                                      | $\begin{array}{ccc} 2 \ \mu m & \Rightarrow 0.5 \ \mu m \\ 50 & \Rightarrow 400 \end{array}$ | $\begin{array}{ccc} 200 & \Rightarrow 100 \text{ nm} \\ 5000 \Rightarrow 10000 \end{array}$ | < 100 nm<br>> 10000      |

| Partitioning                       | Die                                                                                                                                    | blocks of star                       | ndard cells                                                                                  | Gates                                                                                       | Transistors              |

|                                    |                                                                                                                                        | Block-level pa                       | rtitioning                                                                                   | Partitioning/<br>placement                                                                  | Standard<br>cell design  |

|                                    |                                                                                                                                        | Block size depends<br>3D interconnec |                                                                                              | →EDA<br>problem                                                                             | →device/cel<br>I problem |

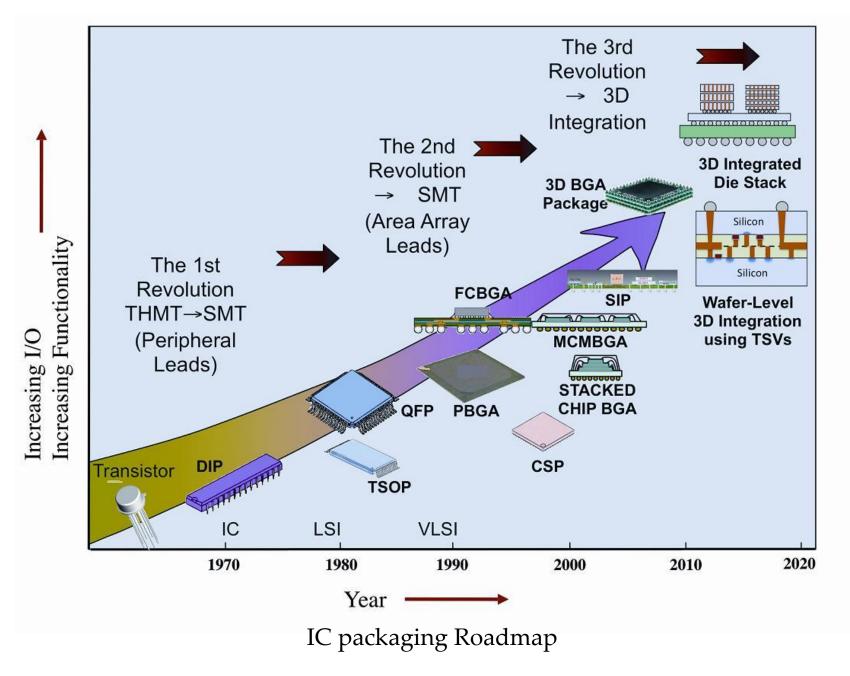

Today's 3D technology landscape segmented by wiring-level, showing cross-sections of typical 2-tier circuit stacks, and indicating planned reductions in contact pitches. (Source: IMEC)

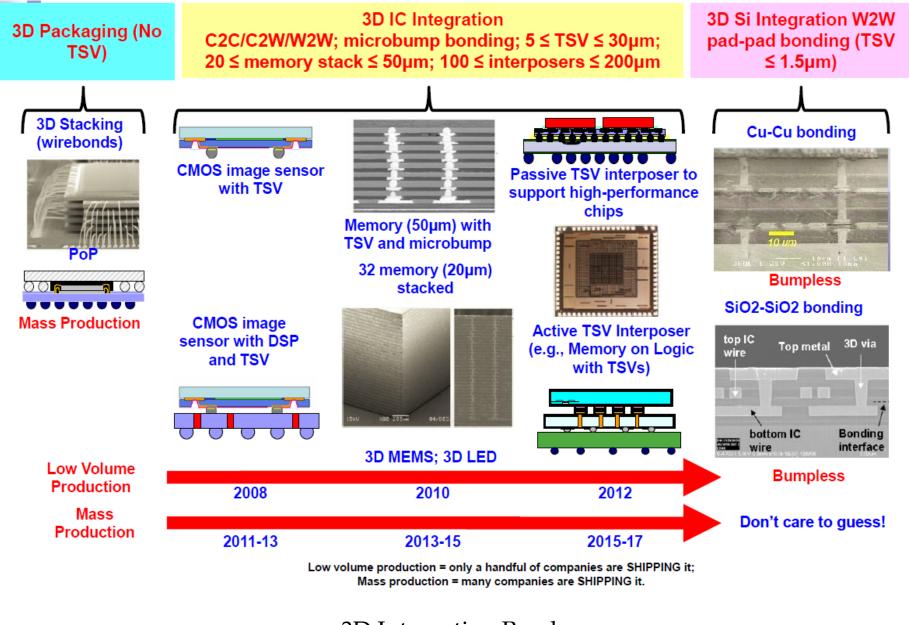

3D Integration Roadmap

(Ref: International Electronics Manufacturing Initiative (iNEMI), 2013 http://www.inemi.org/about-us)

## **TSV AND Si INTERPOSER FORECAST**

|                                 | Bn<br>Packages |                  | TSV Die/<br>Package |      | Bn<br>Die |      | Die per<br>300mm |      | afers<br>i Equiv.) | Typical<br>Wafer Size |

|---------------------------------|----------------|------------------|---------------------|------|-----------|------|------------------|------|--------------------|-----------------------|

|                                 | 2014           | 2016             | 2014                | 2016 | 2014      | 2016 | Wafer            | 2014 | 2016               |                       |

| DRAM/NAND<br>(plus control die) | 0.2            | 1                | 3                   | 2.3  | 0.6       | 2.3  | 650              | 0.9  | 3.5                | 300                   |

| Logic and Memory                | 0              | 0.25             | 1                   | 1    | 0         | 0.25 | 390              | 0.0  | 0.6                | 300                   |

| Si Interposer for Logic         | 0.05           | 0.16             | 1                   | 1    | 0.05      | 0.16 | 300              | 0.2  | 0.5                | 200/300/<br>panel     |

| RF/Discrete/LED/                | 1.7            | 2.5              | 1                   | 1    | 1.7       | 2.5  | 7000             | 0.24 | 0.4                | 150/200/300           |

| Image Sensor                    | 2.6            | 2.9              | 1                   | 1    | 2.55      | 2.85 | 3000             | 0.85 | 1.0                | 200/300               |

| Total                           | 4.5            | <mark>6.8</mark> |                     |      | 4.9       | 8.1  |                  | 2.2  | 6.0                |                       |

#### 3D Integration Roadmap

(Ref: International Electronics Manufacturing Initiative (iNEMI), 2013 http://www.inemi.org/about-us)

|                            | Draft Interposer Table                               |                     |                     |                        |                     |                     |                     |                        |                     |                     |                     |                    |

|----------------------------|------------------------------------------------------|---------------------|---------------------|------------------------|---------------------|---------------------|---------------------|------------------------|---------------------|---------------------|---------------------|--------------------|

| Base Silicon<br>Interposer | Year of Production                                   | 2013                | 2014                | 2015                   | 2016                | 2017                | 2018                | 2019                   | 2020                | 2021                | 2022                | 2023               |

|                            | Minimum TSV pitch (um)                               | 40                  | 40                  | 30                     | 30                  | 30                  | 20                  | 20                     | 20                  | 20                  | 20                  | 20                 |

|                            | Minimum TSV diameter(um) (D)                         | 20                  | 20                  | 15                     | 15                  | 15                  | 10                  | 10                     | 10                  | 10                  | 10                  | 10                 |

|                            | TSV maximum aspect ratio (L/D)                       | 5                   | 5                   | 7                      | 7                   | 7                   | 10                  | 10                     | 10                  | 10                  | 10                  | 10                 |

| 150                        | Minimum Si Wafer final thickness (um) <sup>(3)</sup> | 100                 | 100                 | 100                    | 100                 | 100                 | 100                 | 100                    | 100                 | 100                 | 100                 | 100                |

| TSV Methods and Materials  |                                                      |                     |                     |                        |                     |                     | 1                   |                        |                     |                     |                     |                    |

| Via                        | Via fill method                                      | Cu ECD Fill         | Cu ECD Fill         | Cu ECD Fill            | Cu ECD Fill         | Cu ECD Fill         | Cu ECD Fill         | Cu ECD Fill            | Cu ECD Fill         | Cu ECD Fill         | Cu ECD Fill         | Cu ECD Fi          |

|                            | TSV Fill                                             | Cu / Other          | Cu / Other          | Cu / Other             | Cu / Other          | Cu / Other          | Cu / Other          | Cu / Other             | Cu / Other          | Cu / Other          | Cu / Other          | Cu / Other         |

|                            | Alignment requirement, um<br>(assume 25% exit dia)   | 5                   | 5                   | 3.75                   | 3.75                | 3.75                | 2.5                 | 2.5                    | 2.5                 | 2.5                 | 2.5                 | 2.5                |

|                            | Maximum Number of RDL Layers                         | 4                   | 4                   | 4                      | 4                   | 4                   | 4                   | 4                      | 4                   | 4                   | 4                   | 4                  |

|                            | Maximum Number of RDL Layers -<br>Bottom side        | 2                   | 2                   | 2                      | 2                   | 2                   | 2                   | 2                      | 2                   | 2                   | 2                   | 2                  |

| 3D Integration             |                                                      | Cu-Cu,              | Cu-Cu,              | Cu-Cu,                 | Cu-Cu,              | Cu-Cu,              | Cu-Cu,              | Cu-Cu,                 | Cu-Cu,              | Cu-Cu,              | Cu-Cu,              | Cu-Cu,             |

| 5D integration             | Interconnect methods - Top side                      | Cu-Sn-Cu,           | Cu-Sn-Cu,           | Cu-Sn-Cu,<br>Cu-Ni/Au- | Cu-Sn-Cu,           | Cu-Sn-Cu,           | Cu-Sn-Cu,           | Cu-Sn-Cu,<br>Cu-Ni/Au- | Cu-Sn-Cu,           | Cu-Sn-Cu,           | Cu-Sn-Cu,           | Cu-Sn-Cu           |

|                            | (5)                                                  | Cu-Ni/Au-<br>SnAg,  | Cu-Ni/Au-<br>SnAg,  | SnAg,                  | Cu-Ni/Au-<br>SnAg,  | Cu-Ni/Au-<br>SnAg,  | Cu-Ni/Au-<br>SnAg,  | SnAg,                  | Cu-Ni/Au-<br>SnAg,  | Cu-Ni/Au-<br>SnAg,  | Cu-Ni/Au-<br>SnAg,  | Cu-Ni/Au<br>SnAg,  |

|                            |                                                      | AuSn,               | AuSn,               | AuSn,                  | AuSn,               | AuSn,               | AuSn,               | AuSn,                  | AuSn,               | AuSn,               | AuSn,               | AuSn,              |

|                            |                                                      | Cu-In-Cu            | Cu-In-Cu            | Cu-In-Cu               | Cu-In-Cu            | Cu-In-Cu            | Cu-In-Cu            | Cu-In-Cu               | Cu-In-Cu            | Cu-In-Cu            | Cu-In-Cu            | Cu-In-Cu           |

|                            | Interconnect methods - Bottom                        | Solder              | Solder              | Solder                 | Solder              | Solder              | Solder              | Solder                 | Solder              | Solder              | Solder              | Solder             |

|                            | side                                                 | Cu<br>Pillar/Solder | Cu<br>Pillar/Solder | Cu<br>Pillar/Solder    | Cu<br>Pillar/Solder | Cu<br>Pillar/Solder | Cu<br>Pillar/Solder | Cu<br>Pillar/Solder    | Cu<br>Pillar/Solder | Cu<br>Pillar/Solder | Cu<br>Pillar/Solder | Cu<br>Pillar/Sold/ |

3D Integration Roadmap

(Ref: International Electronics Manufacturing Initiative (iNEMI), 2013 http://www.inemi.org/about-us)

(Ref: Yole Developpement <u>http://www.yole.fr/</u>)

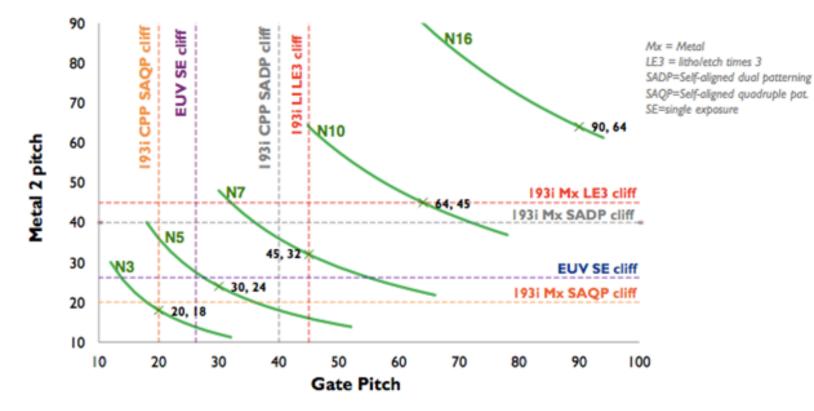

### IMEC LOGIC LITHOGRAPHY ROADMAP

#### KEY TRANSISTOR DIMENSIONS

| Early              | 2013 - 2014 | 2015 - 2016 | 2017 - 2018 | 2019    |

|--------------------|-------------|-------------|-------------|---------|

| production         | 16-14nm     | l 0nm       | 7nm         | 5nm     |

| FinFET pitch (nm)  | 42-48nm     | 30-32nm     | 21-24nm     | 14-16nm |

| Gate Pitch (nm)    | 64-80nm     | 50-64nm     | 40-45nm     | 22-32nm |

| Contact pitch (nm) | 64-80nm     | 50-64nm     | 40-45nm     | 22-32nm |

| Metal pitch (nm)   | 56-64nm     | 40-45nm     | 28-32nm     | 20-22nm |

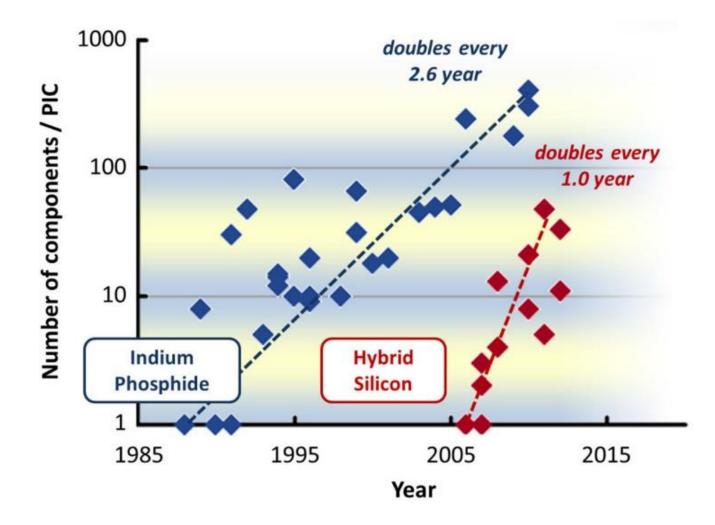

Development of chip complexity measured as the number of components per chip. Data for indiumphosphide-based photonic integrated circuits (PICs, blue) and for hybrid-silicon PICs (red) which fit to exponential growth curves (dashed).

(Ref: M. J. R. Heck, M. L. Davenport, and J. E. Bowers, "Progress in hybrid-silicon photonic integrated circuit technology," SPIE Newsroom, doi:10.1117/2.1201302.004730 (2013)).

| Chip Name      | Measured quantity      | Application | Input<br>configuration | Technology   |  |

|----------------|------------------------|-------------|------------------------|--------------|--|

|                |                        | ILC Analog  |                        |              |  |

| FLC_SIPM       | Pulse charge           | HCAL        | Current input          | CMOS 0,8 µm  |  |

|                | <b>—</b>               | ATLAS       | •                      |              |  |

| MAROC          | Pulse charge, trigger  | luminometer | Current input          | SiGe 0,35 µm |  |

|                | Pulse charge, trigger, |             |                        |              |  |

| SPIROC         | time                   | ILC HCAL    | Current input          | SiGe 0,35 μm |  |

|                |                        |             | Differential           |              |  |

| NINO           | Trigger, pulse width   | ALICE TOF   | input                  | CMOS 0,25 µm |  |

|                | Pulse charge,          |             | Differential           |              |  |

| PETA           | trigger,time           | PET         | input                  | CMOS 0,18 µm |  |

|                |                        |             |                        |              |  |

| BASIC          | Pulse height, trigger  | PET         | Current input          | CMOS 0,35 µm |  |

| SPIDER         | Pulse height, trigger, |             |                        |              |  |

| (VATA64-HDR16) | time                   | SPIDER RICH | Current input          |              |  |

|                |                        |             |                        |              |  |

| RAPSODI        | Pulse height, trigger  | SNOOPER     | Current input          | CMOS 0,35 μm |  |

SiPM for HEP detectors

(Ref: Erika Garutti, Silicon photomultipliers for high energy physics detectors, Journal of Instrumentation, Volume 6, October 2011)

| Chip Name                | # of<br>channels | Digital<br>output | Power<br>supply | Area<br>[sqr mm] | Dynamic<br>range | Input<br>resistance | Timing<br>jitter | Year |

|--------------------------|------------------|-------------------|-----------------|------------------|------------------|---------------------|------------------|------|

| FLC_SIPM                 | 18               | n                 | 5V (0,2W)       | 10               |                  |                     | -                | 2004 |

| MAROC2                   | 64               | у                 | 5 V             | 16               | 80 p <i>C</i>    | 50 Ω                |                  | 2006 |

| SPIROC                   | 36               | у                 | 5 V             | 32               |                  |                     |                  | 2007 |

| NINO                     | 8                | n                 | (0,24W)         | 8                | 2000 pe          | 20 Ω                | 260 ps           | 2004 |

| PETA                     | 40               | у                 | (1,2W)          | 25               | 8 bit            |                     | 50 ps            | 2008 |

| BASIC                    | 32               | У                 | 3,3 V           | 7                | 70 p <i>C</i>    | 17 Ω                | ~120 ps          | 2009 |

| SPIDER<br>(VATA64-HDR16) | 64               | n                 |                 | 15               | 12 pC            |                     |                  | 2009 |

| RAPSODI                  | 2                | У                 | 3,3 V (0,2W)    | 9                | 100 p <i>C</i>   | 20 Ω                | -                | 2008 |

SiPM for HEP detectors

(Ref: Erika Garutti, Silicon photomultipliers for high energy physics detectors, Journal of Instrumentation, Volume 6, October 2011)

| Estimated Year of Production                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2007    | 2008   | 2009   | 2010   | 2011   | 2012   | 2013   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|--------|--------|--------|--------|--------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2001    | 2000   |        | 2010   |        |        |        |

| High Performance MPU properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |        |        |        |        |        |        |

| MPU/ASIC metal 1 1/2 pitch (nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68      | 59     | 52     | 45     | 40     | 36     | 32     |

| V <sub>dd</sub> (high performance) (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.1     | 1      | 1      | 1      | 1      | 0.9    | 0.9    |

| On chip local clock (MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9,285   | 10,972 | 12,369 | 15,079 | 17,658 | 20,065 | 22,980 |

| MTransistors per cm <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 357     | 449    | 566    | 714    | 899    | 1,133  | 1,427  |

| NMOS intrinsic delay τ (ps)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.64    | 0.54   | 0.46   | 0.4    | 0.34   | 0.29   | 0.25   |

| Clock Period (ps)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 108     | 91     | 81     | 66     | 66     | 50     | 44     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |        |        |        |        |        |        |

| Global Electronic Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |        |        |        |        |        |        |

| Minimum global pitch (nm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 210     | 177    | 156    | 135    | 120    | 108    | 96     |

| Conductor resistivity (µΩ-cm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.73    | 2.87   | 3      | 3.1    | 3.22   | 3.39   | 3.52   |

| RC for 1mm global wire (ps)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 209     | 316    | 410    | 523    | 687    | 787    | 977    |

| bit hop length: RC = clock period (µ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 719     | 537    | 444    | 355    | 310    | 252    | 211    |

| ave electron bit hops to cross chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24      | 33     | 39     | 49     | 56     | 69     | 83     |

| ave delay or latency (ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.6     | 3.0    | 3.2    | 3.3    | 3.7    | 3.5    | 3.6    |

| MTransistors within bit hop radius                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6       | 4      | 4      | 3      | 3      | 2      | 2      |

| Power for bits at clock speed (mW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.36    | 1.02   | 0.91   | 0.83   | 0.72   | 0.55   | 0.50   |

| Energy per bit per hop (pJ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.147   | 0.093  | 0.074  | 0.055  | 0.048  | 0.028  | 0.022  |

| Bit flux/Watt (Tbit/sec/cm/W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.140   | 0.166  | 0.172  | 0.186  | 0.186  | 0.261  | 0.276  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |        |        |        |        |        |        |

| Global Photonic Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4 0 0 7 | 4.404  | 4.445  | 4.040  | 000    | 070    | 0.4.0  |

| Meindl partition length ( $\mu$ ), N=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1,287   | 1,184  | 1,115  | 1,010  | 933    | 876    | 818    |

| Light speed * clock period/3 (µ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10,800  | 9,100  | 8,100  | 6,600  | 6,600  | 5,000  | 4,352  |

| ave hops to chip edge for photons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2       | 2      | 2      | 3      | 3      | 4      | 4      |

| Mtransistors within photon hop radius                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1,308   | 1,168  | 1,166  | 977    | 1,230  | 889    | 849    |

| ave delay or latency (ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.09    | 0.09   | 0.09   | 0.09   | 0.09   | 0.09   | 0.09   |

| Energy per bit to cross chip (aJ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90      | 90     | 90     | 90     | 90     | 90     | 90     |

| Potential Bit flux/Watt (Pbit/sec/cm/W)   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11   11 |         |        |        |        |        |        |        |

| (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |        |        |        |        |        |        |

Photonic Interconnect Comparison (Ref: Raymond G. Beausoleil et al. Proceedings of the IEEE, Vol. 96, No. 2, February 2008)

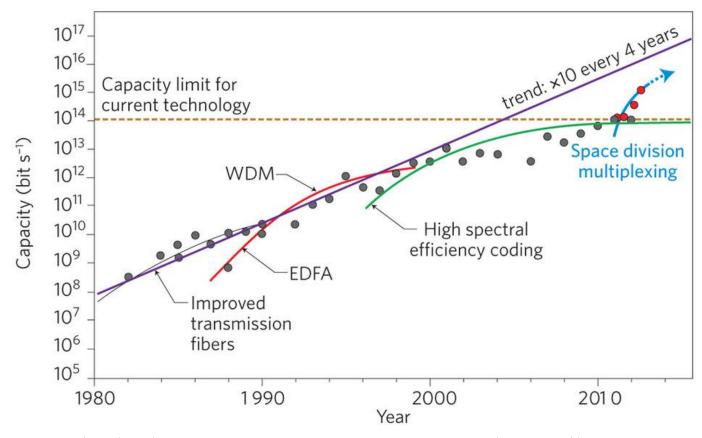

The data points represent the highest capacity transmission numbers (all transmission distances considered) reported at the post-deadline sessions of the annual Optical Fiber Communications Conference over the period 1982 to the present. The transmission capacity of a single fibre increases by a factor of approximately 10 every four years. Key previous technological breakthroughs include the development of low-loss SMFs, the EDFA, WDM and high-spectral-efficiency coding through DSP-enabled coherent transmission. The data points for SDM also include results from the post-deadline session of the annual European Conference on Optical Communications in 2011 and 2012. SDM seems poised to provide the next big jump in transmission capacity.

(Ref: D. J. Richardson, J. M. Fini & L. E. Nelson, Nature Photonics 7, 354–362 (2013) doi:10.1038/nphoton.2013.94 Published online 29 April 2013)

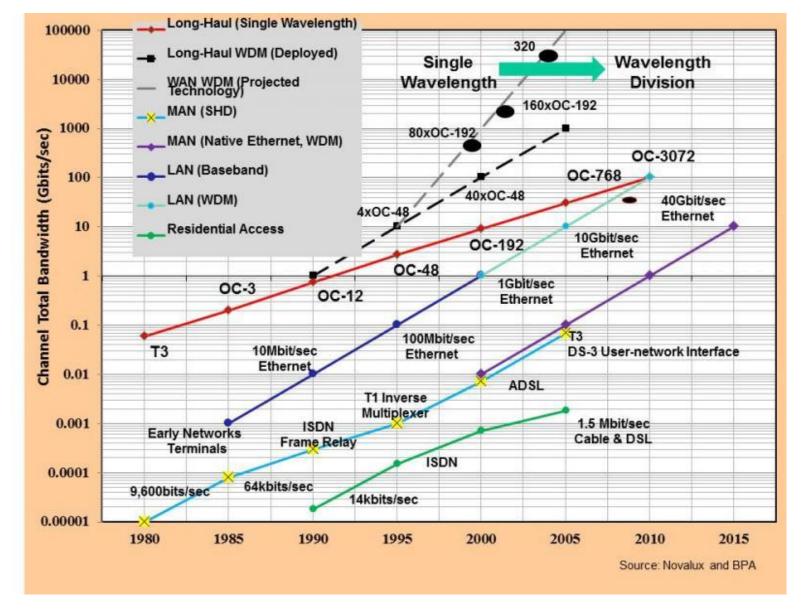

Projected high-speed I/O data bandwidth trends for popular communication standards. (Ref: ITRS <u>http://www.itrs.net/</u>)

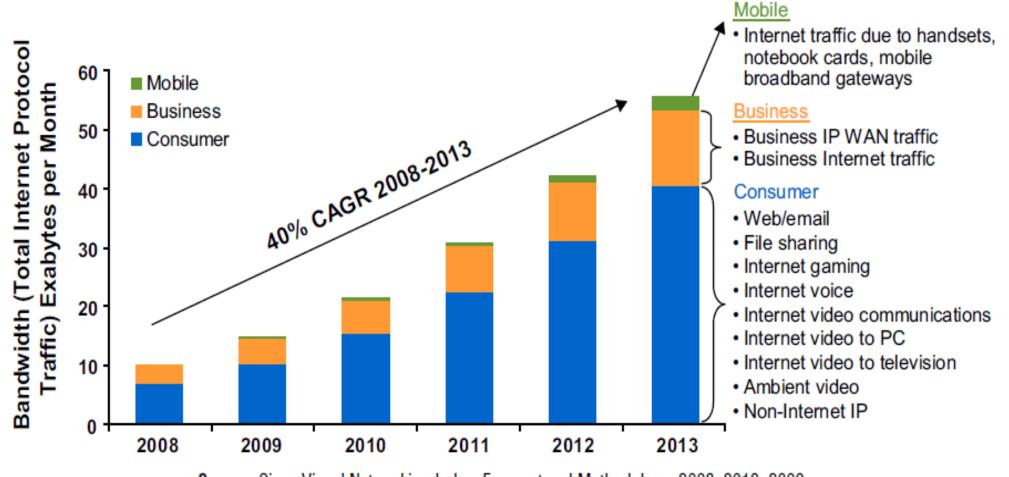

Source: Cisco Visual Networking Index: Forecast and Methodology, 2008–2013, 2009

Global Internet Protocol Traffic Growth, 2008–2013

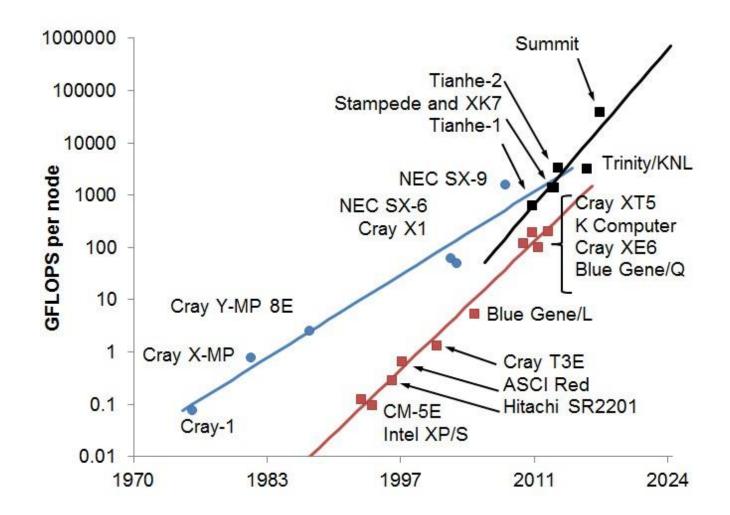

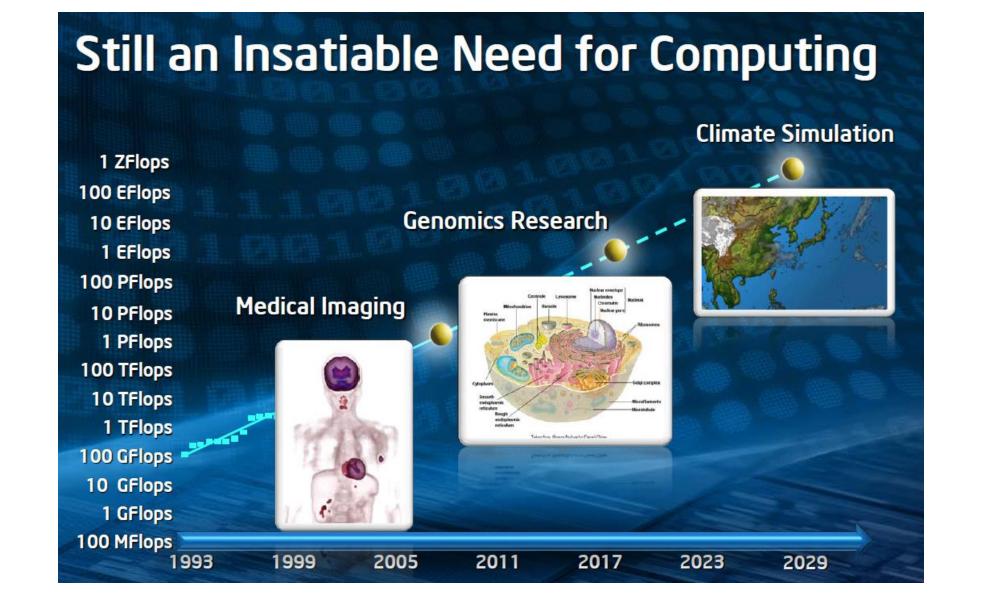

Exascale HPC evolution. The blue line shows the trend for vector machines, the first supercomputers, and the red line for massively parallel machines, which followed them architecturally. The black line shows the more modern hybrid, many core machine.

(Ref: The National Energy Research Scientific Computing Center (NERSC), US, 2015, https://www.nersc.gov/about/)

# Dreams (various technologies)

Device • . FET Extension SET FET [A] 1D structures Channel Molecular Ferromagnetic Spin transistor replacement logic Typical example devices Si CMOS CNT FET SET Spin Gain III-V compound Crossbar latch Moving domain semiconductor and wall transistor NW FET Molecular Ge channel transistor M: QCA NW heteroreplacement Molecular OCA Spin FET structures Nanoribbon transistors with Spin Torque graphene Transistor Cell Size Projected 100 nm300 nm [I] 40 nm [O] 10 nm [U] 140 nm [Y] 100 nm [C] 100 nm [D] (spatial Demonstrated pitch) [B] 590 nm ~1.5 µm [E] 1700 nm [J] ~200 nm [K, L] ~2 µm [V] 250 nm [Z, AA] 100 µm [AB] Density Projected 1E10 4.5E9 6.1E9 6E10 1E12 5E9 4.5E9 4E7 ~2E9 (device/cm<sup>2</sup>) 2.8E8 3.5E7 2E7 1.6E9 1E4 Demonstrated 6.3 THz [F] 10 THz [Q] 40 GHz [AC] 12 THz >1 THz 1 THz [W] 1 GHz [Y] Projected Switch Speed Demonstrated 1.5 THz 200 MHz [G] >300 GHz 2 THz [R] 100 Hz [V] 30 Hz [Z, AA] Not known 61 GHz 61 GHz [C] 61 GHz [C] 1 GHz [O] 1 GHz [U] 10 MHz [Y] Not known Projected Circuit Speed Demonstrated 5.6 GHz 220 Hz [H] Data not available 1 MHz [P] 100 Hz [V] 30 Hz [Z] Not known 1×10<sup>-18</sup> [O] 3E-18 3.00E-18 5E-17 [X] 3E-18 Projected 3E-18 ~1E-17 [Z] [>1.5×10<sup>-17</sup>][S] 8×10<sup>-17</sup>[T] Switching Energy, J 1E-16 1E-11 [H] 1E-16 [J] 3E-7 [V] 6E-18 [AA] Not known Demonstrated [>1.3×10<sup>-14</sup>][S] Binary Projected 238 238 61 10 1000 5E-2 Not known Throughput, Demonstrated 1.6 1E-8 Data not available 2E-4 2E-9 5E-8 Not known GBit/ns/cm RT [M, N] RT RT RT Operational Temperature RT RT RT CNT. Si, III-V. Si, Ge, III-V. InGaAs, InAs, Ferromagnetic Organic Materials System Si III-V, Si, Ge, complex metals molecules InSb alloys In2O3, ZnO, TiO2, oxides SiC, Research Activity [AD] 379 62 91 244 32 122

Table ERD7a Emerging Research Logic Devices—Demonstrated and Projected Parameters

#### (Ref: ITRS <u>http://www.itrs.net/reports.html</u>)

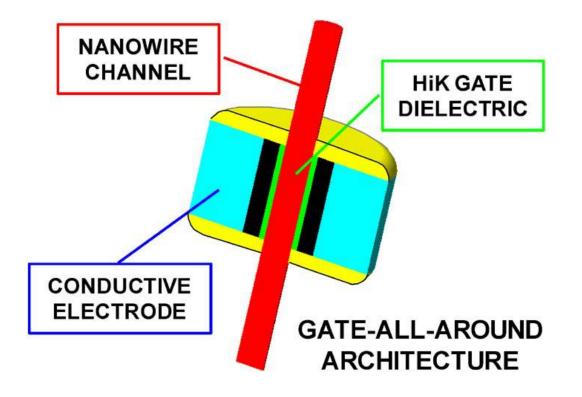

Ultimate CMOS Device with a nanowire channel, a gate-all-around (GAA) architecture, a high-k gate dielectric, and a conductive gate electrode stack. The minimum channel dimensions will be determined by quantum confinement effects and scattering at atomic dimensions. The nanowire architecture is determined by electrostatic requirements to achieve the best possible short-channel control. Each of the various gate layers (interface layer (IL), high-k layer, threshold voltage (VT) control layer, primary work function layer, conduction layer, and so on) is limited by material properties at atomic dimensions.

(Ref: Kelin J. Kuhn, IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 59, NO. 7, JULY 2012)

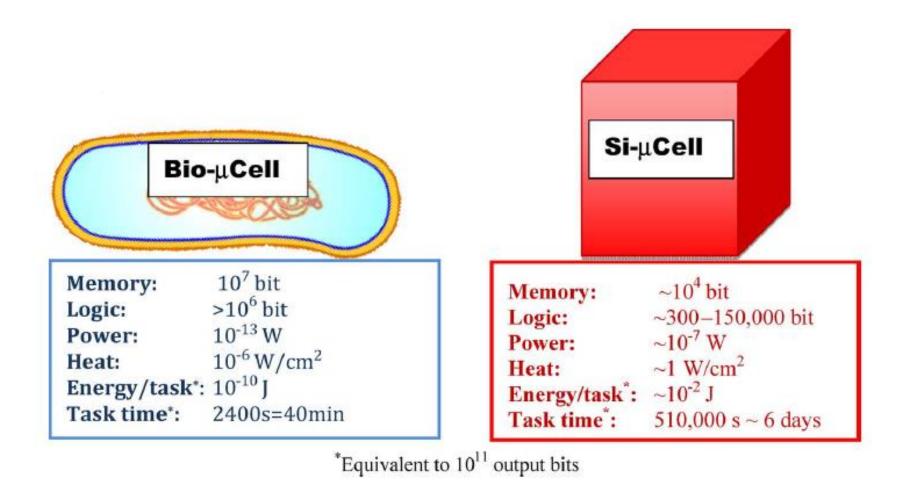

Comparison of significant parameters of the bio-µcell and the Si-µcell.

(Ref: Cavin et al, Science and Engineering Beyond Moore's Law, Proceedings of the IEEE | Vol. 100, May 13th, 2012)

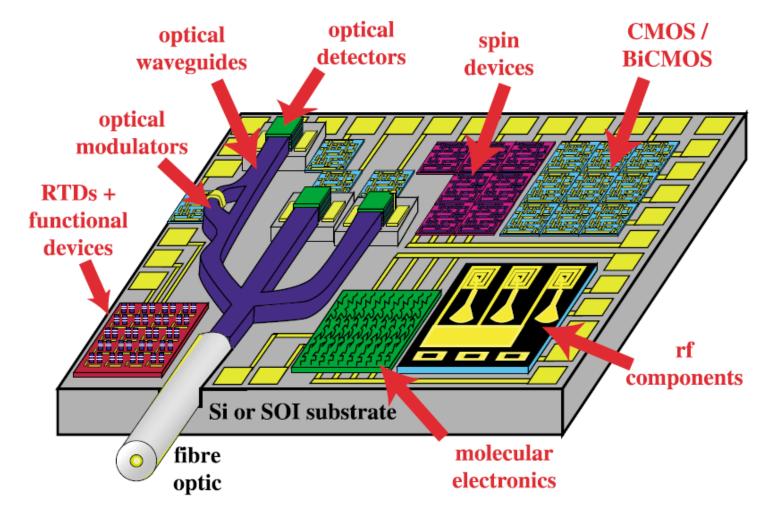

The system-on-a-chip of the future? The ability to integrate new technologies with CMOS or BiCMOS is important but may be too expensive for some technologies or suffer technological problems such as crosstalk like rf solutions. Multi-chip modules may therefore be a more adequate solution for specific applications.

(Ref: European Commission, IST programme, Future and Emerging Technologies, Technology Roadmap for Nanoelectronics, Second Edition, November 2000, Editor: R. Compañó, <u>http://nanotech.law.asu.edu/Documents/2009/09/fetnidrm\_239\_7700.pdf</u>)

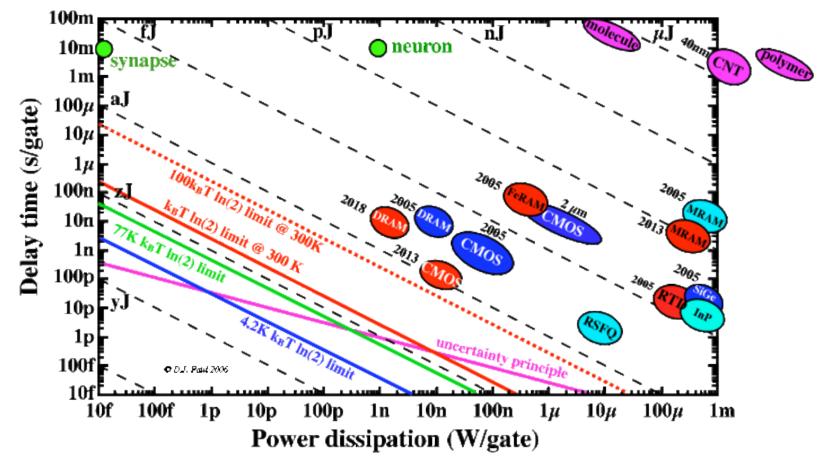

The above figure plots the delay time per transistor (using CVDD/Ion) versus the power dissipation (Ion VDD for the transistors) using either a CMOS inverter, a n-MOS inverter or a p-MOS inverter as appropriate for the technology. To provide a fair comparison, a noise margin required to transmit 1 bit of information down a 1 mm long level-7 interconnect made of copper from a CMOS processor has been assumed for the logic so that the correct scaling of gate width can be accounted for. All devices use EXTRINSIC I-V characteristics from the literature since for CMOS most of the performance limitations are related to contact resistivity, access resistance, parasitic RC time constants etc...... Therefore all comparisons are fair for making circuits from the technology base.)

Semiconductor Group, Glasgow University, (http://userweb.eng.gla.ac.uk/douglas.paul/SiGe/limits.html)

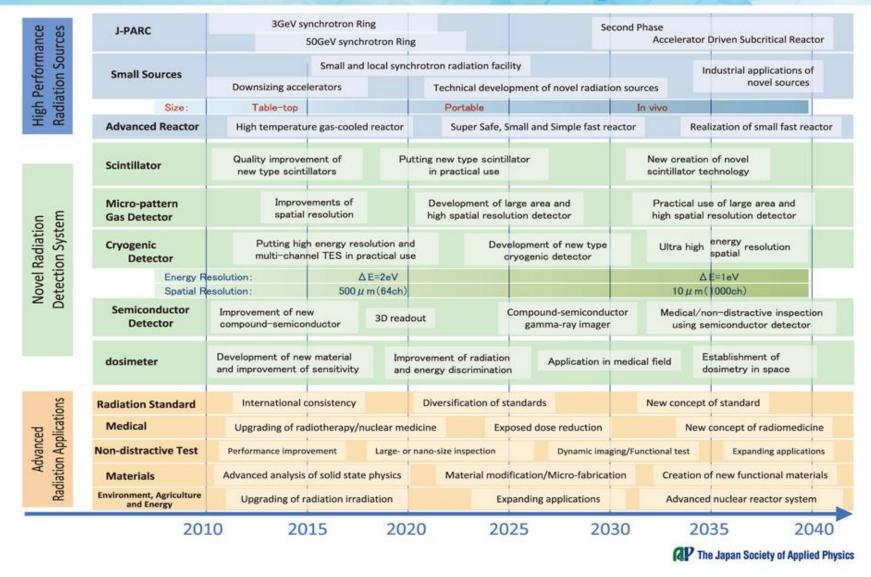

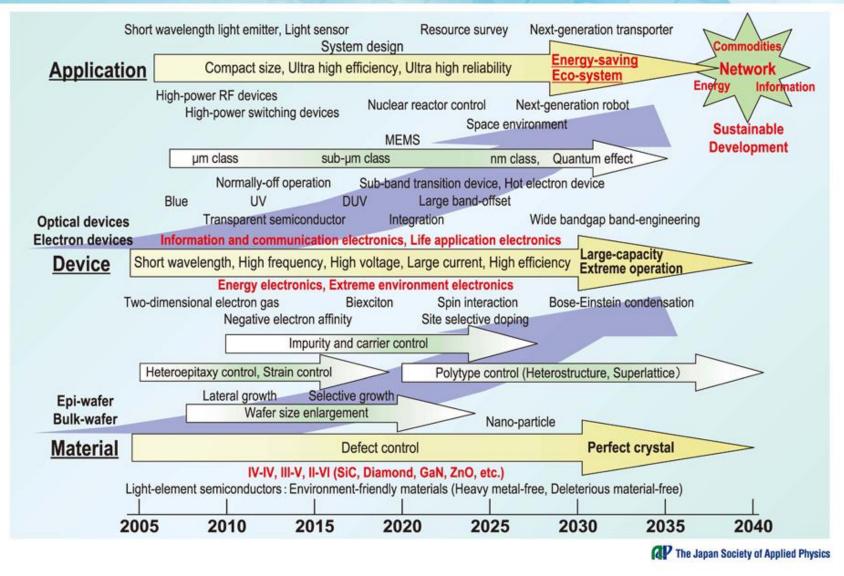

### **Radiation science and engineering**

Japan Society of Applied Physics (Academic Roadmap https://www.jsap.or.jp/english/aboutus/academic-roadmap.html)

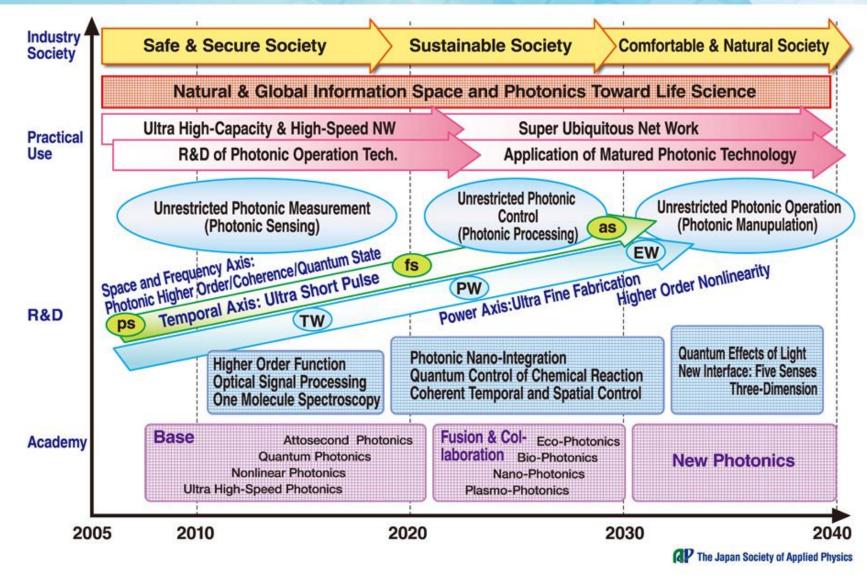

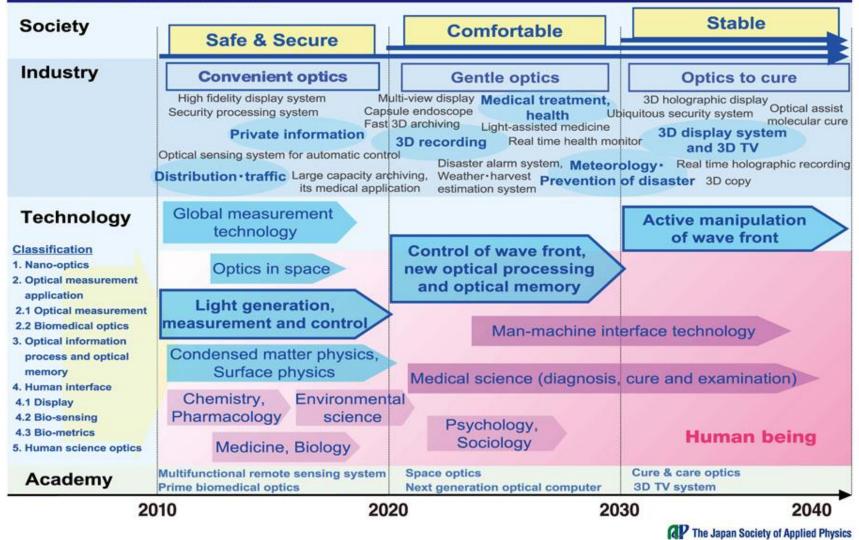

### **Photonics**

| Estimated Year of Production                | 2014   | 2015   | 2016   | 2017   | 2018   | 2019   | 2020   |

|---------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| Estimated real of roduction                 | 2014   | 2010   | 2010   | 2017   | 2010   | 2010   | 2020   |

| High Performance MPU properties             |        |        |        |        |        |        |        |

| MPU/ASIC metal 1 1/2 pitch (nm)             | 28     | 25     | 22     | 20     | 18     | 16     | 14     |

| V <sub>dd</sub> (high performance) (V)      | 0.8    | 0.8    | 0.8    | 0.7    | 0.7    | 0.7    | 0.7    |

| On chip local clock (MHz)                   | 22,980 | 33,403 | 39,683 | 39,683 | 53,207 | 62,443 | 73,122 |

| MTransistors per cm <sup>2</sup>            | 1,798  | 2,265  | 2,854  | 3,596  | 4,537  | 5338   | 7193   |

| NMOS intrinsic delay τ (ps)                 | 0.21   | 0.18   | 0.15   | 0.13   | 0.11   | 0.1    | 0.08   |

| Clock Period (ps)                           | 44     | 30     | 25     | 25     | 19     | 16     | 14     |

|                                             |        |        |        |        |        |        |        |

| Global Electronic Interconnect              |        |        |        |        |        |        |        |

| Minimum global pitch (nm)                   | 84     | 75     | 66     | 60     | 54     | 48     | 42     |

| Conductor resistivity (μΩ-cm)               | 3.73   | 3.93   | 4.2    | 4.39   | 4.58   | 4.93   | 5.38   |

| RC for 1mm global wire (ps)                 | 1353   | 1601   | 2210   | 2794   | 2983   | 4064   | 5795   |

| bit hop length: RC = clock period ( $\mu$ ) | 179    | 137    | 107    | 95     | 79     | 63     | 49     |

| ave electron bit hops to cross chip         | 98     | 128    | 164    | 184    | 220    | 279    | 360    |

| ave delay or latency (ns)                   | 4.2    | 3.8    | 4.1    | 4.6    | 4.1    | 4.5    | 4.9    |

| MTransistors within bit hop radius          | 2      | 1      | 1.0    | 1.0    | 0.9    | 0.7    | 0.5    |

| Power for bits at clock speed (mW)          | 0.34   | 0.33   | 0.31   | 0.21   | 0.20   | 0.18   | 0.17   |

| Energy per bit per hop (pJ)                 | 0.015  | 0.010  | 0.008  | 0.005  | 0.004  | 0.003  | 0.002  |

| Bit flux/Watt (Tbit/sec/cm/W)               | 0.349  | 0.390  | 0.390  | 0.509  | 0.614  | 0.614  | 0.614  |

| Global Photonic Interconnect                |        |        |        |        |        |        |        |

| Meindl partition length (µ), N=1            | 818    | 679    | 623    | 623    | 538    | 496    | 459    |

| Light speed * clock period/3 (µ)            | 4,352  | 2,994  | 2,520  | 2,520  | 1,879  | 1,601  | 1,368  |

| ave hops to chip edge for photons           | 4      | 6      | 7      | 7      | 9      | 11     | 13     |

| Mtransistors within photon hop radius       | 1,069  | 637    | 569    | 717    | 503    | 430    | 422    |

| ave delay or latency (ns)                   | 0.09   | 0.09   | 0.09   | 0.09   | 0.09   | 0.09   | 0.09   |

| Energy per bit to cross chip (aJ)           | 90     | 90     | 90     | 90     | 90     | 90     | 90     |

| Potential Bit flux/Watt (Pbit/sec/cm/W)     | 11     | 11     | 11     | 11     | 11     | 11     | 11     |

| (b)                                         |        |        |        |        |        |        |        |

Photonic Interconnect Comparison (Ref: Raymond G. Beausoleil et al. Proceedings of the IEEE, Vol. 96, No. 2, February 2008)

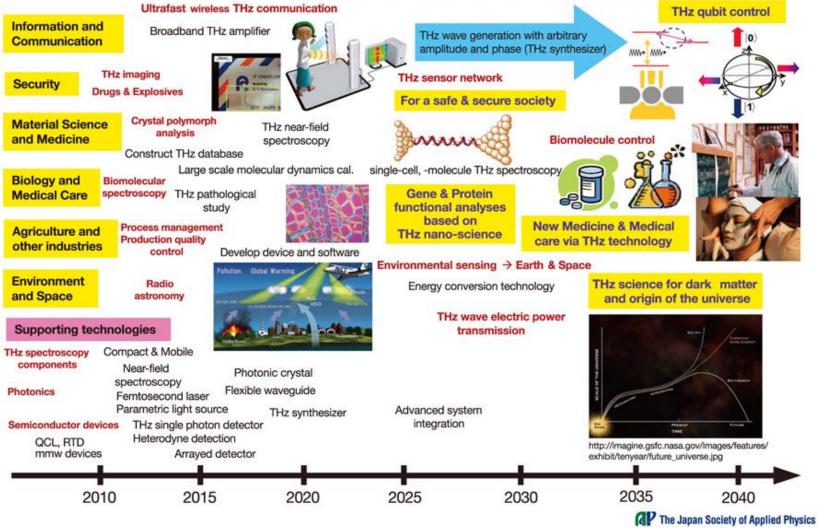

### **Terahertz Electronics**

### **Vision of the future of Terahertz Electronics**

### **Widegap Semiconductor Electronics**

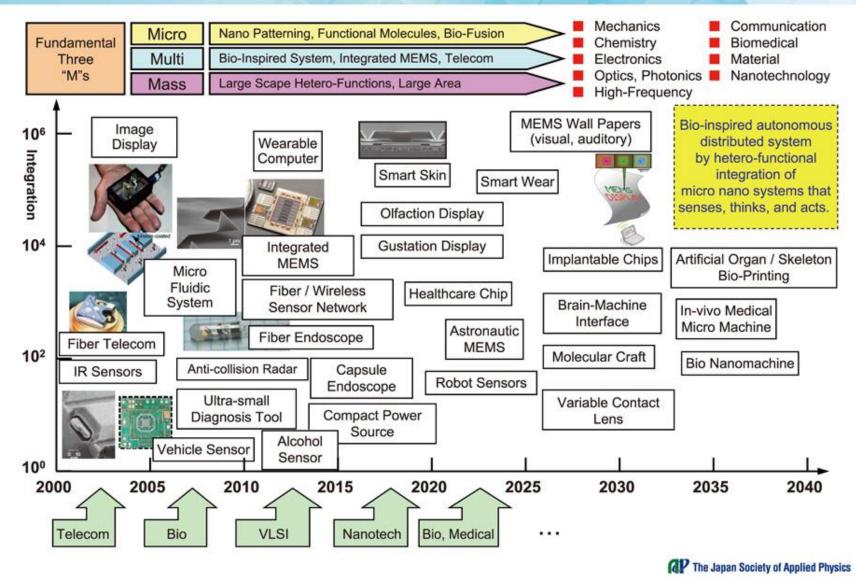

### **Micro/Nano-Mechatronics**

# **Optics**

### **Optics open the future !**

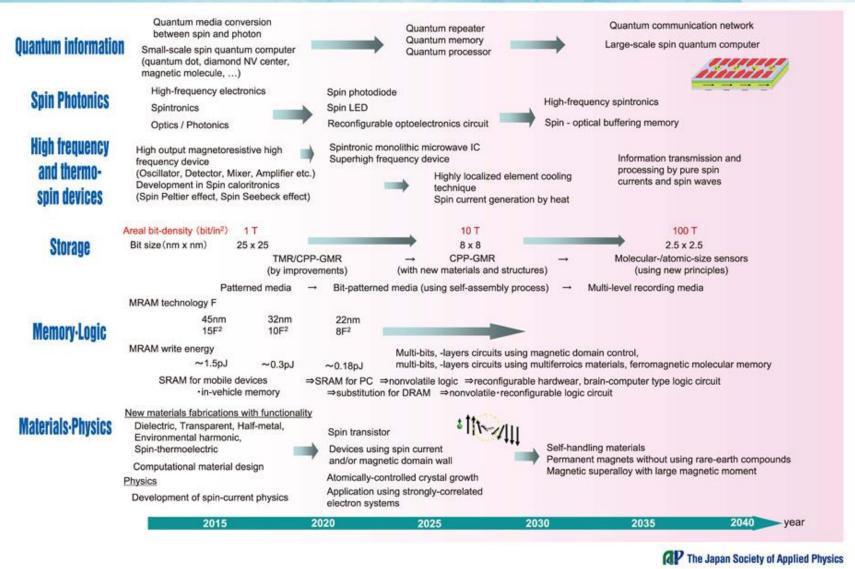

## **Spintronics**

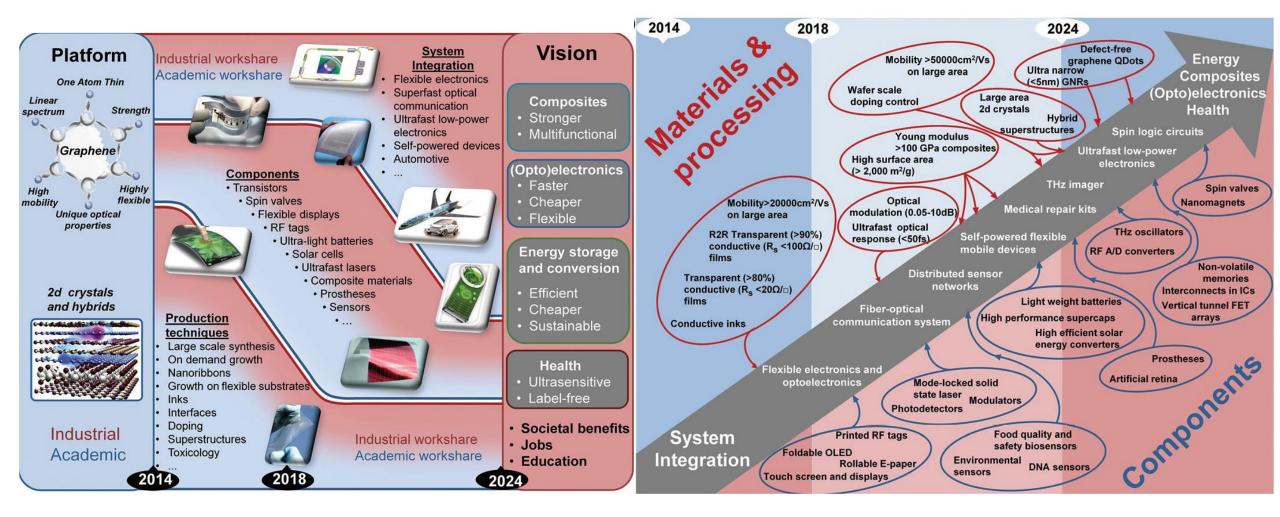

European Technology Roadmap for Graphene

(Ref: Andrea C. Ferrari et. al, Nanoscale, 2015, 7, 4598-4810)

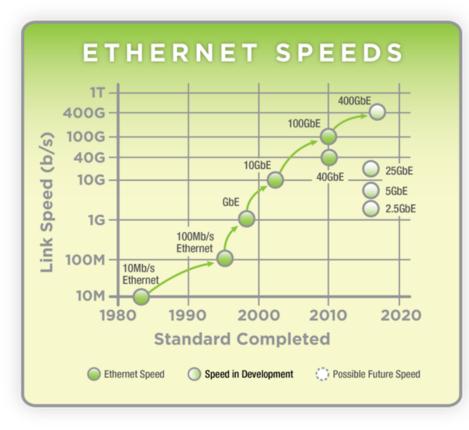

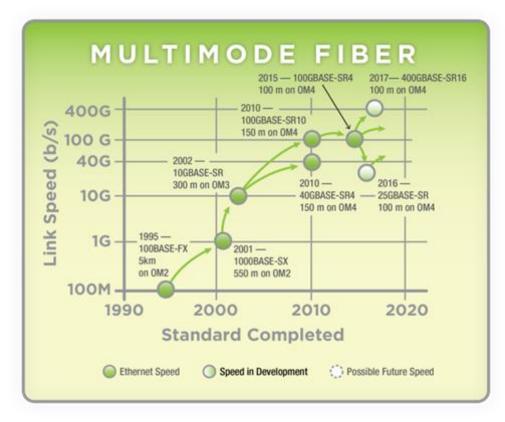

#### The 2015 Ethernet Roadmap

(Ref: The Ethernet Alliance, <u>http://www.ethernetalliance.org/roadmap/</u>)

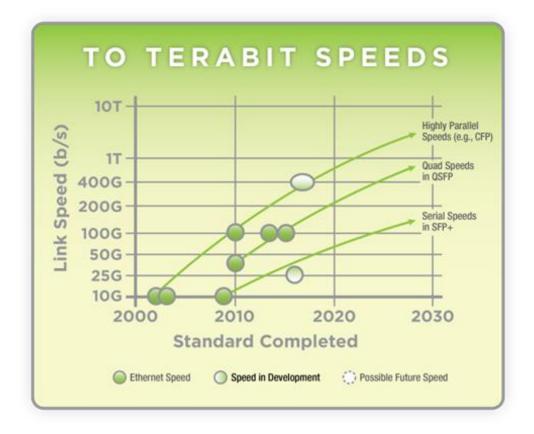

#### The 2015 Ethernet Roadmap

(Ref: The Ethernet Alliance, <u>http://www.ethernetalliance.org/roadmap/</u>)

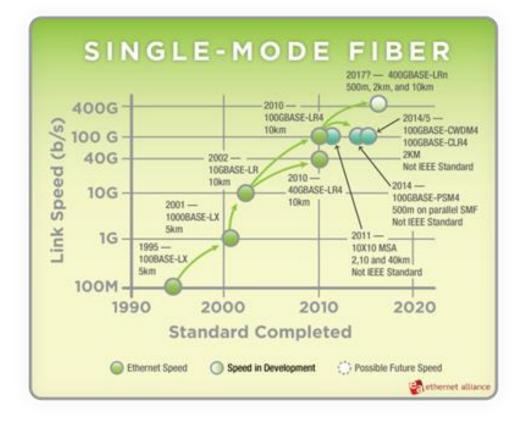

### The 2015 Ethernet Roadmap

(Ref: The Ethernet Alliance, <u>http://www.ethernetalliance.org/roadmap/</u>)

|                                        | Petascale system<br>(2012) | Exascale / data center<br>(2020) | Petascale /<br>departmental (2020) | Terascale /<br>embedded (2020) |

|----------------------------------------|----------------------------|----------------------------------|------------------------------------|--------------------------------|

| Number of nodes                        | [3-8] x10^3                | [50-200] x10^3 (20x)             | [50-100]                           | 1                              |

| Computation (Flop/s & Instructions)    | 10^15                      | 10^18 (1000x)                    | 10^15                              | 10^12                          |

| Memory Capacity (B)                    | [1-2] x10^14               | > 10 ^17 (1000x)                 | > 10^14                            | > 10^11                        |

| Global Memory bandwidth (B/s)          | [2-5] x10^14               | > 10^17 (1000x)                  | > 10^14                            | > 10^11                        |

| Interconnect bisection bandwidth (B/s) | [5-10] x10^13              | ~10^16 (1000x)                   | ~10^13                             | N/A                            |

| Storage Capacity (B)                   | [1-10] x10^15              | >10^18 (1000x)                   | > 10^15                            | > 10^12                        |

| Storage bandwidth (B/s)                | [10-500] x10^9             | > 10 x10^12 (1000x)              | > 10 x10^9                         | > 10^6                         |

| IO operations/s                        | 100 x10^3                  | > 100 x10^6 (1000x)              | > 100 x10^3                        | > 100                          |

| Power Consumption (W)                  | [.5-1.] x10^6              | < 20 x10^6 (20x)                 | < 20 x10^3                         | < 20                           |

HPC Expected system characteristic 2020

(Ref: The European Technology Platform for High Performance Computing <u>http://www.etp4hpc.eu/publications/key-documents/</u>)

|                                     | Traditional technologies           |                                 |                                                                              | Emerging technologies |                                                  |                   |                                                      |  |

|-------------------------------------|------------------------------------|---------------------------------|------------------------------------------------------------------------------|-----------------------|--------------------------------------------------|-------------------|------------------------------------------------------|--|

| Memory type                         | DRAM                               | SRAM                            | NAND                                                                         | FeRAM                 | STT-MRAM                                         | PCRAM             | ReRAM                                                |  |

| Physical effect<br>at work          | Silicon                            | Silicon                         | Tunnel effect                                                                | Ferroelectrics        | advanced<br>Spintronics                          | Phase-Change      | Redox /<br>Memristor                                 |  |

| Technology status                   | Mature                             |                                 |                                                                              | product               | products being<br>introduced                     | 1st<br>Generation | Research                                             |  |

| Read time (ns)                      | <1                                 | <0.3                            | <50                                                                          | <45                   | <20                                              | <60               | <50                                                  |  |

| Write erase time(ns)                | <0.5                               | <0.3                            | 10^6                                                                         | 10                    | 10                                               | 60                | <250                                                 |  |

| Retention time (years)              | N/A                                | N/A                             | >10                                                                          | >10                   | >10                                              | >10               | >10                                                  |  |

| Write endurance<br>(nb of cycles)   | 10^16                              | 10^16                           | 10^5                                                                         | 10^14                 | 10^16                                            | 10^9              | 10^15                                                |  |

| Density (Gbit/cm2)                  | 6.67                               | 0.17                            | 2.47                                                                         | 0.14                  | 1                                                | 1.48              | 250                                                  |  |

| Technology potential<br>scalability | Major<br>technological<br>barriers |                                 |                                                                              | Limited               | Promising                                        | Promising         | Promising                                            |  |

| Exascale<br>applicability           | No recognised<br>alternative       | Potential to scale<br>suitably? | e Tech barriers and<br>endurance, may<br>be overtaken by<br>other NV devices | ·                     | Promising,<br>potential<br>successor for<br>DRAM | Very Promising    | Unclear,<br>potential as<br>compatible<br>SoC device |  |

Expected memory characteristics ranges in 2020

(Ref: The European Technology Platform for High Performance Computing <u>http://www.etp4hpc.eu/publications/key-documents/</u>)

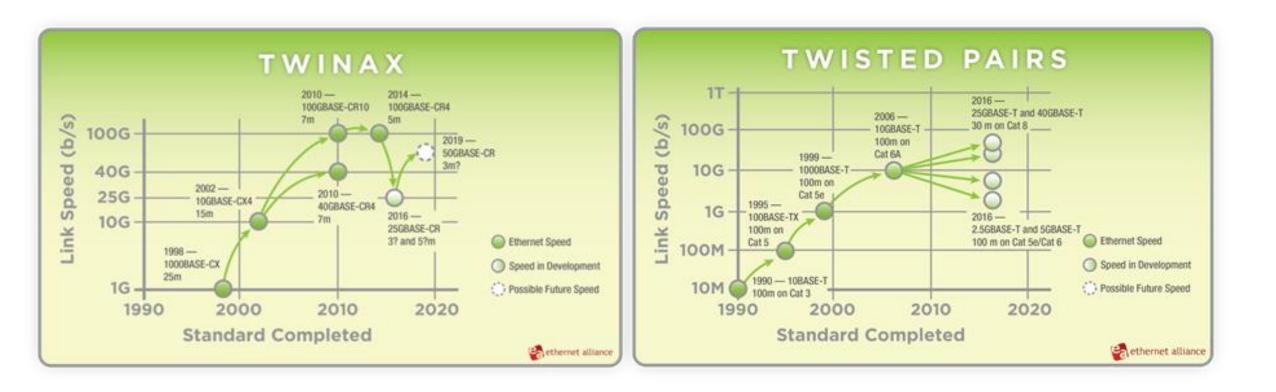

#### Next Generation Computing Roadmap

(Ref: Study carried out for the European Commission by eutema GmbH (Austria) in co – operation with Optimat, EPCC and 451 Research, 2014, <u>https://ec.europa.eu/digital-</u> <u>agenda/en/news/next-generation-</u> <u>computing-roadmap</u>)