# The Belle II DEPFET vertex detector: current status and future plans

Carlos Mariñas University of Bonn

On behalf of the DEPFET Collaboration

cmarinas@uni-bonn.de

#### Outline

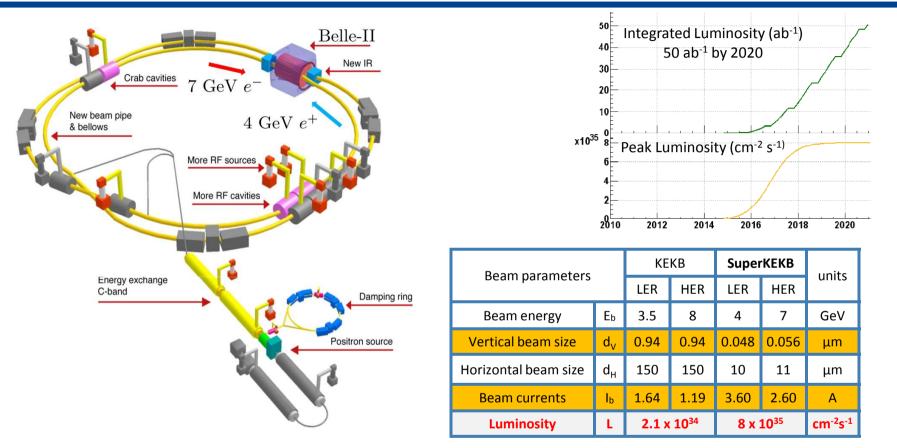

## **KEKB upgrade plan: SuperKEKB Flavour Factory**

- Asymmetric energy (4 GeV, 7 GeV) e<sup>+</sup>e<sup>-</sup> collider at the  $E_{cm} = m(\Upsilon(4S))$  to be realized by upgrading the existing KEKB machine

- Final luminosity  $8\cdot 10^{35}cm^{-2}s^{-1}$  , 40 times higher than the existing KEKB Factory

- Luminosity will be achieved by squeezing the beams (nano beam)

Belle II PXD group has decided on DEPFET as baseline

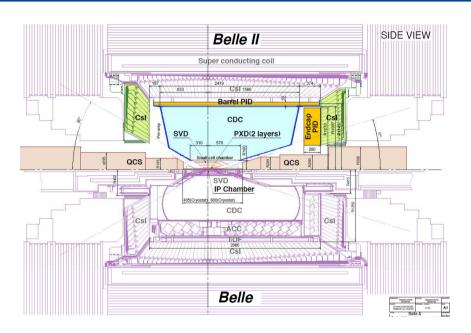

## **Belle II Silicon Vertex Detector**

|                   | Belle | Belle II |

|-------------------|-------|----------|

| # layers          | 4     | 6        |

| Inner radius (cm) | 1.5   | 1.4      |

| Outer radius (cm) | 8     | 14       |

At such high luminosity, we will collect higher number of events but...

• Higher background

$\rightarrow$ Radiation damage and occupancy and fake hits

• Higher event rate

$\rightarrow$  Higher rate trigger, DAQ and computing

DEPFETs for the two innermost layers (L0+L1)

cmarinas@uni-bonn.de

|                | Belle II                     |  |

|----------------|------------------------------|--|

| Occupancy      | 0.4 hits/µm²/s               |  |

| Radiation      | > 1Mrad/year                 |  |

| Frame time     | 20 μs (continuous r.o. mode) |  |

| Momentum range | Low momentum (< 1GeV)        |  |

| Acceptance     | 17°-155°                     |  |

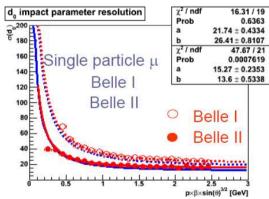

The combination of resolution, mass and power is a substantial challenge

> Required spatial resolution (~10µm) → Moderate pixel size (50 x 50 µm<sup>2</sup>)

> Lowest possible material budget (0.19%  $X_0$ /layer)

$\rightarrow$  The DEPFET technology can cope with this challenging requirements

Tight schedule to develop a complete detector system by 2015

#### 6

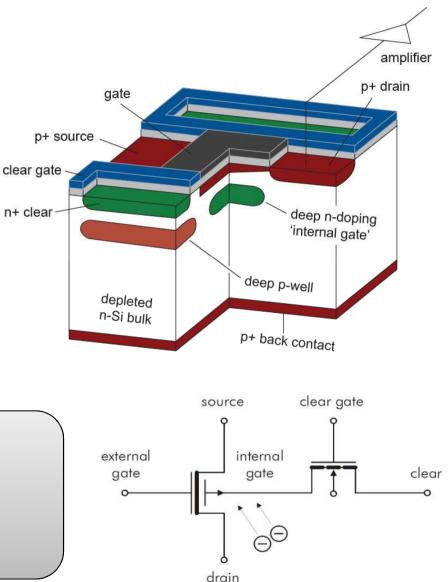

#### Detection and internal amplification

- Good signal-to-noise ratio

- Low power consumption

- $\succ$  Thin detectors

- Accumulated charge can be removed by a clear contact

- > Signal electrons accumulate in the internal gate and modulate the transistor current (g<sub>a</sub>≈400pA/e<sup>-</sup>)

gate)

depleted bulk (sideward depletion). Charge is collected by drift > A deep n-implant creates a potential

Each pixel is a p-channel FET on a completely

minimum for electrons under the gate (internal

## DEPFET – DEpleted P-channel Field Effect Transistor

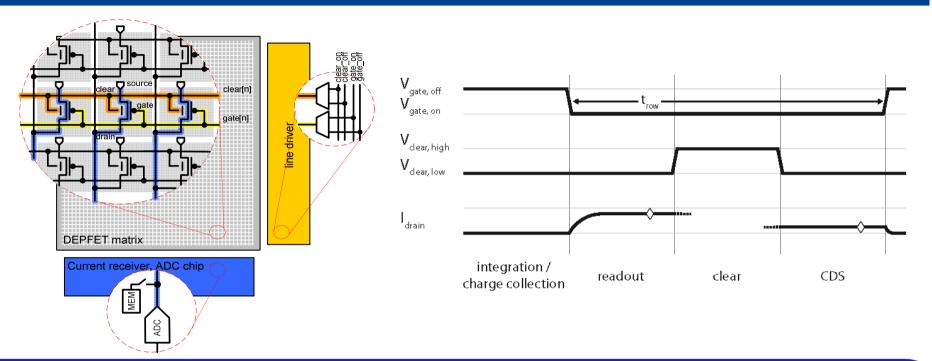

#### **Operation mode: Row wise readout**

#### Row wise readout (Rolling Shutter)

- (If CDS) Select a row, read the current, clear the DEPFET and read the current again. The difference is the signal.

- Single sampling with pedestal substraction afterwards (Baseline)

- Low power consumption: Only one row is active at a time; Readout on demand.

- Steering chips needed (Switchers) and limited frame rate.

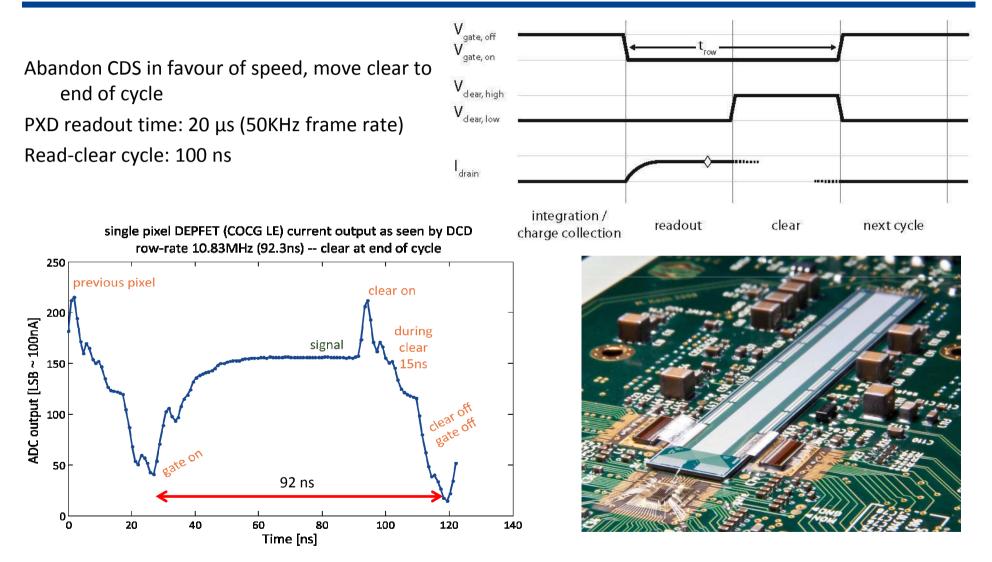

## Single sampling

92 ns row time. The sampling could be even reduced further without compromising the signal settling

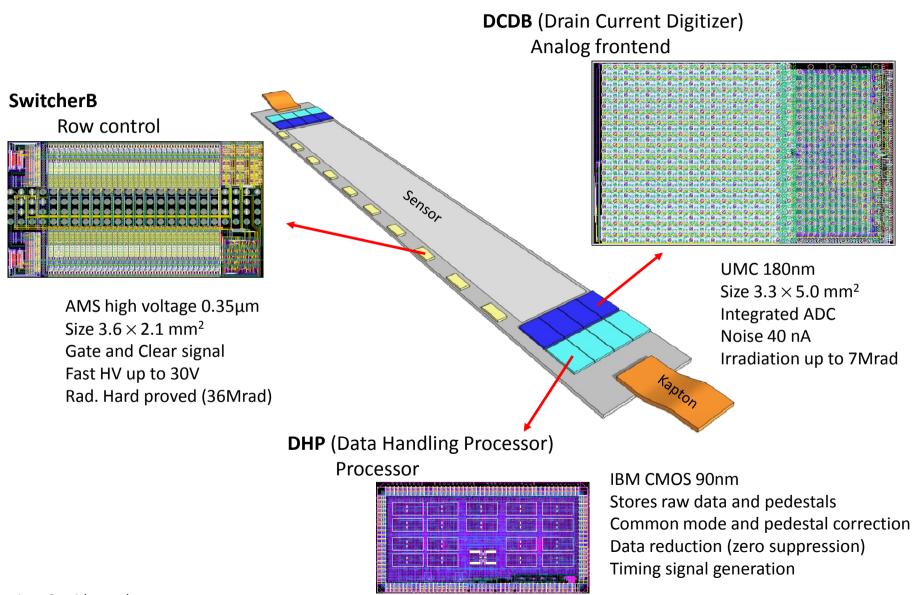

#### **DEPFET auxiliary ASICs**

**DHH** (Data Handling Hybrid): interface of the ladders with the outside world Impedance matching **Electrical - optical interface** Power regulation to other half regulator modules Slow control master (JTAG) power supplies patch panel F0/x, trigger, abort clock from machine local power regulation half module pp **FPGA** from/to other Gbit eth compute half modules node opto < 20 cm  $\leftrightarrow$ TX/RX opto links flex cable 40 DHH 40 20 half modules ~ (O)m ATCA shelf 10-20m?

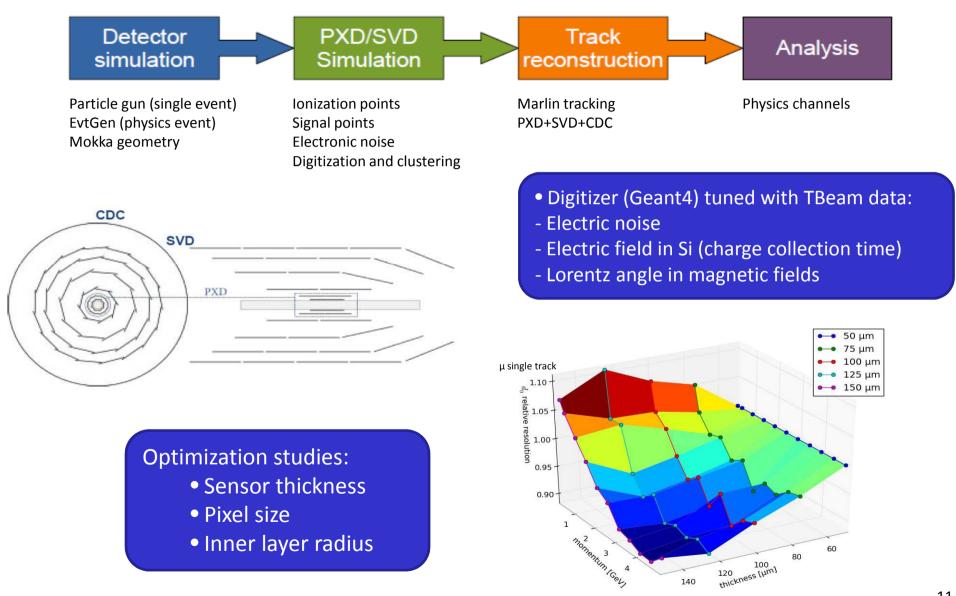

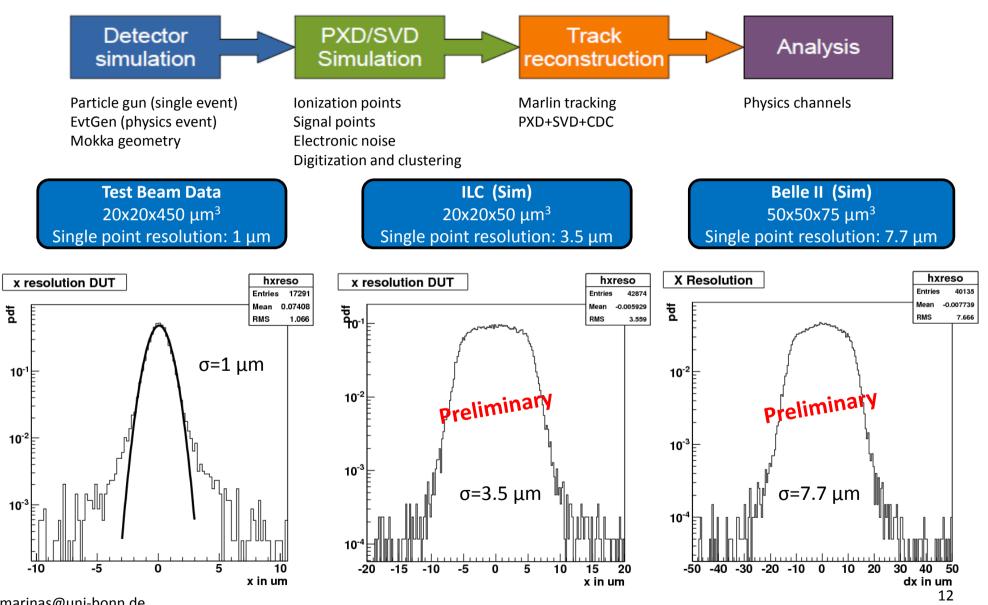

#### **Optimization: Full simulation chain**

#### **Optimization: Full simulation chain**

cmarinas@uni-bonn.de

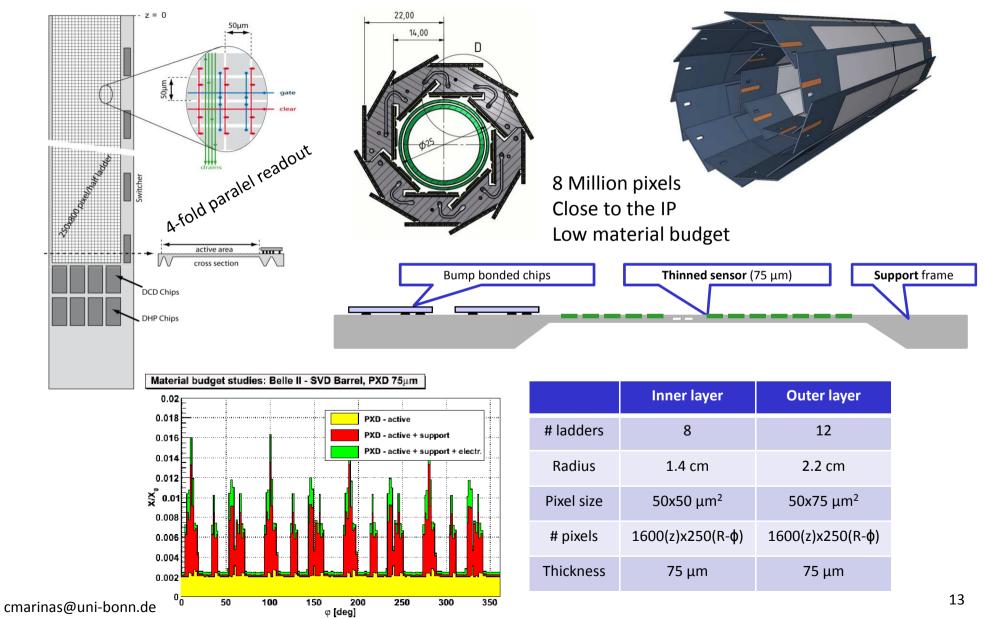

#### The Belle II PXD layout

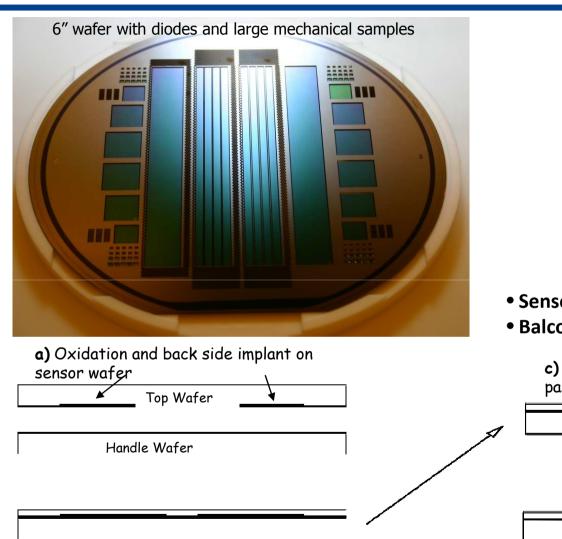

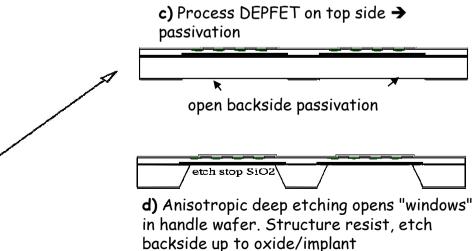

## **Thinning technology**

**b)** Wafer bonding and grinding/polishing of top wafer. Thin sensor side to desired thickness

- Sensor: Thinned down to 75µm

- Balconies: Etched grooves

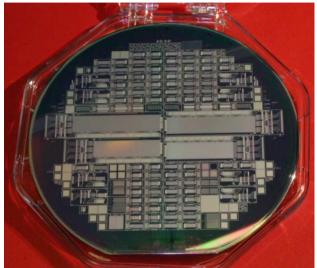

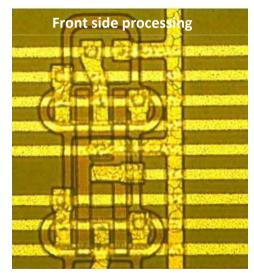

#### **PXD6 prototype production**

8 wafers with 50  $\mu m$  thin sensors

- $\bullet$  Small test matrices to test different pixel sizes from 50 to 200  $\mu m$

- Design variations: short gate lengths, clear structures

- Full size sensors –half ladders for prototyping

- Technology variations on the wafer level

90 steps fabrication process: 9 Implantations 19 Lithographies 2 Poly-layers 2 Alu-layers Back side processing

#### First thin DEPFET sensors produced!

cmarinas@uni-bonn.de

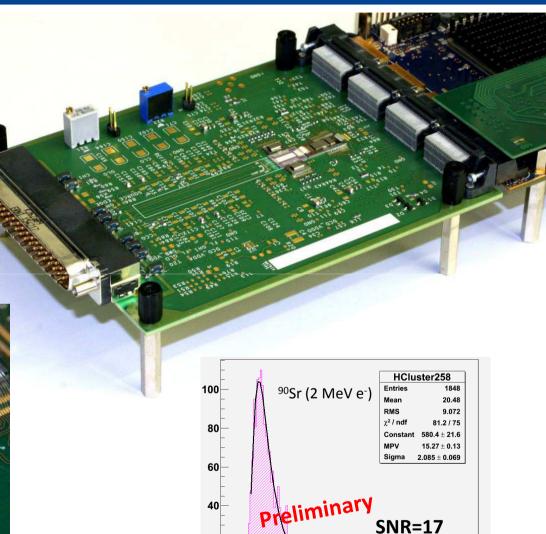

#### **Test platform**

Belle II design Sensor 32x64 pixels 50x75x50 μm<sup>3</sup> SWB and DCDB at full speed DCDB readout at 320MHz 100 ns row time

#### **Close to final specs!**

20

0<mark>0</mark>

(not optimized)

[ADC value]

10 20 30 40 50 60 70 80 90 100

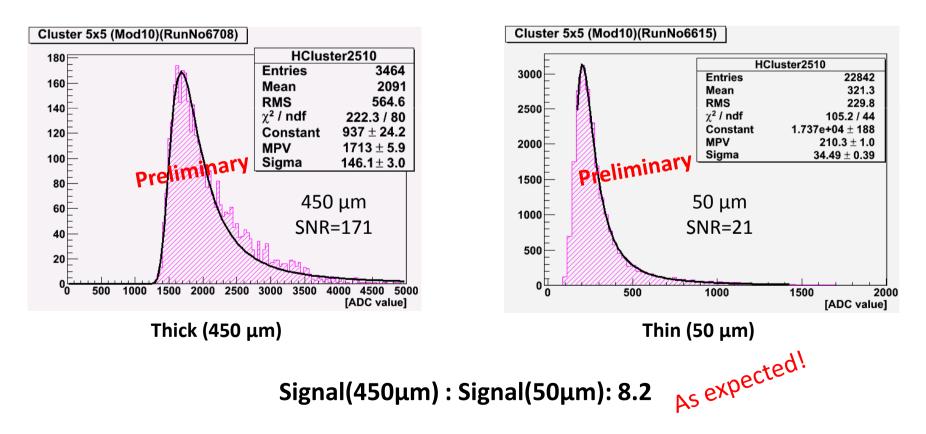

Belle II design: Thin and thick sensors 32x64 pixels L=6 μm Pixel pitch: 50x75x50 μm<sup>3</sup> CURO readout

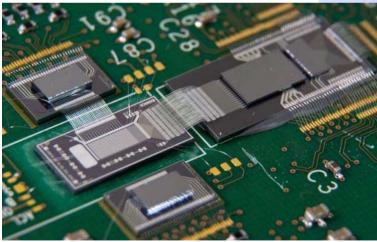

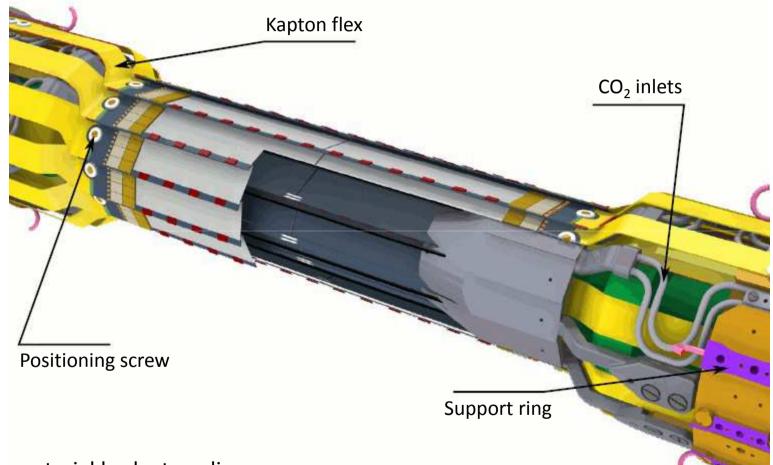

#### **Mechanical design**

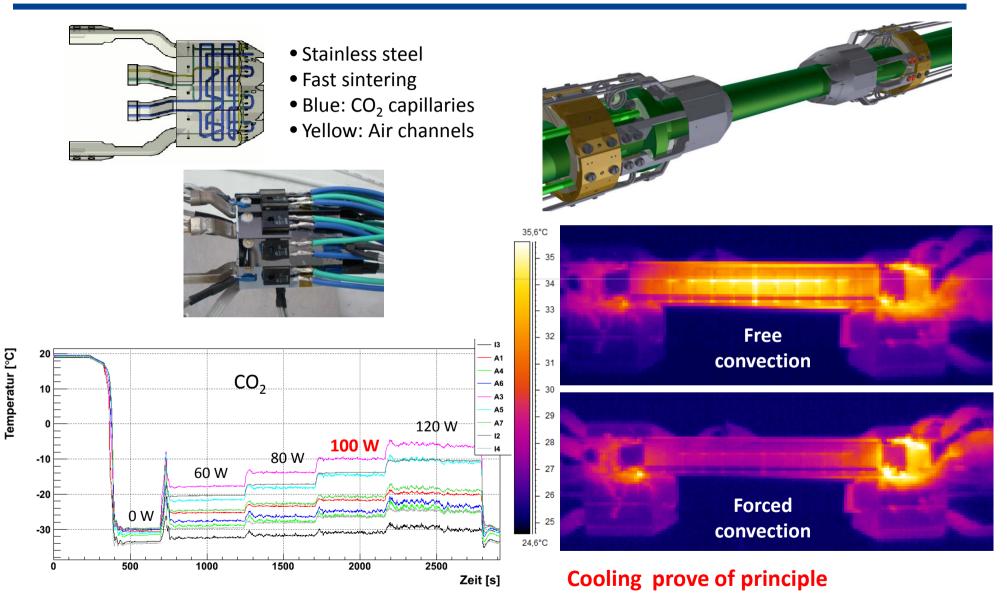

#### Low material budget cooling

- Massive structures outside the acceptance to cool down the readout chips

- The center of the ladder rely on cold air

#### Thermal studies: mock up

- A new super flavour factory, SuperKEKB is currently being built in KEK (Japan)

- To fully exploit the high luminosity, the detector will be upgraded (Belle II)

- The pixel detector will be made of DEPFET sensors

→ High resolution, low power consumption, low material budget

- The DEPFET PXD entered the construction phase All the aspects are being considered (although not treated in this talk)

- $\rightarrow$  Thin sensors (50 µm) produced and read at full speed (100ns sampling time)

- $\rightarrow$  Cooling principle being proved

## depfet.org

Universität Karlsruhe (TH) Research University • founded 1825

## Thank you very much!

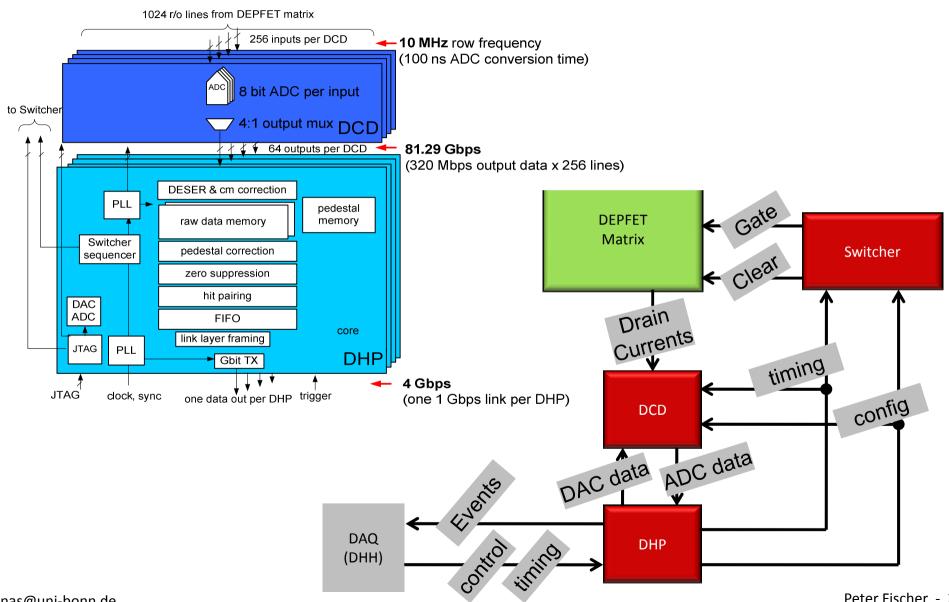

#### **In-module signal flow**

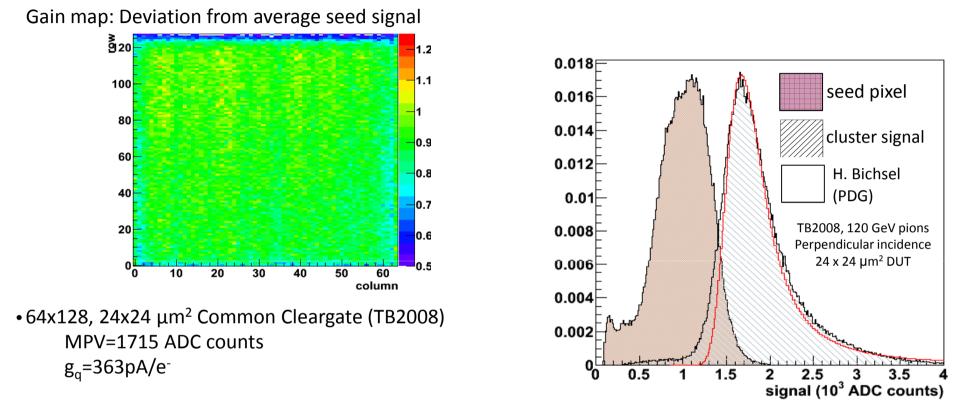

#### TB 2008 and 2009 results

- 64x256, 32x24  $\mu$ m<sup>2</sup> Capacitative Coupled Cleargate (TB2009) MPV~2400 ADC counts g<sub>a</sub>~500pA/e<sup>-</sup>

- 64x256, 20x20  $\mu$ m<sup>2</sup> Common Cleargate, Length<sub>Gate</sub>=5 $\mu$ m (TB2009) MPV~3100 ADC counts g<sub>q</sub>~650pA/e<sup>-</sup> (2x previous g<sub>q</sub>, as expected)

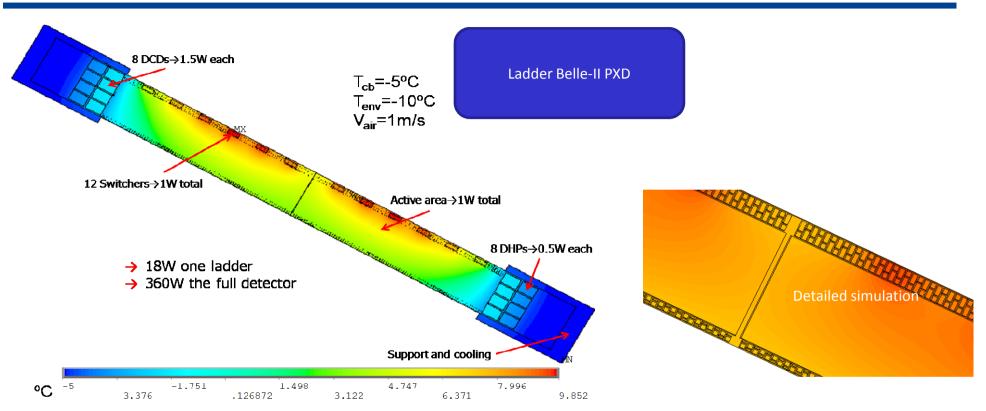

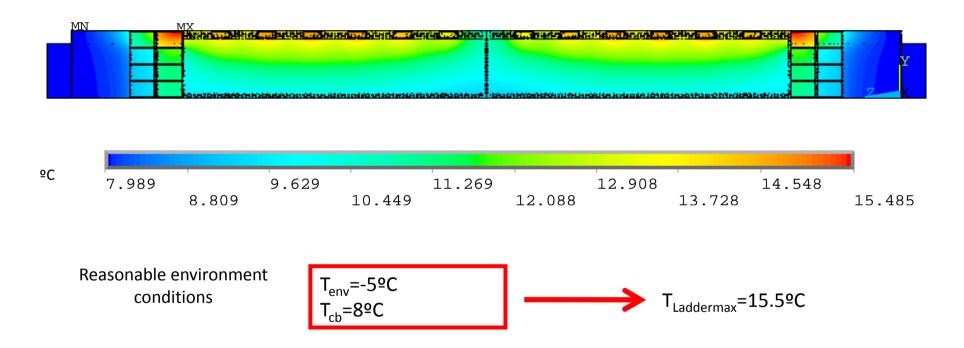

#### Finding the optimal environment

- Implement the full Belle-II ladder geometry in f.e- software

- Apply the loads to the different elements (DCD,DHP,SW,Sensor)

- Find an optimal cooling solution (find T<sub>env</sub> and T<sub>cb</sub>) for the current upper limits on the temperatures:

Temperature distribution along the ladder

- The end of the stave will be cooled by CO<sub>2</sub> inside the cooling block

- The center will be cooled by blowing cold air

ightarrow Both, SVD and PXD subdetectors will be isolated of the CDC