### Wir schaffen Wissen – heute für morgen

Aberystwyth 12th - 16th September 2011

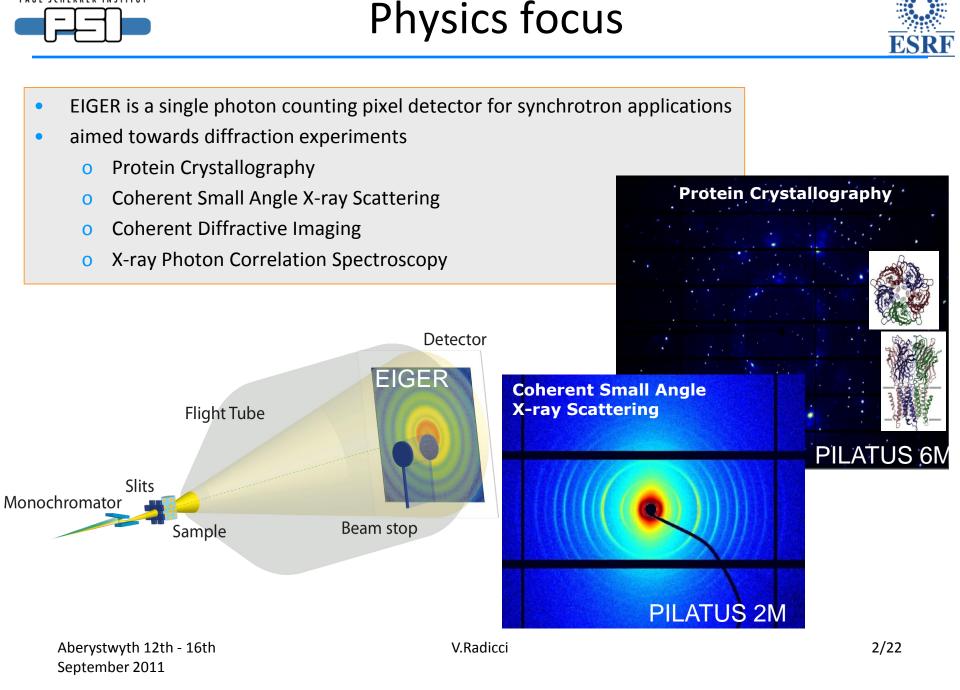

# EIGER a new single photon counting detector for X Ray applications: performance of the chip.

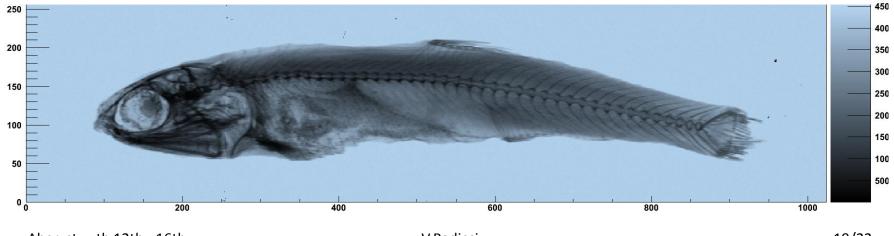

Valeria Radicci Paul Scherrer Institute & ESRF

PAUL SCHERRER INSTITUT

### Requirements for an ideal detector

| EIGER, designed by PSI-SLS detector group, was optimized to<br>satisfy the main requirements for an ideal detector for                            | Chip Size                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| synchrotron radiation applications:                                                                                                               | Pixel Size                                            |

|                                                                                                                                                   | Pixel Array                                           |

| <ul> <li>Single photons sensitivity and no intrinsic noise</li> <li>single photon counting detector</li> </ul>                                    | Technological proc                                    |

| <ul> <li>Good spatial resolution</li> <li>Small pixel size (75x75µm<sup>2</sup>)</li> </ul>                                                       | Sim. Analog<br>Parameters                             |

| <ul> <li>Fast Frame Rate ~tens kHz</li> <li>Simultaneous exposure and readout</li> </ul>                                                          |                                                       |

| <ul> <li>Negligible dead time (~ 3μs)</li> <li>Frame rate up to 22kHz in 4 bit mode</li> </ul>                                                    | Count Rate                                            |

| <ul> <li>Frame rate up to 22kHz in 4 bit mode</li> <li>Detector that can be made as large as possible</li> <li>Modular detector system</li> </ul> | Transistors Matrix<br>Periphery<br>Transistor density |

| <ul> <li>Data transfer parallel at half module level</li> <li>Projects for EIGER 16M Pixel (~32x32 cm<sup>2</sup>)</li> </ul>                     | Nom. power suppli                                     |

| High dynamic range                                                                                                                                | Counter                                               |

| <ul> <li>Count rates up to 1-2 million counts/pixel/second</li> </ul>                                                                             | Readout speed                                         |

| <ul> <li>No spatial distortion and uniform response</li> </ul>                                                                                    | Threshold adjustme                                    |

| <ul> <li>for X-ray energy range few keV to 20 keV</li> </ul>                                                                                      | Analog out for test                                   |

|                                                                                                                                                   | Overflow counter                                      |

| Chip Size                                             | 19.3x20.1 mm <sup>2</sup>                                                                                                          |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Pixel Size                                            | 75x75 μm²                                                                                                                          |

| Pixel Array                                           | 256x256 = 65536                                                                                                                    |

| Technological process                                 | UMC 0.25µm; Rad tol. Design<br>>4MRad                                                                                              |

| Sim. Analog<br>Parameters                             | Gain: 44.6 μV/e-<br>30ns peaking time<br>Timing: 151ns (Ret.to 0@1%)<br>Noise: 135e-rms<br>Static Power:<br>8.8μW/pixel(0.6W/chip) |

| Count Rate                                            | 3.4x10 <sup>9</sup> xray/mm <sup>2</sup> /s                                                                                        |

| Transistors Matrix<br>Periphery<br>Transistor density | 28.44M<br>>120 000<br>430/pix                                                                                                      |

| Nom. power supplies                                   | 1.1V(analog), 2V(digital),<br>1.8V(I/O)                                                                                            |

| Counter                                               | binary, configurable<br>4,8,12bit, double buffered                                                                                 |

| Readout speed                                         | ~22kHz@4bit mode                                                                                                                   |

| Threshold adjustment                                  | Yes 6 Trim Bits                                                                                                                    |

| Analog out for testing                                | Yes                                                                                                                                |

| Overflow counter                                      | Yes                                                                                                                                |

PAUL SCHERRER INSTITUT

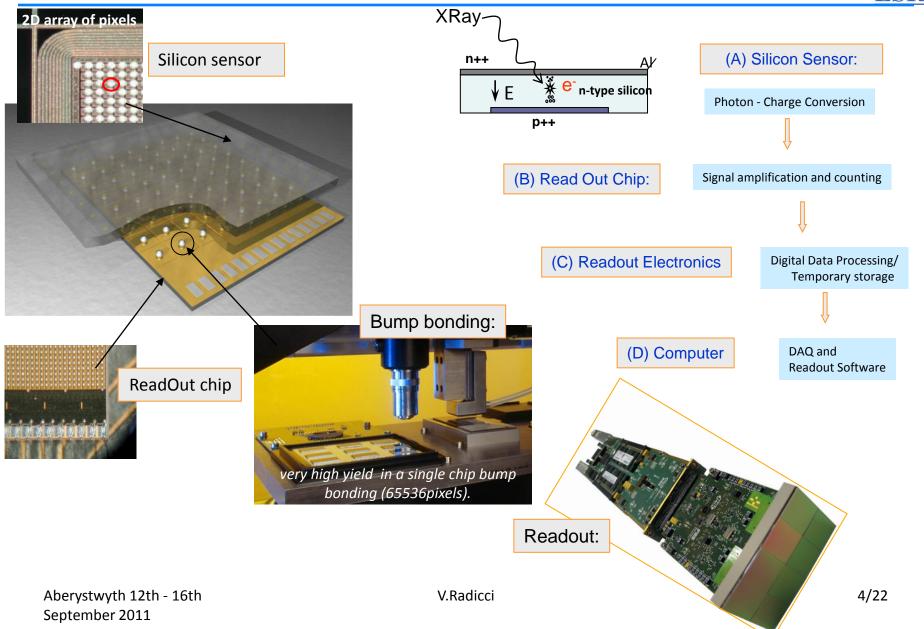

### **EIGER: Hybrid Detector**

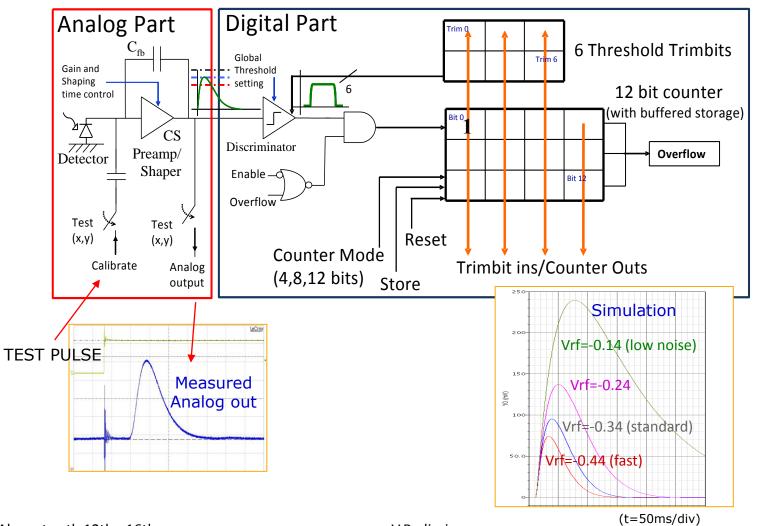

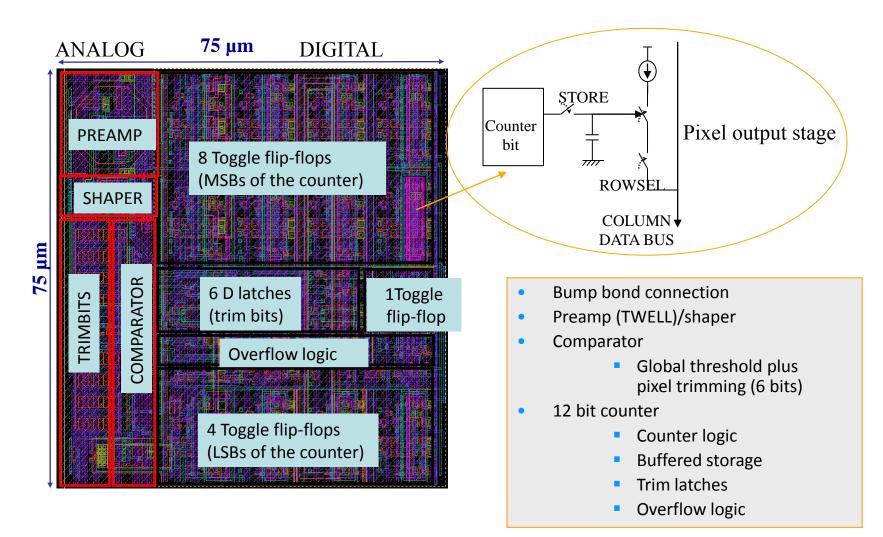

EIGER Pixel Cell

### **EIGER Pixel on Silicon**

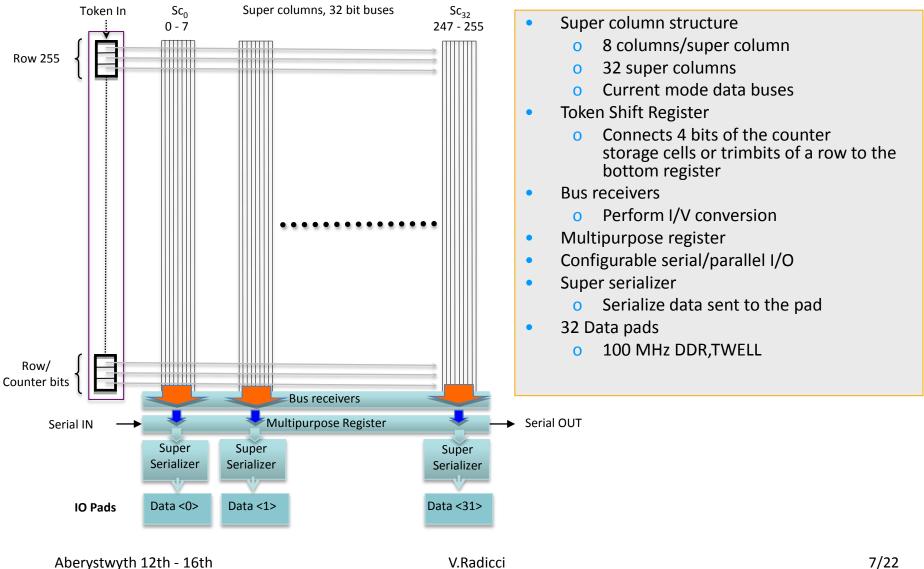

### **EIGER readout architecture**

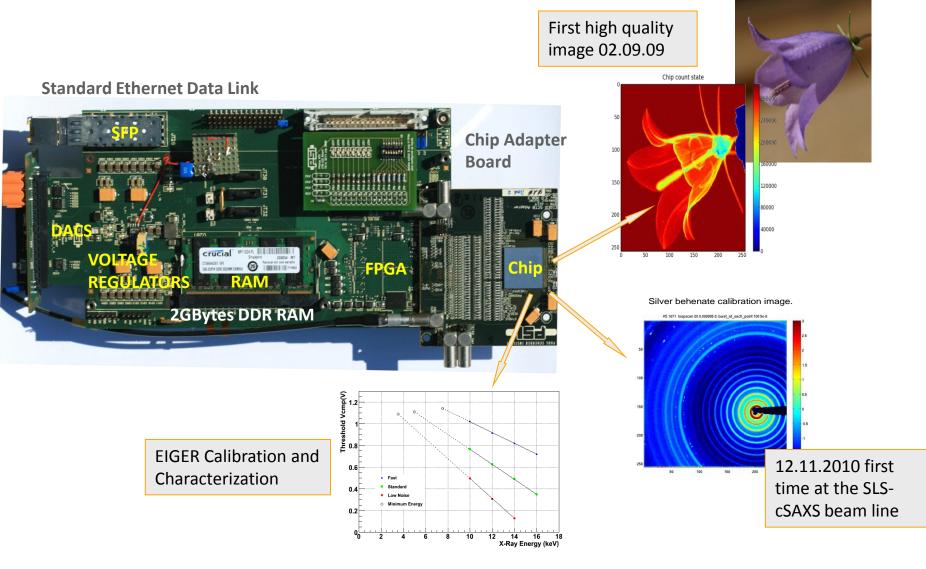

## **EIGER Single chip test Setup**

Aberystwyth 12th - 16th September 2011

# Single chip calibration plan

### The samples

- several single chips tested with an XRay tube and Fluorescence samples for Trimming and Calibration.

- 1 chip tested at the PSI-Optics beam line in two different periods (25-27/02/2011 and 17-21/03/2011). E=10-16KeV

### Single Chip Calibration Plan

- Start with DACs settings from simulation

- Optimize the DACs

- Define a threshold trimming procedure

- Measure different detector characteristic

- Energy calibration

- o Noise

- o Threshold dispersion

- Rate Capability

- o Minimum Energy

- Irradiation tests performed at the beam line:

- pixel region irradiated up to a dose of ~6MRad

- row and column periphery up to a dose of ~7Mrad

## **Energy Calibration**

0.7

0.9 1.0

0.8 0.9 1. Vtrh(V)

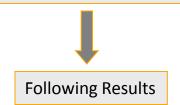

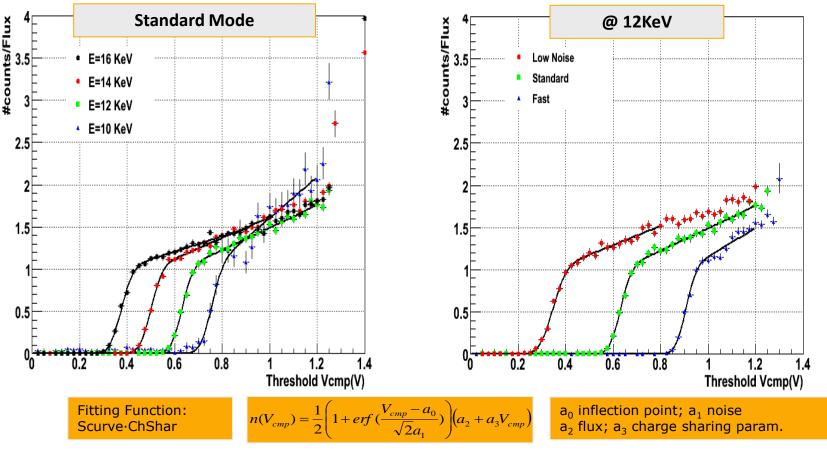

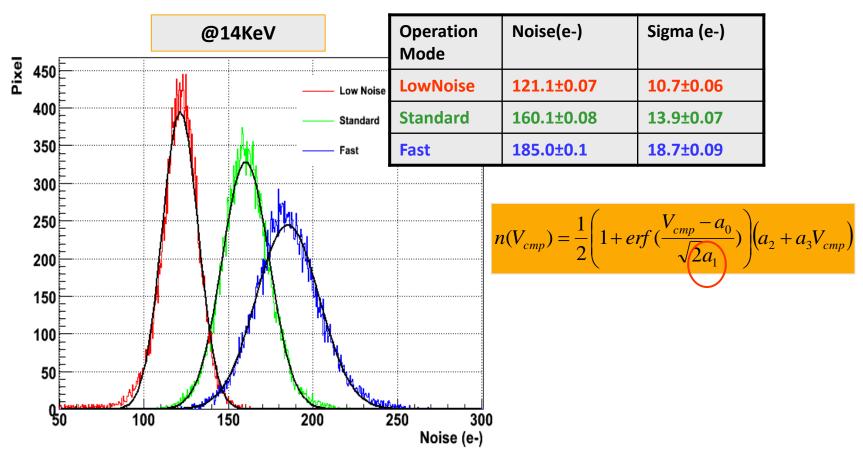

**Energy Calibration:** Monochromatic beam at the Optics Beam line: **10,12,14,16KeV** Threshold scans: Number of counts in each pixel vs Threshold

**Energy Calibration**

September 2011

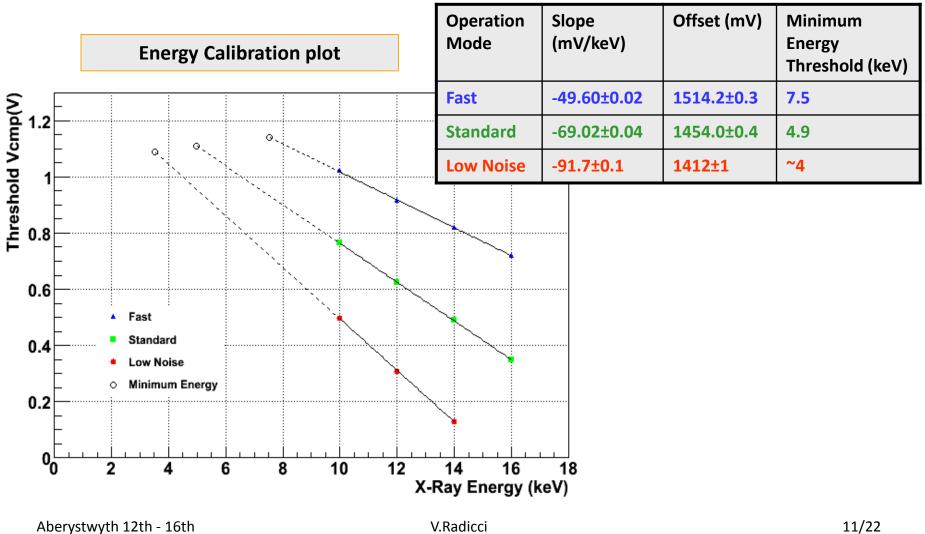

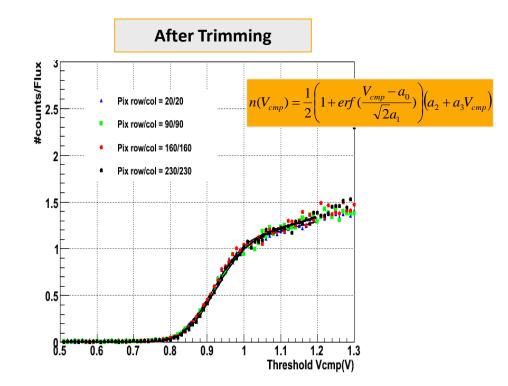

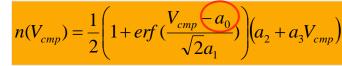

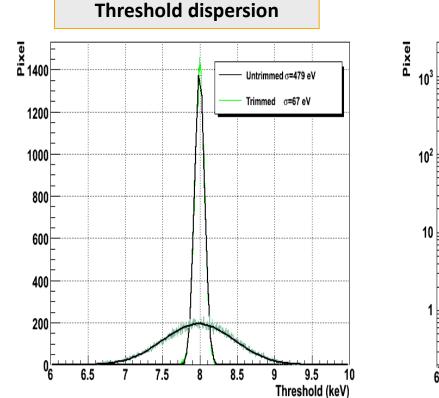

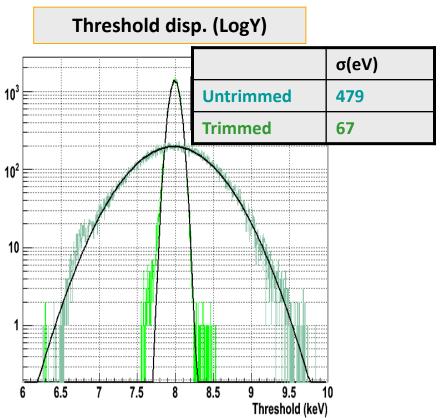

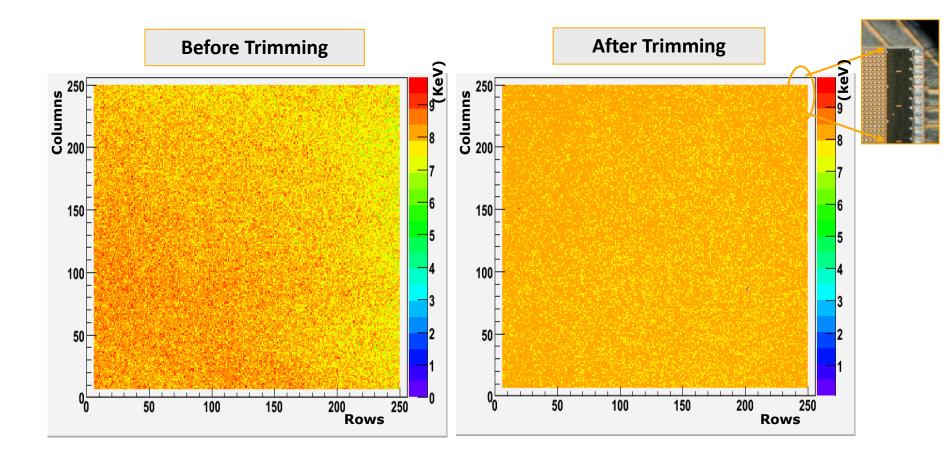

### Data Analysis: Trimming

□ Trimming: XRay tube and Fluorescence screens (Cu Screen 8KeV)

□ Threshold scans: Standard Mode of operation

### **Threshold dispersion**

Aberystwyth 12th - 16th September 2011

### **Threshold Map**

#### Threshold maps: Standard Mode of operation

#### □ Noise distributions: monochromatic beam at the Beam line

Aberystwyth 12th - 16th September 2011

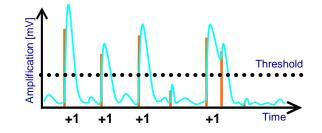

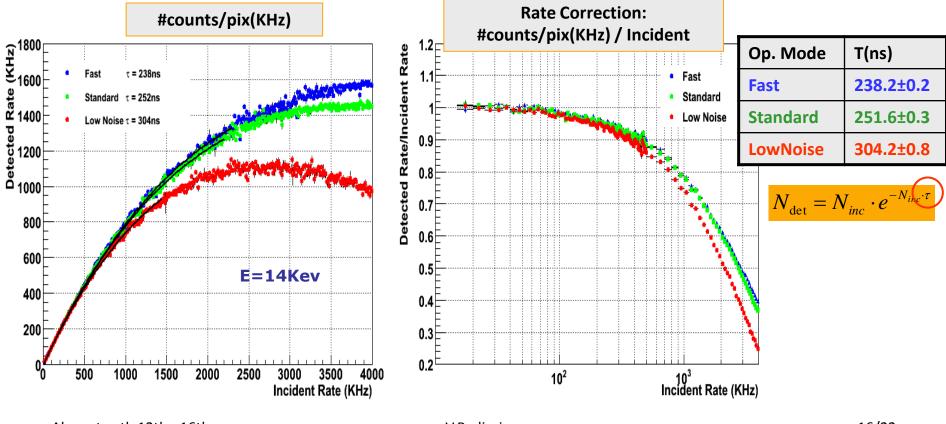

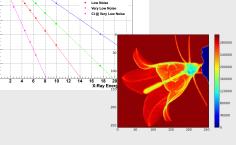

### **Rate Capability**

- Rate Capability: monochromatic beam 14KeV

- Scattering of direct unfocused beam on carbon

- Al. filters to reduce the flux

- □ In each mode of operations Vcmp set @ half energy

Aberystwyth 12th - 16th September 2011

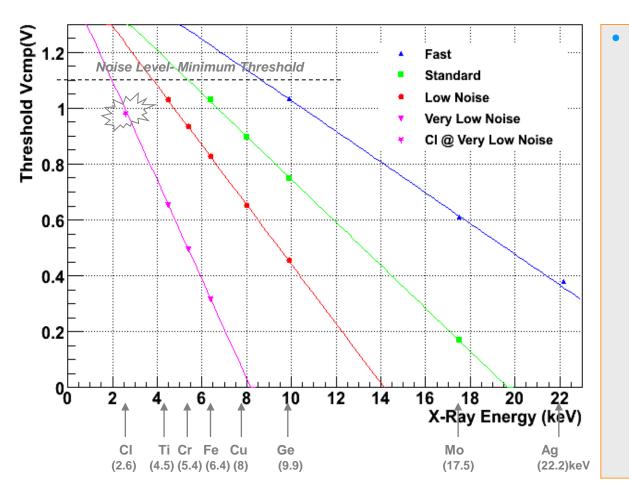

Energy Calibration: XRay tube and Fluorescence samples: from Ag (22KeV) to Ti (4.5KeV) and Cl (2.6KeV)

One new mode operation (Fuchsia): "Very Low Noise" i.e. "Very High Gain of the Preamp."

- good performance of the chip at low energy:

- comparator is linear down to low energies

- minimum threshold Vthr ~1.1V; safe operation of the comparator @ 1V

- threshold energy as low as 2.5keV can set in the highest gain mode

- a further higher gain could also be investigated

- rate capability of "lower noisehigher gain" operation mode to be measured (good feedback from simulation )

Aberystwyth 12th - 16th September 2011

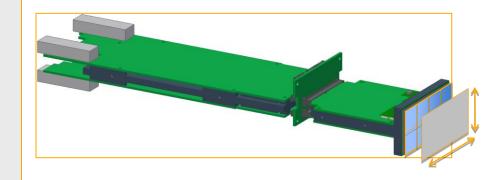

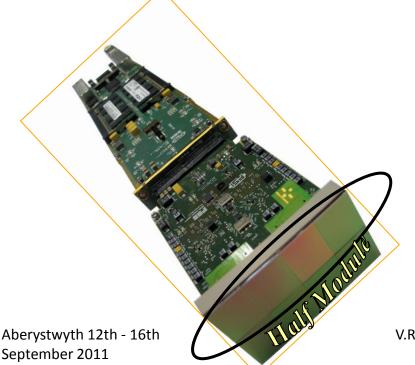

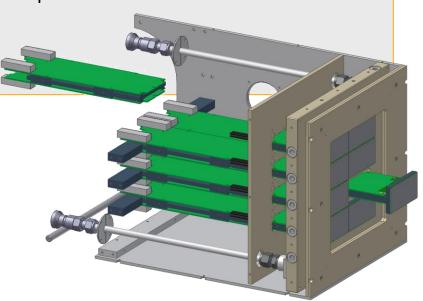

# From Single Chip to Module

#### **EIGER Module:**

- 2x4chips, 500k pixel

- 38 X 77 mm<sup>2</sup> Sensitive area

- Full Module flex high density interconnect board

- Front and Backend Boards

- Parallel readout on half module base

- 8 GB on module data storage

#### Steps towards the module read out:

- Boards have been produced and tested

- Firmware and software are ~ready

- Flex PCB; received May2011; first test OK

- o first Half module connected to the final readout system in May 2011

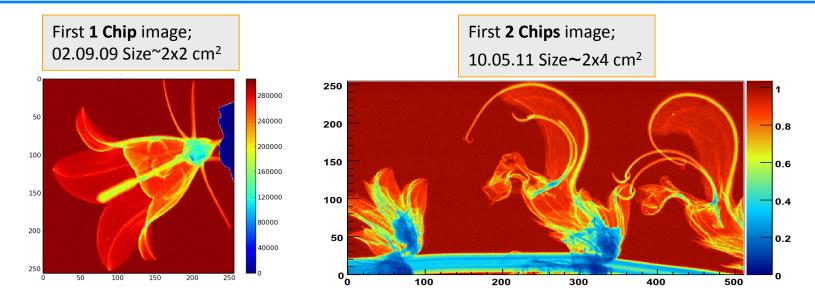

- o two chips read out simultaneously in May 2011 o first half module pictures on the 8<sup>th</sup> Sep. 2011

#### First 4 Chips image; 08.09.1 Size~2x8 cm<sup>2</sup>

Aberystwyth 12th - 16th September 2011

PAUL SCHERRER INSTITUT

### EIGER 4M

#### EIGER 4M pixels:

8 EIGER modules assembled together for a 4 million pixel detector:

- 8x8 chips

- o 2x4 modules

- ~16x16 cm<sup>2</sup>

|              | Detector Spe | Detector Specification |           |  | Data Size   |           |  | Data Rate |         |  |

|--------------|--------------|------------------------|-----------|--|-------------|-----------|--|-----------|---------|--|

|              | Modules      | Chips                  | Pixels    |  | Bit         | Byte      |  | Gbit/s    | MByte/s |  |

|              |              |                        |           |  |             |           |  |           |         |  |

| Chip         |              | 1                      | 65'536    |  | 524 288     | 65 536    |  | 6.3       | 750     |  |

| Half-Module  | 0.5          | 4                      | 262'144   |  | 2'097'152   | 262'144   |  | 25.2      | 3000    |  |

| Module       | 1            | 8                      | 524'288   |  | 4'194'304   | 524'288   |  | 50.3      | 6000    |  |

| 4M Detector  | 8            | 64                     | 4'194'304 |  | 33'554'432  | 4'194'304 |  | 402.7     | 48000   |  |

| 9M Detector  | 18           | 144                    | 9'437'184 |  | 75'497'472  | 9'437'184 |  | 906.0     | 108000  |  |

| 16M Detector | 32           | 256                    | 16777216  |  | 134'217'728 | 16777216  |  | 1610.6    | 201000  |  |

PAUL SCHERRER INSTITUT

# Conclusions

- The Eiger chip is operational since the end of 2009

- First x-ray images achieved a 22 kHz frame rate

- Detailed calibration in 2011 on several single EIGER chips

- Very good performance of the chip

- Inflection point dispersion of ~70 eV

- Noise sigma ~580 eV or 160 e-

- Minimum Energy threshold ~2.5 keV

- Irradiated chip, up to a dose of ~7Mrad, can be calibrated and works at full speed.

- Chips tested up to now are out of foundry specifications

- the same chip design has been produced a second time and are within the foundry specifications

- it is currently being prepared for wafer testing and bump bonding

- from simulation we expect to have improved performances: lower noise and faster speed!

- First experiments at SLS beam line

- Time resolved experiments on proteins

- X-ray Photon Correlation Spectroscopy

- We are working towards modules

- Front and Backend Boards produced

- Firmware and software ready

- First 2 chips XRay images May 2011

- First 4 chips XRay images 8<sup>th</sup> Sep. 2011

- Larger Detector Systems are coming soon

#### Many thanks to the PSI SLS Detector Group

to the PSI-ESRF EIGER Collaboration

#### and to the TEM Group

Anna Bergamaschi, Roberto Di Napoli, Beat Henrich, Dominic Greiffenberg, Ian Johnson, Dhanya Maliakal, Aldo Mozzanica, Christian Ruder, Lukas Schaedler, Bernd Schmitt, Xintian Shi.

Pablo Fajardo, Paul Antoine Douissard.

Elmar Schmid, Gerd Theidel, Akos Schreiber

### Wir schaffen Wissen – heute für morgen

Aberystwyth 12th - 16th September 2011

### **Backup Slides**

PAUL SCHERRER INSTITUT

### **Further considerations**

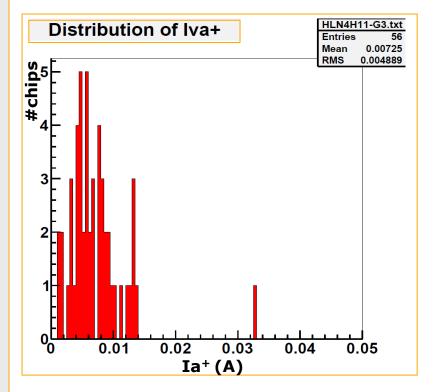

Distribution of Ia<sup>+</sup> for a nominal Va<sup>+</sup> settings

(1.14V) measured on the chips in one wafer

(Wafer test setup)

For the chip under test: Ia<sup>+</sup>~ 8mA;

Iash<sup>+</sup>~ 91mA

Ia<sup>+</sup>/pixel ~ 122nA;

Iash<sup>+</sup>/pixel ~ 1.40μA

Ia<sup>+</sup> and Iash<sup>+</sup> are lower then expected from sim. nom. ~ 182mA /pixel ~ 2.78μA

- Simulation: Lower analogue currents:

- LOW power chip

- BUT higher noise

- Slower preamp.!

The present configuration can be defined as "LOW POWER" chip!