### Results from the NA62 Gigatracker prototype: a low mass and sub-ns time resolution silicon pixel detector

Dr. Elena Martin,

on behalf of the NA62 Gigatracker Working Group PSD9: 9th International Conference on Position Sensitive Detectors Wednesday 14 September 2011, Aberystwyth University

# Outline

- 1. Introduction to NA62 and GigaTracker

- 2. ASIC Demonstator description

- 1. Requirements

- 2. Architecture: sensor assembly, cooling, electronics

- 3. Pixel electronics: On-pixel TDC vs End-of-Column TDC

Conclusions

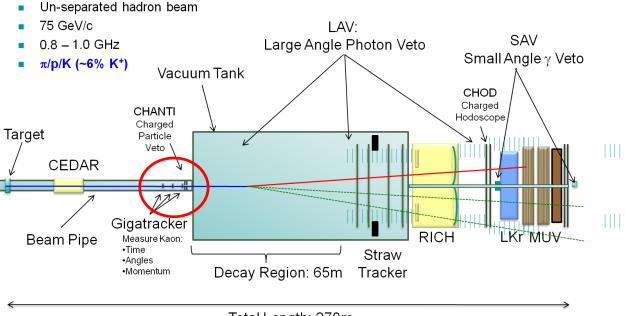

### Introduction to NA62 and GigaTracker

Total Length: 270m

- Fixed target experiment CERN SPS

- 400 GeV/c p<sup>+</sup> incident on target

- 75 ±0.8 GeV/c particles selected at entrance to decay line

- Decay in vacuum tube instrumented with various detectors

- Aims to measure ~80 -100 events over 2 years of run time

- Very rare decay: Branching fraction very small, Massive background rejection required

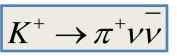

### Introduction to NA62 and GigaTracker

TrajectoryMomentumAngle

•Time

correlate hits with RICH

reduce combinatorics

200 ps per station

$800MHz \leq Total Rate Seen by$

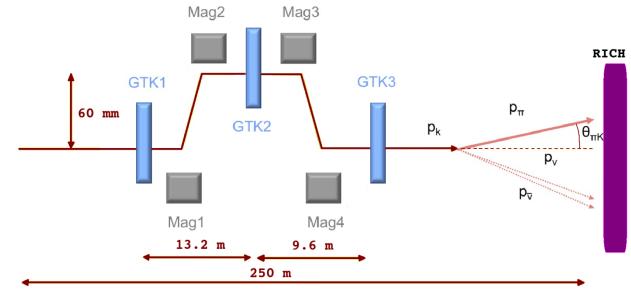

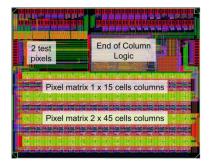

Detector area beam profile •highly non-uniform intensity distribution •2 rows of 5 readout chips

### **ASIC** Demonstator description

| Beam Rate               | 800MHz →1GHz                                                                    |  |

|-------------------------|---------------------------------------------------------------------------------|--|

| Mean Hit Rate/Pixel     | 140kHz (center)                                                                 |  |

| Radiation environment   | 10 <sup>14</sup> n cm² yr <sup>-1</sup>                                         |  |

| Lifetime                | ~1yr                                                                            |  |

| # stations              | 3                                                                               |  |

| Detector area           | 60mm x 27mm                                                                     |  |

| Pixel size              | 300 μm x 300 μm                                                                 |  |

| Pixels/station          | 18000                                                                           |  |

| Readout chip/station    | 10                                                                              |  |

| Sensor technology       | p-in-n                                                                          |  |

| Readout                 | Untriggered                                                                     |  |

| Efficiency              | ≥99%                                                                            |  |

| Material Budget         | ≤0.5% Xo (≤500µm Si)                                                            |  |

| ROC Characteristics     | 130nm CMOS, Thickness ~100µm                                                    |  |

| Sensor Characteristics  | Thickness ~200µm                                                                |  |

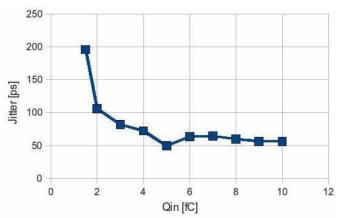

| Dynamic range           | ~(6ke <sup>-</sup> $\rightarrow$ 60ke <sup>-</sup> ), ~(1fC $\rightarrow$ 10fC) |  |

| Q <sub>MP</sub>         | 2.4fC                                                                           |  |

| Time resolution/station | ≤200ps(RMS)                                                                     |  |

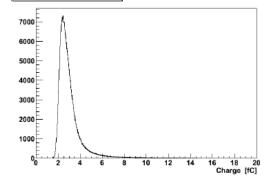

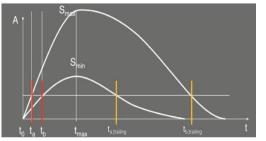

#### Generated signal in GTK1

#### **Géant4 Simulation**

•charge release mechanism is stochastic

•Landau distr. Q<sub>most probable</sub>=2.4 fC

#### Dissipated power perchip ~2 W/cm<sup>2</sup>

Main challenges:

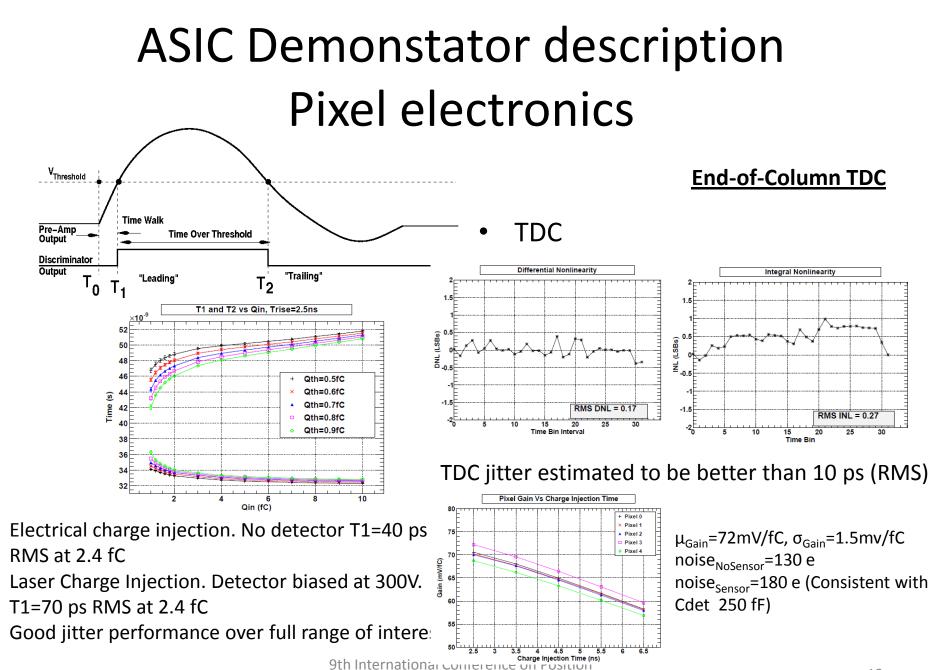

•Time resolution: 200 ps (rms)/station

•On-pixel fast analog pulse shaping (~4 ns peaking time)

•Max data rate per chip: up to 6 Gbit/s

# ASIC Demonstrator description Architecture: assembly, cooling, electronics

| ASSEMBLY                                     | COOLING | ELECTRONICS |

|----------------------------------------------|---------|-------------|

| support and cooling<br>sensor<br>pixel chips |         |             |

| Bump bonds<br>~25 µm                         |         |             |

standard p-in-n sensors 200 μm sensor wafers thick

# ASIC Demonstator description Architecture: assembly, cooling, electronics

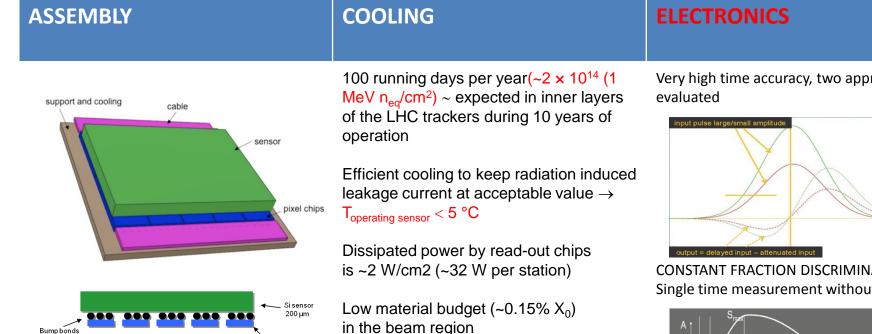

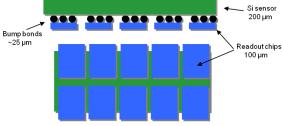

| ASSEMBLY                            | COOLING                                                                                                                                                                           | ELECTRONICS |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| support and cooling cable           | 100 running days per year( $\sim 2 \times 10^{14}$ (1<br>MeV n <sub>eq</sub> /cm <sup>2</sup> ) ~ expected in inner layers<br>of the LHC trackers during 10 years of<br>operation |             |

| pixel chips                         | Efficient cooling to keep radiation induced leakage current at acceptable value $\rightarrow$ T <sub>operating sensor</sub> < 5 °C                                                |             |

|                                     | Dissipated power by read-out chips is ~2 W/cm2 (~32 W per station)                                                                                                                |             |

| Si sensor<br>200 µm<br>Readoutchips | Low material budget (~0.15% $X_0$ ) in the beam region                                                                                                                            |             |

| 100 µm                              | Cooling options under study:<br>•convective cooling in a vessel<br>•micro-channel cooling                                                                                         |             |

| standard p-in-n sensors             |                                                                                                                                                                                   |             |

200 µm sensor wafers thick

# **ASIC** Demonstator description Architecture: assembly, cooling, electronics

standard p-in-n sensors 200  $\mu$ m sensor wafers thick Cooling options under study: convective cooling in a vessel micro-channel cooling

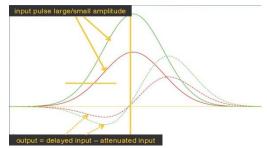

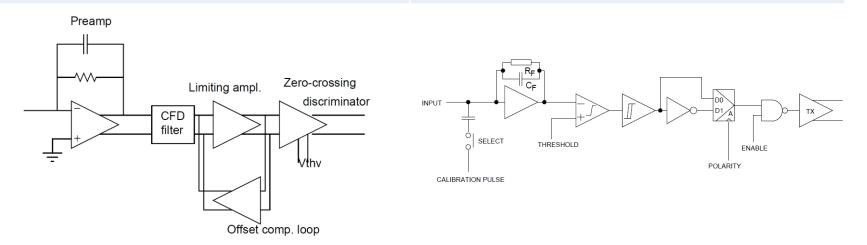

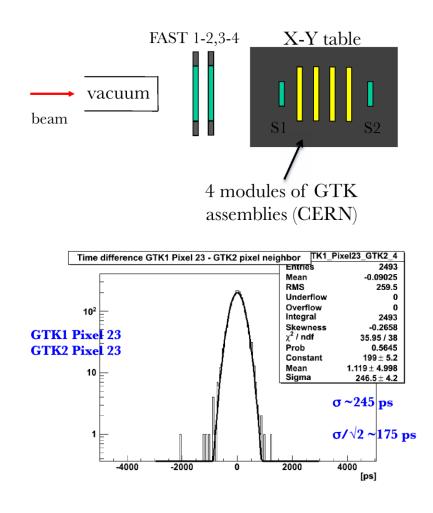

9th International Conference on Position Sensitive Detectors, Aberystwyth University Very high time accuracy, two approaches

CONSTANT FRACTION DISCRIMINATOR Single time measurement without time-walk

TIMF OVER THRESHOLD time-walk correction algorithm based on the signal time over threshold (pulse width)

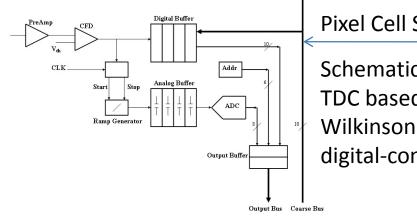

#### **On-pixel TDC**

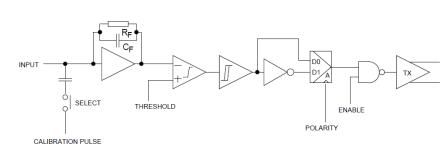

CFD filter + on-pixel TDC based on TAC •maximize signal processing on the pixel cell (including TDC) and distribute clock to the pixel matrix (digital noise)

minimize complexity of end of column logic (no need to propagate the comparator signal outside the pixel)

must be designed to be radiation-tolerant (total dose and SEU aspects), due to the high radiation dose received in the pixel area

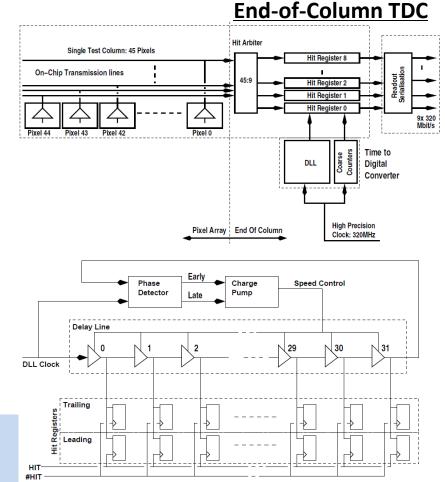

#### End-of-Column TDC

ToT + DLL TDC shared among group of pixels •use high precision digital TDC in the end of column, shared by a group of pixels

minimize on-pixel processing for minimum noise

pixel comparator signals should be propagated to the chip periphery (communication of ultra-fast signal in column transmission lines)

**On-pixel TDC:** prototype measured with the proposed architecture

### **Pixel Cell Schematic**

Schematic of the pixel TDC based on a Wilkinson time-todigital-converter

#### **Constant Fraction Discriminator measurements**

| Dinamic Range        | 1-10fC         |

|----------------------|----------------|

| Area                 | 154 um x 74 um |

| Jitter at 1MIP       | 90ps rms       |

| Time-Walk resolution | 75ps rms       |

| Power consumption    | 900 uW         |

#### **On-pixel TDC:** prototype has been re-designed and the CFD improved

On the base of the experience acquired from the CFD on silicon, a second CFD was studied. Improve the time precision by making the CFD more robust to shape variations.

Smaller area by the delay line of the filter (140 $\mu$ mx69 $\mu$ m)

Trigger discriminator to enable the zero-crossing one (Increases the P<sub>consumption</sub>=1.3mW.

While this architecture is not yet fabricated, simulations show good performances in correcting both time-walk and fluctuations induced by shape variations.

The simulations were performed using 200 input signals generated with Montecarlo for amplitude variations and shape variations coming from statistical fluctuations in the charge released along the sensor and to nonuniformity in the electrical field at the borders of it.

| Process<br>corner | RMS jitter @ 1MIP<br>(ps) | Time resolution<br>(ps rms) |

|-------------------|---------------------------|-----------------------------|

| Typical<br>mean   | 65                        | 29                          |

| + 3σ              | 79                        | 25                          |

| - 3σ              | 68                        | 26                          |

"Implementation of Constant-Fraction-Discriminators (CFD) in Sub-micron CMOS Technology" S. Garbolino et al.

To be presented at IEEE-NSS 2011, Valencia Jitter is due to parasitc capacitors, reducing slope of the signal

- Power = 120uA/pixel

- Gain = 70mV/fC

- 20 fF test charge injection

- Preamp:  $C_F = 14 fF$  and  $R_F = 200 k\Omega$

- TXpre-emphasis, P=100uA

320MHz clock, 32 starved delay cells

→97 ps time bin.

Sensitive Detectors, Aberystwyth University

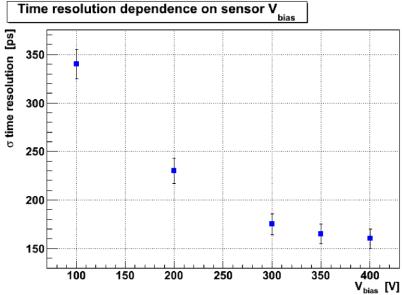

#### End-of-Column TDC

- HPTDC used for all external measurements (25 ps time binning)

- Consistently better than 200 ps

# Conclusions

- 2 options have been evaluated with 2 different prototypes:

- CFD simulation shows the possibility of time resolution below 50ps

- ToT time resolution measured in beam test consistently lower than 200ps

- Another <u>CFD</u> prototype is being fabricated to study <u>lower time resolution architecture</u>

- ToT architecture has shown a more robust behavour and has been choosen to be included in the GTK system, and a full circuit is being developed